# Winbond Mobile Keyboard and Embedded Controller W83L950D

Revision: 1.0 Date: June 2003

- I -

|   | PAGES | DATE             | VERSION | VERSION<br>ON WEB | MAIN CONTENTS                                         |

|---|-------|------------------|---------|-------------------|-------------------------------------------------------|

| 1 | N.A.  | 02/Jan.          | 0.50    | N.A.              | All of the versions before 0.50 are for internal use. |

| 2 | 7     | 02/Feb.          | 0.51    | N.A.              | Add LPC definition.                                   |

| 3 | 109   | 02/Feb.          | 0.51    | N.A.              | Contact information update.                           |

| 4 |       | 03/Feb           | 0.60    | N.A.              | Release for C version chip.                           |

| 5 |       | June 23,<br>2003 | 1.0     | N.A.              | Refine structure and contents.                        |

#### **Revision History**

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

#### Tables of Contents-

| 1. | GENE   | RAL DESCRIPTION                    | 1    |

|----|--------|------------------------------------|------|

| 2. | FEATU  | JRES                               | 1    |

| 3. | PIN C  | ONFIGURATION                       | 3    |

| 4. | PIN DI | ESCRIPTION                         | 4    |

|    | 3.1.   | Basic KBC Function Signals         | 5    |

|    | 3.2.   | Specific Function Signals          | 8    |

|    | 3.3.   | Power, Rest and Clock Signals      | . 10 |

| 5. | SYSTE  | EM BLOCK DIAGRAM                   | 11   |

| 6. | MICRO  | O COMPUTER ARCHITECTURE            | . 12 |

|    | 6.1    | ALU                                | . 12 |

|    | 6.2    | Accumulator                        | . 12 |

|    | 6.3    | B Register                         | . 12 |

|    | 6.4    | Program Status Word (PSW)          | . 12 |

|    | 6.5    | Data Pointers and Selection        | . 12 |

|    | 6.6    | Stack Pointer                      | . 12 |

|    | 6.7    | Program Memory                     | . 13 |

|    | 6.8    | Scratch Pad RAM                    | . 13 |

|    | 6.9    | SFR Bit Addressable Location       | . 15 |

|    | 6.10   | External SRAM                      | . 16 |

|    | 6.11   | Scratched ULTRA ROM                | . 16 |

| 7. | SPEC   | AL FUNCTION REGISTER               | . 17 |

|    | 7.1    | Standard SFR Address and Registers | . 17 |

|    | 7.2    | Advanced SFR Address and Registers | . 18 |

| 8. | 8051 A | ND BASIC CONTROL REGISTER          | . 19 |

|    | 8.1    | Stack Pointer                      | . 19 |

|    | 8.2    | Data Pointer Low                   | . 19 |

|    | 8.3    | Data Pointer High                  | . 19 |

|    | 8.4    | Data Pointer Low1                  | . 19 |

|    | 8.5    | Data Pointer High1                 | . 19 |

9.

|     | 8.6    | Data Pointer Select                            | . 20 |

|-----|--------|------------------------------------------------|------|

|     | 8.7    | Power Control                                  | . 20 |

|     | 8.8    | Program Status Word                            | . 20 |

|     | 8.9    | Accumulator                                    | . 21 |

|     | 8.10   | B Register                                     | . 21 |

|     | 8.11   | CLK Controller Register                        | . 21 |

|     | 8.12   | Chip Controller Register                       | . 22 |

|     | 8.13   | Chip Status Register                           | . 22 |

|     | 8.14   | Device ID; Device REV Register                 | . 22 |

| 9.  | INTER  | RUPTS                                          | . 23 |

|     | 9.1    | Interrupt Control                              | . 23 |

|     | 9.2    | Interrupt Source Selection                     | . 23 |

|     | 9.3    | External interrupt Pin Selection               | . 23 |

|     | 9.4    | Key Input Interrupt (Key-on Wake Up)           | . 23 |

|     | 9.5    | Interrupt Vector Table                         | . 25 |

|     | 9.6    | Interrupt Enable Register (IE)                 | . 26 |

|     | 9.7    | Interrupt Enable Register 1(IE1)               | . 26 |

|     | 9.8    | Interrupt Enable Register 1(IE2)               | . 27 |

|     | 9.9    | Interrupt Priority Register (IP)               | . 28 |

|     | 9.10   | Interrupt Priority Register 1(IP1)             | . 28 |

|     | 9.11   | Interrupt Priority Register 1(IP2)             | . 29 |

|     | 9.12   | Interrupt Type Register 1(IT1)                 | . 30 |

|     | 9.13   | Interrupt Type Register 2(IT2)                 | . 30 |

|     | 9.14   | Interrupt Request Register (IREQ)              | . 31 |

|     | 9.15   | Interrupt Request1 Register 1(IREQ1)           | . 32 |

|     | 9.16   | Interrupt Request2 Register 1(IREQ2)           | . 32 |

|     | 9.17   | Interrupt Source Selection Register 1(INTSEL1) | . 33 |

|     | 9.18   | Interrupt Source Selection Register 2(INTSEL2) | . 34 |

| 10. | BUS IN | ITERFACE AND GATEA20 / KBRESET/ PORT92H        | . 35 |

|     | 10.1   | Data Bus Buffer Control Register (DBBCON)      | . 35 |

11.

| 10.2   | Data Bus Buffer Register 0(DBB0)                   | 36  |  |  |  |  |  |  |  |

|--------|----------------------------------------------------|-----|--|--|--|--|--|--|--|

| 10.3   | Data Bus Buffer Status Register 0(DBBSTS0)         | 36  |  |  |  |  |  |  |  |

| 10.4   | Data Bus Buffer Register 1(DBB1)                   | 36  |  |  |  |  |  |  |  |

| 10.5   | ata Bus Buffer Status Register 1(DBBSTS1)          |     |  |  |  |  |  |  |  |

| 10.6   | erial IRQ Select Register 1(SIRQ1)                 |     |  |  |  |  |  |  |  |

| 10.7   | Serial IRQ Select Register 2(SIRQ2)                | 37  |  |  |  |  |  |  |  |

| 10.8   | Data Bus Buffer 0 Address Low Register (DBB0ADDL)  | 37  |  |  |  |  |  |  |  |

| 10.9   | Data Bus Buffer 0 Address High Register (DBB0ADDH) | 37  |  |  |  |  |  |  |  |

| 10.10  | Data Bus Buffer 1 Address Low Register (DBB1ADDL)  | 37  |  |  |  |  |  |  |  |

| 10.11  | Data Bus Buffer 1 Address High Register (DBB1ADDH) | 38  |  |  |  |  |  |  |  |

| 10.12  | Hardware GATEA20 and KBRESET and Port 92h Support  | 38  |  |  |  |  |  |  |  |

| 10.13  | Advance Keyboard Controller Register (AKBCTRL)     | 38  |  |  |  |  |  |  |  |

|        | 10.13.1 KB Control Register (KBCTRL)               | .39 |  |  |  |  |  |  |  |

|        | 10.13.2 Port 92 Control Register                   | .39 |  |  |  |  |  |  |  |

| I/O PO | RT                                                 | 40  |  |  |  |  |  |  |  |

| 11.1   | Port GP0 Data Register (GP0)                       | 40  |  |  |  |  |  |  |  |

| 11.2   | Port GP0 Direction Register (GP0D)                 | 40  |  |  |  |  |  |  |  |

| 11.3   | Port GP1 Data Register (GP1)                       | 40  |  |  |  |  |  |  |  |

| 11.4   | Port GP1 Direction Register (GP1D)                 | 40  |  |  |  |  |  |  |  |

| 11.5   | Port GP2 Data Register (GP2)                       | 40  |  |  |  |  |  |  |  |

| 11.6   | Port GP2 Direction Register (GP2D)                 | 40  |  |  |  |  |  |  |  |

| 11.7   | Port GP3 Data Register (GP3)                       | 41  |  |  |  |  |  |  |  |

| 11.8   | Port GP3 Direction Register (GP3D)                 | 41  |  |  |  |  |  |  |  |

| 11.9   | Port GP4 Data Register (GP4)                       | 41  |  |  |  |  |  |  |  |

| 11.10  | Port GP4 Direction Register (GP4D)                 | 41  |  |  |  |  |  |  |  |

| 11.11  | Port GP5 Data Register (GP5)                       | 41  |  |  |  |  |  |  |  |

| 11.12  | Port GP5 Direction Register (GP5D)                 | 41  |  |  |  |  |  |  |  |

| 11.13  | Port GP6 Data Register (GP6)                       | 42  |  |  |  |  |  |  |  |

| 11.14  | Port GP6 Direction Register (GP6D)                 | 42  |  |  |  |  |  |  |  |

- V -

|     | 11.15 | Port GP7 Data Register     | (GP7)                                    | 42 |

|-----|-------|----------------------------|------------------------------------------|----|

|     | 11.16 | Port GP7 Direction Regi    | ister (GP7D)                             | 42 |

|     | 11.17 | Port GP8 Data Register     | / Port GP4 Input Register (GP8/GP4)      | 42 |

|     | 11.18 | Port GP8 Direction Regi    | ister / Port 7 Input Register (GP8D/GP7) | 42 |

|     | 11.19 | Port Control Register 1(   | PCTRL1)                                  | 43 |

|     | 11.20 | Port Control Register 2    | (PCTRL2)                                 | 43 |

|     | 11.21 | Port Control Register 3    | (PCTRL3)                                 | 44 |

| 12. | TIMEF |                            |                                          | 45 |

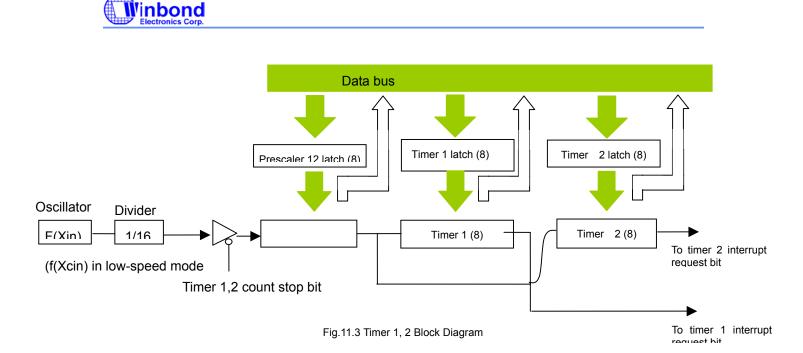

|     | 12.1  | Timer 1 and Timer 2        |                                          | 45 |

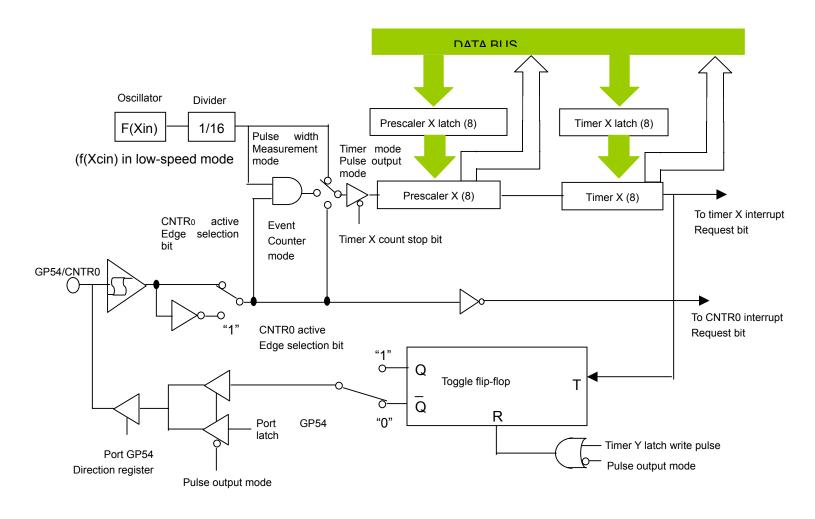

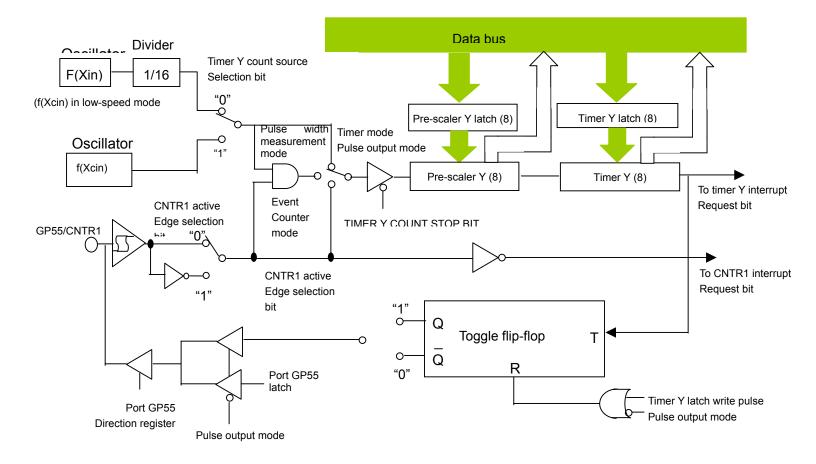

|     | 12.2  | Timer X and Timer Y        |                                          | 45 |

|     |       | 12.2.1 Timer Mode          |                                          | 45 |

|     |       | 12.2.2 Pulse Output Mod    | e                                        | 45 |

|     |       | 12.2.3 Event Counter Mo    | de                                       | 45 |

|     |       | 12.2.4 Pulse Width Meas    | urement Mode                             | 45 |

|     | 12.3  | Prescaler 12 (PRE 12)      |                                          |    |

|     | 12.4  | Timer 1 (T1)               |                                          | 48 |

|     | 12.5  | Timer 2 (T2)               |                                          | 48 |

|     | 12.6  | Timer XY mode register (   | (TM)                                     | 48 |

|     | 12.7  | Prescaler X (PREX)         |                                          | 49 |

|     | 12.8  | Timer X (TX)               |                                          | 49 |

|     | 12.9  | Prescaler Y (PREY)         |                                          | 49 |

|     | 12.10 | Timer Y (TY)               |                                          | 49 |

| 13. | SERIA | . I/O                      |                                          | 50 |

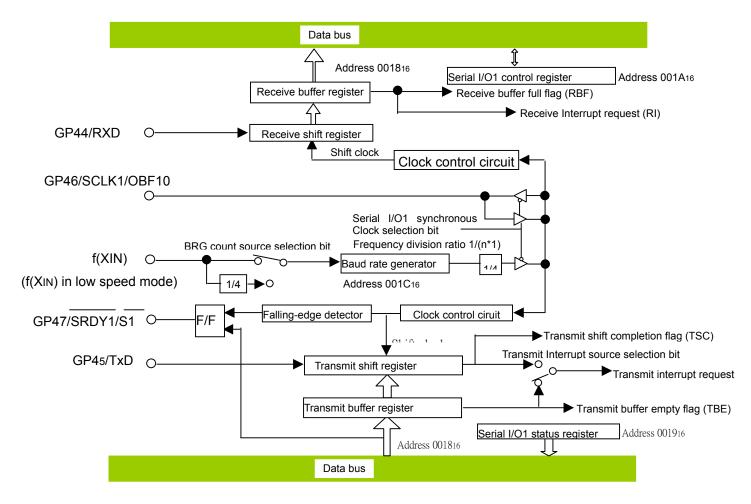

|     | 13.1  | Serial I/O 1               |                                          | 50 |

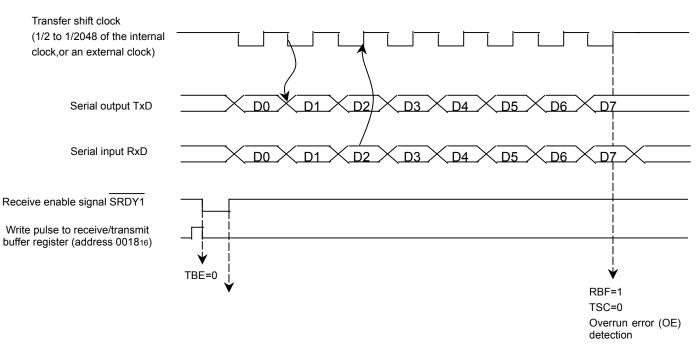

|     |       | 13.1.1 Clock Synchronou    | s Serial I/O Mode                        | 50 |

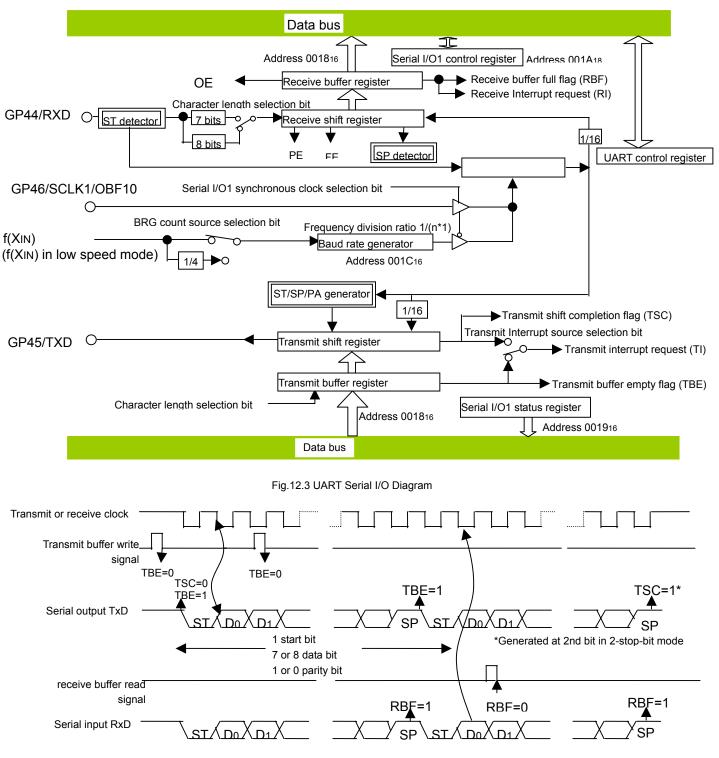

|     |       | 13.1.2 Asynchronous Ser    | ial I/O (UART) Mode                      | 51 |

|     |       | 13.1.3 Transmit / Receive  | e buffer register (TB/RB)                | 53 |

|     |       | 13.1.4 Serial I/O 1 status | register (SIO1STS)                       | 53 |

|     |       | 13.1.5 Serial I/O 1 contro | I register (SIO1CON)                     | 54 |

|     |       | 13.1.6 UART control regis  | ster (UARTCON)                           | 54 |

|     |       |                            |                                          |    |

|     |       | 13.1.7 Baud rate generator (BRG)              | 55 |

|-----|-------|-----------------------------------------------|----|

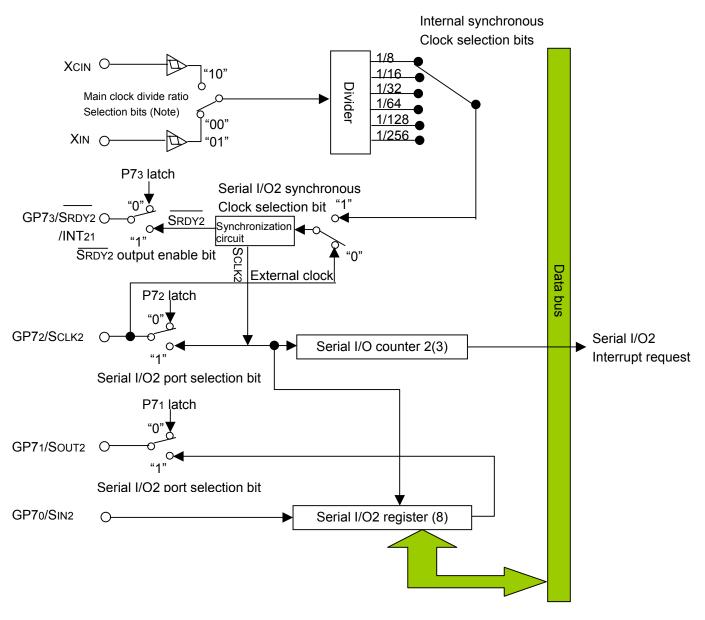

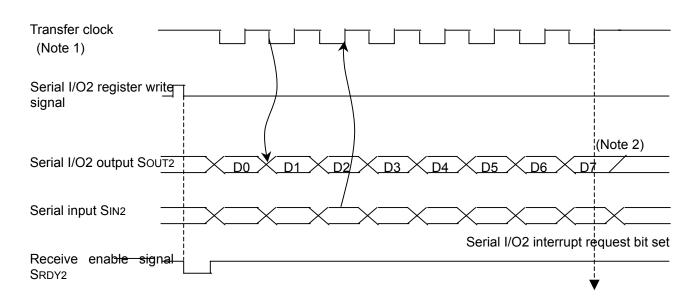

|     | 13.2  | Serial I/O 2                                  | 56 |

|     | 13.3  | Serial I/O 2 control register (SIO2CON)       | 57 |

|     | 13.4  | Serial I/O2 register (SIO2)                   | 58 |

| 14. | PWM   |                                               | 59 |

|     | 14.1  | PWM 0 and 1 Operation                         | 59 |

|     | 14.2  | Transfer From Register to Latch               | 59 |

|     | 14.3  | PWM0H register (PWM0H)                        | 59 |

|     | 14.4  | PWM0L register (PWM0L)                        | 59 |

|     | 14.5  | PWM1H register (PWM1H)                        | 59 |

|     | 14.6  | PWM1L register (PWM1L)                        | 60 |

| 15. | AUXII | IARY PWM CHANNLE                              | 60 |

|     | 15.1  | AUXILIARY PWM Controller Register (APWMCON)   | 60 |

|     | 15.2  | PWM CHANNLE 2 PERIOD Low BYTE (PWM2PL)        | 61 |

|     | 14.3  | PWM CHANNLE 2 PERIOD High BYTE (PWM2PH)       | 61 |

|     | 14.4  | PWM CHANNLE 2 HIGH SIGNAL Low BYTE (PWM2HSL)  | 61 |

|     | 14.5  | PWM CHANNLE 2 HIGH SIGNAL High BYTE (PWM2HSH) | 61 |

|     | 14.6  | PWM CHANNLE 3 PERIOD Low BYTE (PWM3PL)        | 61 |

|     | 14.7  | PWM CHANNLE 3 PERIOD High BYTE (PWM3PH)       | 61 |

|     | 14.8  | PWM CHANNLE 3 HIGH SIGNAL Low BYTE (PWM3HSL)  | 61 |

|     | 14.9  | PWM CHANNLE 3 HIGH SIGNAL High BYTE (PWM3HSH) | 61 |

| 16. | A-D C | ONVERTER                                      | 62 |

|     | 16.1  | AD/DA control register 0(ADCON)               | 63 |

|     | 16.2  | A/D conversion register 0(AD0)                | 64 |

|     | 16.3  | A/D conversion register 1(AD1)                | 64 |

|     | 16.4  | D-A Converter                                 | 64 |

|     | 16.5  | D-A Conversion Register 0(DA0)                | 64 |

|     | 16.6  | D-A Conversion Register 1(DA1)                | 64 |

| 17. | COM   | PARATOR CIRCUIT                               | 64 |

|     | 17.1  | Comparator Operation                          | 64 |

- VII -

|     | 17.2   | Comparator Data Register (CMPD)                            | 65 |

|-----|--------|------------------------------------------------------------|----|

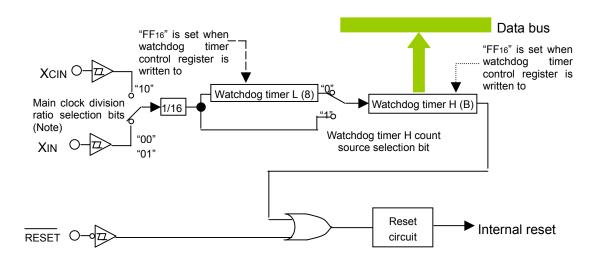

| 18. | WATC   | HDOG TIMER                                                 | 65 |

|     | 17.1.  | Standard Operation of Watchdog Timer                       | 65 |

|     | 17.2.  | Initial Value of Watchdog Timer                            | 65 |

|     | 17.3.  | Watchdog Timer H Count Source Selection Bit Operation      | 65 |

|     | 17.4.  | IDLE Mode Disable Bit                                      | 66 |

|     | 17.5.  | Watchdog timer control register (WDTCON)                   | 66 |

| 19. | FLASH  | I MEMORY                                                   | 67 |

|     | 19.1   | On chip program flash memory                               | 67 |

|     |        | 19.1.1 SFRAH, SFRAL(0F9h, 0F8h)                            | 67 |

|     |        | 18.1.1 SFRFD (0FAh)                                        | 67 |

|     |        | 18.1.2 SFRCN (0FBh)                                        | 67 |

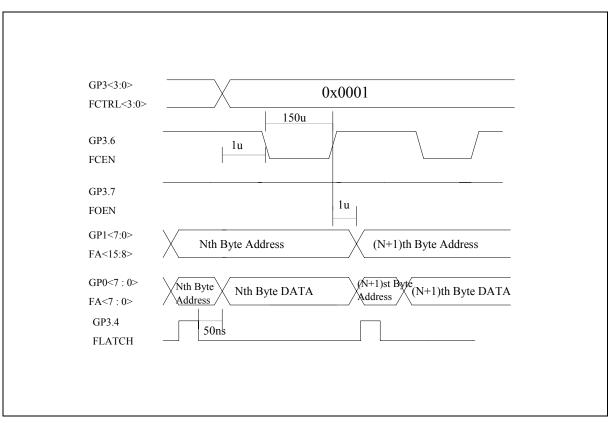

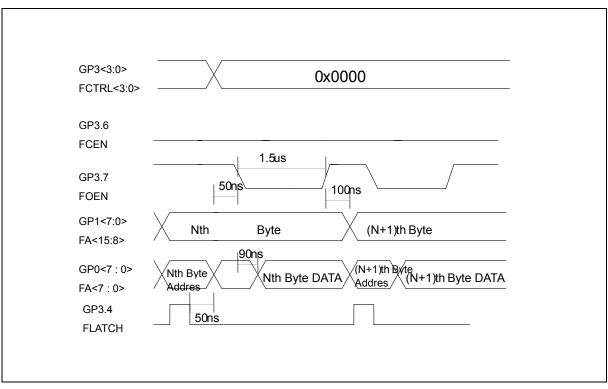

|     | 19.2   | External Programming Mode                                  | 67 |

| 20. | PS/2 D | DEVICE INTERFACE                                           | 70 |

|     | 20.1   | PS/2 Transmit and Receive DATA Registers (PS2DATA)         | 70 |

|     |        | 20.1.1 Transmit Register                                   | 70 |

|     |        | 20.1.2 Receive Register                                    | 70 |

|     | 20.2   | PS/2 Control Registers (PS2CON)                            | 71 |

|     | 20.3   | PS/2 Status Registers (PS2STS)                             | 72 |

|     | 20.4   | PS/2 Status_2 Registers (PS2STS_2)                         | 73 |

| 21. | SMBU   | S ADDRESS AND REGISTERS                                    | 74 |

|     | 21.1   | SMBus Host Status Register (HSR)                           | 74 |

|     | 21.2   | SMBus Host Control Register (HCR)                          | 75 |

|     | 21.3   | SMBus Host Read Byte Count Register (H_RBC)                | 76 |

|     | 21.4   | SMBus Host/Slave Data FIFO Register (DFIFO)                | 76 |

|     | 21.5   | SMBus Host-Slave Address Register (SADR)                   | 76 |

|     | 21.6   | SMBus Host/Slave Mode and FIFO Level Length Register (HMR) | 77 |

|     | 21.7   | SMBus Host/Slave FIFO Control Register (FCR)               | 77 |

|     | 21.8   | SMBus Host/Slave interrupt Control Register (ICR)          | 78 |

|     | 21.9   | SMBus Host/Slave interrupt Status Register (ISR)           | 79 |

|     | 21.10 | SMBus Host/Slave FIFO Status Register (FSR)                          | 80 |

|-----|-------|----------------------------------------------------------------------|----|

|     | 21.11 | SMBus User Defined Register (UDR)                                    | 80 |

|     | 21.12 | SMBus System Control Register (SCR)                                  | 80 |

|     | 21.13 | SMBus Test 0 Register (TST0)                                         | 81 |

|     | 21.14 | SMBus Test 1 Register (TST1)                                         | 81 |

| 22. | AUXIL | IARY SMBUS ADDRESS AND REGISTERS                                     | 82 |

|     | 22.1  | Auxiliary SMBus Host Status Register (AHSR)                          | 82 |

|     | 22.2  | Auxiliary SMBus Host Control Register (AHCR)                         | 83 |

|     | 22.3  | Auxiliary SMBus Host Read Byte Count Register (AH_RBC)               | 84 |

|     | 22.4  | Auxiliary SMBus Host/Slave Data FIFO Register (ADFIFO)               | 84 |

|     | 22.5  | Auxiliary SMBus Host-Slave Address Register (ASADR)                  | 84 |

|     | 22.6  | Auxiliary SMBus Host/Slave Mode and FIFO Level Length Register(AHMR) | 85 |

|     | 22.7  | Auxiliary SMBus Host/Slave FIFO Control Register (AFCR)              | 85 |

|     | 22.8  | Auxiliary SMBus Host/Slave interrupt Control Register (AICR)         | 86 |

|     | 22.9  | Auxiliary SMBus Host/Slave interrupt Status Register (AISR)          | 87 |

|     | 22.10 | Auxiliary SMBus Host/Slave FIFO Status Register (AFSR)               | 88 |

|     | 22.11 | Auxiliary SMBus User Defined Register (AUDR)                         | 88 |

|     | 22.12 | Auxiliary SMBus System Control Register (ASCR)                       | 88 |

|     | 22.13 | Auxiliary SMBus Test 0 Register (ATST0)                              | 89 |

|     | 22.14 | Auxiliary SMBus Test 1 Register (ATST1)                              | 89 |

| 23. | ELEC  | TRICAL CHARACTERISTICS                                               | 89 |

|     | 23.1  | Absolute Maximum Ratings                                             | 89 |

|     | 23.2  | DC Characteristics (V <sub>DD</sub> = 5V)                            | 90 |

|     | 23.3  | DC Characteristics (V <sub>DD</sub> = 3.3V)                          | 92 |

| 24. | ORDE  | RING INFORMATION                                                     | 94 |

| 25. | HOW   | TO READ THE TOP MARKING                                              | 94 |

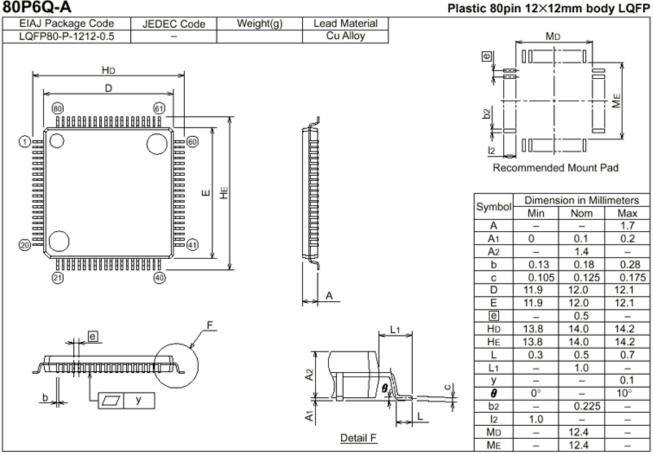

| 26. | PACK  | AGE DIMENSIONS                                                       | 95 |

## Flectronics Corp.

#### 1. GENERAL DESCRIPTION

The Winbond mobile keyboard and embedded controller W83L950D architecture consists of a Turbo-51 core logic controller and surrounded by various components, 2K+256 bytes of RAM, 40K on-chip MTP-ROM, ISA or LPC host interface, 9 general purpose I/O port with 13 external interrupt source, 4 timers, 2 serial port, 2 SMBus interface for master and slave, 3 PS2 port, two 8-bits and two 16-bits PWM channels, 2 D-A and 8 A-D converters.

#### 2. FEATURES

#### Pin out

• Pin-to-Pin compatible with Mitsubishi M3886 family (ISA mode)

#### **Core logic**

- Turbo 8052 microprocessor based

- 256 bytes internal RAM

- 40K bytes embedded programmable flash memory

- 2K bytes external SRAM

- Host interface -

- Software optional with ISA or LPC interface

- Primary programmable I/O address communication port in LPC mode

- Support either Parallel IRQ in ISA or SERIRQ in LPC interface

- Hardware Fast Gate A20 and KBRST support

- Port 92h support

#### SMBus

• Support 2 SMBus interface for master and slave.

#### Timers

- Support 4 Timer signal with 3 pre-scalars.

- Timer 1 and 2 shard the same pre-scalar and are free-running only.

- Timer X and Y have individual pre-scalar and support up to 4 control modes, free running, pulse output, event counter and pulse width measurement.

#### PWM

- Support 4 PWM channels

- PWM 0 and 1 (channel 00/01 or 10/11) are 14bits and worked at fixed frequency 15.6 KHz

- PWM 2 and 3 are16 bits and programmable frequency from 122 Hz to 16 MHz.

#### ADC

• Support 2 DA output and 8 AD input

- DA 0, 1 are 8bits resolution

- AD 0-7 are firmware programmable optional with 10 or 8 bits resolution.

#### PS2

- Support 3 hardware PS2 channels

- Optional PS2 clock inhibit by hardware or firmware.

#### GPIO

• Support 72 GPIO pins totally, and all are bit-addressable to facility firmware coding.

#### FLASH

• Support External On-Board Flash via Matrix interface (GP0, 1, 3)

#### ACPI

- Support ACPI appliance

- Secondary programmable I/O address communication port in LPC mode

#### Package

• 80-pin LQFP

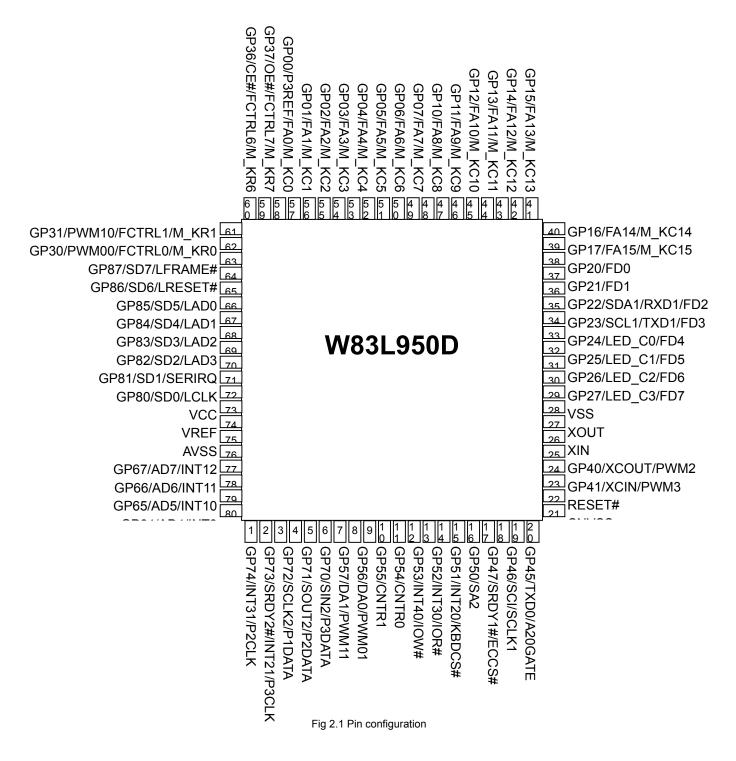

#### 3. PIN CONFIGURATION

#### 4. PIN DESCRIPTION

| TYPE       | DESCRIPTION                                                                             |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| I/O12t     | TTL level bi-directional pin with 12 mA source-sink capability                          |  |  |  |  |  |

| I/O24c     | TTL level output pin with 12 mA source-sink capability and CMOS level input             |  |  |  |  |  |

| I/O12c     | TTL level output pin with 12 mA source-sink capability and CMOS level input             |  |  |  |  |  |

| I/OD12c    | TTL level open drain output pin with 12 mA sink capability and CMOS level input.        |  |  |  |  |  |

| I/O24c(t)  | TTL level output pin with 24mA source-sink capability and CMOS or TTL level input.      |  |  |  |  |  |

| I/OD12c(t) | TTL level open drain output pin with 12 mA sink capability and CMOS or TTL level input. |  |  |  |  |  |

| INc        | CMOS level input pin                                                                    |  |  |  |  |  |

| INs        | Schmitt-trigger input pin                                                               |  |  |  |  |  |

| INt        | TTL level input pin                                                                     |  |  |  |  |  |

| INcu       | CMOS level input pin with internal pull up resistor                                     |  |  |  |  |  |

| INa        | Analog input                                                                            |  |  |  |  |  |

| O12        | TTL level output pin with 12 m A source-sink capability                                 |  |  |  |  |  |

| OD12       | Open-drain output pin with 12 m A sink capability                                       |  |  |  |  |  |

| Oa         | Analog output                                                                           |  |  |  |  |  |

#### 3.1. Basic KBC Function Signals

| SYMBOL                              | PIN   | I/O                                             | FUNCTION                                                                                                                                                                                                                                                                                     |

|-------------------------------------|-------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     |       | I/O24c(t)                                       | These signal lines communicate data information over ISA bus to the host. (ISA only)                                                                                                                                                                                                         |

| SD [7:0]<br>GPIO 8 [7:0]<br>LPC I/F | 63-70 | I/O24c<br>INc<br>INc<br>I/O24c<br>I/O24c<br>Inc | General purpose IO port.<br>Pin63: LFRAME#,<br>Pin64: LRESET#.<br>Pin [68:65]: LAD [3:0],<br>Pin69: SERIRQ<br>Pin70: LCLK<br>These signal lines communicate data information through<br>LPC bus to the host.<br>Bus Type Selection please refer to 10 DBBCON register.<br>(No H/W strapping) |

| SA2                                 | 17    | INt                                             | The signal line communicates address information over ISA bus to the host. (ISA only)                                                                                                                                                                                                        |

| GPIO 50                             |       | I/O12c                                          | General purpose IO port.                                                                                                                                                                                                                                                                     |

| IOR#                                |       | INt                                             | The signal line communicates control information over ISA bus to the host. (ISA only)                                                                                                                                                                                                        |

| GPIO 52                             | 15    | I/O12c                                          | General purpose IO port.                                                                                                                                                                                                                                                                     |

| INT30                               |       | INs                                             | External interrupt input.                                                                                                                                                                                                                                                                    |

| IOW#                                |       | INt                                             | The signal line communicates control information over ISA bus to the host. (ISA only)                                                                                                                                                                                                        |

| GPIO 53                             | 14    | I/O12c                                          | General purpose IO port.                                                                                                                                                                                                                                                                     |

| INT40                               |       | INs                                             | External interrupt input.                                                                                                                                                                                                                                                                    |

| IRQ1                                |       | O12                                             | ISA IRQ1 Output. (ISA only)                                                                                                                                                                                                                                                                  |

| GPIO 42                             | 23    | I/O12c(t)                                       | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                                                                                                                                                                                                                            |

| INT0                                |       | INs                                             | External interrupt input                                                                                                                                                                                                                                                                     |

| SYMBOL  | PIN | I/O       | FUNCTION                                                                                   |

|---------|-----|-----------|--------------------------------------------------------------------------------------------|

| IRQ12   |     | O12       | ISA IRQ12 Output. (ISA only)                                                               |

| GPIO 43 | 22  | I/O12c(t) | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                          |

| INT1    |     | INs       | External interrupt input.                                                                  |

| SCI     |     | O12       | SCI Output. (ISA only)                                                                     |

| GPIO 46 | 19  | I/O12c(t) | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                          |

| SCLK1   |     | INc       | Serial I/O 1 function I/O                                                                  |

| KBDCS#  | 16  | Int       | Decode the address 60h and 64h to input chip selected signal. (ISA only)                   |

| GPIO 51 |     | I/012c    | General purpose IO port.                                                                   |

| INT20   |     | INs       | External interrupt input.                                                                  |

| ECCS#   |     | INt       | Decode the address 62h and 66h to input chip selected signal. (ISA only)                   |

| GPIO 47 | 18  | I/O12c(t) | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                          |

| SRDY1#  |     | INc       | Serial I/O 1 function I/O                                                                  |

| A20GATE |     | O12       | Gate A20 output. This pin is controlled by AKBCCTRL. (External pull-up circuit is needed.) |

| GPIO 45 | 20  | I/O12c(t) | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                          |

| TxD0    |     | O12       | Serial I/O1 interface                                                                      |

| KBRST#  |     | O12       | CPU reset output. It should be connected to Chipset. This pin is high after KBC reset.     |

| GPIO 44 | 21  | I/O12c(t) | (External pull-up circuit is needed.)                                                      |

|         |     |           | General purpose IO port.<br>(Input level selected by PCTRL2_bit0)                          |

| RxD0    |     | INc       | Serial I/O1 interface.                                                                     |

| SYMBOL                                       | PIN                                 | I/O                                | FUNCTION                                                                                                                          |

|----------------------------------------------|-------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| P1CLK                                        |                                     | INs                                | PS2 Port 1 Clock.                                                                                                                 |

| GPIO 75                                      | 4                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| INT41                                        |                                     | INs                                | External interrupt input                                                                                                          |

| P2CLK                                        |                                     | INs                                | PS2 Port 2 Clock.                                                                                                                 |

| GPIO 74                                      | 5                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| INT31                                        |                                     | INs                                | External interrupt input.                                                                                                         |

| P3CLK                                        |                                     | INs                                | PS2 Port 3 Clock.                                                                                                                 |

| GPIO 73                                      | 6                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| INT21                                        |                                     | INs                                | External interrupt input.                                                                                                         |

| SRDY2#                                       |                                     | INs                                | SERIAL I/O2 INTERFACE                                                                                                             |

| P1DATA                                       |                                     | INs                                | PS2 Port 1 Data.                                                                                                                  |

| GPIO 72                                      | 7                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| SCLK2                                        |                                     | INs                                | SERIAL I/O2 INTERFACE                                                                                                             |

| P2DATA                                       |                                     | INs                                | PS2 Port 2 Data.                                                                                                                  |

| GPIO 71                                      | 8                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| SOUT2                                        |                                     | OD12                               | Serial I/O2 interface.                                                                                                            |

| P3DATA                                       |                                     | INs                                | PS2 Port 3 Data.                                                                                                                  |

| GPIO 70                                      | 9                                   | I/OD12 <sub>C(t)</sub>             | General purpose IO port.<br>(Input level selected by PCTRL2_bit1)                                                                 |

| SIN2                                         |                                     | INs                                | Serial I/O2 interface.                                                                                                            |

| LED_C [3:0]                                  | 31-34                               | O12                                | LED control signal (include Num Lock, Scroll Lock, Caps Lock and Katakana Lock).                                                  |

| GPIO 2[7:4]                                  |                                     | I/O12c                             | General purpose IO port.                                                                                                          |

| GPIO 2[3:0]<br>SCL 1<br>SDA1<br>TxD1<br>RxD1 | 35-38<br>35<br>36<br>35<br>35<br>36 | I/O12c<br>INs<br>INs<br>O12<br>INc | General purpose IO port.<br>SMBus 1 CLOCK interface<br>SMBus 1 DATA interface<br>SERIAL I/O 1 interface<br>SERIAL I/O 1 interface |

### 3.2. Specific Function Signals

| SYMBOL      | PIN     | I/O        | FUNCTION                              |  |  |  |  |

|-------------|---------|------------|---------------------------------------|--|--|--|--|

| DA [1:0]    |         | Oa         | D-A converter output signals.         |  |  |  |  |

| PWM11       | 10,11   | O12        | PWM output signals.                   |  |  |  |  |

| PWM01       | 10,11   | O12        |                                       |  |  |  |  |

| GPIO 5[7,6] |         | I/O12c     | General purpose IO port.              |  |  |  |  |

| AD [7:0]    |         | INa        | A-D converter output signal.          |  |  |  |  |

| GPIO 6[7:0] | 1,74-80 | I/O12c     | General purpose IO port.              |  |  |  |  |

| INT5– INT12 |         | INs        | External interrupt input.             |  |  |  |  |

| SCL 0       |         | I/OD12c    | SMBus 0 CLOCK signal.                 |  |  |  |  |

| GPIO77      | 2       | I/OD12c(t) | General purpose IO port.              |  |  |  |  |

| GFIOT       |         | 1/OD120(t) | (Input level selected by PCTRL2_bit1) |  |  |  |  |

| SDA 0       |         | I/OD12c    | SMBus 0 DATA signal.                  |  |  |  |  |

| GPIO76      | 3       | I/OD12c(t) | General purpose IO port.              |  |  |  |  |

| GFIO70      |         | 1/OD120(t) | (Input level selected by PCTRL2_bit1) |  |  |  |  |

| PWM3        |         | O12        | PWM interface signal.                 |  |  |  |  |

| Xcin        | 26      | INa        | Sub-clock gen.                        |  |  |  |  |

| GPIO 41     |         | I/O12c     | GENERAL PURPOSE IO PORT.              |  |  |  |  |

| PWM2        |         | 012        | PWM interface signal.                 |  |  |  |  |

| Xcout       | 27      | Oa         | Sub-clock gen.                        |  |  |  |  |

| GPIO 40     |         | I/O12c     | General purpose IO port.              |  |  |  |  |

| SYMBOL                                                     | PIN         | I/O                                 | FUNCTION                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------------------------------------------------------|-------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CNTR 1                                                     | 12          | INs                                 | Timer Y signal.                                                                                                                                                                                                                                     |  |  |  |  |  |

| GPIO 55                                                    | 12          | I/O12c                              | General purpose IO port.                                                                                                                                                                                                                            |  |  |  |  |  |

| CNTR 0                                                     | 13          | INs                                 | Timer X signal.                                                                                                                                                                                                                                     |  |  |  |  |  |

| GPIO 54                                                    | 15          | I/O12c                              | General purpose IO port.                                                                                                                                                                                                                            |  |  |  |  |  |

| M_KC [7:0]<br>FA [7:0]<br>GPIO 0[7:0]<br>P3ref             | 47-54<br>54 | O12<br>INc<br>I/O12c<br>INa         | <ul><li>24 pins Matrix KB Row signals.</li><li>Address signals of External Memory interface.</li><li>General purpose IO port.</li><li>Comparator reference power source input signal.</li></ul>                                                     |  |  |  |  |  |

| M_KC [15:8]                                                |             | O12                                 | 24 pins Matrix KB Row signals.                                                                                                                                                                                                                      |  |  |  |  |  |

| FA [15:8]                                                  | 39-46       | INc                                 | Address signals of External Memory interface.                                                                                                                                                                                                       |  |  |  |  |  |

| GPIO 1[7:0]                                                |             | I/O12c                              | General purpose IO port.                                                                                                                                                                                                                            |  |  |  |  |  |

| M_KR [1:0]<br>PWM10,<br>PWM00<br>GPIO 3[1:0]<br>FCTRL[1:0] | 61,62       | INcu<br>O12<br>O12<br>I/O12c<br>INc | <ul> <li>24 pins Matrix KB Column signals.</li> <li>PWM output signals.</li> <li>PWM output signals.</li> <li>General purpose IO port.</li> <li>External flash program mode control signal (*Internal pull-up controlled by PCTRL1_BIT4)</li> </ul> |  |  |  |  |  |

| M_KR 2<br>GPIO 32<br>FCTRL[2]                              | 60          | INcu<br>I/O12c<br>INc               | 24 pins Matrix KB Column signals.<br>General purpose IO port.<br>External flash program mode control signal<br>(*Internal pull-up controlled by PCTRL1_BIT4)                                                                                        |  |  |  |  |  |

| M_KR 3<br>GPIO 33<br>FCTRL[3]                              | 59          | INcu<br>I/O12c<br>INc               | 24 pins Matrix KB Column signals.<br>General purpose IO port.<br>External flash mode control signal<br>(*Internal pull-up controlled by PCTRL1_BIT4)                                                                                                |  |  |  |  |  |

| M_KR 4<br>GPIO 34                                          | 58          | INcu<br>I/O12c                      | 24 pins Matrix KB Column signals.<br>General purpose IO port.<br>(*Internal pull-up controlled by PCTRL1_BIT5)                                                                                                                                      |  |  |  |  |  |

| SYMBOL                   | PIN   | I/O                          | FUNCTION                                                                                                                                                                                          |  |  |  |  |  |

|--------------------------|-------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| M_KR 5<br>GPIO 35        | 57    | INcu<br>I/O12c               | 24 pins Matrix KB Column signals.<br>General purpose IO port.<br>(*Internal pull-up controlled by PCTRL1_BIT5)                                                                                    |  |  |  |  |  |

| M_KR 6<br>GPIO 36<br>CE# | 56    | INcu<br>I/O12c<br>INc        | <ul><li>24 pins Matrix KB Column signals.</li><li>General purpose IO port.</li><li>Chip enable signals of external flash program mode<br/>(*Internal pull-up controlled by PCTRL1 BIT5)</li></ul> |  |  |  |  |  |

| M_KR 7<br>GPIO37<br>OE#  | 55    | INcu General purpose IO port |                                                                                                                                                                                                   |  |  |  |  |  |

| GPIO 2[7:0]<br>FD [7:0]  | 31-38 | I/O12c                       | General purpose IO port.<br>Data signals of External flash program mode<br>interface.                                                                                                             |  |  |  |  |  |

#### 3.3. Power, Rest and Clock Signals

| SYMBOL | PIN | I/O    | FUNCTION                                                                                                  |  |  |  |  |

|--------|-----|--------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Vcc    | 71  |        | +5V/+3.3∨                                                                                                 |  |  |  |  |

| Vref   | 72  |        | Reference voltage of AD/DA (Less than Vcc)                                                                |  |  |  |  |

| Vss    | 30  |        | GND                                                                                                       |  |  |  |  |

| Avss   | 73  |        | AGND                                                                                                      |  |  |  |  |

| CNvss  | 24  | I/O12c | Normal connects to VSS.<br>If this pin is connects to Vcc, the chip is in external<br>flash program mode. |  |  |  |  |

| Reset# | 25  | I/O12c | Chip reset signal input for active low, at least 8 PCICLK wide.                                           |  |  |  |  |

| Xin    | 28  | INa    | Clock input (8MHz)                                                                                        |  |  |  |  |

| Xout   | 29  | Oa     | Clock output                                                                                              |  |  |  |  |

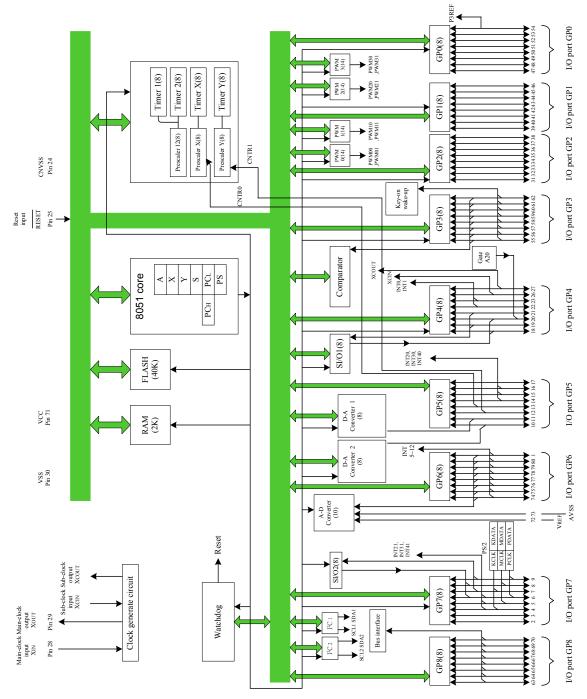

#### 5. SYSTEM BLOCK DIAGRAM

Fig 4.1 System Block Diagram

- 11 -

#### **Winbond** Electronics Corp.

#### 6. MICRO COMPUTER ARCHITECTURE

The Turbo-51 core logic of Winbond Keyboard controller is based on the industry standard 8032 device. It is built around an 8-bit ALU that uses internal registers for temporary storage and control of the peripheral devices. It can execute the standard 8032 instruction set.

The Winbond Keyboard controller separates the memory into two sections, the Program Memory and the Data Memory. The Program Memory, MTP-ROM, is used to store the instruction op-codes, and the Data Memory, RAM, is used to store data and now is consists of a 256 bytes scratch pad RAM and a 2K bytes external SRAM. The external SRAM can be accessed by either MOVX instruction in generally or to be a scratched ultra ROM for special purpose.

The brief descriptions of the internal blocks are shown as follows.

#### 6.1 ALU

The ALU is the heart of the Winbond Keyboard controller. It is responsible for the arithmetic and logical functions. It is also used in decision-making, in case of jump instructions, and is also used in calculating jump addresses. The user cannot directly use the ALU, but the Instruction Decoder reads the op-codes, decodes it, and sequences the data through the ALU and its associated registers to generate the required result. The ALU mainly uses the ACC that is a Special Function Register (SFR) on the chip. Another SFR, namely B register is also used in Multiply and Divide instructions. The ALU generates several status signals that are stored in the Program Status Word register (PSW).

#### 6.2 Accumulator

The Accumulator (ACC) is the primary register used in arithmetic, logical and data transfer operations in the Winbond Keyboard controller. Since the Accumulator is directly accessible by the CPU, most of the high-speed instructions make use of the ACC as one argument.

#### 6.3 B Register

This is an 8-bit register that is used as the second argument in the MUL and DIV instructions. For all other instructions it can be used simply as a general-purpose register.

#### 6.4 Program Status Word (PSW)

This is an 8-bit SFR, which is used to store the status bits of the ALU. It holds the Carry flag, the Auxiliary Carry flag, General-purpose flags, the Register Bank Select, the Overflow flag, and the Parity flag.

#### 6.5 Data Pointers and Selection

The Data Pointers are used to do 16 bits addressing that can transfer data to and from either external Data Memory or on-chip MTP-ROM. The Winbond Keyboard controller has provided two separate Data Pointers, DPTR (DPH, DPL) and DPTR1 (DPH1, DPL1), and a Data Pointers Selection register, DPS, to select which DPTR should be utilized. The user can switch either of them with minimum software overhead, and thereby greatly increasing the system throughput by setting DPS in sequentially.

#### 6.6 Stack Pointer

The Winbond Keyboard controller has an 8-bit Stack Pointer which points to the top of the Stack. This stack resides in the Scratch Pad RAM in the Winbond Keyboard controller. Hence the size of the stack is limited by the size of this RAM.

#### **Winbond** Electronics Corp.

#### 6.7 Program Memory

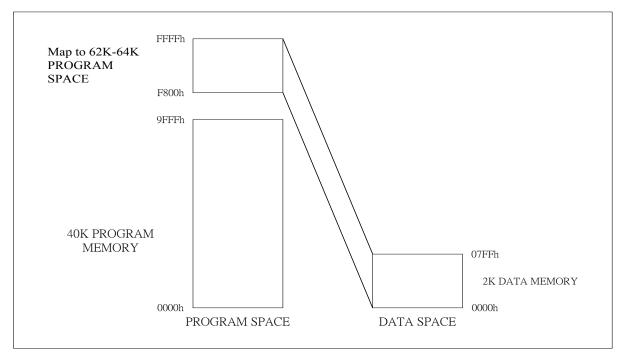

The Winbond Keyboard controller includes one 40K bytes of main MTP-ROM for application program (APROM). This reality on-chip MTP-ROM begins at address 0000h and continuous through 0AFFFh. After reset, the micro-controller executes the new application program in the main MTP-APROM. The addressing of Program Memory can up to 64K bytes long.

#### 6.8 Scratch Pad RAM

The Winbond Keyboard controller has a 256 bytes on-chip scratch pad RAM which architecture is almost same as industry standard microprocessor 8052. This RAM begins at address 00h to 0FFh, can be used for temporary storage during program execution.

From 00h to 1Fh, is divided into 4 Banks, which is used to provide 4 Register-sets, each bank has individual R0 to R7. Only one Register-set is accessible at a time, which decided by the bit 4,3 of PSW, RS1, RS0.

From 20h to 2Fh, is either a general Byte-addressable memory area or a specific purpose Bit-addressable memory area. No control bit needed here. If it is accessed by a Bit-addressable instruction, the range of bit address is from 00h to 7Fh in linearly to any bit-operational instruction.

From 30h to 7Fh, is a general memory area, which can be accessed by direct or indirect addressing.

From 80h to 0FFh is a special memory area, which can be accessed by only indirect addressing. At the same location which also addressed from 80h to FFh, there is a Special Function Registers (SFRs) Area, can be accessed by only direct addressing. This difference is to provide two physical memory entities coexisted at the same address without contention occurred.

For more detail please refer to below figure.

| FFh                     |                 |           |           |           |                 |                 |           |  |  |

|-------------------------|-----------------|-----------|-----------|-----------|-----------------|-----------------|-----------|--|--|

|                         |                 | I         | ndirect   | RAM       |                 |                 |           |  |  |

| 80h                     |                 |           |           |           |                 |                 |           |  |  |

| 7Fh                     |                 |           |           |           |                 |                 |           |  |  |

|                         |                 |           | Direct    | RAM       |                 |                 |           |  |  |

| 30h                     |                 |           |           |           |                 |                 | =0        |  |  |

| 2Fh 7F                  | <u>7E</u>       | 7D        | 7C        | 7B        | 7A<br>70        | 79              | 78        |  |  |

| 2Eh 77                  | 76              | 75        | 74        | 73        | 72              | 71              | 70        |  |  |

| 2Dh <u>6F</u>           | <u>6E</u>       | 6D        | 6C        | 6B        | 6A              | 69              | 68        |  |  |

| 2Ch <u>67</u>           | 66              | <u>65</u> | <u>64</u> | <u>63</u> | 62              | 61              | <u>60</u> |  |  |

| 2Bh <u>5F</u><br>2Ah 57 | <u>5E</u>       | 5D        | 5C        | 5B        | <u>5A</u><br>52 | <u>59</u><br>51 | 58        |  |  |

| 29h 4F                  | <u>56</u><br>4E | 55<br>4D  | 54<br>4C  | 53<br>4B  | <u>52</u><br>4A | 49              | 50        |  |  |

| 2911 4F<br>28h 47       | <u>4⊏</u><br>46 | 40        | 40        | 4D<br>43  | 4A<br>42        | 49              | 48<br>40  |  |  |

| 27h 3F                  | 3E              | 3D        | 3C        | 3B        | 42<br>3A        | 39              | 38        |  |  |

| 26h 37                  | 36              | 35        | 34        | 33        | 32              | 31              | 30        |  |  |

| 25h 2F                  | 2E              | 2D        | 2C        | 2B        | 2A              | 29              | 28        |  |  |

| 24h 27                  | 26              | 25        | 24        | 23        | 22              | 21              | 20        |  |  |

| 23h 1F                  | 1E              | 1D        | 1C        | 1B        | 1A              | 19              | 18        |  |  |

| 22h 17                  | 16              | 15        | 14        | 13        | 12              | 11              | 10        |  |  |

| 21h 0F                  | 0E              | 0D        | 00        | 0B        | 0A              | 09              | 08        |  |  |

| 20h 07                  | 06              | 05        | 04        | 03        | 02              | 01              | 00        |  |  |

| 1Fh                     | -               | -         | _         |           |                 |                 |           |  |  |

| 18h                     |                 |           | Ban       | k 3       |                 |                 |           |  |  |

| 17h                     |                 |           | Dam       | . 0       |                 |                 |           |  |  |

| 10h                     |                 |           | Ban       | K 2       |                 |                 |           |  |  |

| 0Fh                     |                 |           | Ban       | 61        |                 |                 |           |  |  |

| 08h                     |                 |           | Dan       | K I       |                 |                 |           |  |  |

| 07h<br>00h              |                 |           | Ban       | k 0       |                 |                 |           |  |  |

Fig.5.1 Scratch Pad RAM Map

#### **Winbond** Electronics Corp.

#### 6.9 SFR Bit Addressable Location

Some of the SFRs are also bit addressable. The instruction decoder is able to distinguish a bit access from a byte access by the type of the instruction itself. The following table lists the bit addressable SFR only.

As the below table shown, it is different with traditional industry standard micro-processor 8052, only register ACC, B and PSW are still populated in this bit-addressable table, the others were removed and instead of nine GPIO registers. This may provide a quickly response to firmware's GPIO operation.

The discontinued gaps of the SFR bit addressable location, 0C8h or 0D8h etc, are not available and undefined. Access to them may result in unknown error.

| FFH   | []    |       |       |       |       |       | []    |       | ı _   |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| FOH   | F7    | F6    | F5    | F4    | F3    | F2    | F1    | FO    | В     |

| 1 011 |       |       |       |       |       |       |       |       |       |

| EOH   | E7    | E6    | E5    | E4    | E3    | E2    | E1    | EO    | ACC   |

| LUII  | СҮ    | AC    | FO    | RS1   | RS0   | OV    |       | Р     |       |

| D0H   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    | PSW   |

| Dom   | GP8.7 | GP8.6 | GP8.5 | GP8.4 | GP8.3 | GP8.2 | GP8.1 | GP8.0 |       |

| COH   | C7    | C6    | C5    | C4    | C3    | C2    | C1    | C0    | GP8   |

| COII  | GP7.7 | GP7.6 | GP7.5 | GP7.4 | GP7.3 | GP7.2 | GP7.1 | GP7.0 |       |

| B8H   | BF    | BE    | BD    | BC    | BB    | BA    | B9    | B8    | GP7   |

|       | GP6.7 | GP6.6 | GP6.5 | GP6.4 | GP6.3 | GP6.2 | GP6.1 | GP6.0 |       |

| BOH   | B7    | B6    | B5    | B4    | B3    | B2    | B1    | B0    | GP6   |

| DUII  | GP5.7 | GP5.6 | GP5.5 | GP5.4 | GP5.3 | GP5.2 | GP5.1 | GP5.0 |       |

| A8H   | AF    |       | AD    | AC    | AB    | AA    | A9    | A8    | GP5   |

| 11011 | GP4.7 | GP4.6 | GP4.5 | GP4.4 | GP4.3 | GP4.2 | GP4.1 | GP4.0 |       |

| A0H   | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    | GP4   |

| 11011 | GP3.7 | GP3.6 | GP3.5 | GP3.4 | GP3.3 | GP3.2 | GP3.1 | GP3.0 |       |

| 98H   | 9F    | 9E    | 9D    | 9C    | 9B    | 9A    | 99    | 98    | GP3   |

| 7011  | GP2.7 | GP2.6 | GP2.5 | GP2.4 | GP2.3 | GP2.2 | GP2.1 | GP2.0 |       |

| 90H   | 97    | 96    | 95    | 94    | 93    | 92    | 91    | 90    | GP2   |

| 9011  | GP1.7 | GP1.6 | GP1.5 | GP1.4 | GP1.3 | GP1.2 | GP1.1 | GP1.0 |       |

| 88H   | 8F    | 8E    | 8D    | 8C    | 8B    | 8A    | 89    | 88    | GP1   |

| 001   | GP0.7 | GP0.6 | GP0.5 | GP0.4 | GP0.3 | GP0.2 | GP0.1 | GP0.0 |       |

| 80H   | 87    | 86    | 85    | 84    | 83    | 82    | 81    | 80    | ] GP0 |

#### Fig 5.2. Bit Address Location

#### 6.10 External SRAM

The Winbond Keyboard controller has a 2K bytes external SRAM and is read/write accessible. The SRAM begins at address 0000h to 07FFh, is accessed via the MOVX instruction in generally. There is no conflict or overlap among the 256bytes scratch pad RAM and the 2K bytes external SRAM as they use different addressing modes and separate instructions. The addressing of external SRAM can up to 64K bytes long.

#### 6.11 Scratched ULTRA ROM

The external SRAM can be accessed by either general external memory instruction, i.e. MOVX, or to be a scratch ROM for special purpose which achieved by re-mapping this area to a part of logical Program Memory, addressed on 0F800h to 0FFFFh (62K to 64K), unlike the industry standard 8052 derivatives. No control switch is needed here. In other words, using MOVX to transfer data to and jump to it by an absolutely JUMP instruction to accomplish this operation. This feature can increase the system throughput and is convenient to perform On-Chip internal flash task.

Fig.5.3 Memory Map

#### 7. SPECIAL FUNCTION REGISTER

#### 7.1 Standard SFR Address and Registers

| F8h | SFRAL    | SFRAH   | SFRFD   | SFRCN     | DEVICE ID | DEVICE<br>REV. |                  |                              |

|-----|----------|---------|---------|-----------|-----------|----------------|------------------|------------------------------|

| F0h | +B       |         |         |           |           |                |                  |                              |

| E8h |          |         |         |           |           |                |                  |                              |

| E0h | +ACC     |         | ADCON   | AD0       | AD1       | DA0            | DA1              | CMPD                         |

| D8h | DBB0     | DBBSTS0 | DBBCON  | DBB1      | DBBSTS1   |                |                  |                              |

| D0h | +PSW     |         |         |           | PWM0H     | PWM0L          | PWM1H            | PWM1L                        |

| C8h | TB/RB    | SIO1STS | SIO1CON | UARTCON   | BRG       | SIO2CON        | WDTCON           | SIO2                         |

| C0h | IREQ     | IREQ1   | IREQ2   |           | INTSEL1   | INTSET2        | KBCTR            | CHIPSTS                      |

| B8h | IP       | IE1     | IP1     | IE2       | IP2       | IT1            | IT2              |                              |

| B0h | PRE12    | T1      | T2      | ТМ        | PREX      | ТХ             | PREY             | TY                           |

| A8h | IE       | I2CISR  | I2CFSR  | I2CUDR    | I2CSCR    | I2CTST0        | I2CTST1          | <u>(TEST</u><br><u>MODE)</u> |

| A0h | I2CHSR   | I2CHCR  | I2CRBC  | I2C DFIFO | I2C SADR  | I2CHMR         | I2CFCR           | I2CICR                       |

| 98h | GP8      | GP8D    | PCTRL1  | PCTRL2    | PCTRL3    | CLKCTRL        | Advance<br>index | Advance<br>data              |

| 90h | GP4      | GP4D    | GP5     | GP5D      | GP6       | GP6D           | GP7              | GP7D                         |

| 88h | GP0      | GP0D    | GP1     | GP1D      | GP2       | GP2D           | GP3              | GP3D                         |

| 80h | CHIPCTRL | SP      | DPL     | DPH       | DPL1      | DPH1           | DPS              | PCON                         |

A register prefixed a "+" sign means it is a bit addressable register. Note that the SFR address which involved x0h or x8h, is no longer to be the bit-addressable register.

The TEST MODE register is an internal purpose register; the user should not access it.

Any gaps of SFR are not defined in Winbond keyboard controller, access them may result in unknown problem.

#### **Winbond** Electronics Corp.

#### 7.2 Advanced SFR Address and Registers

The Winbond keyboard controller defined another Advanced SFR area to expand the hardware control registers without memory-mapped register. There are two registers, [Advance Index] and [Advance Data], can be used to addressing this Advanced SFR register space. These two registers are located at 09Eh and 09Fh of the Standard SFR register area.

The addressing method is very similar with people well known Super I/O device. For example, if we wish set SIRQ2 to 55h, set [Advance index] to 01h, and then set [Advance data] to 055h.

| 78h |           |          |          |            |           |          |          |         |

|-----|-----------|----------|----------|------------|-----------|----------|----------|---------|

| 70h |           |          |          |            |           |          |          |         |

| 68h |           |          |          |            |           |          |          |         |

| 60h |           |          |          |            |           |          |          |         |

| 58h |           |          |          |            |           |          |          |         |

| 50h |           |          |          |            |           |          |          |         |

| 48h |           |          |          |            |           |          |          |         |

| 40h |           |          |          |            |           |          |          |         |

| 38h |           |          |          |            |           |          |          |         |

| 30h | AI2CISR   | AI2CFSR  | AI2CUDR  | AI2CSCR    | AI2CTST0  | AI2CTST1 |          |         |

| 28h | AI2CHSR   | AI2CHCR  | AI2CRBC  | AI2C DFIFO | AI2C SADR | AI2CHMR  | AI2CFCR  | AI2CICR |

| 20h | PWM2PL    | PWM2PH   | PWM2HSL  | PWM2HSH    | PWM3PL    | PWM2PH   | PWM2HSL  | PWM2HSH |

| 18h | P3PS2DATA | P3PS2CON | P3PS2STS | P3S2STS_2  | APWMCON   |          |          |         |

| 10h | P1PS2DATA | P1PS2CON | P1PS2STS |            | P2PS2DATA | P2PS2CON | P2PS2STS |         |

| 08h | AKBCCTRL  |          |          |            |           |          |          |         |

| 00h | SIRQ1     | SIRQ2    | ADD1L    | ADD1H      | ADD2L     | ADD2H    |          | ADDCON  |

#### 8. 8051 AND BASIC CONTROL REGISTER

#### 8.1 Stack Pointer

| Bit: | 7         | 6    | 5    | 4    | 3           | 2    | 1    | 0    |

|------|-----------|------|------|------|-------------|------|------|------|

|      | SP.7      | SP.6 | SP.5 | SP.4 | SP.3        | SP.2 | SP.1 | SP.0 |

|      | Mnemonic: | SP   |      | A    | ddress: 81h |      |      |      |

The Stack Pointer stores the Scratch-pad RAM address where the stack begins. In other words it always points to the top of the stack.

#### 8.2 Data Pointer Low

| Bit: | 7         | 6     | 5     | 4     | 3           | 2     | 1     | 0     |

|------|-----------|-------|-------|-------|-------------|-------|-------|-------|

|      | DPL.7     | DPL.6 | DPL.5 | DPL.4 | DPL.3       | DPL.2 | DPL.1 | DPL.0 |

|      | Mnemonic: | DPL   |       | A     | ddress: 82h |       |       |       |

This is the low byte of the standard 8032 16-bit data pointer.

#### 8.3 Data Pointer High

| Bit: | 7         | 6     | 5     | 4     | 3       | 2      | 1     | 0     |

|------|-----------|-------|-------|-------|---------|--------|-------|-------|

|      | DPH.7     | DPH.6 | DPH.5 | DPH.4 | DPH.3   | DPH.2  | DPH.1 | DPH.0 |

|      | Mnemonic: | DPH   |       |       | Address | s: 83h |       |       |

Mnemonic: DPH Add This is the high byte of the standard 8032 16-bit data pointer.

#### 8.4 Data Pointer Low1

| Bit: | 7      | 6          | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|------------|--------|--------|--------|--------|--------|--------|

|      | DPL1.7 | DPL1.6     | DPL1.5 | DPL1.4 | DPL1.3 | DPL1.2 | DPL1.1 | DPL1.0 |

| I    | Mne    | monic: DPL | 1      |        | Ad     |        |        |        |

This is the low byte of the new additional 16-bit data pointer that has been added to the Winbond Keyboard controller. The user can switch between DPL, DPH and DPL1, DPH1 simply by setting DPS = 1. The instructions that use DPTR will now access DPL1 and DPH1 in place of DPL and DPH.

#### 8.5 Data Pointer High1

| Bit: | 7      | 6          | 5      | 4            | 3      | 2      | 1      | 0      |  |

|------|--------|------------|--------|--------------|--------|--------|--------|--------|--|

|      | DPH1.7 | DPH1.6     | DPH1.5 | DPH1.4       | DPH1.3 | DPH1.2 | DPH1.1 | DPH1.0 |  |

|      | Mnemo  | onic: DPH1 |        | Address: 85h |        |        |        |        |  |

This is the high byte of the new additional 16-bit data pointer that has been added to the Winbond Keyboard controller. The user can switch between DPL, DPH and DPL1, DPH1 simply by setting DPS = 1. The instructions that use DPTR will now access DPL1 and DPH1 in place of DPL and DPH.

#### 8.6 Data Pointer Select

| Bit: | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0     |

|------|-----------|-----|---|---|---|---|---|-------|

|      | -         | -   | - | - | - | - | - | DPS.0 |

|      | Mnemonic: | DPS |   | A |   |   |   |       |

DPS.0 This bit is used to select the DPL, DPH pair or DPL1, DPH1 pair as the active Data Pointer, DPTR. When set to 1, DPL1, DPH1 will be selected, else DPL, DPH will be selected.

DPS.1-7 These bits are reserved but will read 0.

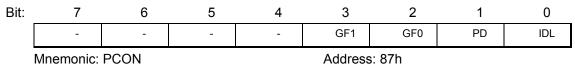

#### 8.7 **Power Control**

GF1-0 These two bits are general-purpose user flags.

PD Setting this bit causes the Winbond Keyboard controller to go into the POWERDOWN mode. In this mode all the clocks are stopped and program execution is frozen.

IDL Setting this bit causes the Winbond Keyboard controller to go into the IDLE mode. In this mode the clocks to the CPU is stopped, so program execution is frozen. But the clock to the serial, timer and interrupt blocks is not stopped, and these blocks continue operating unhindered. The chip can be wakening to operation mode by active interrupt.

#### 8.8 Program Status Word

| Bit: | 7         | 6   | 5  | 4   | 3        | 2  | 1  | 0 |

|------|-----------|-----|----|-----|----------|----|----|---|

|      | CY        | AC  | F0 | RS1 | RS0      | OV | F1 | Р |

|      | Mnemonic: | PSW |    |     | Address: |    |    |   |

CY Carry flag: Set for an arithmetic operation, which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations.

AC Auxiliary carry: Set when the previous operation resulted in a carry (during addition) or borrow (during subtraction) from the high order nibble.

F0 User flag 0: General-purpose flag that can be set or cleared by the user by software.

RS.1-0 Register bank selects bits:

| ess |

|-----|

| 7h  |

| Fh  |

| 7h  |

| Fh  |

|     |

OV Overflow flag: Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation or vice-versa.

F1User Flag 1: General-purpose flag that can be set or cleared by the user by software

P Parity flag: Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.

#### 8.9 Accumulator

| Bit: | 7         | 6     | 5     | 4     | 3           | 2     | 1     | 0     |

|------|-----------|-------|-------|-------|-------------|-------|-------|-------|

|      | ACC.7     | ACC.6 | ACC.5 | ACC.4 | ACC.3       | ACC.2 | ACC.1 | ACC.0 |

|      | Mnemonic: | ACC   |       | A     | ddress: E0h | 1     |       |       |

ACC.7-0 The A or ACC register is the standard 8032 accumulator

#### 8.10 B Register

| Bit: | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

|      | B.7 | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 |

|      |     |     |     |     |     |     |     | -   |

Mnemonic: B

Address: F0h

B.7-0 The B register is the standard 8032 accumulator

#### 8.11 CLK Controller Register

| Bit: | 7          | 6 | 5                      | 4 | 3 | 2        | 1     | 0       |

|------|------------|---|------------------------|---|---|----------|-------|---------|

|      | CLKSEL 1-0 |   | CLKSEL 1-0 FREQSEL 1-0 |   | - | -RING_EN | PLLEN | CLKSEL# |

Mnemonic: CLKCTRL

Address: 9Dh

Default: 0x40

#### B.7-6 PLL CLK OUT SELECT

- = 00: 4Mhz

- = 01: 8MHz

- = 10: Reserved

- = 11: Reserved

#### **B.5-4 PLL INPUT CLOCK SOURCE SELECT**

PLL CLOCK INPUT is directly connected to Xin and Xout pin.

- = 00: 8MHz

- = 01: 14.318MHz

- = 10: Reserved

- = 11: Reserved

- B.2 4MHZ RING OSC ENABLE

- = 0: 8051 CLK source is from Xin and Xout pin..

- = 1: 8051 CLK source is from 4MHZ RING OSC.

#### **B.1 PLL ENABLE**

- = 0: 8051 CLK source is from Xin and Xout pin. and bit 7-6 is disable.

- = 1: 8051 CLK source is from PLL block and bit 7-6 is enable.

- B.0 CLK SOURCE SELECT

- = 0: CLK source is Xin and Xout.

- = 1: CLK source is Xcin and Xcout.

#### 8.12 Chip Controller Register

| Bit: | 7         | 6        | 5     | 4     | 3       | 2      | 1                  | 0      |

|------|-----------|----------|-------|-------|---------|--------|--------------------|--------|

|      | -         | -        | PLLPD | ADCPD | -       | -      | -FAST PD<br>WAKEUP | RSTEN# |

|      | Mnemonic: | CHIPCTRL | _     |       | Address | s: 80h |                    |        |

B.7-6: Reserved

#### B.5: PLL POWER DOWN BIT (PLLPD)

- = 0: PLL NO POWER DOWN

- = 1: PLL POWER DOWN.

- B.4: ADC POWER DOWN BIT (ADCPD)

- = 0: ADC NO POWER DOWN

- = 1: ADC POWER DOWN.

- B.3-2: Reserved

- B.1: FAST 51 PD MODE WAKUP.

- =0: NORMAL WAKUP MODE (65535 SYSTEM CLOCK)

- =1: FAST WAKUP MODE (1 SYSTEM CLOCK).

- B.0: RSTEN#

- = 0: PIN RESET# ENABLE (default).

- The chip is reset when either Power On Reset or pin Reset#.

- = 1: PIN RESET# DISABLE

The chip is reset only when Power On Reset.

#### 8.13 Chip Status Register

| Bit: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|------|---|---|---|---|---|---|---|------|

|      | - | - | - | - | - | - | - | WTRF |

Mnemonic: CHIPCTRL

Address: C7h

B.7-1: Reserve

B.0: WTRF

Hardware will set this bit when the watchdog timer causes the reset. Software can clear it by writing a 0 to this bit.

#### 8.14 Device ID; Device REV Register

| Bit:        | 7          | 6      | 5         | 4     | 3    | 2          | 1        | 0 |

|-------------|------------|--------|-----------|-------|------|------------|----------|---|

| Device ID   | 0-         | 0      | 0         | 1     | 0    | 0          | 0        | 1 |

| Device Rev. | 0          | 0      | 0         | 0     | Rev. |            |          |   |

| Mr          | nemonic: [ | DEVICE | ID, DEVIC | E REV | A    | ddress: 0F | Ch, 0FDh |   |

- 22 -

#### 9. INTERRUPTS

Interrupts occur by 20 sources among 24 sources, 13 external and 11 internal interrupt.

#### 9.1 Interrupt Control

Each interrupt is controlled and corresponding to a bit in Interrupt Enable Register (IE), the Interrupt Type Register (IT), the Interrupt Priority Control Register (IP) and the Interrupt Request Register (IREQ). An interrupt occurs if the corresponding Interrupt Request occur and enable bits is "1". When several interrupts occur at the same time, the interrupts are received according to priority setting. If interrupts are setting to same priority, then it is decided by hardware internal checking rule.

#### 9.2 Interrupt Source Selection

The below interrupt sources can be selected by the Interrupt Source Selection Register (INTSEL).

- 1. INT0 or Input buffer full.

- 2. INT1 or Output buffer empty.

- 3. Serial I/O1 transmission / SCL, SDA interrupt

- 4. CNTR0 / SCL, SDA interrupt

- 5. Serial I/O2 or I2C.

- 6. INT2 or I2C.

- 7. CNTR1 or Key-on wake-up.

- 8. 8 A-D conversion or Key-on wake-up.

- 9. INT 5 or Auxiliary I2C.

- 10. INT 6 or Keyboard PS/2 INT.

- 11. INT 7 or MOUSE PS/2 INT.

- 12. INT 8 or Internal PS/2 INT.

- 13. INT 9 or Auxiliary SCL, SDA interrupt.

#### 9.3 External interrupt Pin Selection

The occurrence sources of the external interrupt INT2, INT3, and INT4 can be selected from either input from INT20, INT30, INT40 pin, or input from INT21, INT31, and INT41 pin by the INT2, INT3, INT4 interrupt switch bit (bit 4 of PCTRL2).

#### 9.4 Key Input Interrupt (Key-on Wake Up)

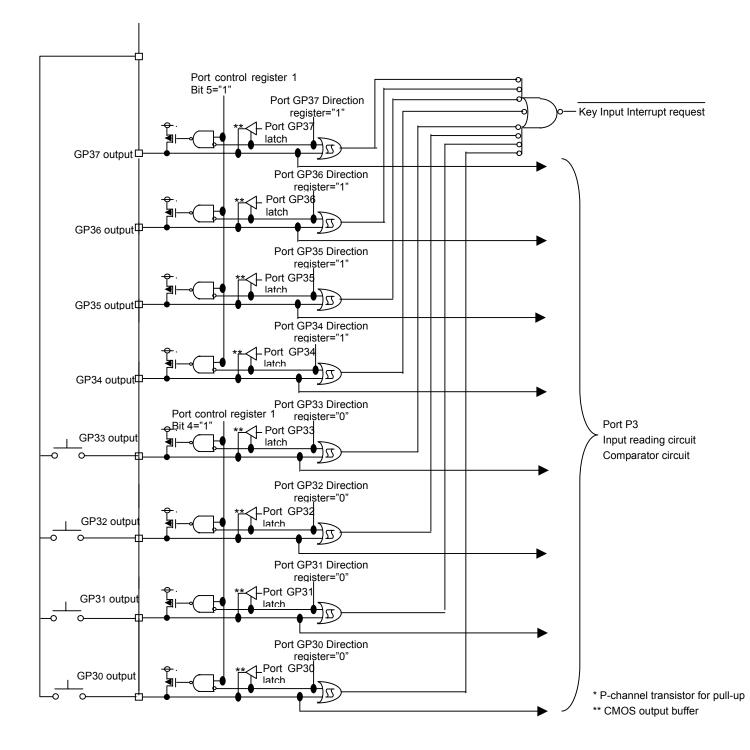

A Key input interrupt request is generated by applying "L" level to any pin of port GP3 that have been set to input mode. In other words, it is generated when AND of input level goes from "1" to "0". An example of using a key input interrupt is shown in blow Figure, where an Interrupt Request is generated by pressing one of the keys consisted as an active-low key matrix which inputs to ports P30-P33.

Fig.8.1 Connection Example

#### 9.5 Interrupt Vector Table

| SOURCE                                    | VECTOR ADDRESS |  |  |  |  |

|-------------------------------------------|----------------|--|--|--|--|