# TMC22x5yA

# **Multistandard Digital Video Decoder**

# Three-Line Adaptive Comb Decoder Family, 8 & 10 bit

#### **Features**

- · Very high performance, low cost

- · Adaptive comb-based decoding

- Multiple pin-compatible versions

- 3-line, 2-line, and band-split

- 8- and 10-bit processing

- · Internal digital linestores

- Supports NTSC/PAL field and NTSC frame based decoding

- Multiple input formats

- CCIR-601/624 (D1), D2, CVBS, YC

- Multiple output formats

- CCIR-601/624 (D1), RGB, YC<sub>B</sub>C<sub>R</sub>

- 10-18 Mpps data rate

- · Parallel and serial control interface

- Single +5V power supply

### **Applications**

- · Studio television equipment

- · Personal computer video input

- · MPEG and JPEG compression inputs

### **Description**

The TMC22x5yA family of Digital Video Decoders offers unprecedented, broadcast-quality video processing performance in a single chip. It accepts line-locked or subcarrier-locked composite, YC, or D1 digital video and produces digital components in a variety of formats.

An internal three-line adaptive comb decoder structure produces optimal picture quality with a wide range of source material. NTSC/PAL field and NTSC frame based decoding is supported with external memory. Full comb programmability allows the user to tailor the decoder's response to a particular systems goals.

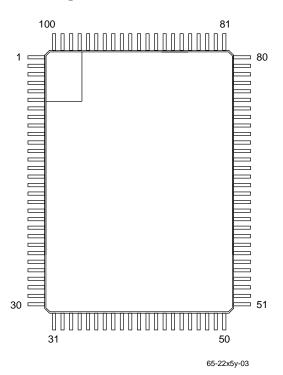

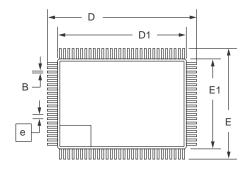

A family of products offers 3-line, 2-line, and simple decoders in 8-bit and 10-bit versions—all in a pin and software-compatible format. Serial and parallel control ports are provided. These submicron CMOS devices are packaged in a 100-lead Metric Quad Flat Pack (MQFP).

#### **Related Products**

- TMC22071 Genlocking Video Digitizer

- TMC22x9x 8 bit Digital Video Encoders

- TMC2081 Digital Video Mixer

- TMC3003 Triple 10-bit D/A Converter

- TMC1185 10 bit A/D converter

- · TMC2192 10 bit video encoder

- TMC2072 Enhanced Genlocking Video Digitizer

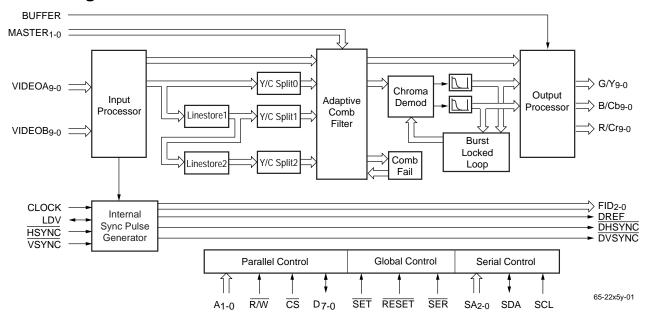

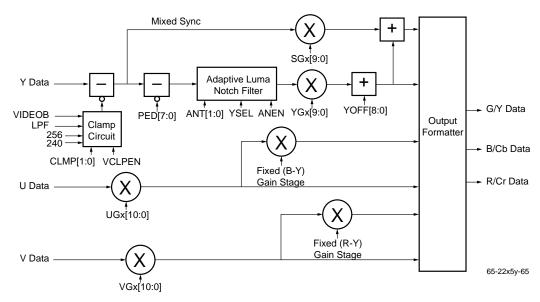

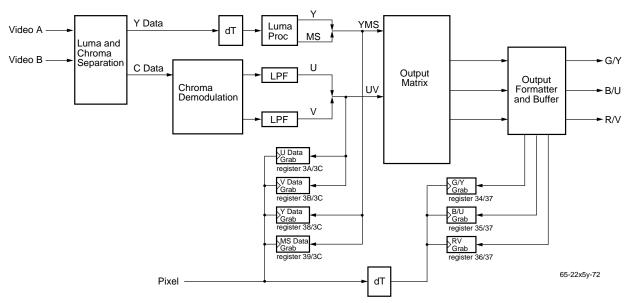

## **Block Diagram**

### **Table of Contents**

| Features                                                                | 1  |

|-------------------------------------------------------------------------|----|

| Applications                                                            | 1  |

| Description                                                             | 1  |

| Block Diagram                                                           | 1  |

| Contents                                                                |    |

| List of Tables and Figures                                              | 3  |

| General Description                                                     |    |

| Input Processor                                                         |    |

| Adaptive Comb Filter                                                    |    |

| Output Processor                                                        | 5  |

| Parallel and Serial Microprocessor Interfaces                           | 5  |

| Pin Assignments                                                         |    |

| Pin Descriptions                                                        |    |

| Control Register Map                                                    |    |

| Control Register Definitions                                            |    |

| Decoder Introduction                                                    |    |

| YC Separation                                                           | 40 |

| Comb Filter Architecture for YC Separation                              |    |

| YC Line-Based Comb Filters                                              |    |

| D1 Line-Based Comb Filters                                              |    |

| NTSC Frame and Field Based Decoders                                     |    |

| Composite Frame-Based Comb Filters                                      |    |

| Composite Field-Based Comb Filters                                      |    |

| PAL Field Comb Decoders                                                 |    |

| Composite PAL Field Comb Filters                                        |    |

| The TMC22x5yA Comb Filter Architecture TMC22x5yA Functional Description |    |

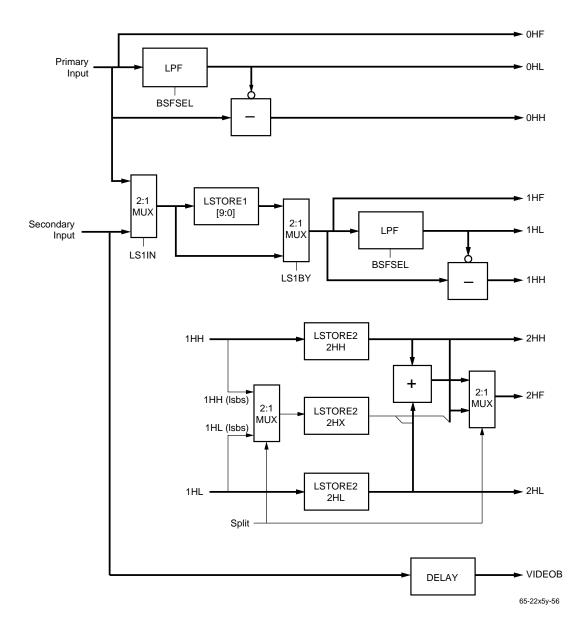

| Input Processor                                                         |    |

| Bandsplit Filter (BSF)                                                  |    |

| Comb Filter Input                                                       |    |

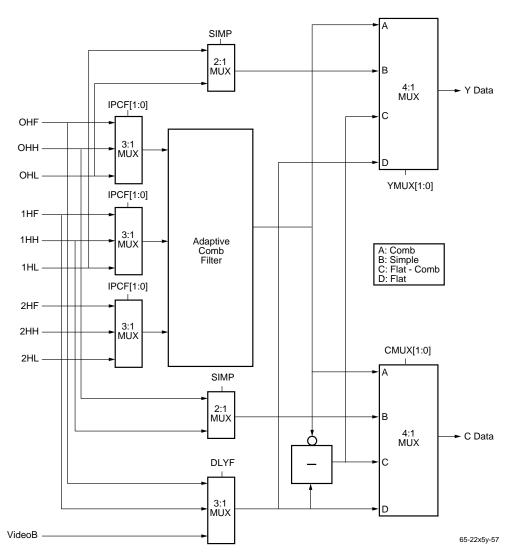

| Adaptive Comb Filter                                                    | 43 |

| Comb Fails                                                              |    |

| Comb Fail Detection                                                     |    |

| Generation of the Comb Fail Signals                                     |    |

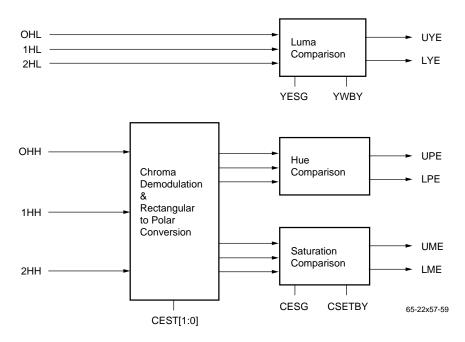

| Luma Error Signals                                                      |    |

| Hue and Saturation Error Signals                                        |    |

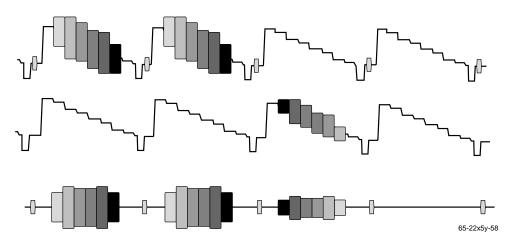

| Picture Correlation                                                     |    |

| Adapting the Comb Filter                                                |    |

| XLUT                                                                    |    |

| Digital Burst Locked Loop                                               |    |

| Color Kill Counter                                                      |    |

| PAL Color Frame Bit                                                     |    |

| Hue Control                                                             |    |

| System Monitoring of the Burst Loop Error                               | 55 |

|                                                                                                                                                | 55                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Pedestal Removal                                                                                                                               |                                                                |

| Clamp Generator                                                                                                                                | 55                                                             |

| Luma Notch Filter                                                                                                                              | 56                                                             |

| Matrix                                                                                                                                         |                                                                |

| Programmable U Scalar                                                                                                                          | 56                                                             |

| Programmable V Scalar                                                                                                                          | 56                                                             |

| Programmable Y Scalar                                                                                                                          |                                                                |

| Programmable MS Scalar                                                                                                                         | 56                                                             |

| Fixed (B-Y) and (R-Y) Scalars                                                                                                                  | 56                                                             |

| Y Offset                                                                                                                                       |                                                                |

| Matrix Limiters                                                                                                                                | 57                                                             |

| Examples of Output Matrix Operation                                                                                                            | 57                                                             |

| Simple Luma Color Correction                                                                                                                   | 58                                                             |

| CBCR MSB Inversion                                                                                                                             | 58                                                             |

| Output Rounding                                                                                                                                | 58                                                             |

| Output Formats                                                                                                                                 | 58                                                             |

| Decimating CBCR Data                                                                                                                           |                                                                |

| Multiplexed YCBCR Output (TRS Words Inserted).                                                                                                 | 58                                                             |

| YC Outputs                                                                                                                                     |                                                                |

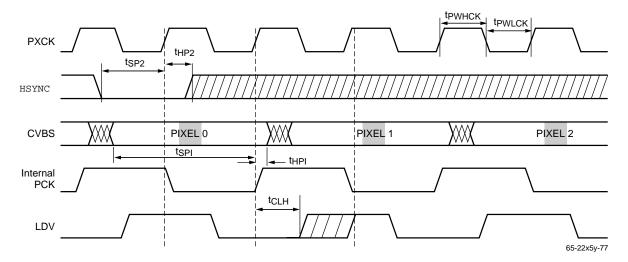

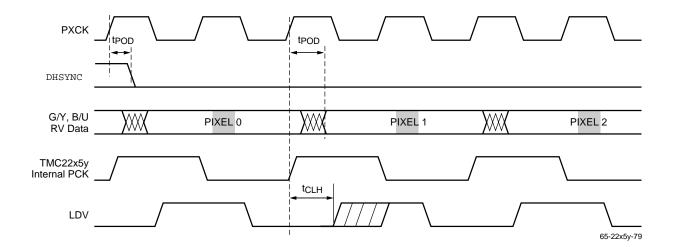

| The LDV Clock                                                                                                                                  |                                                                |

| Sync Pulse Generator                                                                                                                           |                                                                |

| Internal Field and Line Numbering Scheme                                                                                                       |                                                                |

| Timing Parameters                                                                                                                              |                                                                |

| Subservior Programming                                                                                                                         | 61                                                             |

| Subcarrier Programming                                                                                                                         |                                                                |

| Horizontal Timing                                                                                                                              | 61                                                             |

| Horizontal Timing Horizontal and Vertical Timing Parameters                                                                                    | 61<br>61                                                       |

| Horizontal Timing  Horizontal and Vertical Timing Parameters  Vertical Blanking                                                                | 61<br>61<br>62                                                 |

| Horizontal Timing                                                                                                                              | 61<br>61<br>62<br>65                                           |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65                                                 |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65                                           |

| Horizontal Timing Horizontal and Vertical Timing Parameters Vertical Blanking VINDO Operation Video Measurement Pixel Grab Composite Line Grab | 61<br>62<br>65<br>65<br>65                                     |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br><b> 65</b><br>67                             |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>65<br>67<br>67                         |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>65<br>67<br>68                         |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>68                         |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>71<br>72                   |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>71<br>72                   |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>71<br>72<br>73             |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>71<br>72<br>73<br>76<br>76 |

| Horizontal Timing                                                                                                                              | 61<br>61<br>62<br>65<br>65<br>67<br>67<br>72<br>73<br>76<br>76 |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>71<br>72<br>75<br>76<br>77 |

| Horizontal Timing                                                                                                                              | 61<br>62<br>65<br>65<br>67<br>67<br>72<br>73<br>75<br>76<br>77 |

### **List of Tables and Figures**

|              | J                                    |            |                                       |

|--------------|--------------------------------------|------------|---------------------------------------|

| Γable 1.     | TMC22x5yA Decoder Family 4           | Figure 11. | Input Processor 44                    |

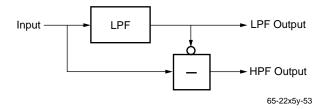

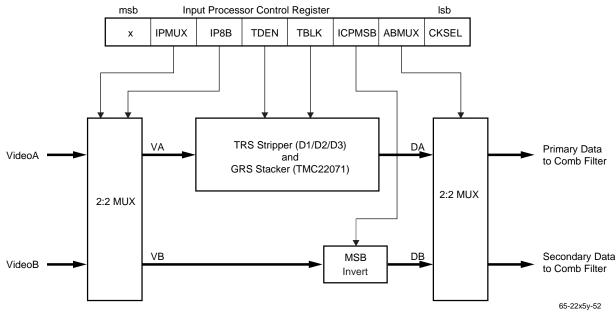

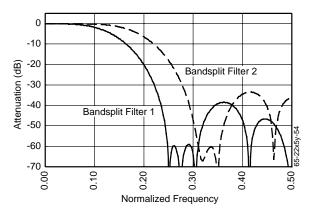

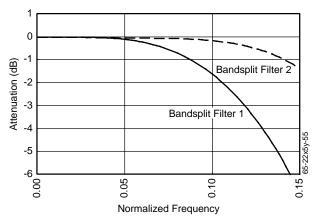

| Γable 2.     | Normalized Subcarrier Frequency      | Figure 12. | Complementary Bandsplit Filter 44     |

|              | as a Function of Pixel Data Rates 45 | Figure 13. | Bandsplit Filter, Full Frequency      |

| Γable 3.     | Comb Filter Architecture 48          |            | Response 45                           |

| Γable 4.     | Simple Example of an Adaptive        | Figure 14. | Bandsplit Filter, Passband            |

|              | Comb Filter Architecture 48          |            | Response 45                           |

| Γable 5.     | Adaption Modes 51                    | Figure 15. | Block Diagram of Comb Filter Input 46 |

| Γable 6.     | XLUT Input Selection 52              |            | Signal Flow Around the Adaptive       |

| Γable 7.     | XLUT Output Function52               | · ·        | Comb Filter 47                        |

| Table 8.     | XLUT Special Function Definitions 52 | Figure 17. | Example of a Comb Fail Using a NTSC   |

| Γable 9.     | PAL-B,G,H,I Bruch                    | Ü          | Two Line Comb Filter49                |

|              | Blanking Sequence 53                 | Figure 18. | Generation of Upper and Lower Comb    |

| Γable 10.    | PAL-M Bruch Blanking Sequence 54     | 3          | Fail Signals50                        |

| Γable 11.    | Blanking Level Selection55           | Figure 19. | Comb Filter Selection51               |

| Table 12.    | Adaptive Notch Threshold Control 55  |            | XLUT Input Selection52                |

| Γable 13.    | Matrix Limiters57                    |            | Block Diagram of Digital Burst        |

| Table 14.    | Output Format 58                     | 9          | Locked Loop53                         |

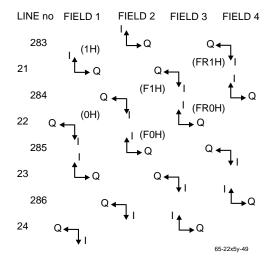

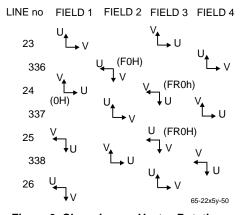

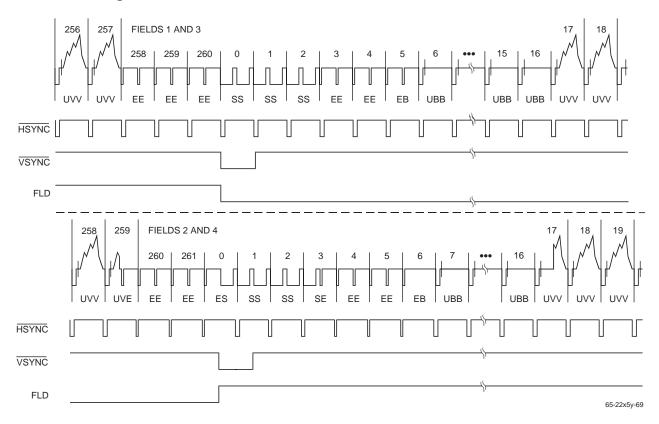

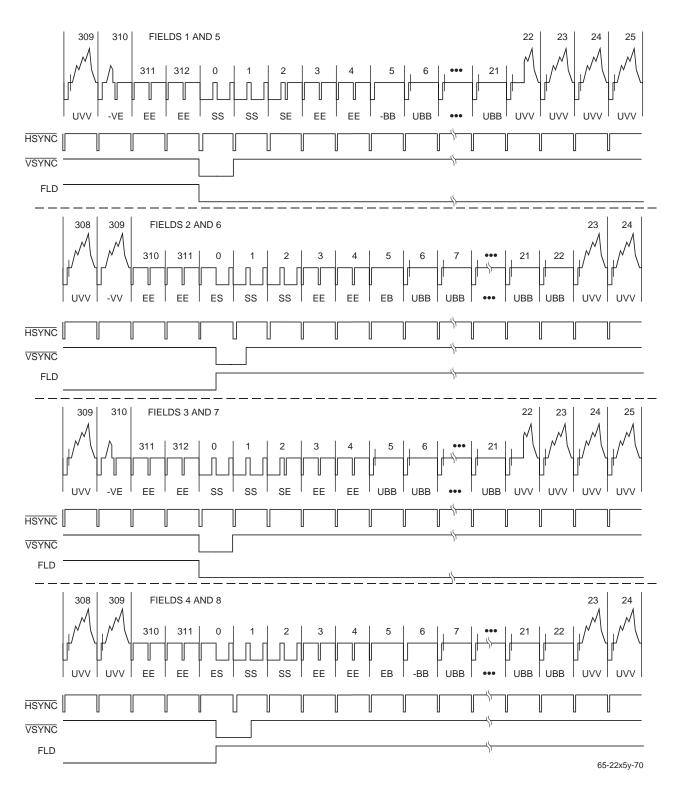

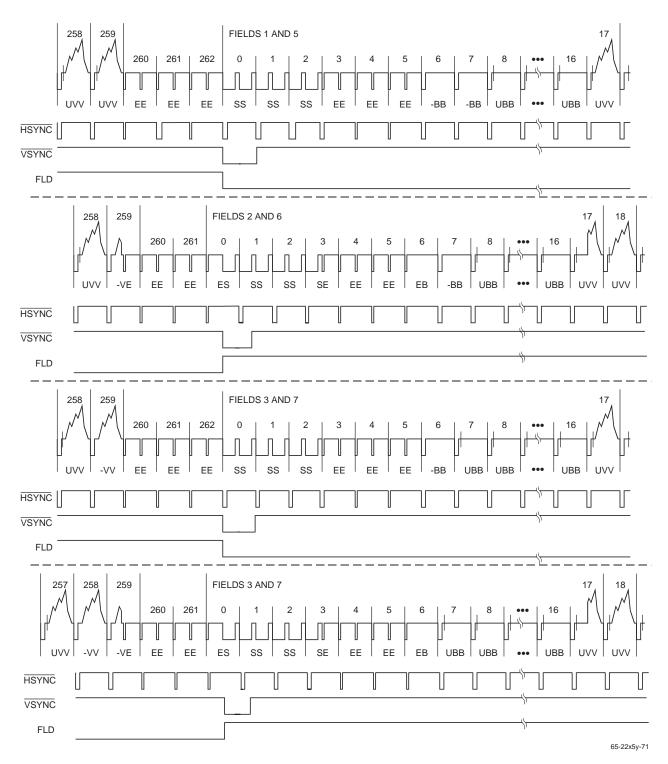

| Γable 15.    | NTSC Field and Line Numbering 59     | Figure 22. | Gaussian Low Pass Filters54           |

| Table 16.    | PAL B,G,H,I Field and                | _          | Gaussian LPF Passband Detail54        |

| - abio 101   | Line Numbering59                     |            | Output Processor Block Diagram 55     |

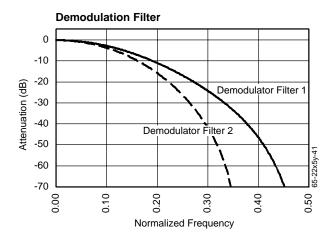

| Γable 17.    | PAL M Field and Line Numbering 59    |            | Adaptive Notch Filters56              |

| Table 18.    | Vertical Blanking Period60           |            | Luminance Notch Filter56              |

| Гable 19.    | Vertical Burst Blanking Period 60    |            | Horizontal Timing61                   |

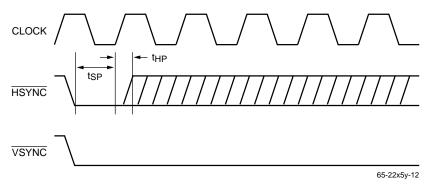

| Table 20.    | Table of Line Idents, LID[4:0]60     |            | External HSYNC and VSYNC Timing       |

| Table 21.    | Timing Offsets 61                    | ga. o 20.  | for Field 1(3, 5, or 7)               |

| Table 22.    | PAL VINDO operation63                | Figure 29. | NTSC Vertical Interval62              |

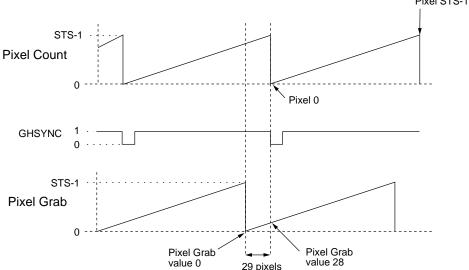

| Гable 23.    | Pixel Grab Control66                 |            | PAL-B,G,H,I,N Vertical Interval 62    |

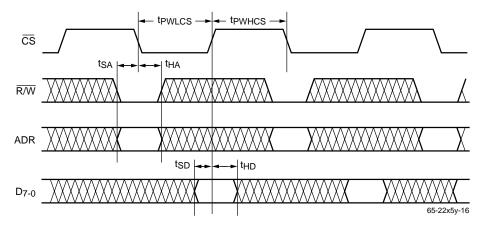

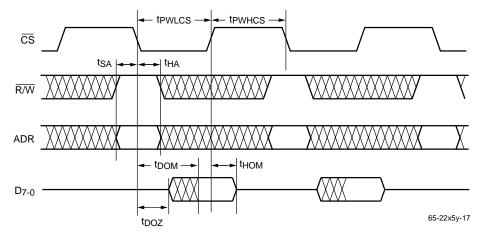

| Table 24.    | Parallel Port Control 67             |            | PAL-M Vertical Interval63             |

| Table 25.    | Serial Port Addresses 69             |            | Pixel Grab Locations64                |

| . a.b.to _0. |                                      |            | Relationship Between Pixel Count      |

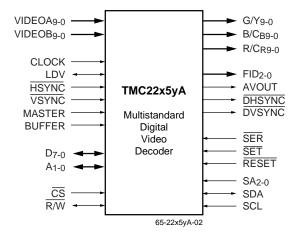

| igure 1.     | Logic Symbol4                        | 3          | and Pixel Grab Value65                |

| igure 2.     | Pixel Data Format 4                  | Figure 34. | Microprocessor Parallel Port –        |

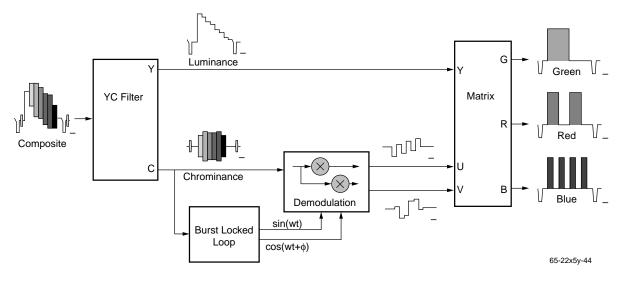

| igure 3.     | Fundamental Decoder                  | Ü          | Write Timing66                        |

| J            | Block Diagram 40                     | Figure 35. | Microprocessor Parallel Port –        |

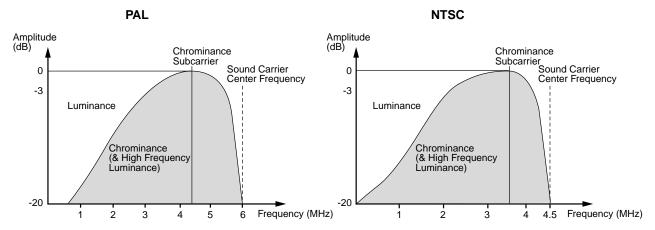

| igure 4.     | Comparison of the Frequency          | 3          | Read Timing68                         |

| J            | Spectrum of NTSC and PAL             | Figure 36. | Serial Port Read/Write Timing69       |

|              | Composite Video Signals 40           |            | Serial Interface –                    |

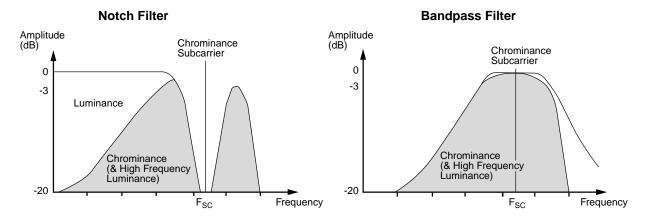

| igure 5.     | Examples of Notch and Bandpass       | 3          | Typical Byte Transfer70               |

| J            | Filters 41                           | Figure 38. | Equivalent Digital Input Circuit 71   |

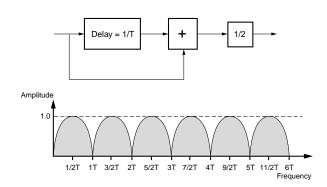

| igure 6.     | 41                                   |            | Equivalent Digital Output71           |

| igure 7.     | Chrominance Vector Rotation in       |            | Threshold Levels for Three-state 71   |

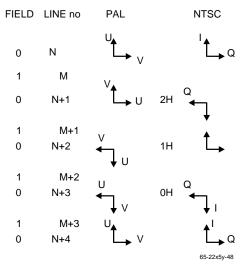

| J            | PAL and NTSC 42                      |            | Input Timing Parameters72             |

| igure 8.     | Chrominance Vector Rotation Over     |            | Functional Block Diagram of the       |

| J            | 4 Fields in NTSC                     | J          | TMC22x5yA G/Y, B/U, and R/V Output    |

| igure 9.     | Chrominance Vector Rotation Over     |            | Stage73                               |

| J            | 4 Fields in PAL                      | Figure 43. | Output Timing Parameters74            |

| igure 10.    | TMC22x5yA Line Based Comb            | <b>5</b>   |                                       |

| J 2 . 3.     | Filter Architecture43                |            |                                       |

|              |                                      |            |                                       |

### **General Description**

The TMC22x5yA digital decoder can be used as a universal input to digital video processing systems by decoding digital composite video and transcoding digital component inputs into a common data format.

The digital comb filter decoder implements one of sixteen comb filter architectures to produce luminance and color difference component signals which are virtually free of the cross-color and cross-luminance artifacts associated with simple bandsplit filter decoders.

Table 1. TMC22x5yA Decoder Family

|                     | TM | C221 | 5yA | TM | C220 | 5yA |

|---------------------|----|------|-----|----|------|-----|

| Function            | 3  | 2    | 1   | 3  | 2    | 1   |

| 10-bit Data         | ~  | ~    | ~   |    |      |     |

| 8-bit Data          | ~  | ~    | ~   | ~  | ~    | ~   |

| D1 Interface        | ~  | ~    | ~   | ~  | ~    | ~   |

| Line-Locked Mode    | ~  | ~    | ~   | ~  | ~    | ~   |

| fsc-Locked Mode     | ~  | ~    | ~   | ~  | ~    | ~   |

| Genlock Mode        | ~  | ~    | ~   | ~  | ~    | ~   |

| NTSC Frame Comb     | ~  |      |     | ~  |      |     |

| NTSC/PAL Field Comb | ~  |      |     | ~  |      |     |

| 3-Line Comb         | ~  |      |     | ~  |      |     |

| 2-Line Comb         | /  | ~    |     | ~  | ~    |     |

| Line Grab           | ~  | ~    |     | ~  | ~    |     |

| Pixel Grab          | >  | ~    | ~   | ~  | ~    | ~   |

Because the cost/performance tradeoff varies among applications, the TMC22x5yA decoder has been developed as a family of six parts. They are all assembled in the same package, and fit the same footprint. The register maps are identical.

Figure 1. Logic Symbol

The devices come in 8- and 10-bit resolution versions (see Figure 2 for data alignment between 8- and 10-bit versions). Within each resolution version there are three models, offering three-line adaptive comb filtering, two-line adaptive

comb filtering, and simple decoding. The TMC22153A 10-bit three-line comb filter can be programmed to emulate any of the other parts. All prototyping can be performed with this version to evaluate performance tradeoffs, and lowercost versions are easily substituted in production.

#### **Input Processor**

The digitized video and clocks provided to the decoder can be either locked to the line frequency or the subcarrier frequency of the digitized waveform, providing broadcast quality decoding from the NTSC square pixel rate of 12.27 MHz to the PAL four times subcarrier pixel rate of 17.73 MHz.

| MSB                                  |                                      |     |                                                                                                  |                                      | LSB                                                                                              |        |

|--------------------------------------|--------------------------------------|-----|--------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------|--------|

| VA9<br>VB9<br>G/Y9<br>B/CB9<br>R/CR9 | VA8<br>VB8<br>G/Y8<br>B/CB8<br>R/CR8 | ••• | VA <sub>2</sub><br>VB <sub>2</sub><br>G/Y <sub>2</sub><br>B/CB <sub>2</sub><br>R/CR <sub>2</sub> | VA1<br>VB1<br>G/Y1<br>B/CB1<br>R/CR1 | VA <sub>0</sub><br>VB <sub>0</sub><br>G/Y <sub>0</sub><br>B/CB <sub>0</sub><br>R/CR <sub>0</sub> | 10 bit |

| VA9<br>VB9<br>G/Y9<br>B/CB9<br>R/CR9 | VA8<br>VB8<br>G/Y8<br>B/CB8<br>R/CR8 | ••• | VA2<br>VB2<br>G/Y2<br>B/CB2<br>R/CR2                                                             | N/C<br>N/C<br>N/C<br>N/C             | N/C<br>N/C<br>N/C<br>N/C                                                                         | 8 bit  |

Figure 2. Pixel Data Format

Inputs containing embedded GRS (CADEKA Video Input Processors), TRS words (D1 multiplexed component signals), and TRS-ID words (deserialized D2 signals) can be used to lock the internal horizontal and vertical state machines to the embedded information. If this information is not provided, external horizontal and vertical syncs are required for all line-locked input formats, and are optional for NTSC inputs locked to four times the subcarrier (4\*Fsc). A simple sync separator is provided for digitized inputs locked to the subcarrier frequency: the internal sync separator locks to the mid point of syncs during the vertical field group, then flywheels during the active portion of the field. For this reason, the DHSYNC and DVSYNC operations are not guaranteed in subcarrier mode.

#### **Adaptive Comb Filter**

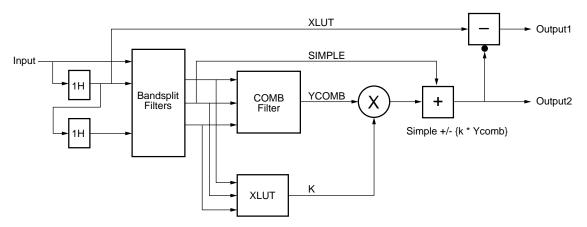

The line based adaptive comb filter in the TMC22x5yA adds or subtracts the high frequency data from three adjacent field lines to produce the average of the high frequency luminance by canceling the chrominance signals, which in flat fields of color are 180 degrees apart. Unfortunately flat fields of color are rare and, when vertical transitions in the picture occur, the output of the comb filter contains a mixture of both high frequency luminance and chrominance, at which time the comb fails. To avoid the comb filter artifacts that occur when this happens, three sets of error signals are sent to a user-programmable lookup table, allowing the output of the comb filter to be mixed with the output of an internal bandsplit decoder.

To produce these comb fail error signals, the video on each of the inputs to the comb filter is passed through a simple bandsplit decoder. The low-frequency portion of the signal is

assumed to be luminance and the high frequency portion is processed as chrominance to find the magnitude and phase of the chrominance vector. These three components are then compared across the (0H & 1H) and (1H & 2H) taps of the comb filter to produce the difference in luminance, chrominance magnitude, and chrominance phase. These differences are then translated in the user-programmable lookup table to produce the "K" signal which controls the complementary mix between the output of the comb filter and the simple bandsplit decoder. That is, the "K" signals controls how much of the combed high frequency luminance signal is subtracted from the simple bandsplit chrominance for chroma combs, or added to the low frequency output of the bandsplit for luma comb filters.

#### **Output Processor**

The demodulated chrominance signal and the luminance signal are passed through a programmable output matrix, producing RGB, YUV, or YCBCR. When the clock is at 27MHz, a D1 signal can be produced on the R/V output with the embedded TRS words fixed to the external  $\overline{\text{HSYNC}}$  and  $\overline{\text{VSYNC}}$  timing.

#### Parallel and Serial Microprocessor Interfaces

The parallel microprocessor interface employs 12 pins, the serial port uses 5. A single pin,  $\overline{SER}$ , selects between the two interface modes.

In parallel interface mode, one address line is decoded for access to the internal control register and its pointer. Controls are reached by loading a desired address through the 8-bit D7-0 port, followed by the desired data (read or write) for that address. The control register address pointer auto-increments to address 3Fh and then remains there.

A 2-line serial interface may also be used for initialization and control. The same set of registers accessed by the parallel port is available to the serial port. The device address in the serial interface is selected via pins SA<sub>2-0</sub>.

The RESET pin sets all internal state machines to their initialized conditions and places the decoder in a power-down mode. All register data are maintained while in power-down mode.

### Pin Assignments

| Pin | Name              | Pin | Name              | Pin | Name                | Pin | Name                |

|-----|-------------------|-----|-------------------|-----|---------------------|-----|---------------------|

| 1   | G/Y <sub>1</sub>  | 26  | R/Cr <sub>1</sub> | 51  | RESET               | 76  | GND                 |

| 2   | G/Y <sub>0</sub>  | 27  | R/Cr <sub>0</sub> | 52  | SET                 | 77  | VIDEOA <sub>0</sub> |

| 3   | LDV               | 28  | GND               | 53  | SER                 | 78  | VIDEOA <sub>1</sub> |

| 4   | GND               | 29  | $V_{DD}$          | 54  | SA <sub>0</sub>     | 79  | VIDEOA <sub>2</sub> |

| 5   | V <sub>DD</sub>   | 30  | DREF              | 55  | SA <sub>1</sub>     | 80  | VIDEOA3             |

| 6   | B/Cb9             | 31  | FID <sub>0</sub>  | 56  | SA <sub>2</sub>     | 81  | VIDEOA4             |

| 7   | B/Cb <sub>8</sub> | 32  | FID <sub>1</sub>  | 57  | GND                 | 82  | VIDEOA5             |

| 8   | B/Cb <sub>7</sub> | 33  | FID <sub>2</sub>  | 58  | SDA                 | 83  | VIDEOA <sub>6</sub> |

| 9   | B/Cb <sub>6</sub> | 34  | DHSYNC            | 59  | SCL                 | 84  | VIDEOA7             |

| 10  | B/Cb <sub>5</sub> | 35  | DVSYNC            | 60  | CS                  | 85  | VIDEOA <sub>8</sub> |

| 11  | B/Cb <sub>4</sub> | 36  | D <sub>0</sub>    | 61  | R/W                 | 86  | VIDEOA9             |

| 12  | B/Cb <sub>3</sub> | 37  | D <sub>1</sub>    | 62  | A <sub>0</sub>      | 87  | MASTER <sub>0</sub> |

| 13  | B/Cb <sub>2</sub> | 38  | D <sub>2</sub>    | 63  | A <sub>1</sub>      | 88  | MASTER <sub>1</sub> |

| 14  | B/Cb <sub>1</sub> | 39  | GND               | 64  | GND                 | 89  | CLOCK               |

| 15  | B/Cb <sub>0</sub> | 40  | V <sub>DD</sub>   | 65  | $V_{DD}$            | 90  | GND                 |

| 16  | GND               | 41  | D <sub>3</sub>    | 66  | VIDEOB <sub>0</sub> | 91  | V <sub>DD</sub>     |

| 17  | $V_{DD}$          | 42  | D <sub>4</sub>    | 67  | VIDEOB <sub>1</sub> | 92  | GND                 |

| 18  | R/Cr9             | 43  | D <sub>5</sub>    | 68  | VIDEOB <sub>2</sub> | 93  | G/Y <sub>9</sub>    |

| 19  | R/Cr <sub>8</sub> | 44  | D <sub>6</sub>    | 69  | VIDEOB <sub>3</sub> | 94  | G/Y <sub>8</sub>    |

| 20  | R/Cr7             | 45  | D <sub>7</sub>    | 70  | VIDEOB4             | 95  | G/Y <sub>7</sub>    |

| 21  | R/Cr <sub>6</sub> | 46  | GND               | 71  | VIDEOB5             | 96  | G/Y <sub>6</sub>    |

| 22  | R/Cr <sub>5</sub> | 47  | V <sub>DD</sub>   | 72  | VIDEOB6             | 97  | G/Y <sub>5</sub>    |

| 23  | R/Cr <sub>4</sub> | 48  | HSYNC             | 73  | VIDEOB <sub>7</sub> | 98  | G/Y <sub>4</sub>    |

| 24  | R/Cr <sub>3</sub> | 49  | VSYNC             | 74  | VIDEOB <sub>8</sub> | 99  | G/Y <sub>3</sub>    |

| 25  | R/Cr <sub>2</sub> | 50  | BUFFER            | 75  | VIDEOB9             | 100 | G/Y <sub>2</sub>    |

# **Pin Descriptions**

| Pin Name              | Pin Number                                   | Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|----------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inputs                | Į.                                           |       | -                                                                                                                                                                                                                                                                                                                                                                                                        |

| VIDEOA9-0             | 86, 85, 84, 83,<br>82, 81, 80, 79,<br>78, 77 | TTL   | Video input A. An 8 or 10 bit data input to the input multiplexer. For 8-bit versions (TMC2205yA) the data are left-justified (VIDEOA9-2).                                                                                                                                                                                                                                                               |

| VIDEOB <sub>9-0</sub> | 75, 74, 73, 72,<br>71, 70, 69, 68,<br>67, 66 | TTL   | <b>Video input B.</b> An 8 or 10 bit data input to the input multiplexer. For 8-bit versions (TMC2205yA) the data are left-justified (VIDEOB <sub>9-2</sub> ).                                                                                                                                                                                                                                           |

| VSYNC                 | 49                                           | TTL   | <b>Vertical sync input.</b> A vertical sync signal (active low) occurring at the start of the first vertical sync pulse in a vertical field group. A falling edge of <del>VSYNC</del> which is coincident with a falling edge of <del>HSYNC</del> indicates field 1. This signal is active only when SPGIP <sub>1-0</sub> = 00.                                                                          |

| HSYNC                 | 48                                           | TTL   | <b>Horizontal sync input.</b> A horizontal sync signal (active low) occurring at the falling edge of the video sync. This signal is active only when $SPGIP_{1-0} = 00$ .                                                                                                                                                                                                                                |

| MASTER <sub>1-0</sub> | 88, 87                                       | TTL   | Master decoder control.                                                                                                                                                                                                                                                                                                                                                                                  |

|                       |                                              |       | <ul> <li>Adaptive comb decoder</li> <li>Simple bandsplit decoder</li> <li>Reserved</li> <li>Flat notched luma and simple bandsplit chroma</li> </ul>                                                                                                                                                                                                                                                     |

| BUFFER                | 50                                           | TTL   | Control register select. This signal switches between two sets of registers which control the gain or hue values in the output matrix. When BUFFER = 0, registers 17-1F are active. When BUFFER = 1, registers 27-2F take control.                                                                                                                                                                       |

| CLOCK                 | 89                                           | TTL   | Master processing clock. The clock signal can either be at twice the pixel data rate in the line locked modes, or at four times the subcarrier frequency in the subcarrier mode. The interpretation of the CLOCK signal is set by the CKSEL register bit.                                                                                                                                                |

| SET                   | 52                                           | TTL   | Programmable function pin. The function specified by the SET register is active when SET is low. The decoder returns to its previous operation when SET goes high.                                                                                                                                                                                                                                       |

| Outputs               |                                              |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

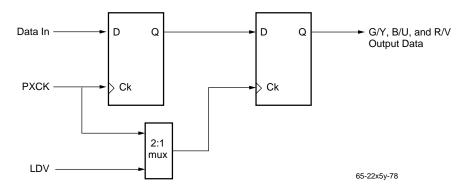

| G/Y <sub>9-0</sub>    | 93, 94, 95, 96,<br>97, 98, 99, 100,<br>1, 2  | TTL   | <b>Green or Luminance digital output.</b> For 8-bit versions (TMC2205yA) the data are left-justified (G/Y9-2).                                                                                                                                                                                                                                                                                           |

| B/C <sub>B9-0</sub>   | 6, 7, 8, 9, 10,<br>11, 12, 13, 14,<br>15     | TTL   | <b>Blue or C<sub>B</sub> digital output.</b> For 8-bit versions (TMC2205y) the data are left-justified (B/C <sub>B</sub> 9-2).                                                                                                                                                                                                                                                                           |

| R/CR9-0               | 18, 19, 20, 21,<br>22, 23, 24, 25,<br>26, 27 | TTL   | Red or $C_R$ digital output. For 8-bit versions (TMC2205yA) the data are left-justified (R/ $C_R$ 9-2).                                                                                                                                                                                                                                                                                                  |

| DVSYNC                | 35                                           | TTL   | <b>Vertical sync output.</b> The DVSYNC signal occurs once per field and lasts for 1 video line.                                                                                                                                                                                                                                                                                                         |

| DHSYNC                | 34                                           | TTL   | Horizontal sync output. The DHSYNC signal occurs once per line and lasts for 64 clock periods.                                                                                                                                                                                                                                                                                                           |

| LDV                   | 3                                            | TTL   | Data synchronization output. LDV can be an internally or externally generated clock signal. The internal LDV signal is produced when the CLOCK input is at twice the pixel data rate (PXCK); and is a pixel data rate clock phase locked to the falling edge of the HSYNC. The external LDV can be selected under software control, and must be at the CLOCK, or a sub multiple of the CLOCK, frequency. |

# Pin Descriptions (cont.)

| Pin Name            | Pin Number                                  | Value | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------|---------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DREF                | 30                                          | TTL   | <b>Decoder reference signal.</b> This is a dual function pin, controlled by register 24, that can function as an active video output indicator or output as a clamp pulse. When set to the active video output function, the DREF pin is HIGH during the video portion of each line and LOW during the horizontal and vertical blanking levels. When set to output a clamp pulse, the clamp pulse is controlled by register 24 and 25 allowing a user to program when a 0.5 μSec pulse is output relative to HSYNC. |  |  |  |

| FID <sub>2</sub> -0 | 33, 32, 31                                  | TTL   | Field identification output. A 3 bit field ident from the DRS signal.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| μP Interface        | •                                           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| D7-0                | 45, 44, 43, 42,<br>41, 38, 37, 36           | TTL   | <b>Parallel control port data I/O.</b> All control parameters are loaded into and read back over this 8 bit data port.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| A1-0                | 63, 62                                      | TTL   | Parallel control port address inputs. These pins govern whether the microprocessor interface selects a table/register address or reads/ writes table/register contents.                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CS                  | 60                                          | TTL   | <b>Parallel control port chip select.</b> When $\overline{CS}$ is high the microprocessor interface port, D <sub>7-0</sub> , is set to HIGH impedance and ignored. When $\overline{CS}$ is LOW, the microprocessor can read or write parameters over D <sub>7-0</sub> .                                                                                                                                                                                                                                             |  |  |  |

| R/W                 | 61                                          | TTL   | Parallel control port read/write control. When $\overline{R/W}$ and $\overline{CS}$ are LOW, the microprocessor can write to the control registers or XLUT over D <sub>7-0</sub> . When $\overline{R/W}$ is HIGH and $\overline{CS}$ is LOW, it can read the contents of any selected XLUT address or control register over D <sub>7-0</sub> .                                                                                                                                                                      |  |  |  |

| RESET               | 51                                          | TTL   | Chip master reset. Bringing RESET LOW sets the software reset control bit, SRESET, LOW and disables the digital outputs. If HRESET is LOW the decoder outputs remain disabled after RESET goes HIGH until the SRESET bit is set high by the host. If HRESET is HIGH when RESET goes HIGH the decoder the internal state machines are enabled.                                                                                                                                                                       |  |  |  |

| SER                 | 53                                          | TTL   | Serial/parallel interface select. This pin will select between a parallel (HIGH) or serial (LOW) interface port.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SDA                 | 58                                          | R-Bus | Serial data interface. Bi-directional serial interface to the control port.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SCL                 | 59                                          | R-Bus | Serial interface clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| SA <sub>2</sub> -0  | 56, 55, 54                                  | TTL   | <b>Serial Address.</b> Three bits providing the lsbs of the serial chip ID used to identify the decoder.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Power Supp          | Power Supply                                |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| V <sub>DD</sub>     | 5, 17, 29, 40,<br>47, 65, 91                | +5 V  | Power Supply. Positive power supply for digital circuits, +5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| GND                 | 4, 16, 28, 39,<br>46, 57, 64, 76,<br>90, 92 | 0.0 V | Ground. Ground for digital circuits, 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

## **Control Register Map**

The TMC22x5yA is initialized and controlled by a set of registers which determine the operating modes.

An external controller is employed to write and read the Control Registers through either the 8-bit parallel or 2-line serial interface port. The parallel port, D7-0, is governed by pins  $\overline{\text{CS}}$ ,  $\overline{\text{R/W}}$ , and A<sub>1-0</sub>. The serial port is controlled by SDA and SCL.

| Reg | Bit            | Name        | Function                                           |  |  |  |  |

|-----|----------------|-------------|----------------------------------------------------|--|--|--|--|

|     | Global Control |             |                                                    |  |  |  |  |

| 00  | 7              | SRST        | Software reset                                     |  |  |  |  |

| 00  | 6              | HRST        | Hardware reset                                     |  |  |  |  |

| 00  | 5-3            | SET         | SET pin function                                   |  |  |  |  |

| 00  | 2              | DHVEN       | Output H&V sync enable                             |  |  |  |  |

| 00  | 1-0            | STD         | Selects video standard                             |  |  |  |  |

|     |                | Input Proce | essor Control                                      |  |  |  |  |

| 01  | 7              |             | reserved, set to zero                              |  |  |  |  |

| 01  | 6              | IPMUX       | Input mux control                                  |  |  |  |  |

| 01  | 5              | IP8B        | 8 bit input format                                 |  |  |  |  |

| 01  | 4              | TDEN        | TRS detect enable                                  |  |  |  |  |

| 01  | 3              | TBLK        | TRS blank enable                                   |  |  |  |  |

| 01  | 2              | IPCMSB      | Chroma input msb invert                            |  |  |  |  |

| 01  | 1              | ABMUX       | AB mux control                                     |  |  |  |  |

| 01  | 0              | CKSEL       | Input clock rate select                            |  |  |  |  |

|     |                | Burst Lo    | op Control                                         |  |  |  |  |

| 02  | 7              | BLLRST      | BLL auto. reset enable                             |  |  |  |  |

| 02  | 6              | VIPEN       | Video Input Processor enable                       |  |  |  |  |

| 02  | 5-4            | LOCK        | Global lock mode                                   |  |  |  |  |

| 02  | 3              | BLM         | BLL lock mode                                      |  |  |  |  |

| 02  | 2              | KILD        | Color kill disable                                 |  |  |  |  |

| 02  | 1              | DMODBY      | Demod bypass                                       |  |  |  |  |

| 02  | 0              | CINT        | C <sub>B</sub> C <sub>R</sub> interpolation enable |  |  |  |  |

|     |                | Chroma Pro  | cessor Control                                     |  |  |  |  |

| 03  | 7-5            | BLFS        | Burst loop filter select                           |  |  |  |  |

| 03  | 4              | CCEN        | Chroma coring enable                               |  |  |  |  |

| 03  | 3-2            | CCOR        | Chroma coring threshold                            |  |  |  |  |

| 03  | 1              | GAUBY       | Gaussian filter bypass                             |  |  |  |  |

| 03  | 0              | GAUSEL      | Gaussian filter select                             |  |  |  |  |

|     |                |             | hreshold                                           |  |  |  |  |

| 04  | 7-0            | BTH         | Burst threshold                                    |  |  |  |  |

|     |                | Ped         | lestal                                             |  |  |  |  |

| 05  | 7-0            | PED         | Pedestal level                                     |  |  |  |  |

| Reg                 | Bit | Name       | Function                                        |  |  |

|---------------------|-----|------------|-------------------------------------------------|--|--|

|                     | ļ.  | Luma Proce | essor Control                                   |  |  |

| 06                  | 7-6 |            | reserved, set to zero                           |  |  |

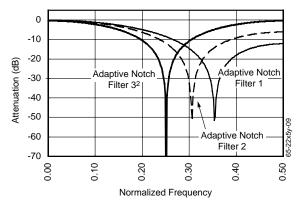

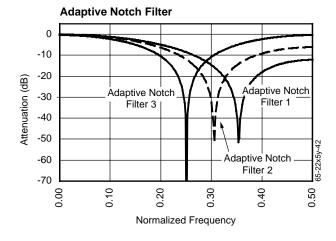

| 06                  | 5   | ANEN       | Adaptive notch enable                           |  |  |

| 06                  | 4   | ANR        | Adaptive notch rounding                         |  |  |

| 06                  | 3-2 | ANT        | Adaptive notch threshold                        |  |  |

| 06                  | 1   | ANSEL      | Adaptive notch select                           |  |  |

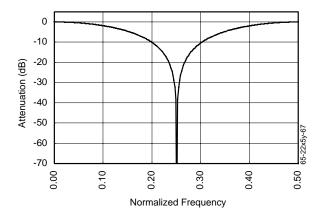

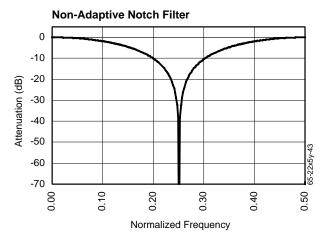

| 06                  | 0   | NOTCH      | Notch enable                                    |  |  |

|                     |     | Comb Proc  | essor Control                                   |  |  |

| 07                  | 7   | LS1BY      | Line store 1 bypass                             |  |  |

| 07                  | 6   | LS1IN      | Line store 1 input                              |  |  |

| 07                  | 5   | LS2DLY     | Line store 2 delay                              |  |  |

| 07                  | 4   | SPLIT      | Line store 2 data width                         |  |  |

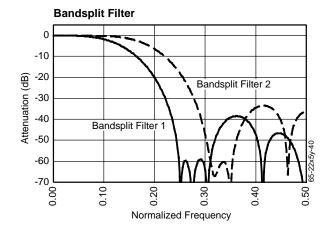

| 07                  | 3   | BSFBY      | Bandsplit filter bypass                         |  |  |

| 07                  | 2   | BSFSEL     | Bandsplit filter select                         |  |  |

| 07                  | 1   | BSFMSB     | Inverts msb of bandsplit filter                 |  |  |

| 07                  | 0   | GRSDLY     | Delays input to GRS decode by 1H                |  |  |

|                     |     | Mid-Sy     | nc Level                                        |  |  |

| 08                  | 7-0 | MIDS       | Mid-sync level                                  |  |  |

|                     |     | Extend     | ded DRS                                         |  |  |

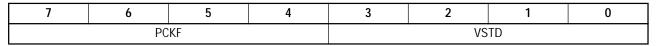

| 09                  | 7-4 | PCKF       | Clock rate                                      |  |  |

| 09                  | 3-0 | VSTD       | Video standard                                  |  |  |

|                     |     | Outpu      | t Control                                       |  |  |

| 0A                  | 7   | OP8B       | Output rounded to 8 bits                        |  |  |

| 0A                  | 6-5 | OPLMT      | Output limit select                             |  |  |

| 0A                  | 4-3 | MSEN       | Mixed sync enable                               |  |  |

| 0A                  | 2   | OPCMSB     | Chroma output msb invert                        |  |  |

| 0A                  | 1   | YBAL       | Luma color correction                           |  |  |

| 0A                  | 0   | BUREN      | Output burst enable                             |  |  |

| 0B                  | 7   | FMT422     | Enables CBCR output mux                         |  |  |

| 0B                  | 6   | CDEC       | C <sub>B</sub> C <sub>R</sub> decimation enable |  |  |

| 0B                  | 5   | YUVT       | Enables D1 output                               |  |  |

| 0B                  | 4-2 |            | reserved, set to zero                           |  |  |

| 0B                  | 1   | DRSEN      | DRS output enable                               |  |  |

| 0B                  | 0   | DRSCK      | DRS data rate                                   |  |  |

| Comb Filter Control |     |            |                                                 |  |  |

| 0C                  | 7-6 | ADAPT      | Adaption mode                                   |  |  |

| 0C                  | 5   | YCES       | YC input error signal control                   |  |  |

| 0C                  | 4   | YCSEL      | luma/chroma comb filter select                  |  |  |

| 0C                  | 3-0 | COMB       | Comb filter architecture                        |  |  |

| Reg         Bit         Name         Function           0D         7-6         CEST         Chroma error signal transform           0D         5         CESG         Chroma error signal gain           0D         4         YESG         Luma error signal gain           0D         3         CESTBY         Chroma error signal bypass           0D         1         FAST         Adaption speed select           0D         0         YWBY         Luma weighting bypass           0E         7-6         XIP         XLUT input select           0E         5-4         XSF         XLUT special function           0E         5-4         XSF         XLUT special function           0E         5-4         XSF         XLUT special function           0E         3-2         YMUX         Y output select           0E         1-0         CMUX         C output select           0F         7         Cottput select           0F         7         Adaption Threshold           0F         7         Cottput select           0F         7         Comb filter input select           0F         1         YCCOMP         YC or Composite input select                                                                               |     | <b>D</b> : | N1                  | F                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|---------------------|--------------------------|

| transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reg | Bit        | Name                | Function                 |

| OD         4         YESG         Luma error signal gain           OD         3         CESTBY         Chroma error signal bypass           OD         2         XFEN         XLUT filter enable           OD         1         FAST         Adaption speed select           OD         0         YWBY         Luma weighting bypass           OE         7-6         XIP         XLUT input select           OE         5-4         XSF         XLUT special function           OE         5-4         XSF         XLUT special function           OE         3-2         YMUX         Y output select           OE         1-0         CMUX         C output select           OF         7         reserved, set to zero           OF         6-5         CAT         Adaption Threshold           OF         4         DCES         D1 CBCR error signal           OF         4         DCES         D1 CBCR error signal           OF         4         DCES         D1 CBCR error signal           OF         3-2         IPCF         Comb filter input select           OF         1         YCCOMP         YC or Composite input select           OF         <                                                                            | 0D  | 7-6        | CEST                |                          |

| 0D         3         CESTBY         Chroma error signal bypass           0D         2         XFEN         XLUT filter enable           0D         1         FAST         Adaption speed select           0D         0         YWBY         Luma weighting bypass           0E         7-6         XIP         XLUT input select           0E         5-4         XSF         XLUT special function           0E         5-4         XSF         XLUT special function           0E         5-4         XSF         XLUT special function           0E         3-2         YMUX         Y output select           0F         1-0         CMUX         C output select           0F         7         reserved, set to zero           0F         4         DCES         D1 CBCR error signal           0F         4         DCES         D1 CBCR error signal           0F         4         DCES         D1 CBCR error signal           0F         3-2         IPCF         Comb filter input select           0F         1         YCCOMP         YC or Composite input select           0F         0         SYNC         Sync to sync 8 lsbs           11         <                                                                            | 0D  | 5          | CESG                | Chroma error signal gain |

| bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0D  | 4          | YESG                | Luma error signal gain   |

| 0D         1         FAST         Adaption speed select           0D         0         YWBY         Luma weighting bypass           0E         7-6         XIP         XLUT input select           0E         5-4         XSF         XLUT special function           0E         3-2         YMUX         Y output select           0E         1-0         CMUX         C output select           0F         7         reserved, set to zero           0F         6-5         CAT         Adaption Threshold           0F         4         DCES         D1 CBCR error signal           0F         3-2         IPCF         Comb filter input select           0F         1         YCCOMP         YC or Composite input select           0F         1         YCCOMP         YC or Composite input select           0F         0         SYNC         Sync processor select           Sync Pulse Generator           10         7-0         STS7-0         Sync to sync 8 Isbs           11         7-0         STS7-0         Sync to burst           12         7-0         BTV         Burst to video           13         7-0         AV7-0         Active                                                                                   | 0D  | 3          | CESTBY              | _                        |

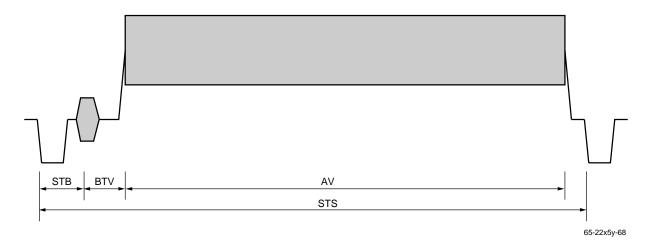

| OD 0 YWBY Luma weighting bypass OE 7-6 XIP XLUT input select OE 5-4 XSF XLUT special function OE 3-2 YMUX Y output select OE 1-0 CMUX C output select OF 7 reserved, set to zero OF 6-5 CAT Adaption Threshold OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 lsbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 15 7 reserved, set to zero 16 6-2 VINDO Number of lines in vertical window 15 1 VDIV Action inside VINDO 16 7-6 reserved, set to zero 16 5-4 NFDLY new field detect delay 16 3-2 SPGIP SPG input select  Buffered register set 0 Active when BUFFER pin set LOW 17 7-0 SG07-0 Msync gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                                 | 0D  | 2          | XFEN                | XLUT filter enable       |

| OE 7-6 XIP XLUT input select OE 5-4 XSF XLUT special function OE 3-2 YMUX Y output select OE 1-0 CMUX C output select OF 7 reserved, set to zero OF 6-5 CAT Adaption Threshold OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 lsbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 14 3 reserved, set to zero 14 2-0 STS10-8 Sync to sync 3 msbs 15 7 reserved, set to zero 15 6-2 VINDO Number of lines in vertical window 15 1 VDIV Action inside VINDO 15 0 VDOV Action outside VINDO 16 7-6 reserved, set to zero 16 5-4 NFDLY new field detect delay 16 3-2 SPGIP SPG input select  Buffered register set 0  Active when BUFFER pin set LOW  17 7-0 SG07-0 Msync gain, 8 lsbs 18 7-0 YG07-0 Y gain, 8 lsbs                                                                                                                                                                                                                                                                     | 0D  | 1          | FAST                | Adaption speed select    |

| OE 5-4 XSF XLUT special function OE 3-2 YMUX Y output select OE 1-0 CMUX C output select OF 7 reserved, set to zero OF 6-5 CAT Adaption Threshold OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 lsbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 15 7 reserved, set to zero 14 2-0 STS10-8 Sync to sync 3 msbs 15 7 reserved, set to zero 16 6-2 VINDO Number of lines in vertical window 15 1 VDIV Action inside VINDO 16 7-6 reserved, set to zero 16 5-4 NFDLY new field detect delay 16 3-2 SPGIP SPG input select  Buffered register set 0 Active when BUFFER pin set LOW  17 7-0 SG07-0 Msync gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                               | 0D  | 0          | YWBY                | Luma weighting bypass    |

| OE 3-2 YMUX Y output select OE 1-0 CMUX C output select OF 7 reserved, set to zero OF 6-5 CAT Adaption Threshold OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 lsbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 15 7 reserved, set to zero 16 6-2 VINDO Number of lines in vertical window 15 1 VDIV Action inside VINDO 15 0 VDOV Action outside VINDO 16 7-6 reserved, set to zero 16 5-4 NFDLY new field detect delay 16 3-2 SPGIP SPG input select  Buffered register set 0 Active when BUFFER pin set LOW 17 7-0 SG07-0 Msync gain, 8 lsbs 18 7-0 YG07-0 Y gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                                                                   | 0E  | 7-6        | XIP                 | XLUT input select        |

| OE 1-0 CMUX C output select  OF 7 reserved, set to zero  OF 6-5 CAT Adaption Threshold  OF 4 DCES D1 CBCR error signal  OF 3-2 IPCF Comb filter input select  OF 1 YCCOMP YC or Composite input select  OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs  11 7-0 STB Sync to burst  12 7-0 BTV Burst to video  13 7-0 AV7-0 Active video line 8 lsbs  14 7-6 reserved, set to zero  14 5-4 AV9-8 Active video line 2 msbs  15 7 reserved, set to zero  15 6-2 VINDO Number of lines in vertical window  15 1 VDIV Action inside VINDO  15 0 VDOV Action outside VINDO  16 7-6 reserved, set to zero  16 5-4 NFDLY new field detect delay  16 3-2 SPGIP SPG input select  Buffered register set 0  Active when BUFFER pin set LOW  17 7-0 SG07-0 Msync gain, 8 lsbs  18 7-0 YG07-0 Y gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                                                                          | 0E  | 5-4        | XSF                 | XLUT special function    |

| OF 7 reserved, set to zero OF 6-5 CAT Adaption Threshold OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 Isbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 Isbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 15 7 reserved, set to zero 16 6-2 VINDO Number of lines in vertical window 15 1 VDIV Action inside VINDO 16 7-6 reserved, set to zero 17 7-6 SPGIP SPG input select  Buffered register set 0 Active when BUFFER pin set LOW 17 7-0 SG07-0 Msync gain, 8 Isbs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0E  | 3-2        | YMUX                | Y output select          |

| OF6-5CATAdaption ThresholdOF4DCESD1 CBCR error signalOF3-2IPCFComb filter input selectOF1YCCOMPYC or Composite input selectOF0SYNCSync processor selectSync Pulse Generator107-0STS7-0Sync to sync 8 lsbs117-0STBSync to burst127-0BTVBurst to video137-0AV7-0Active video line 8 lsbs147-6reserved, set to zero145-4AV9-8Active video line 2 msbs143reserved, set to zero142-0STS10-8Sync to sync 3 msbs157reserved, set to zero156-2VINDONumber of lines in vertical window151VDIVAction inside VINDO150VDOVAction outside VINDO167-6reserved, set to zero165-4NFDLYnew field detect delay163-2SPGIPSPG input select161-0MSIPMixed sync separator input selectBuffered register set 0Active when BUFFER pin set LOW177-0SG07-0Msync gain, 8 lsbs187-0YG07-0Y gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0E  | 1-0        | CMUX                | C output select          |

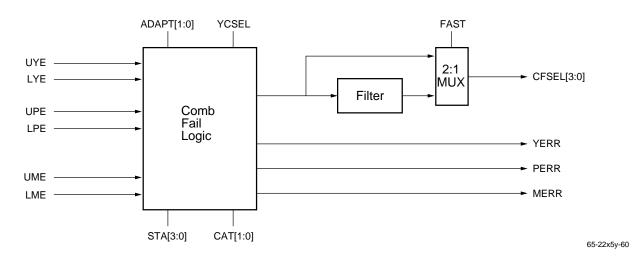

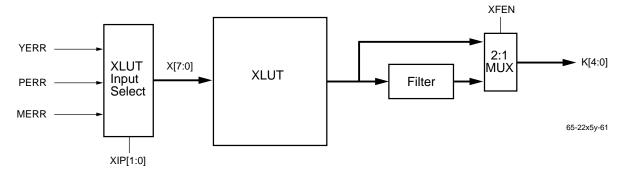

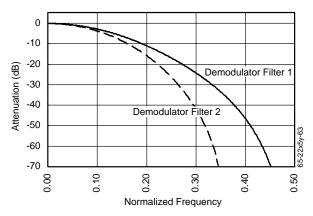

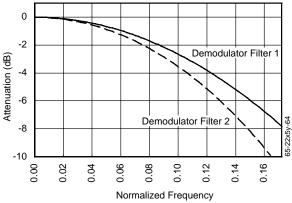

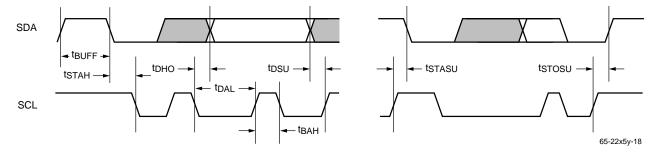

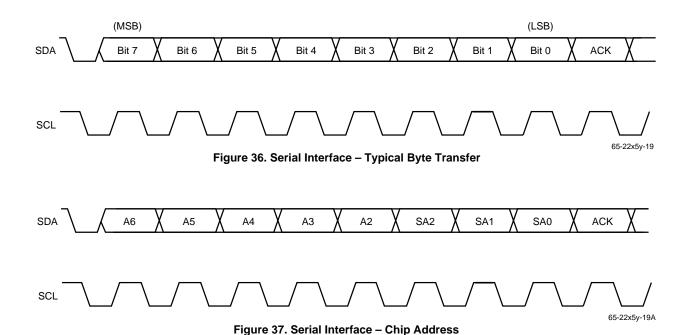

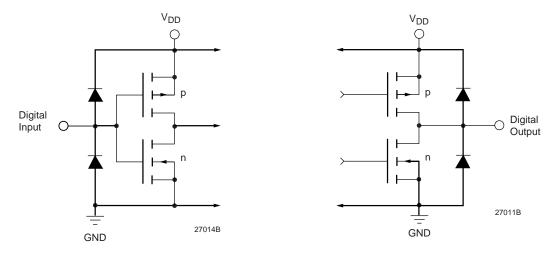

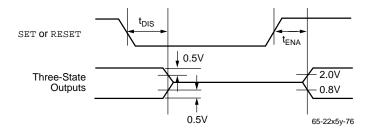

| OF 4 DCES D1 CBCR error signal OF 3-2 IPCF Comb filter input select OF 1 YCCOMP YC or Composite input select OF 0 SYNC Sync processor select  Sync Pulse Generator  10 7-0 STS7-0 Sync to sync 8 lsbs 11 7-0 STB Sync to burst 12 7-0 BTV Burst to video 13 7-0 AV7-0 Active video line 8 lsbs 14 7-6 reserved, set to zero 14 5-4 AV9-8 Active video line 2 msbs 15 7 reserved, set to zero 16 6-2 VINDO Number of lines in vertical window 17 7-0 MSIP Mixed sync separator input select  Buffered register set 0 Active when BUFFER pin set LOW 17 7-0 SG07-0 Msync gain, 8 lsbs 18 7-0 YG07-0 Y gain, 8 lsbs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0F  | 7          |                     | reserved, set to zero    |