# ICs for Communications

Multichannel Network Interface Controller for HDLC MUNICH32

PEB 20320 Version 3.4

User's Manual 01.2000

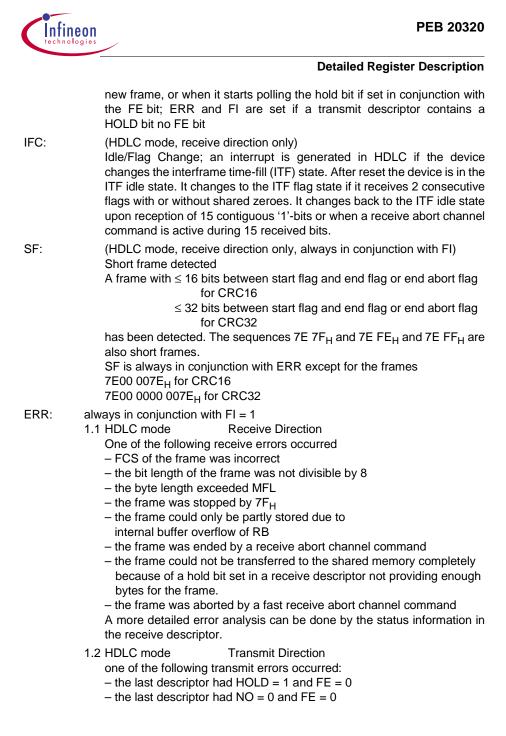

DS3

| PEB 20320                                                       |       |                                                  |  |  |

|-----------------------------------------------------------------|-------|--------------------------------------------------|--|--|

| Revision History:                                               |       | Current Version: 01.2000                         |  |  |

| Previous Ver                                                    | sion: | User's Manual 1998-06-01 DS2 (V3.4)              |  |  |

| Page<br>(in previous<br>Version)Page<br>(in current<br>Version) |       | Subjects (major changes since last revision)     |  |  |

|                                                                 |       | Package P-TQFP-176-1 removed from User's Manual. |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE<sup>TH</sup>, ASM<sup>TH</sup>, ASP<sup>TH</sup>, POTSWIRE<sup>TH</sup>, QuadFALC<sup>TH</sup>, SCOUT<sup>TH</sup> are trademarks of Infineon Technologies AG.

#### Edition 01.2000 Published by Infineon Technologies AG, SC, Balanstraße 73, 81541 München © Infineon Technologies AG 2000. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

**Components used in life-support devices or systems must be expressly authorized for such purpose!** Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

## Preface

The Multichannel Network Interface Controller for HDLC (MUNICH32) is a Multichannel Protocol Controller for a wide area of telecommunication and data communication applications.

#### **Organization of this Document**

This User's Manual is divided into 9 chapters. It is organized as follows:

- Chapter 1, Introduction Gives a general description of the product and its family, lists the key features, and presents some typical applications.

- Chapter 2, Functional Description This chapter provides a detailed description of the interfaces and the protocol modes.

- Chapter 3, Operational Description Provides a description of MUNICH32 reset procedure and initialization.

- Chapter 4, Detailed Register Description Gives a detailed description of the shared memory organization.

- Chapter 5, Application Notes

- Chapter 6, Application Hints

- Chapter 7, Electrical Characteristics Gives a detailed description of all electrical DC and AC characteristics and provides timing diagrams and values for all interfaces.

- Chapter 8, Package Outlines

- Chapter 9, Appendix This chapter provides source code examples.

#### **Your Comments**

We welcome your comments on this document as we are continuously aiming at improving our documentation. Please send your remarks and suggestions by e-mail to

sc.docu\_comments@infineon.com

Please provide in the subject of your e-mail:

device name (MUNICH32), device number (PEB 20320), device version (Version 3.4), and in the body of your e-mail:

document type (User's Manual), issue date (01.2000) and document revision number (DS3).

3

User's Manual

User's Manual

4

| Table of                                                                                          | Contents Page                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                                | Introduction.7Features.8Pin Configuration.11Pin Definitions and Functions.12Logic Symbol.22Functional Block Diagram.23System Integration.25                                                                                                                                                                                                                                                                                                         |

| <b>2</b><br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.4<br>2.5                            | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>3</b><br>3.1<br>3.2                                                                            | Operational Description       .131         Reset State       .131         Initialization Procedure       .132                                                                                                                                                                                                                                                                                                                                       |

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.3<br>4.4        | Detailed Register Description134Organization of the Shared Memory134Control and Configuration Section136Action Specification (Read Once After Each Action Request Pulse)136Interrupt Queue Specification140Interrupt Information141Time Slot Assignment148Channel Specification149Current Receive and Transmit Descriptor Address161Transmit Descriptor162Receive Descriptor168                                                                     |

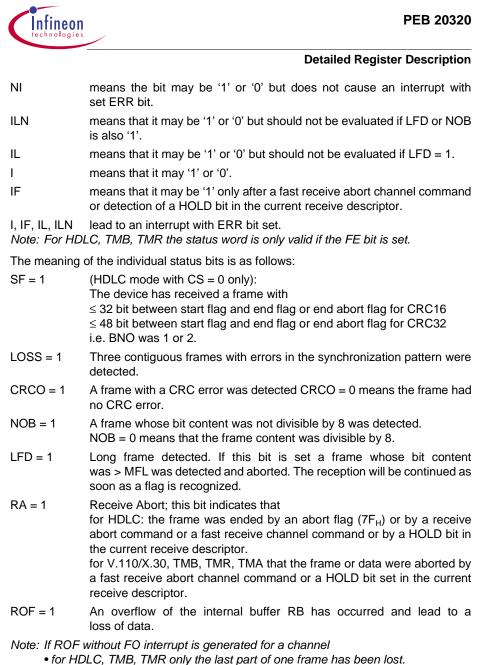

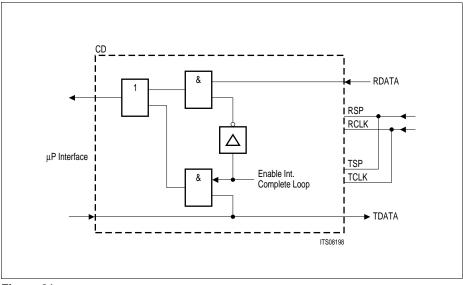

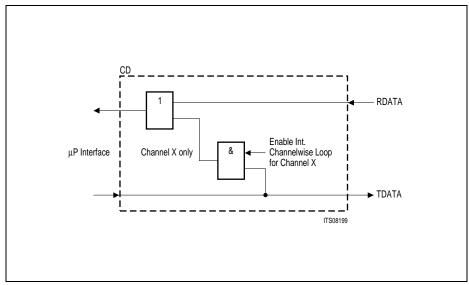

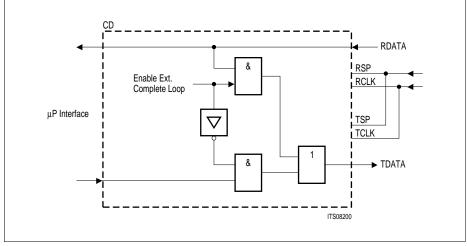

| <b>5</b><br>5.1<br>5.1.1<br>5.1.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.2<br>5.1.3<br>5.1.3.1 | Application Notes       173         Test Loops       173         Test Loop Definitions for the MUNICH32       173         Internal Complete Test Loop       173         Internal Channelwise Test Loop       174         External Complete Test Loop       174         External Channelwise Test Loop       174         Test Loop Activation       176         Test Loop Deactivation and Switching       176         Software Operations       177 |

User's Manual

5

#### **Table of Contents** Page 5.1.3.2 5.1.4 5.1.4.1 Internal Channelwise Test Loop ......178 5.1.4.2 5.2 5.2.1 5.2.2 5.2.3 Device Driver Module MUNICH32 .....191 5.2.3.1 5.2.3.2 Application Module MROUTE .....194 5.2.4 5.2.5 5.2.6 5.2.7 5.3 5.3.1 5.3.2 6 6.1 6.2 6.3 6.3.1 6.3.2 7 7.1 Absolute Maximum Ratings 7.2 7.3 74 7.5 7.6 8 9 9.1 Source Code Extract MUNICH32 ......243 9.2

6

User's Manual

#### Introduction

#### 1 Introduction

The Multichannel Network Interface Controller for HDLC (MUNICH32) is a Multichannel Protocol Controller, which handles up to 32 data channels of a full duplex PCM highway. It performs layer 2 HDLC formatting/deformatting or V.110 and X.30 protocols up to a network data rate of 38.4 Kbit/s as well as transparent transmission for the DMI mode 0, 1 and 2. The processed data is passed on to an external memory shared with one or more host processors.

MUNICH32 is compatible with the LAPD ISDN (Integrated Services Digital Network) protocol specified by CCITT as well as with HDLC, SDLC, LAPB DMI protocols. It provides any rate adaption for time slot transmission data rate from 64 Kbit/s down to 8 Kbit/s and the concatenation of any time slots to data channels, supporting the ISDN H0, H11, H12 superchannels.

Due to these functions the MUNICH32 can be used in a wide area of telecommunication and data communication applications, e.g. in central office switches, for the connection of a digital PABX to a host computer, as a central D-channel controller to 32 ISDN basic access D-channels or as a multiplexer for terminals and other peripherals. Up to 4 MUNICH32s can be connected to one PCM highway, so a D-channel controller with 128 channels can be achieved.

7

User's Manual

# Multichannel Network Interface Controller for HDLC MUNICH32

**PEB 20320**

#### Version 3.4

CMOS

#### 1.1 Features

- Serial Interface

- Up to 32 independent communication channels.

- Serial multiplexed (full duplex) input/output for 2048-, 4096-, 1544- or 1536-Kbit/s PCM highways.

- Dynamic Programmable Channel Allocation

- Compatible with T1/DS1 24-channel and CEPT 32-channel PCM byte format.

- Concatenation of any, not necessarily consecutive, time slots to superchannels independently for receive and transmit direction.

- Support of H0, H11, H12 ISDN-channels.

- Subchanneling on each time slot possible.

- Bit Processor Functions (adjustable for each channel)

- HDLC Protocol

- Automatic flag detection and transmission

- Shared opening and closing flag

- Detection of interframe-time-fill change, generation of interframe-time-fill '1's or flags

- Zero bit insertion

- Flag stuffing and flag adjustment for rate adaption

- CRC generation and checking (16 or 32 bits)

- Transparent CRC option per channel and/or per message

- Error detection (abort, long frame, CRC error, 2 categories of short frames, non-octet frame content)

- Special short frame mode to allow reception of 'frames' with a least on byte length

- ABORT/IDLE generation

| Туре      | Package      |

|-----------|--------------|

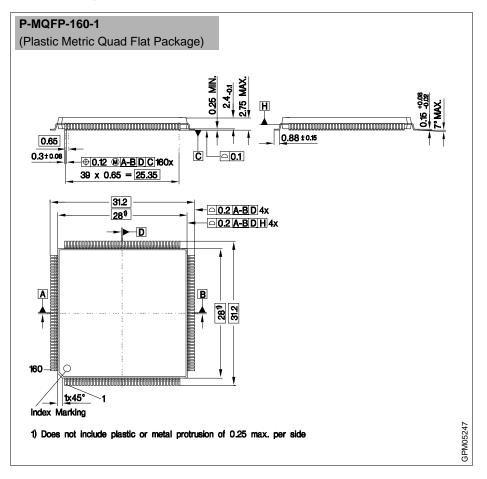

| PEB 20320 | P-MQFP-160-1 |

User's Manual

#### Introduction

- V.110/X.30 Protocol

- Automatic synchronization in receive direction, automatic generation of the synchronization pattern in transmit direction

- E / S / X bits freely programmable in transmit direction, van be changed during transmission; changes monitored and reported in receive direction

- Generation/detection of loss of synchronism

- Bit framing with network data rates from 600 bit/s up to 38.4 Kbit/s

- Transparent Mode A

- Slot synchronous transparent transmission/reception without frame structure

- Bit-overwrite with fill/mask bits

- Flag generation, flag stuffing, flag extraction, flag generation in the abort case with programmable flag

- Transparent Mode B

- Transparent transmission/reception in frames delimited by 00<sub>H</sub> flags

- Shared opening and closing flag

- Flag stuffing, flag detection, flag generation in the abort case

- Error detection (non octet frame content, short frame, long frame)

- Transparent Mode R

- Transparent transmission/reception with GSM 08.60 frame structure

- Automatic 0000<sub>H</sub> flag generation/detection

- Support of 40,  $39^{1}/_{2}$ ,  $40^{1}/_{2}$  octet frames

- Error detection (non octet frame content, short frame, long frame)

- Protocol Independent

- Channel inversion (data, flags, IDLE code)

- Format conventions as in CCITT Q.921 § 2.8

- Data over- and underflow detected

- Processor Interface

- ON-CHIP 64-channel DMA controller with buffer chaining capability.

- Compatible with Motorola 68020 processor family and

- Intel 32-bit processor (80386).

- 32 bit data bus and 32 bit address bus (4 Gbyte RAM addressable, Motorola and Intel non-parity) or 28 bit address bus (256 Mbyte RAM addressable, Intel parity)

- Intel parity mode with data byte parity (4 parity bits)

- Parity check for read accesses

- Parity generation for write accesses

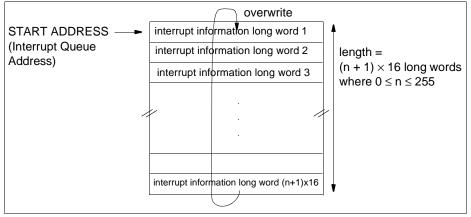

- Interrupt-circular buffer with variable size

- Maskable interrupts for each channel

- μP interface buffer of depth 16 long words for adaptive bus occupation

User's Manual

9

#### Introduction

- General

- Connection of up to four MUNICH32 supporting a 128-channel basic access D-channel controller.

- ON-CHIP receive and transmit data buffer; the buffer size is 256 bytes each.

- HDLC protocol or transparent mode, support of ECMA 102, CCITT I4.63 RA2,

- V.110, X.30, DMI mode 0, 1, 2 (bit rate adaption), GSM 08.60 TRAU frames.

10

- LOOP mode, complete loop as well as single channel loop

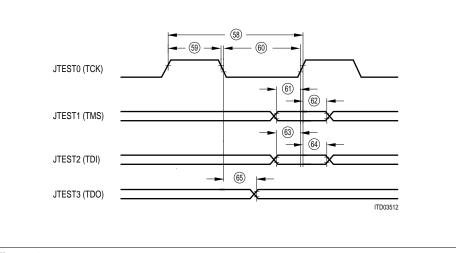

- JTAG boundary scan test

- Advanced low-power CMOS technologyTTL-compatible inputs/outputs

- 160 pin P-MQFP package

User's Manual

#### Introduction

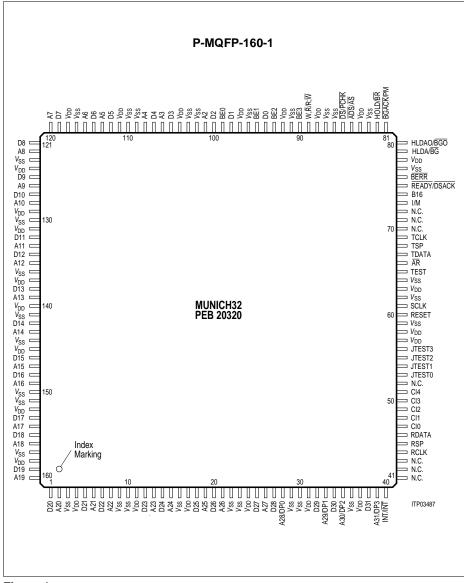

1.2 Pin Configuration (top view)

User's Manual

11

#### Introduction

#### 1.3 Pin Definitions and Functions

Pin Definitions and Functions

| Pin No.<br>P-MQFP-160-1                                                                                                                                       | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83, 87, 88, 92,<br>97, 103, 104,<br>110, 111, 117,<br>123, 130, 136,<br>141, 144, 150,<br>151, 157, 3, 9,<br>10, 16, 22, 23,<br>29, 30, 36, 59,<br>62, 64, 77 | V <sub>SS</sub> | 1                       | <b>Ground</b> (0 V)<br>All pins must have the same level.                                                                                                                                                                                                                                                                                          |

| 73                                                                                                                                                            | I/M             | 1                       | Intel Bus Mode or Motorola Bus Mode<br>By connecting this pin to either $V_{SS}$ or $V_{DD}$<br>the bus interface can be adapted to either<br>Intel or Motorola environment. The data is<br>interpreted either in Intel or Motorola<br>manner; i.e. little or big endian convention.<br>I/M = low: Intel bus mode<br>I/M = high: Motorola bus mode |

| 39                                                                                                                                                            | A31<br>DP3      | 0<br>I/O                | Address Bit 31<br>(Intel non-parity/Motorola) tristate when<br>unused.<br>Data Parity 3 (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(31:24).                                                                                                                                                       |

| 35                                                                                                                                                            | A30<br>DP2      | 0<br>I/O                | Address Bit 30<br>(Intel non-parity/Motorola) tristate when<br>unused.<br>Data Parity 2 (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(23:16).                                                                                                                                                       |

Note: Input pins that are unused in a specific configuration must be strapped to  $V_{ss}$ . I/O or output pins that are unused in a specific configuration must be left open!

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1                                                                                                                    | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                                                                                                                                         | A29     | 0                       | Address Bit 29<br>(Intel non-parity/Motorola) tristate when<br>unused.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                            | DP1     | I/O                     | <b>Data Parity 1</b> (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(15:8)                                                                                                                                                                                                                                                                                                                                                                     |

| 28                                                                                                                                         | A28     | 0                       | Address Bit 28<br>(Intel non-parity/Motorola) tristate when<br>unused                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                            | DP0     | I/O                     | <b>Data Parity 0</b> (Intel parity mode),<br>bidirectional tristate line containing/<br>expecting parity bit of D(7:0)                                                                                                                                                                                                                                                                                                                                                                      |

| 26, 21, 19, 15,<br>13, 8, 6, 2, 160,<br>156, 154, 149,<br>147, 143, 139,<br>135, 133, 128,<br>126, 122, 120,<br>116, 114, 109,<br>107, 102 | A(27:2) | 0                       | Address Bus<br>tristate when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 91, 94, 96, 100                                                                                                                            | BE(3:0) | 0                       | Byte Enable (Intel bus mode)<br>The MUNICH32 provides word and long<br>word transfer. The byte enables determine<br>the address offset to the address<br>A31 A2, the actual word has been<br>stored to.<br>Address Offset Size (Motorola mode)<br>Indicates the number of bytes remaining to<br>be transferred for this access. These<br>signals define the active sections of the<br>data bus.<br>In both cases these signals are tristate<br>when unused.<br>See Chapter 2.2 for details. |

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1                                                                                                                                          | Symbol          | Input (I)<br>Output (O) | Function                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38, 34, 32, 27,<br>25, 20, 18, 14,<br>12, 7, 5, 1, 159,<br>153, 148, 146,<br>142, 138, 134,<br>132, 127, 125,<br>121, 119, 115,<br>113, 108, 106,<br>101, 99, 95 | D(31:0)         | I/O                     | <b>Data Bus</b><br>The data bus lines are bidirectional tristate<br>lines which interface with the system's<br>data bus.                                                                              |

| 86                                                                                                                                                               | DS              | 0                       | <b>Data Strobe</b> (Motorola mode)<br>This signal indicates that valid data is to be<br>placed on the data bus (read cycle) or has<br>been placed on the data bus by the<br>MUNICH32 (write cycle).   |

|                                                                                                                                                                  | РСНК            | Ο                       | <b>Parity Check</b> (Intel parity mode)<br>This signal indicates, whether the parity<br>bits of a read cycle are valid (PCHK high)<br>or invalid (PCHK low). See <b>Chapter 2.2.1</b><br>for details. |

| 84, 93, 89, 98,<br>105, 112, 118,<br>124, 129, 131,<br>137, 140, 145,<br>152, 158, 4, 11,<br>17, 24, 31, 37,<br>57, 58, 63, 78                                   | V <sub>DD</sub> | I                       | Supply voltage 5 V $\pm$ 5%<br>All pins must have the same level.                                                                                                                                     |

| 85                                                                                                                                                               | ADS             | 0                       | Address Status (Intel bus mode)<br>This signal indicates that a valid bus cycle<br>definition and address are being driven at<br>the pins.                                                            |

|                                                                                                                                                                  | ĀS              | Ο                       | Address Strobe (Motorola bus mode)A valid address is transmitted on theaddress bus at the falling edge of AS.In both cases this signal is active low andtristate when unused.                         |

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|--------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90                      | W/R    | 0                       | Write/Read (Intel bus mode)<br>This signal distinguishes write from read<br>operations.                                                                                                                                                                                                                                                                                                                |

|                         | R/W    | 0                       | <b>Read/Write</b> (Motorola bus mode)<br>This signal distinguishes between read<br>and write operations.<br>In both cases this signal is tristate when<br>unused.                                                                                                                                                                                                                                      |

| 75                      | READY  | I                       | <b>Ready</b> (Intel bus mode)<br>This signal indicates that the current bus<br>cycle is complete. When READY is<br>asserted during a read cycle the<br>MUNICH32 latches the input data and<br>terminates the cycle. When READY is<br>asserted during a write cycle the<br>MUNICH32 terminates the cycle.                                                                                               |

|                         | DSACK  | Ι                       | <b>Data Transfer Acknowledge</b> (Motorola<br>bus mode)<br>This active low input indicates that a data<br>transfer may be performed. During a read<br>cycle data becomes valid at the falling<br>edge of DSACK. The data is latched<br>internally and the bus cycle is terminated.<br>During a write cycle the falling edge of<br>DSACK marks the latching of data and the<br>bus cycle is terminated. |

15

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 76                      | BERR   | Ι                       | <b>Bus Error</b> (Intel and Motorola bus mode)<br>This active low signal informs the<br>MUNICH32 that a bus cycle error has<br>occurred. The MUNICH32 terminates the<br>bus cycle.<br>In case of an erroneous read cycle in the<br>control and configuration section an<br>'Action Request Fail' interrupt is generated<br>and the action is suspended. In case of an<br>erroneous read cycle in the transmit data<br>section the corresponding frame is<br>aborted and a FO interrupt is generated. In<br>all other cases of read or write cycles<br>terminated with an error condition no<br>further actions are performed by the<br>MUNICH32. Please see <b>Chapter 2.2</b> ,<br>'Microprocessor Interface', first paragraph<br>and <b>Figure 18</b> .<br>As bus cycles are executed without time<br>limit this signal prevents a hang-up<br>situation of the MUNICH32. |

| 74                      | B16    | 1                       | <b>Word Operation</b><br>Setting this bit to $V_{DD}$ causes the<br>MUNICH32 to perform 32-bit long word<br>accesses to the shared memory, setting it<br>to $V_{SS}$ causes the MUNICH32 to perform<br>16-bit word accesses on the data lines<br>D(15:0) only. In 16-bit word access mode<br>the data lines D(31:16) should be left<br>open.<br>This bit is <b>not</b> dynamic and should be set<br>to $V_{DD}$ in Intel parity mode.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

16

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                   |

|-------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82                      | HOLD   | 0                       | <b>Bus Hold Request</b> (Intel bus mode)<br>This signal is driven high when the<br>MUNICH32 requests the control of the<br>bus.                                                                                                                                            |

|                         | BR     | I/O                     | <b>Bus Request</b> (Motorola bus mode)<br>This signal is driven low when the<br>MUNICH32 requests the control of the bus<br>and is interpreted when another<br>MUNICH32 wants to be the bus master.                                                                        |

| 79                      | HLDA   | I                       | <b>Bus Hold Acknowledge</b> (Intel bus mode)<br>This active high signal indicates that the<br>processor has released the control of the<br>bus. The MUNICH32 starts the bus cycles.                                                                                        |

|                         | BG     | I                       | <b>Bus Grant</b> (Motorola bus mode)<br>This active low signal indicates that the<br>MUNICH32 may assume the bus<br>mastership.                                                                                                                                            |

| 81                      | BGACK  | I/O                     | Bus Grant Acknowledge (Motorola bus<br>mode)<br>This signal is driven low by the device,<br>when it has become the bus master. It also<br>informs the MUNICH32 whether another<br>device is bus master.                                                                    |

|                         | РМ     | I                       | <b>Parity Mode</b> (Intel bus mode)<br>This signal has to be strapped to $V_{\rm DD}$<br>before reset to enable the Intel parity<br>mode or to $V_{\rm SS}$ before reset to enable the<br>Intel non-parity mode. It has to be left<br>strapped during reset and operation. |

User's Manual

17

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80                      | HLDAO  | 0                       | Bus Hold Acknowledge Passing ON<br>(Intel bus mode)<br>If another MUNICH32 has initiated a<br>HOLD REQUEST the HOLD<br>ACKNOWLEDGE is passed on via<br>HLDAO. The MUNICH32 does not give<br>another HOLD REQUEST before the<br>HOLD ACKNOWLEDGE has been<br>deactivated in order to prevent blocking in<br>the case of continuous request by one<br>MUNICH32.          |

|                         | BGO    | 0                       | <b>Bus Grant Acknowledge</b> (Motorola bus<br>mode)<br>If the MUNICH32 has not requested the<br>bus mastership it passes on the BUS<br>GRANT. The MUNICH32 does not give<br>another BUS REQUEST before the BUS<br>REQUEST and the BUS GRANT<br>ACKNOWLEDGE have been deactivated<br>in order to prevent blocking in the case of<br>continuous request by one MUNICH32. |

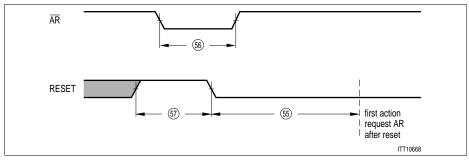

| 66                      | ĀR     | Ι                       | Action Request<br>AR must be pulsed low to cause an action<br>of the MUNICH32. The AR is activated for<br>updating the mode and channel<br>configurations, setting a test loop, or<br>initializing the interrupt queue. The<br>min. time between Reset and first AR is<br>500 μs.                                                                                      |

18

User's Manual

#### Introduction

## Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40                      | INT/INT | 0                       | Interrupt Request<br>An interrupt is given when a transmission/<br>reception error is detected, frames are<br>received or transmitted, or a host initiated<br>action is performed. The interrupt pulse<br>signal interacts with a write cycle to the<br>shared memory. The data written into the<br>interrupt queue contains the interrupt<br>specification.<br>The interrupt is active high for Intel bus<br>mode and active low for Motorola bus<br>mode. |

| 44                      | RCLK    | I                       | Receive Clock<br>This clock provides the data clock for RDA<br>T1/DS1 24-channel 1.544 MHz<br>24-channel 1.536 MHz<br>CEPT 32-channel 2.048 MHz<br>32-channel 4.096 MHz                                                                                                                                                                                                                                                                                     |

| 45                      | RSP     | I                       | <b>Receive Synchronization Pulse</b><br>This signal provides the reference for the<br>receive PCM frame synchronization. It<br>marks the first bit in the PCM frame.                                                                                                                                                                                                                                                                                        |

| 46                      | RDATA   | Ι                       | <b>Receive Data</b><br>Serial data is received at this PCM input<br>port. The MUNICH32 supports the T1/<br>DS1 24-channel PCM format, the CEPT<br>32-channel PCM format as well as a 32-<br>channel PCM format with 4.096-Mbit/s bit<br>rate.                                                                                                                                                                                                               |

| 61                      | SCLK    | Ι                       | System ClockPCM highway system clock highwayfrequency32-channel16.384 MHz2.048 or4.096 MHz24-channel12.288 MHz1.536 MHz24-channel12.352 MHz1.544 MHz                                                                                                                                                                                                                                                                                                        |

User's Manual

19

### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1 | Symbol         | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51 47                   | CI(4:0)        | I                       | Chip Identification<br>Up to four MUNICH32 can be connected<br>to the PCM highway. These inputs define<br>the start address of the control section<br>pointer in the shared memory.<br>Cl4 is the polarity of A31 A22<br>Cl3 is the polarity of A21 A16<br>Cl2 is the polarity of A15 A4<br>Cl1 is the polarity of A3<br>Cl0 is the polarity of A2<br>A1, A0 are always '00' |

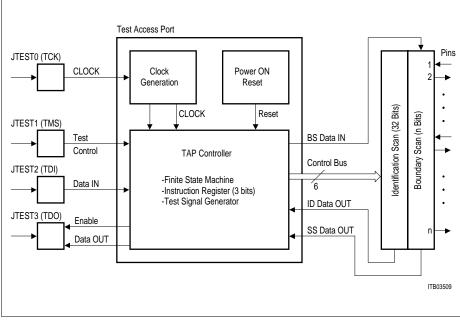

| 56 53                   | JTEST<br>(3:0) | I/O                     | <b>Test Pins</b><br>The MUNICH32 supports the JTAG<br>boundary scan test and the JTAG test<br>standards.                                                                                                                                                                                                                                                                     |

| 65                      | TEST           | Ι                       | <b>Test</b><br>If this bit is set to $V_{\rm DD}$ MUNICH32 works in<br>a test mode.<br>For the functional working mode this bit<br>must be set to $V_{\rm SS}$ .                                                                                                                                                                                                             |

| 67                      | TDATA          | 0                       | <b>Transmit Data</b><br>Serial data is sent by this PCM output port<br>is push-pull for active bits in the PCM<br>frame and tristate for inactive bits.                                                                                                                                                                                                                      |

| 68                      | TSP            | I                       | <b>Transmit Synchronization Pulse</b><br>This signal provides the reference for the<br>transmit frame synchronization. It marks<br>the last bit in the PCM frame.                                                                                                                                                                                                            |

| 69                      | TCLK           | I                       | Transmit Clock<br>This clock provides the data clock for<br>TDATA<br>T1/DS1 24-channel 1.544 MHz<br>24-channel 1.536 MHz<br>CEPT 32-channel 2.048 MHz<br>32-channel 4.096 MHz                                                                                                                                                                                                |

User's Manual

#### Introduction

Pin Definitions and Functions (cont'd)

| Pin No.<br>P-MQFP-160-1       | Symbol | Input (I)<br>Output (O) | Function                                                                    |

|-------------------------------|--------|-------------------------|-----------------------------------------------------------------------------|

| 60                            | RESET  | I                       | Reset                                                                       |

| 41, 42, 43, 52,<br>70, 71, 72 | N.C.   |                         | <b>No Connect</b><br>These pins are reserved and should not be<br>connected |

21

User's Manual

#### Introduction

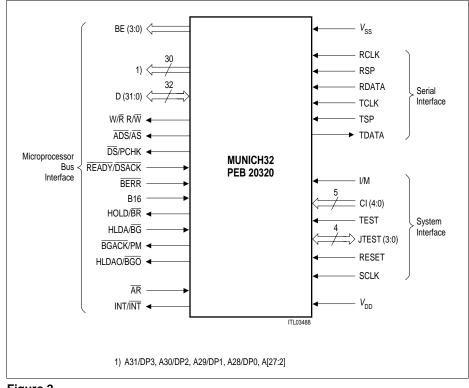

#### 1.4 Logic Symbol

Figure 2 MUNICH32 Logic Symbol

User's Manual

22

#### Introduction

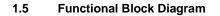

#### Figure 3 Block Diagram of MUNICH32

User's Manual

23

#### Introduction

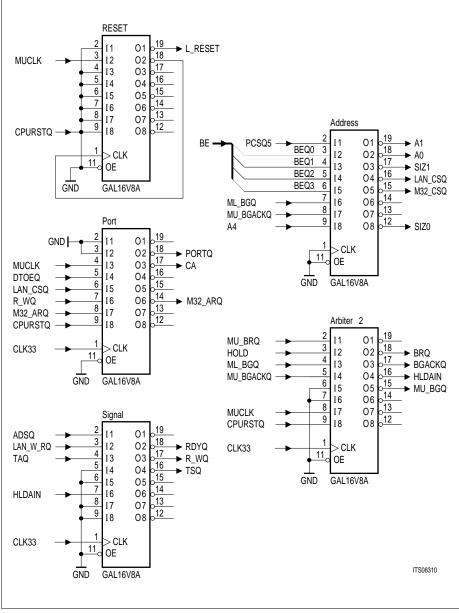

The internal functions of MUNICH32 are partitioned into 8 major blocks.

- 1. Serial Interface, Formatter Control Unit CD

- Parallel-Serial conversion, PCM timing, switching of the test loops, controlling of the multiplex procedure.

- 2. Transmit Formatter TF

- HDLC frame, bit stuffing, flag generation, flag stuffing and adjustment,

CRC generation, transparent mode transmission and V.110, X.30 80 bit framing.

- 3. Transmit Buffer TB

- Buffer size of 64 long words allocated to the channels, i.e. eight PCM frames can be stored before transmission, individual channel capacity programmable.

- 4. Receive Deformatter RD

- HDLC frame, zero-bit deletion, flag detection, CRC checking, transparent mode reception and V.110, X.30 80 bit framing.

- 5. Receive Buffer RB

- Buffer size of 64 long words allocated to the channels, i.e. eight PCM frames can be stored, individual long words are freely accessible by each channel.

- 6. Configuration and State RAM CSR

- Since the Transmit Formatter, Receive Deformatter are used in a multiplex manner, the state and configuration information of each channel has to be stored.

- 7. DMA Controller CM

- Interrupt processing, memory address calculation, chaining list handling, chip configuration.

- 8. µP interface MI

- Motorola/Intel microprocessor interface.

#### Introduction

#### 1.6 System Integration

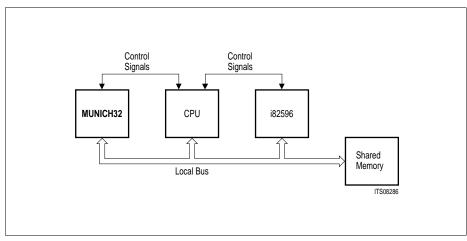

The MUNICH32 is designed to handle up to 32 data channels of a PCM highway. It transfers the data between the PCM highway and a memory shared with a host processor via a 32-bit  $\mu$ P interface. At the same time it performs protocol formatting and deformatting as well as rate adaption for each channel independently. The host sets the operating mode, bit rate adaption method and time slot allocation of each channel by writing the information into the shared memory.

Using subchanneling each time slot can be shared between up to four MUNICH32s; so that in one single time slot four different D-channels can be handled by four MUNICH32s.

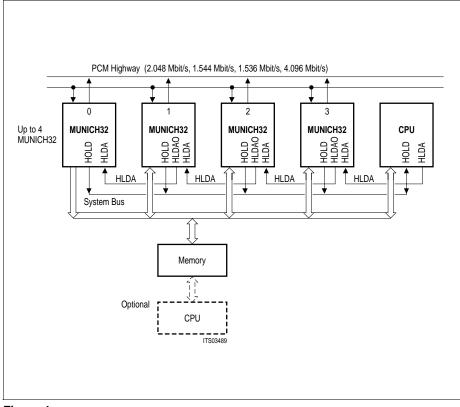

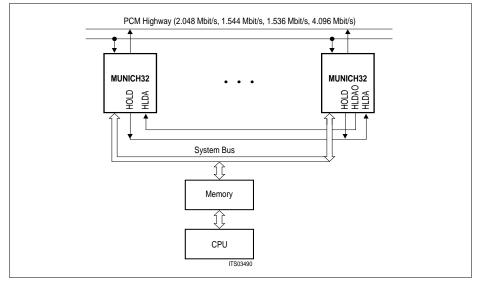

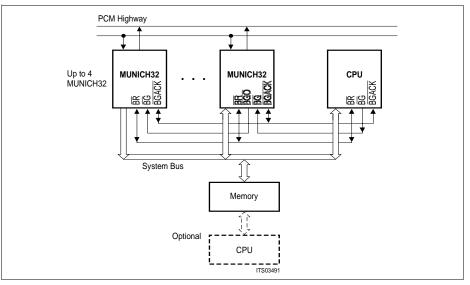

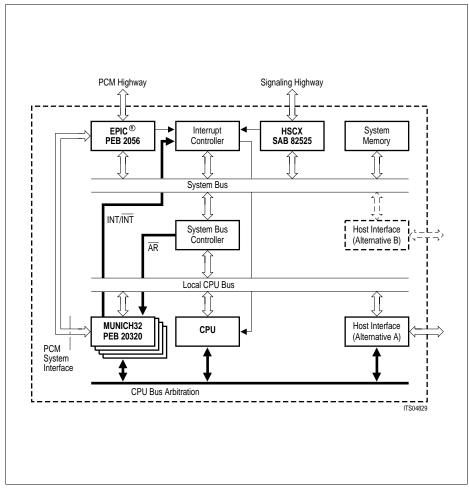

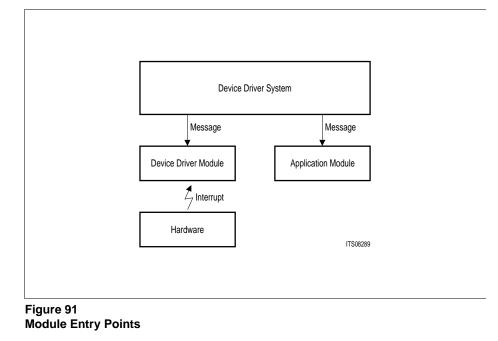

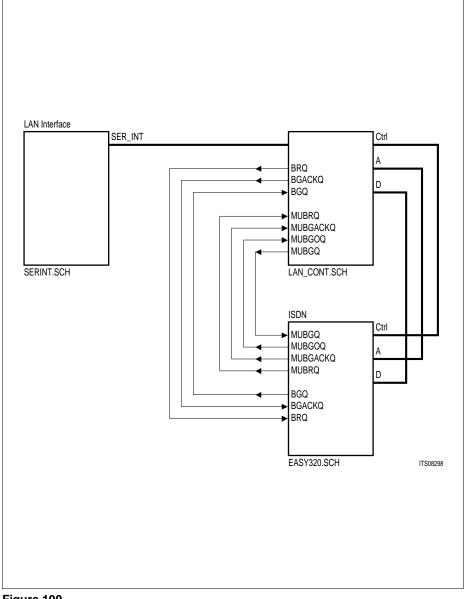

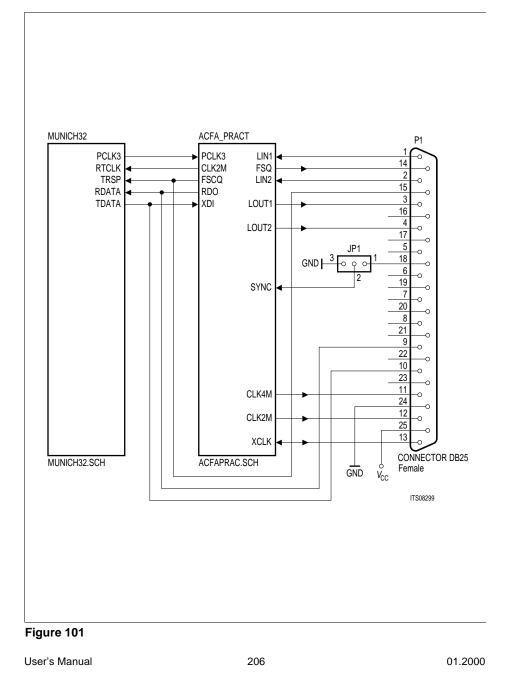

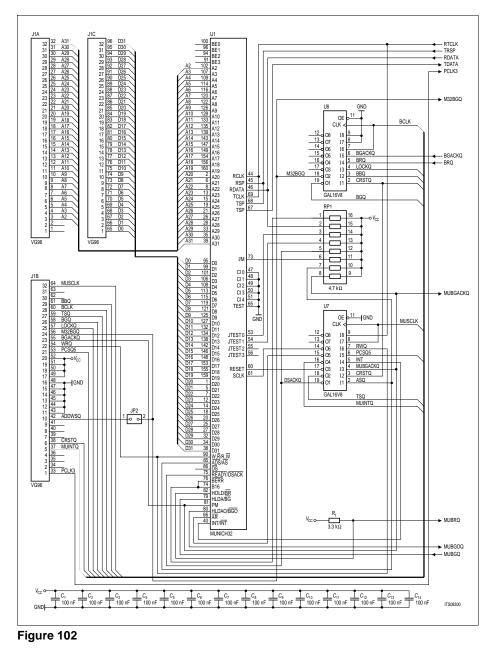

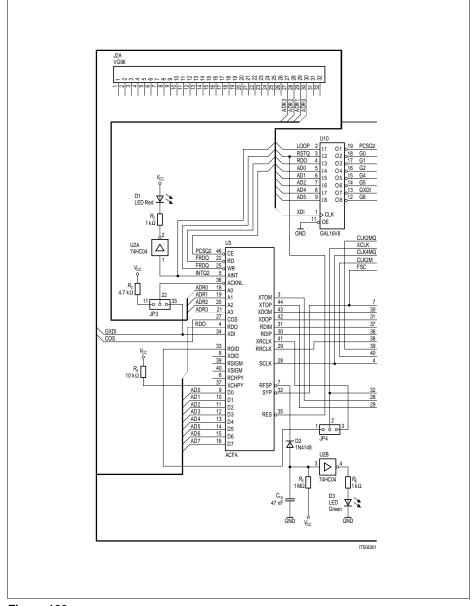

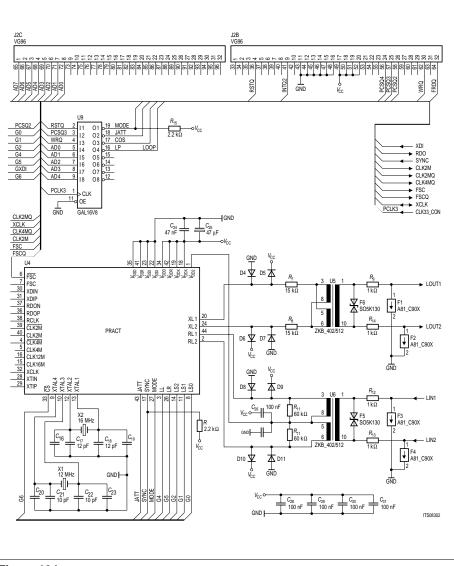

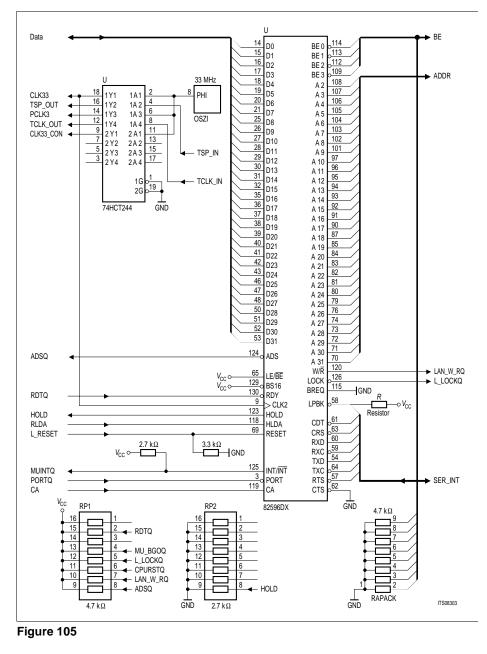

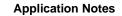

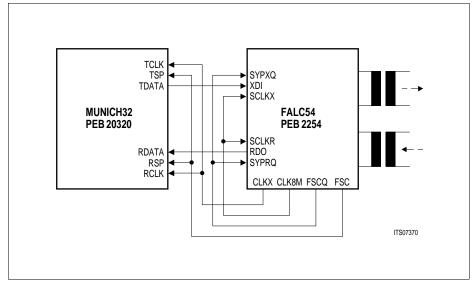

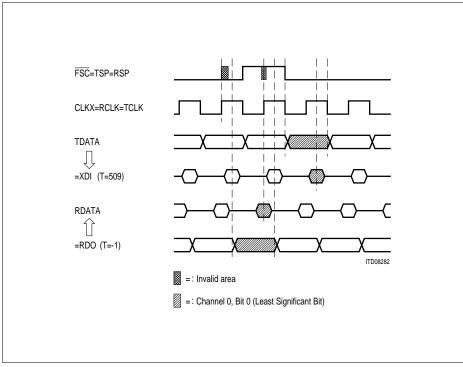

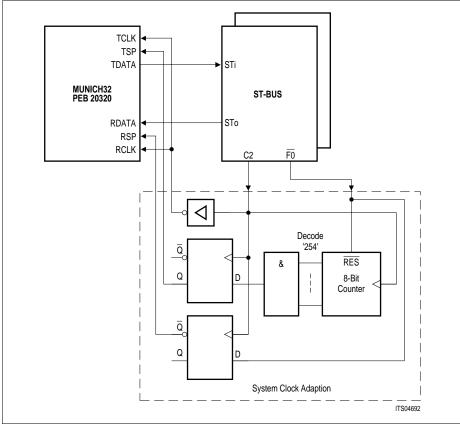

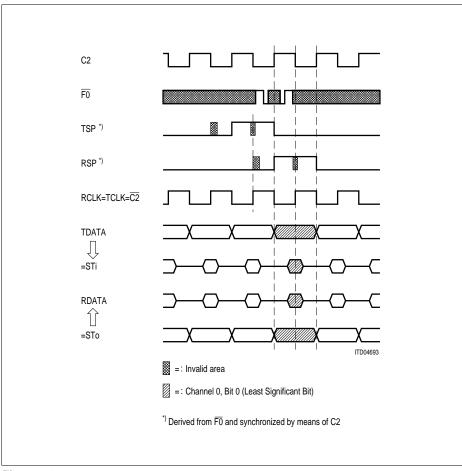

Figure 4, Figure 5 and Figure 6 give a general overview of system integration of the MUNICH32.

Figure 4 General System Integration (Intel Bus Mode)

User's Manual

25

#### Introduction

#### Figure 5 General System Interface (Intel Bus Mode)

#### Figure 6 General System Interface (Motorola Bus Mode)

User's Manual

26

#### Introduction

MUNICH32's bus interface consists of a 32 bit bidirectional data bus (D31 ... D0), 32/28 Address lines (A31 ... A2, BE3 ... BE0) or (A27 ... A2, BE3 ... BE0), four data byte parity lines DP(3:0), five lines (W/R/R/W, ADS/AS, DS/PCHK, BERR READY/DSACK) to control and monitor the bus cycle, one action request and one Interrupt line.

The system bus allocation is controlled by the four signals (HOLD/BR, HLDA/BG, BGACK, HLDAO/BGO). A mode pin allows the bus interface to be configured for either Intel or Motorola mode. An operation mode pin B16 enables the transfer of a 32 bit long word in two consecutive 16 bit word operations.

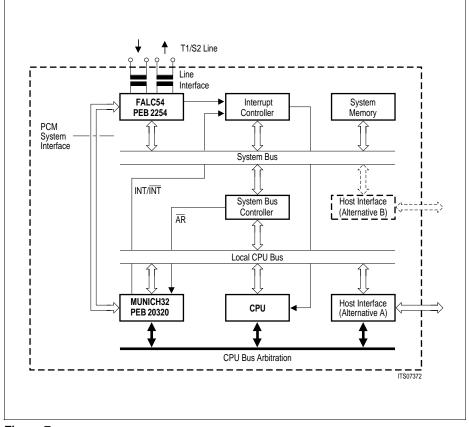

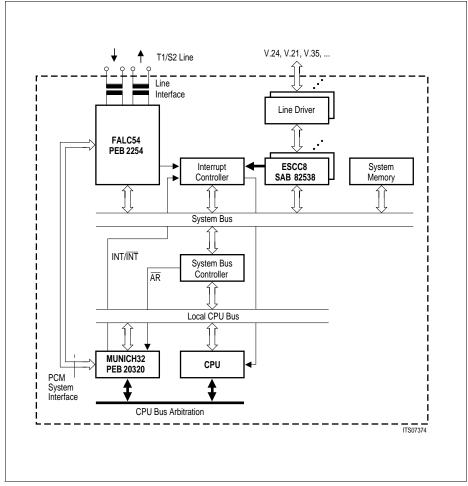

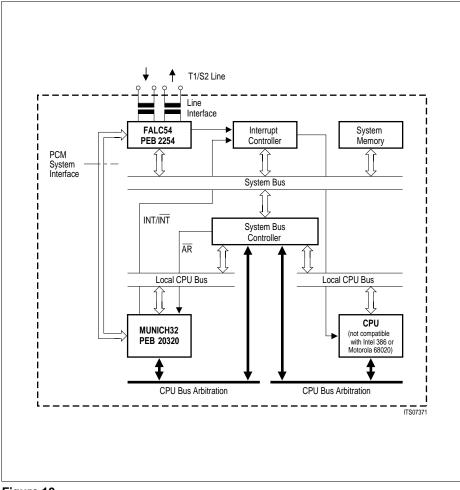

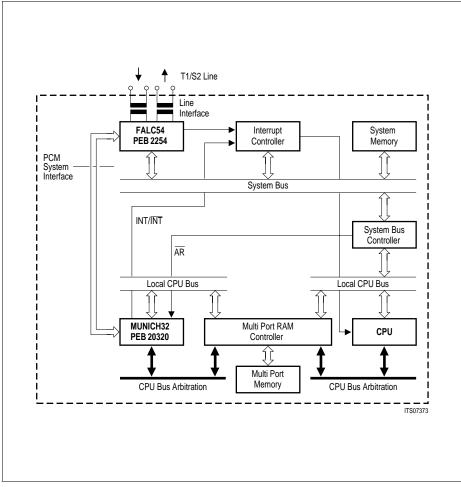

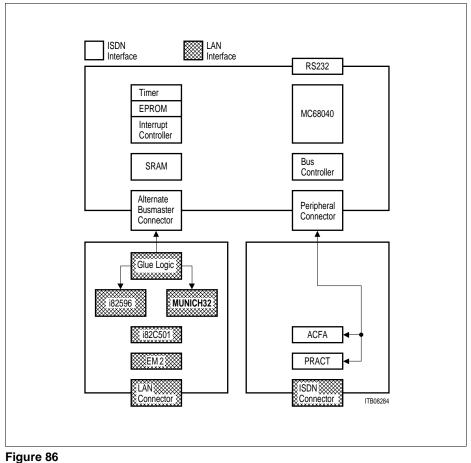

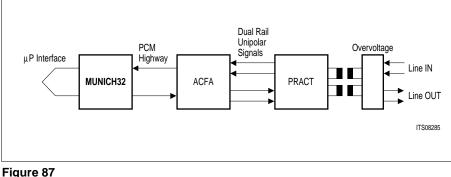

**Figure 7, Figure 8, Figure 9, Figure 10** and **Figure 11** illustrate how the MUNICH32 may be used in different applications, like in a Primary Rate Interface, a Router, a Packet Switch and a Central D-Channel Handler, as part of an ISDN switching system.

Figure 7 Architecture of a Primary Access Board

User's Manual

27

Introduction

#### Figure 8 Architecture of a Central D-Channel Handler

User's Manual

28

Introduction

#### Figure 9 Architecture of a Packet Switch/Router

User's Manual

29

#### Introduction

#### Figure 10 MUNICH32 in a System with a RISC CPU

Note: To reduce complexity the host interface is not explicitly shown here.

User's Manual

30

#### Introduction

#### Figure 11 MUNICH32 in a System using Multiport Memory

Note: To reduce complexity the host interface is not explicitly shown here.

User's Manual

31

#### **Functional Description**

#### 2 Functional Description

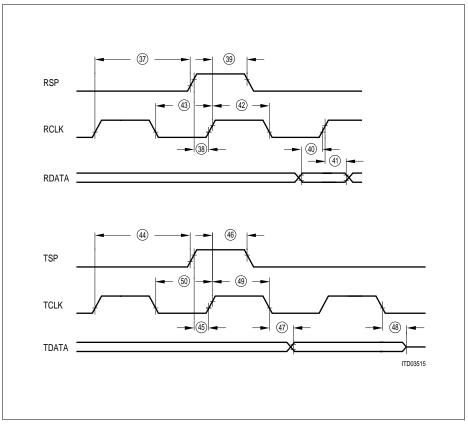

#### 2.1 Serial Interface

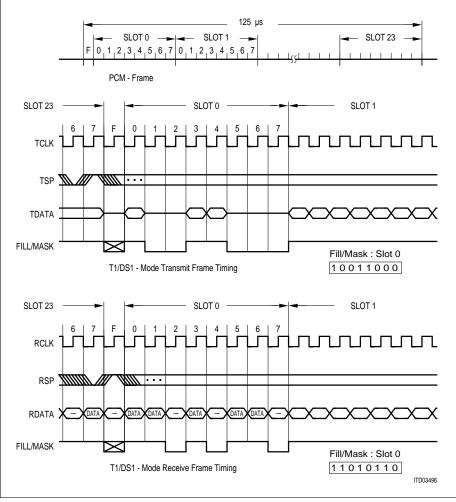

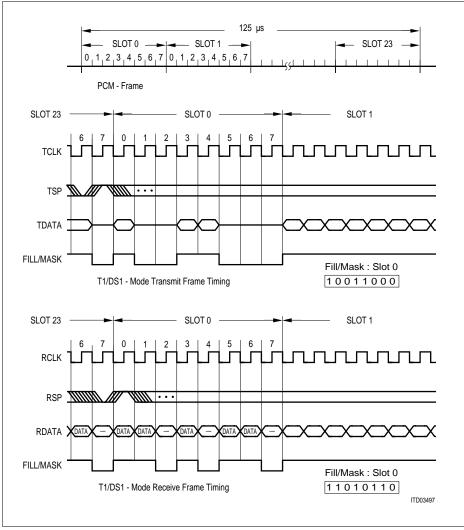

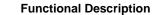

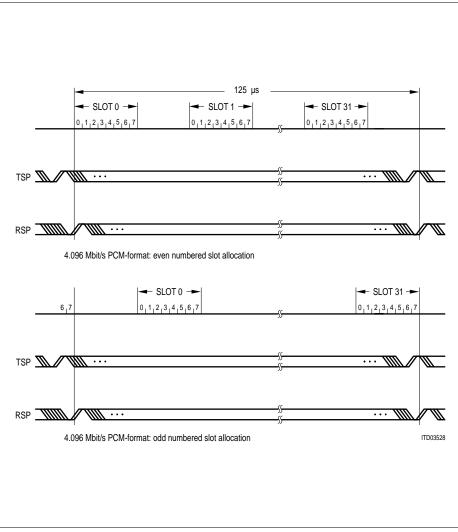

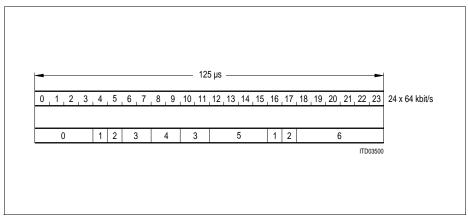

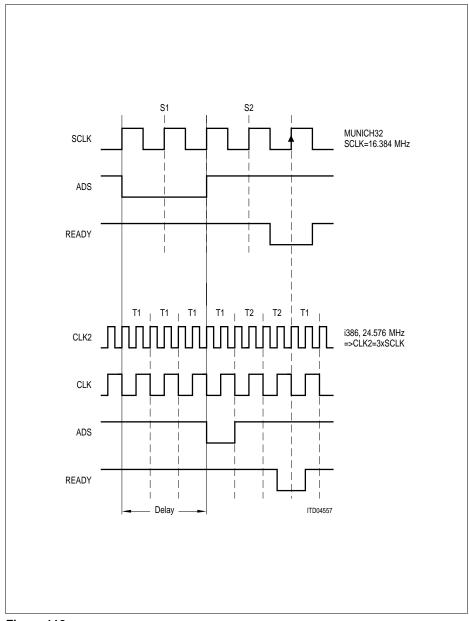

The serial interface of MUNICH32 includes a data receive (RDATA) and a data transmit line (TDATA) as well as the accompanying control signals (RCLK = Receive Clock, RSP = Receive Synchronization Pulse, TCLK = Transmit Clock, TSP = Transmit Synchronization Pulse). The timings of the receive and transmit PCM highway are independent of each other, i.e. the frame positions and clock phases are not correlated. Data is transmitted and received either at a rate of 2.048 Mbit/s for the CEPT 32-Channel European PCM format (**Figure 14**) or 1.544 Mbit/s or 1.536 Mbit/s for the T1/DS1 24-Channel American PCM format (**Figure 12** and **Figure 13**). MUNICH32 may also be connected to a 4.096-Mbit/s PCM system (**Figure 15**), where it handles either the even- or odd-numbered time slots, so all 64 time slots can be covered by connecting two MUNICH32s to the PCM highway.

The actual bit rate of a time slot can be varied from 64 Kbit/s down to 8 Kbit/s for the receive and transmit direction. A fill mask code specified in the time slot assignment determines the bit rate and which bits of a time slot should be ignored. Any of these time slots can be combined to a data channel allowing transmission rates from 8 Kbit/s up to 2.048 Mbit/s.

The frame alignment is established by the transmit and receive synchronization pulse (TSP, RSP), respectively. The sampled rising edge of TSP identifies the current bit on the serial line (TDATA) as the last bit of a PCM frame. The sampled rising edge of RSP indicates that the current bit on the serial line (RDATA) is the first bit of a PCM frame.

The F-bit for the 1.544 MHz T1/DS1 24-channel PCM format is ignored in receive direction, the corresponding bit is tristate in transmit direction. It is therefore assumed that this channel is handled by a different device.

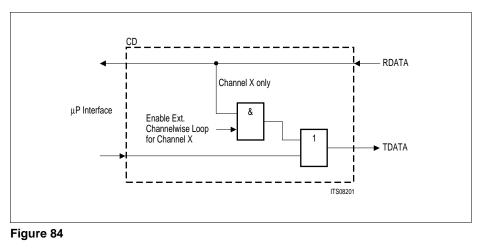

For test purposes four different test loops can be switched. In a complete loop all logical channels are mirrored either from serial data output to input (internal loop) or vice versa (external loop).

In a channelwise loop one single logical channel is logically mirrored either from serial data output to input (internal loop) or vice versa (external loop).

A detailed description of the different loops is found in Chapter 4.2.1 and Chapter 5.1.

32

User's Manual

Functional Description

## Figure 12

#### T1/DS1 Mode PCM Frame Timing 1.544 MHz

- Note 1: A *box* in a bit of the RDATA line means that this bit is ignored (HDLC, TMB, TMR, V.110/X.30) or received as '1'-bit (TMA; one overwrite).

- Note 2: The fill/mask bit for the F-bit is not defined. TDATA is tristate for the F-bit, and the F-bit is ignored in the receive direction.

- Note 3: TSP and RSP must have one single rising and falling edge during a 125  $\mu s$  PCM frame.

User's Manual

Functional Description

# Figure 13

- T1/DS1 Mode PCM Frame Timing 1.536 MHz

- Note 1: A box in a bit of the RDATA line means that this bit is ignored (HDLC, TMB, TMR, V.110/X.30) or received as '1'-bit (TMA; one overwrite).

- Note 2: TSP and RSP must have one single rising and falling edge during a 125  $\mu s$  PCM frame.

User's Manual

#### Figure 14 CEPT Mode PCM Frame Timing

- Note 1: A box in a bit of the RDATA line means that this bit is ignored (HDLC, TMB, TMR, V.110/X.30) or received as '1'-bit (TMA; one overwrite).

- Note 2: TSP and RSP must have one single rising and falling edge during a 125  $\mu s$  PCM frame.

User's Manual

Functional Description

#### Figure 15 4.096 Mbit/s PCM Frame Timing

- Note 1: A box in a bit of the RDATA line means that this bit is ignored (HDLC, TMB, TMR, V.110/X.30) or received as '1'-bit (TMA; one overwrite).

- Note 2: TSP and RSP must have one single rising and falling edge during a 125  $\mu s$  PCM frame.

User's Manual

36

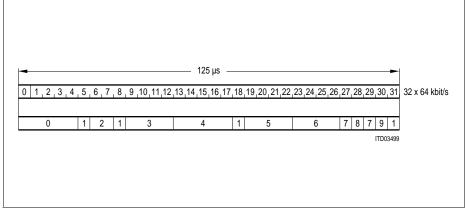

# Figure 16 Example: Programmable Channel Allocation for 32 Time Slots

Figure 17 Example: Programmable Channel Allocation for 24 Time Slots

User's Manual

37

#### **Functional Description**

#### 2.2 Microprocessor Interface

A 64-channel DMA controller (32 channels in receive direction and 32 channels in transmit direction) with buffer chaining capability is integrated in the MUNICH32. It provides DMA functions for up to 32 full duplex channels and allows data transfer between the serial interface and an external memory. The MUNICH32 performs long word by long word transfers on a 32-bit bidirectional data bus (D(31:0)) and addresses up to 4 GByte of RAM with a 30-bit address bus (A(31:2)). The chip always works as a system bus master and can be operated in either a Intel or Motorola environment. MUNICH32 receives commands and data from the host processor via the shared memory. The host stores the action specification containing configuration initialization and monitor commands in the memory. Afterwards the host informs the MUNICH32 by generating an action request pulse (AR line). The MUNICH32 reacts by reading the action specification to the interrupt queue. In addition, the INT/INT line is activated during the write access belonging to the interrupt specification.

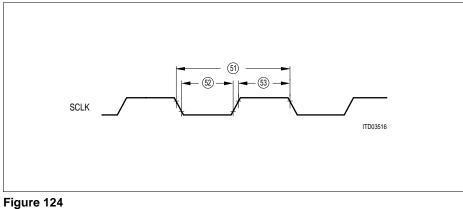

The timing of the microprocessor interface is established according to the Intel 80386 or Motorola 68020 processor. The system clock (SCLK) provides the fundamental timing for the  $\mu$ P interface and is the internal device clock. Each bus cycle performs a long word (B16 = 1) or a word (B16 = 0) transfer and takes four system clock periods in the fastest case, any number of wait clock cycles can be inserted.

MUNICH32's architecture is based on a 32-bit data structure. Therefore MUNICH32 performs long word operations preferably. While the word operation mode is selected the long word operation is divided into two consecutive word operations. In the case of a read access the data of the two words are connected together to build a 32-bit long word before processing.

| Mode     | <b>Operation Mode B16</b> | BE(3–0)        | Access    |

|----------|---------------------------|----------------|-----------|

| Intel    | 1                         | 0 <sub>H</sub> | long word |

|          | 0                         | 3 <sub>H</sub> | MSB word  |

|          | 0                         | C <sub>H</sub> | LSB word  |

| Motorola | 1                         | 0 <sub>H</sub> | long word |

|          | 0                         | 8 <sub>H</sub> | MSB word  |

|          | 0                         | A <sub>H</sub> | LSB word  |

For a read access first the MSB bytes of a long word will be transferred and then the LSB bytes via D(15:0).

For a write access first the LSB-bytes of a long word will be transferred and then the MSB bytes via D(15:0).

The signal B16 cannot be changed dynamically and should be set to '1' in Intel parity mode (parity mode is not available in 16-bit word Intel mode).

User's Manual

#### **Functional Description**

#### 2.2.1 Intel Mode

The Intel mode has two submodes – parity mode (even parity) and non parity mode – to be chosen by strapping PM to '1' or '0' respectively.

In Intel mode the lower (higher) ordered byte of a long word (D31 ... D0) is assigned to the lower (higher) ordered physical address.

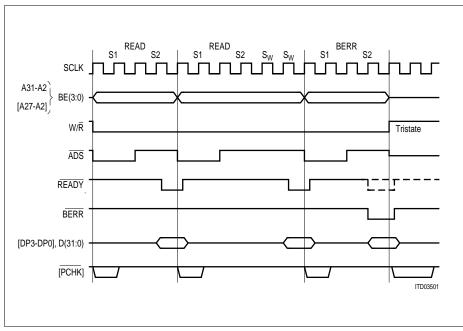

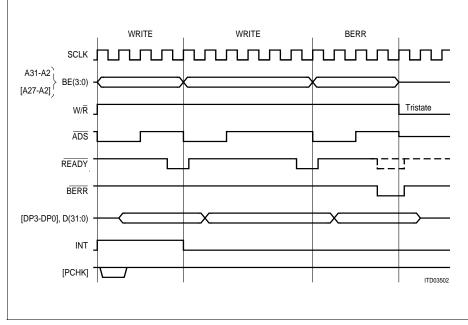

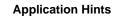

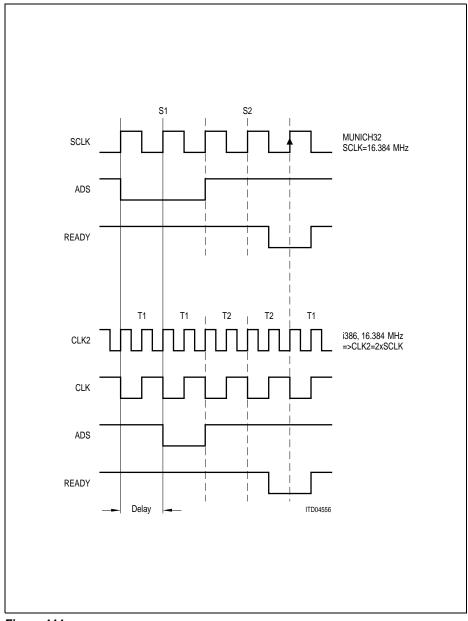

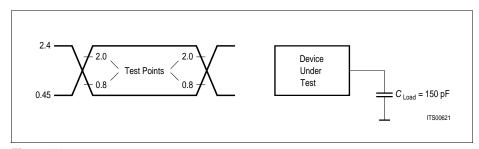

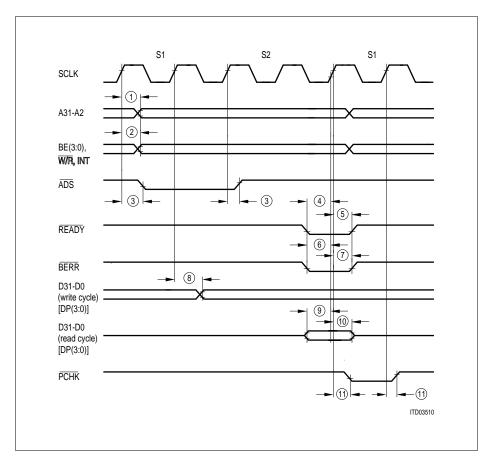

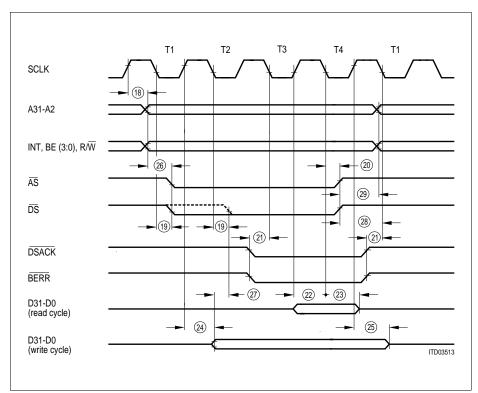

The read or write bus cycle is controlled by the signals  $W/\overline{R}$ ,  $\overline{ADS}$  and  $\overline{READY}$  as shown in **Figure 18**, **Figure 19**. Each bus cycle consists of two bus states (S1, S2). During state S1 the address signals and bus cycle definition signals are driven valid. Simultaneously, the address status  $\overline{ADS}$  is asserted to indicate their availability. The bus cycles are terminated by asserting  $\overline{READY}$ .  $\overline{READY}$  is ignored on the first bus state S1 and sampled at the end of the following state S2. If  $\overline{READY}$  is not asserted in S2 then wait cycles SW are inserted until a bus cycle end is detected. During a read cycle the MUNICH32 floats its data signals to allow external memory to drive the data bus.

The input data and parity bits DP3–0 (if parity mode is selected) is latched when READY is asserted. During a write cycle MUNICH32 drives the data signals and parity bits DP3–0 (if parity mode is selected) beginning in the second clock period of S1 until the first clock period following the cycle acknowledgment READY. If a bus cycle error indicated by BERR has occurred, the MUNICH32 terminates the bus cycle. In case of a read cycle in the control and configuration section an action request fail interrupt is generated and the action is suspended. In case of a read cycle in the transmit data section the corresponding frame is aborted and a FO interrupt is generated. In all other cases of read or write cycles terminated with an error condition no actions are performed.

A 4-bit data byte parity bus DP3–0 is used in Intel mode if parity mode is selected by strapping PM to '1'. During a read access DP3–0 is supposed to contain the parity of D(31:24), D(23:16), D(15:8) and D(7:0) respectively. A low active output  $\overrightarrow{PCHK}$  indicates whether the parity was correct ( $\overrightarrow{PCHK} = 1$ ) or wrong ( $\overrightarrow{PCHK} = 0$ ) in the clock cycle after the data/parity is latched.  $\overrightarrow{PCHK}$  stays low 1 or 2 clock cycles. No further action is taken as consequence to a parity fail.

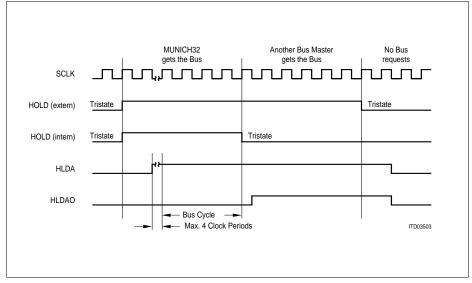

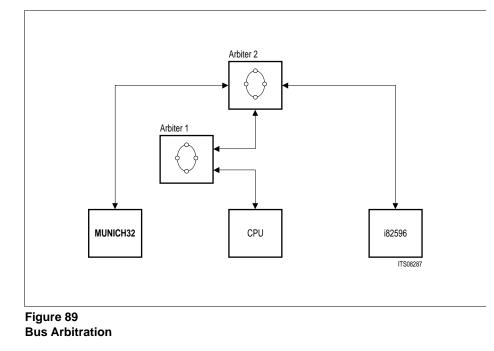

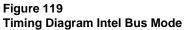

As the memory access is performed by using one common system bus, bus management is done with the signals HOLD, HLDA and HLDAO as shown in **Figure 20**.

The wired or HOLD line is driven high whenever one of the MUNICH32s has to perform a bus transfer. The activated HOLD ACKNOWLEDGE indicates that the bus control will be released. If the specific device has activated the HOLD itself, it will start the memory accesses. Otherwise it will pass the signal to the next cascaded device. Several memory accesses may be required if the MUNICH32 has not been granted access recently. In this example of four MUNICH32 devices sharing the same bus, each device will generate four memory cycles, giving a total of 16 cycles per HOLD/HLDA/HLDAO tenure. In order to prevent blocking in the case of continuous request by one device, the MUNICH32 does not generate another HOLD REQUEST before the HOLD ACKNOWLEDGE has been deactivated.

User's Manual

If the HOLD ACKNOWLEDGE is driven low while the MUNICH32 is performing a bus cycle, the bus is released later than two clock periods after de-assertion of HOLD ACKNOWLEDGE. The current bus cycle is finished with a bus cycle error. This action should be followed by an ASP.RES as described in **Chapter 4.2.1**.

Figure 18 Read Cycle Timing Diagram (Intel mode)

User's Manual

40

Functional Description

Figure 19 Write Cycle Timing Diagram (Intel mode)

User's Manual

41

#### Functional Description

#### Figure 20 Bus Management for Intel Bus Mode

- Note 1: Bus Cycle means, that the MUNICH32 under consideration starts a read or write access at most 4 clock periods after HLDA is asserted after its HOLD. The MUNICH32 terminates the cycle typically two clock periods after the last bus cycle.

- Note 2: In the Bus Management example it is assumed that the MUNICH32 under consideration has a higher priority than the other bus master. HOLD (internal) is therefore the internal request generated by the MUNICH32, HOLD (external) the signal on the external HOLD line, being the OR combination of the HOLD signal generated by the MUNICH32 and the other bus master(s).

- Note 3: A typical configuration example for a system with several bus masters is given in **Figure 4** and **Figure 5**.

42

User's Manual

#### **Functional Description**

#### 2.2.2 Motorola Mode

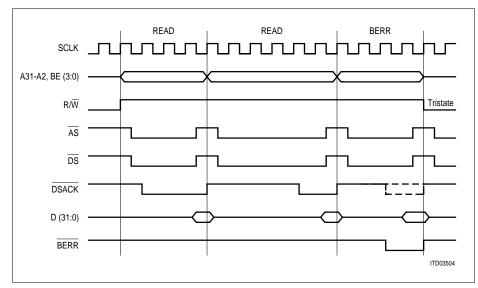

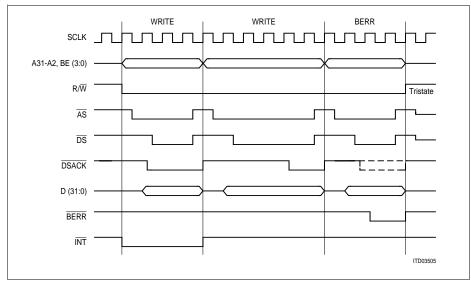

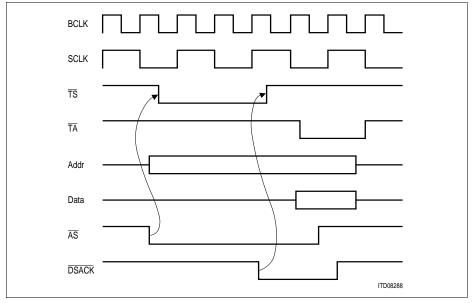

In Motorola mode the bus is used in an asynchronous manner. The bus operation uses the handshake lines (AS, DS, DSACK and BERR) to control data transfer as shown in **Figure 21**, **Figure 22**. Address strobe AS indicates the validity of an address on the address bus (A31 ... A2) and of the bus definition R/W (Read or Write cycle). It is asserted half a clock cycle after the beginning of a bus cycle. The data strobe DS signal is used as a condition for valid data of a write cycle. MUNICH32 asserts DS one full clock cycle after the assertion of AS during a write cycle. The data is placed on the bidirectional data bus (D31 ... D0) half a clock cycle after AS is driven low. For a read cycle, MUNICH32 asserts DS to signal the external memory to drive the data on the bus. DS is asserted at the same time as AS during a read cycle. The data is latched with the last falling edge of the clock for that cycle.

The bus cycle is terminated if the data transfer acknowledge ( $\overline{DSACK}$ ) is asserted with the falling edge of the third clock period. Otherwise MUNICH32 inserts wait cycles until  $\overline{DSACK}$  is recognized.  $\overline{AS}$  and  $\overline{DS}$  are driven high half a clock period before bus cycle end.

The bus error BERR is also a bus cycle termination indicator. It can be used in the absence as well as in conjunction with DSACK. If an abnormal termination has occurred during a read cycle, MUNICH32 generates an interrupt and aborts the corresponding transmit channel. For a write cycle no further action is performed.

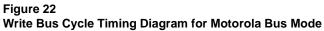

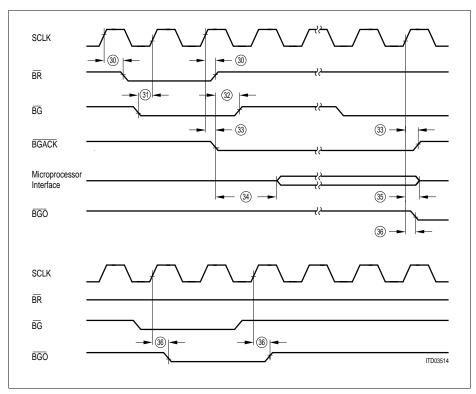

As the MUNICH32 is used in a multi-bus-master application, bus arbitration has to be done to avoid simultaneous system bus access by more than one master. In Motorola mode the bus arbitration protocol of the 68020 is established using the signals BR, BG, BGACK and BGO as shown in **Figure 23**. The wired-or Bus Request (BR) is driven low to indicate to the processor that one of the MUNICH32s requires control of the bus. The activated Bus Grant (BG) signals the availability of the system bus. If the MUNICH32 has activated the bus request itself, it asserts the wired-or Bus Grant Acknowledge to indicate that it has assumed bus mastership. Otherwise it will pass the BUS GRANT signal to the device cascaded next (BGO). At the same time it releases the Bus Request. After finishing the last bus cycle, the Bus Grant Acknowledge is deactivated and the Bus Grant is passed on. In order to prevent blocking in the case of continuous request by one device, MUNICH32 does not generate another Bus Request before the external Bus Request and Bus Grant Acknowledge have been deactivated.

After getting the bus mastership MUNICH32 drives the bus and starts the first bus cycle one clock after assertion of BGACK. After finishing the memory access it releases the bus and de-asserts BGACK at the same time.

43

User's Manual

Functional Description

User's Manual

44

# Functional Description

#### Figure 23 Bus Management for Motorola Mode

- Note: 1. In the Bus Management example it is assumed that the MUNICH32 under consideration has a higher priority than the other bus master. BR and BGACK are wired AND lines to be pulled to '1' by an external signal.

- 2. A typical configuration example for a system with several bus masters is given in **Figure 6**.

User's Manual

45

#### 2.2.3 DMA Priorities

# **Prioritization of Queueing DMA Cycles**

| Priority                                                     | Interrupt                                                |  |

|--------------------------------------------------------------|----------------------------------------------------------|--|

| Highest priority                                             | Receive link list including accesses to the descriptors  |  |

|                                                              | Transmit link list including accesses to the descriptors |  |

| Lowest priority Configuration of a channel (action requests) |                                                          |  |

The MUNICH32 will perform all pending accesses on the same bus tenure.

Note: Several bus transactions may be required if the MUNICH32 has not been given access to the system bus for a long period of time. This is often seen in multimaster systems where several MUNICH32 devices share the system bus.

User's Manual

46

#### **Functional Description**

#### 2.3 Basic Functional Principles

MUNICH32 is a Multichannel Network Interface Controller for HDLC, offering a variety of additional features like subchanneling, data channels comprising of one or more time slots, DMI 0, 1, 2 transparent or V.110/X.30 transmission and programmable rate adaption. MUNICH32 performs formatting and deformatting operations in any network configuration, where it implements, together with a microprocessor and a shared memory, the bit oriented part (flag, bit stuffing, CRC check) of the layer 2 (data link protocol level) functions of the OSI reference model.

The block diagram is shown in **Figure 3**. MUNICH32 is designed to handle up to 32 data channels of a 1.536/1.544 Mbit/s T1/DS1 24-channel, 2.048-Mbit/s CEPT 32-channel or a 4.096-Mbit/s 32-channel PCM highway. The device provides transmission for all bit rates from 8 Kbit/s up to 2.048 Mbit/s of packed data in HDLC format or of data in a transparent format supporting the DMI mode (0, 1, 2) or V.110/X.30 mode. Tristating of the transmission line as well as switching a channelwise or complete loop are also possible. An on-chip 64-channel DMA generator controls the exchange of data and channel control information between the MUNICH32 and the external memory.

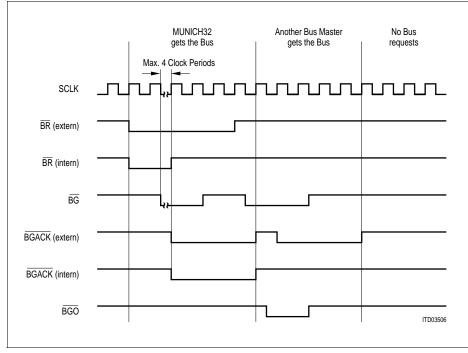

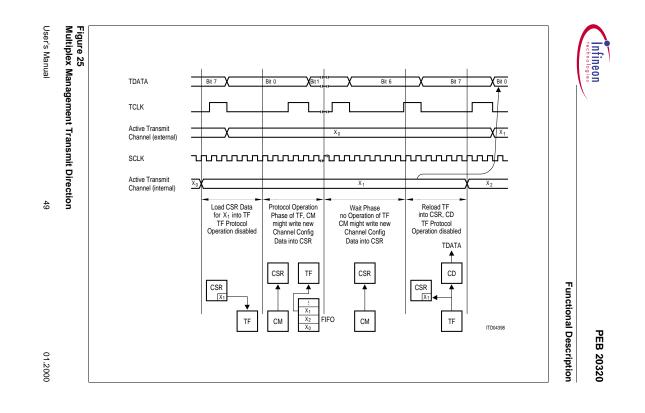

The MUNICH32 processes receive and transmit data independently for each time slot and transmission direction respectively (blocks TF = Transmit Formatter, RD = Receive Deformatter). The frame counters are reset by the rising edges of the RSP or TSP line. The processing units TF and RD work with a multiplex management, i.e. there exists only one protocol handler, which is used by all channels in a time sharing manner (see Figure 24 and Figure 25). The actual configuration, e.g. transmission mode, channel assignment, fill/mask code or state of the protocol handlers is retrieved from the Configuration and State RAM (CSR) at the beginning of the time slot and reloaded to the CSR at the end. The control unit (CD) controls the access to the CSR and allows writing of reconfiguration information only if the continuous transfer of the configuration information between the CSR and the formatters (TF and RD) will not be disturbed. In receive direction, 32 unpacked data bits are first accumulated and then stored into an on-chip receive buffer (RB) for transfer to the shared memory. As soon as the RB receives 32 bits for a channel it requests access to the parallel microprocessor bus. The on-chip transmit buffer (TB) is always kept full of data ready for transmission. The TB will request more data when 32 bits become available in the ITBS. These buffers allows a flexible access to the shared memory in order to prevent data underflow (Tx) and data overflow (Rc).

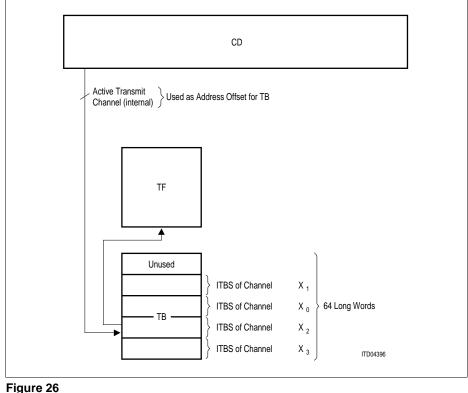

The transmit buffer (TB) has a size of 64 long words (= 256 bytes). In this buffer, data of 8 PCM frames can be stored for each data channel. In this case, there are max. 1 ms between access to the shared memory and data supply to the Transmit Formatter. In order to meet these requirements a variable and programmable part of the buffer (ITBS) must be allocated to each data channel (see **Figure 26**).

47

User's Manual

For example:

a) 2.048-Mbit/s PCM highway

$32\times 64\text{-Kbit/s}$  data channels (8 bits are sent with each PCM frame). Two long words of the buffer are allocated to each data channel.

b) 1  $\times$  2.048-Kbit/s data channel

The maximum buffer size for one channel (63 long words) is allocated to this data channel.

c) 6  $\times$  256-Kbit/s and 8  $\times$  64 Kbit/s data channels.

Eight long words of the buffer are allocated to each of the 6 data channels with 256 Kbit/s and two long words are assigned to each of the 8 data channels with a transmission rate of 64 Kbit/s.

The choice of the individual buffer size of each data channel can be made in the channel specification (shared memory). The buffer size of one channel is changeable without disturbing the transmission of the other channels.

#### Figure 26 Partitioning of TB

User's Manual

50

# **Functional Description**

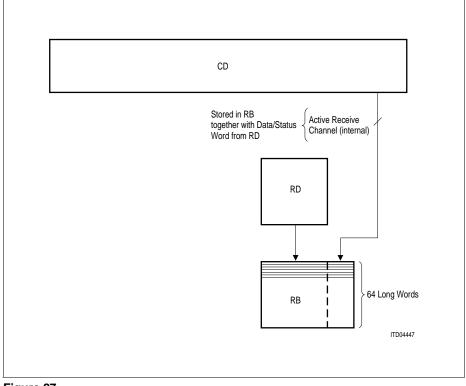

The receive buffer (RB) is a FIFO buffer and also has a size of 64 long words, which allows storing the data of eight complete PCM frames before transferring to the shared memory.

#### Figure 27 Partitioning of RB

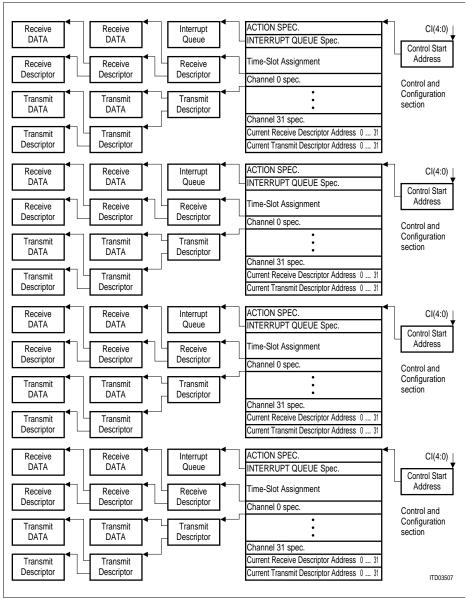

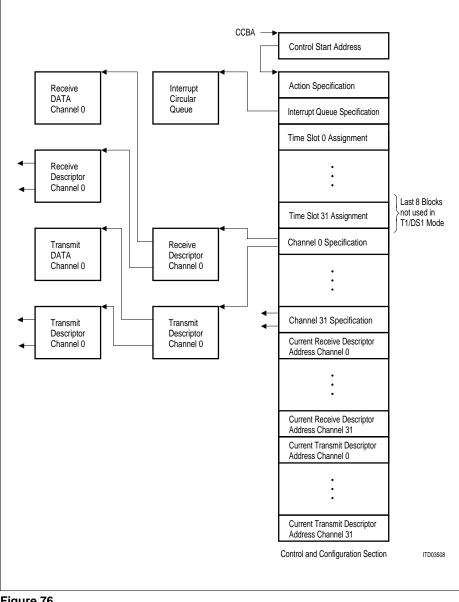

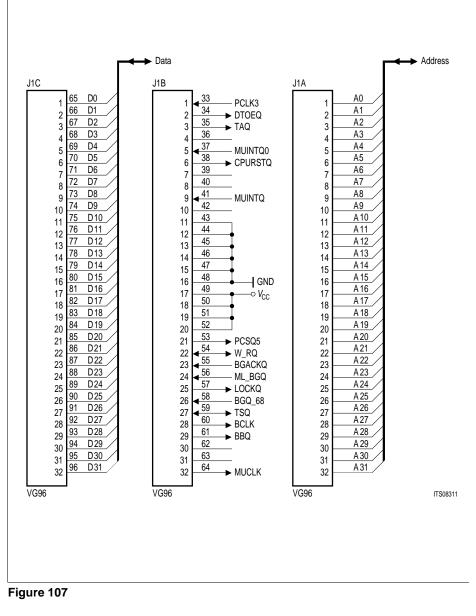

The data transfer to the shared memory is performed via a 32-bit microprocessor interface working either in SIEMENS/Intel or Motorola bus mode. **Figure 28** shows the division of the shared memory required for each MUNICH32:

- Configuration start address located at a programmable address

- Control and configuration section

- An interrupt circular queue with variable size

- Descriptor and data sections for each channel.

User's Manual

51

#### Functional Description

#### Figure 28 Memory Division for up to four MUNICH32

User's Manual

52

#### **Functional Description**

The shared memory allocated for each transmit and receive channel is organized as a chaining list of buffers set up by the host. Each chaining list is composed of descriptors and data sections. The descriptor contains the pointer to the next descriptor, the start address and the size of a data section. It also includes control information like frame end indication, transmission hold and rate adaption with interframe time-fill.

In the transmit direction the MUNICH32 reads a transmit descriptor, calculates the data address, writes the current transmit descriptor address into the CCS, and fills the on-chip transmit buffer. When the data transfer of the specified section is completed, the MUNICH32 releases the buffer, and branches to the next transmit descriptor. If a frame end is indicated the HDLC, TMB or TMR frame will be terminated and a specified number of the interframe time-fill byte will be sent in order to perform rate adaption. If frame end is found in a transmit descriptor TMA channel the specified number of programmable TMA flags is appended to the data in the descriptor. If frame end is found in a transmit descriptor TMA channel the specified number of a V.110/X.30 channel the frame is aborted (after the data in the descriptor are sent) by finishing the current 10-octet frame with 'zeros' and sending 2 more 10-octet frames with 'zeros' which leads to a loss of synchronism on the peer side. An adjustment for the inserted zeros in HDLC is programmable, which leads to a reduction of the specified number of interframe time-fill by  $1/8^{\text{th}}$  of the number of zero insertions. This can be used to send long HDLC frames with a more or less fixed data rate in spite of the zero insertions. A maskable interrupt is generated before transmission is started again.

53

User's Manual

#### **Functional Description**

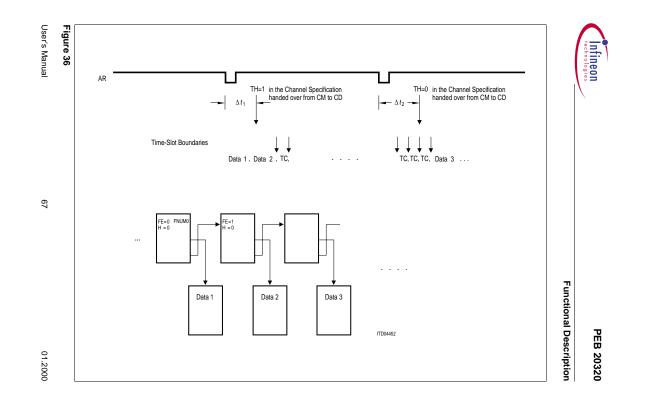

# The following Sections give Examples of Typical Transmit Situations for the Individual Modes

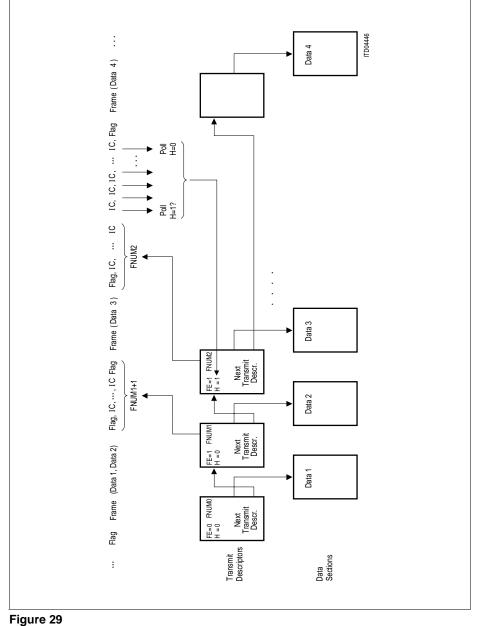

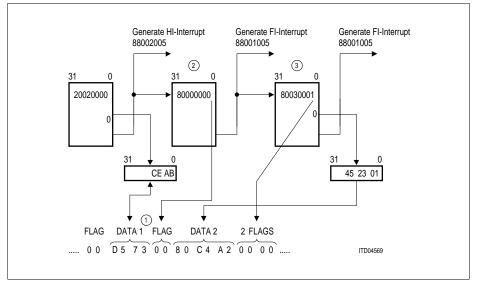

# Variable Size Frame Oriented Protocols (HDLC, TMB, TMR)

Normal operation, handling of frame end (FE) indication and hold (H) indication.

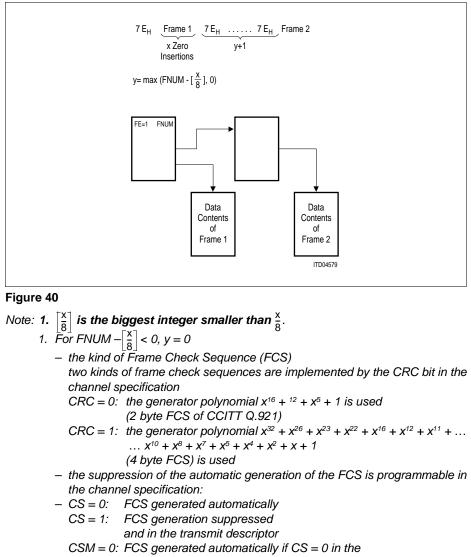

- Note: 1. FNUM0 must be set to zero.

- 2.  $Flag = 7E_H$  for HDLC  $00_H$  for TMB, TMR

- $IC = 7E_H$  for HDLC and IFTF = 0 FF<sub>H</sub> for HDLC and IFTF = 1  $00_H$  for TMB, TMR

- 3. After sending the FNUM2 1 IC characters the device starts polling the hold bit in the transmit descriptor once for each further sent IC character. It also rereads the pointer to the next transmit descriptor once with each poll of the hold indication. The pointer to the next transmit descriptor can be changed while HOLD = 1 is set. The value of the pointer, (read in the poll where HOLD = 0) is used as the next descriptor address. If more than 6 IC characters will be sent, the use of the Transmit Hold (TH) should be considered as an alternative to using the descriptor hold bit. See **Chapter 5.3.2**.

54

User's Manual

**Functional Description**

i iguio 20

User's Manual

55

#### **Functional Description**

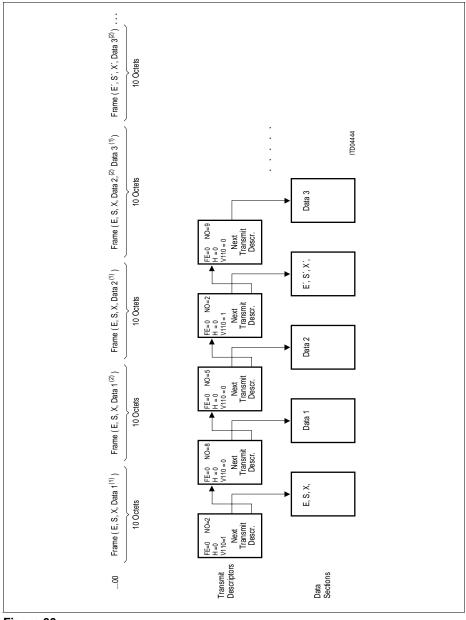

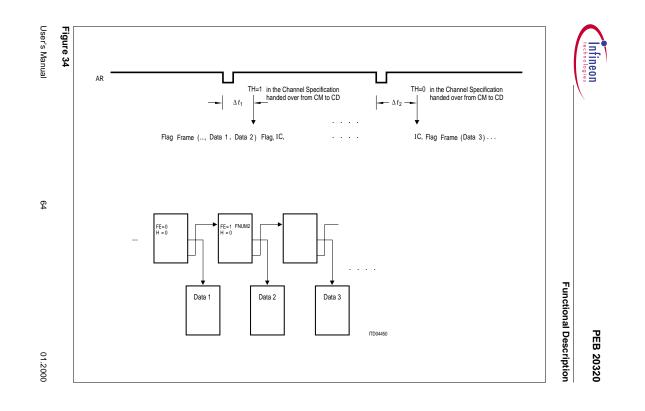

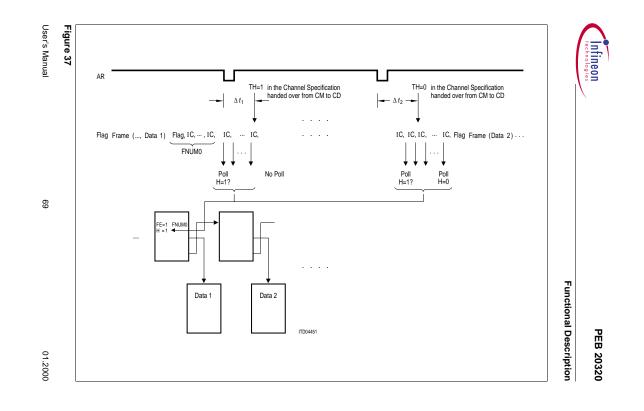

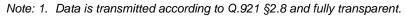

#### Fixed Size Frame Oriented Protocols (V110/X.30)

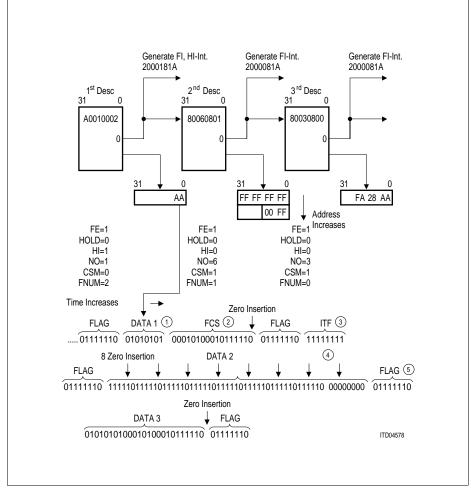

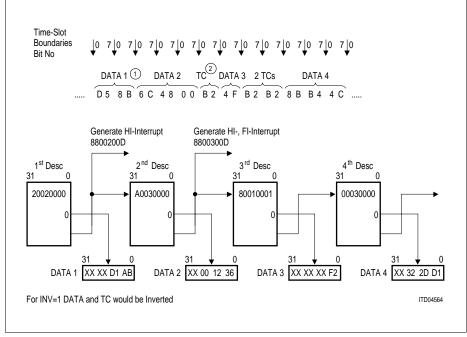

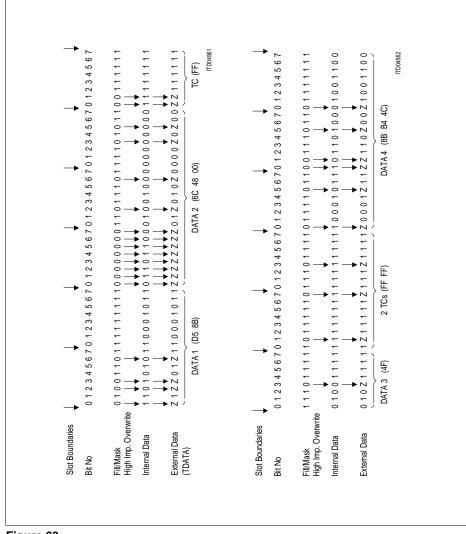

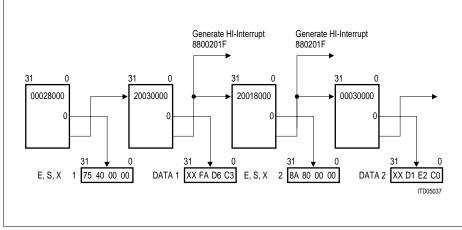

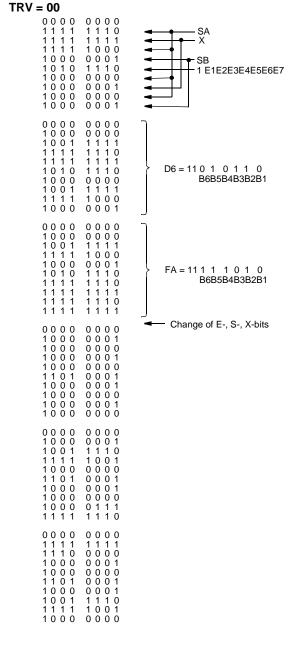

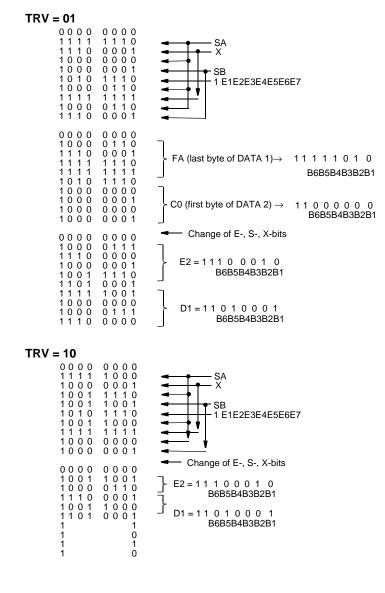

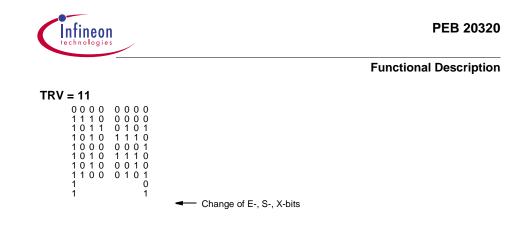

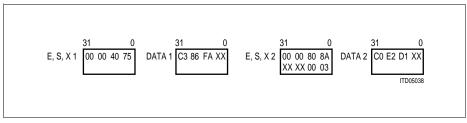

Normal operation, E, S, X change (indicated by the V.110-bit in the transmit descriptor) Example for TRV = '11'

Note: 1. FNUM must be 0 for all transmit descriptors.

- 2. The actual E-, S-, X-bits have to be in the first transmit descriptor after reset.

- 3. As shown in the example the contiguous parts of a data section belonging to one descriptor are sent in contiguous frames (DATA 1<sup>(1)</sup> are the bytes 0 3 of DATA 1, DATA 1<sup>(2)</sup> are the bytes 4 7 of DATA 1). If the end of a data section is reached within a frame, the frame is continued with data from the next data section belonging to a transmit descriptor with the bit V.110 = 0 (DATA 2<sup>(2)</sup> = byte 4 of DATA 2, DATA 3<sup>(1)</sup> = byte 0 2 of DATA 3).

- 4. The E-, S-, X-bits are only changed from one frame to the next not within a frame. The change occurs in the first frame which does not contain data of the previous data section.

- 5. Neither FE nor H may be set to 1 during a normal operation of the mode. They both lead to an abort of the serial interface.

56

User's Manual

**Functional Description**

Figure 30

User's Manual

57

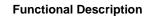

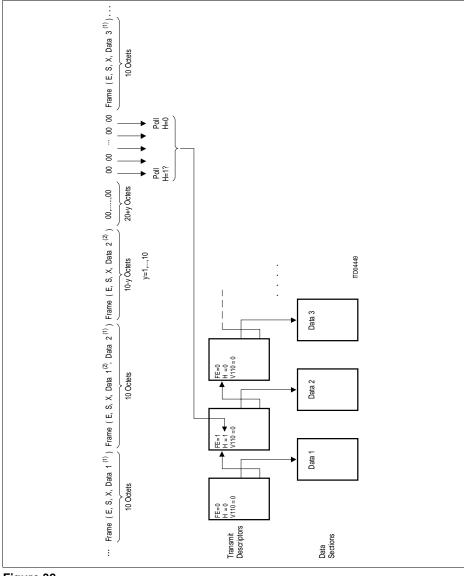

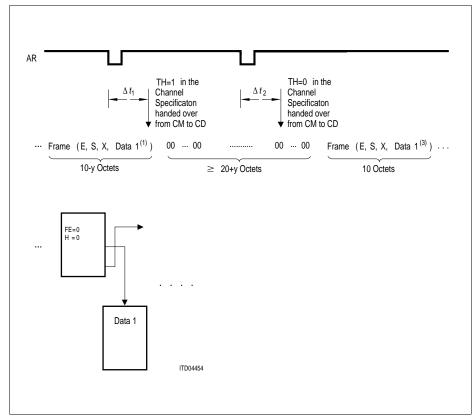

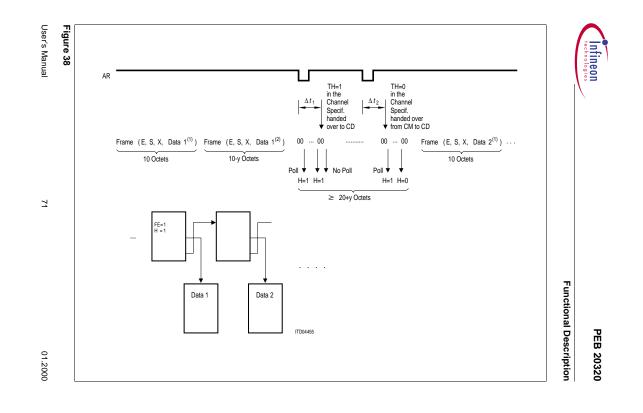

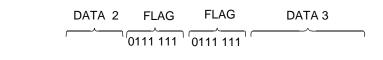

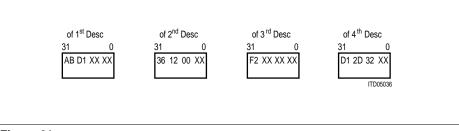

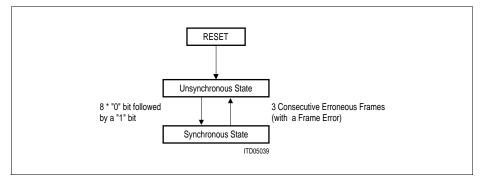

#### Fixed Size Frame Oriented Protocols (V.110/X.30)

Handling of frame end (FE) indication

Note: 1. FNUM must be '0' for all transmit descriptors.

- 2. The frame (E, S, X, DATA 2<sup>(2)</sup>) is the beginning of a 10-octet frame. It stops with the octet no. y, containing the last data bit of DATA 2 to be sent.

- 3. Since y = 1, ..., 10 the 20 + y times  $00_H$  characters sent afterwards cause the peer station to recognize 3 consecutive 10-octet frames with frame error which leads to a loss of synchronism in the peer station.

- For y = 10 DATA 2 is identical to DATA 2<sup>(1)</sup> and 30 times 00<sub>H</sub> characters are sent after frame (E, S, X, DATA 1<sup>(2)</sup>, DATA 2<sup>(1)</sup>).

- 5. The E-, S-, X-bits are supposed to be loaded by an earlier transmit descriptor in the example. A descriptor changing them (with V.110-bit set) can be put between, before or after the descriptors in the example. It will change these bits according to the rules discussed previously.

58

User's Manual

Figure 31

User's Manual

59

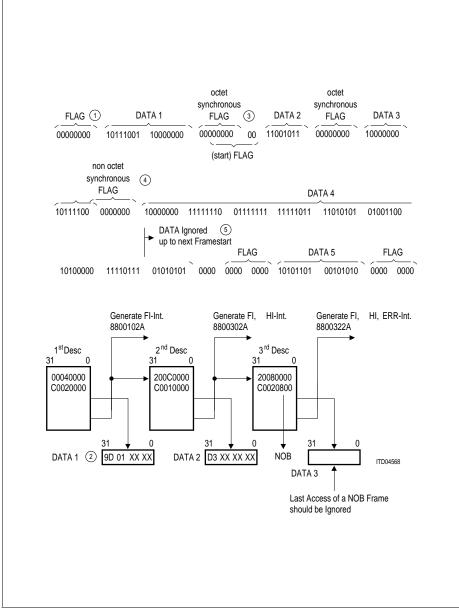

**Functional Description**

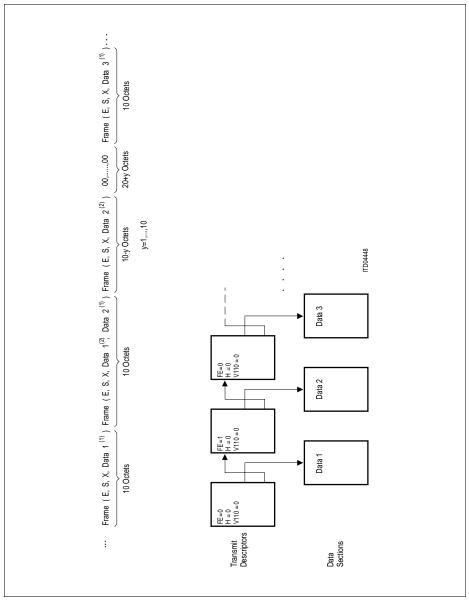

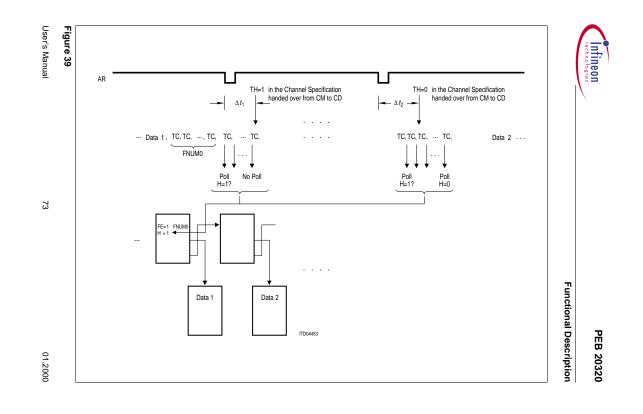

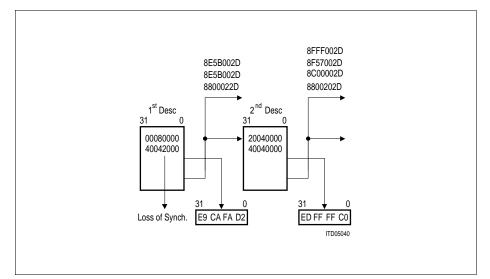

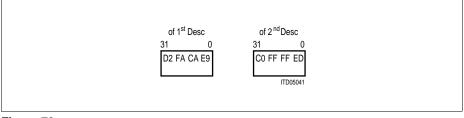

# Fixed Size Frame Oriented Protocols (V110/X.30)

Handling of hold (H) indication

Figure 32

User's Manual

60

# **Functional Description**

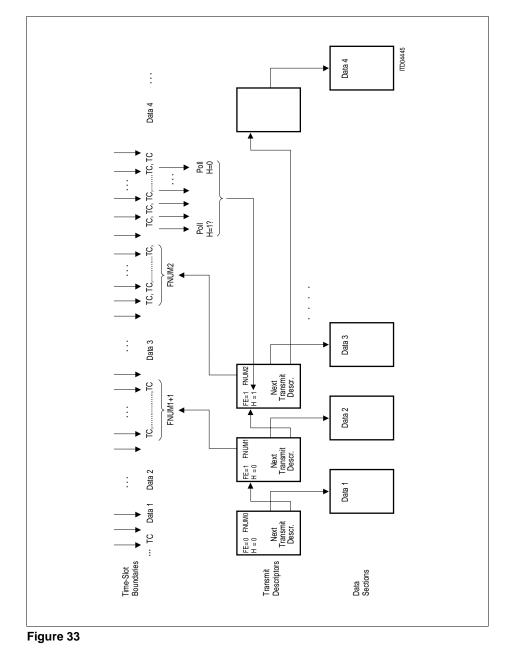

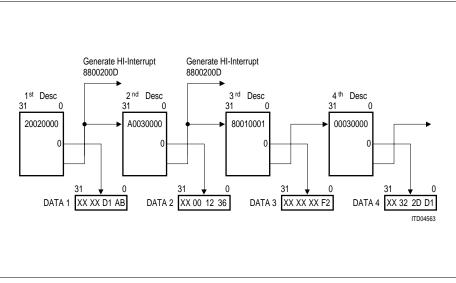

### **Time Slot Oriented Protocol (TMA)**

Normal operation, handling of frame end (FE) indication and hold (H) indication.

Note: 1. FNUM must be set to zero.

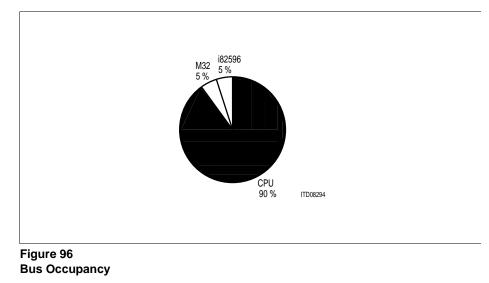

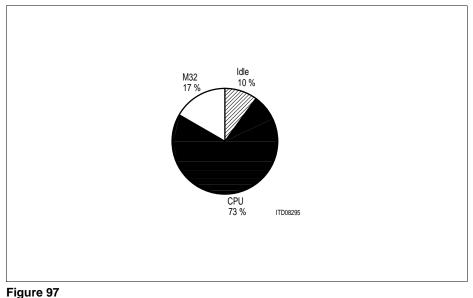

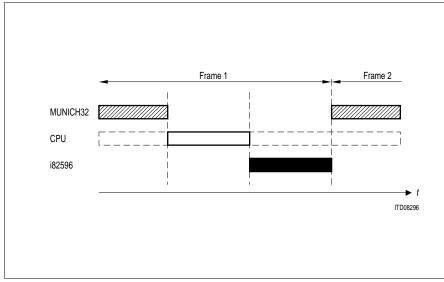

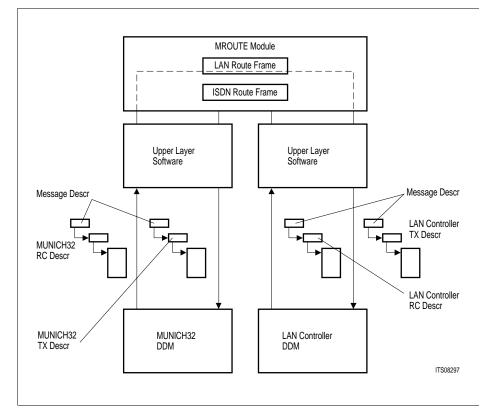

- 2.  $TC = FF_H$  for TMA and FA = 0the programmed flag with TMA and FA = 1