# Power Management and Interface IC for Smartcard Readers and Couplers

The MC33560 is an interface IC for smartcard reader/writer applications. It enables the management of any type of smart or memory card through a simple and flexible microcontroller interface. Moreover, several couplers can be coupled in parallel, thanks to the chip select input pin (Pin 5). The MC33560 is particularly suited to low power and portable applications because of its power saving features and the minimum of external parts required. Battery life is extended by the wide operating range and the low quiescent current in standby mode. A highly sophisticated protection system guarantees timely and controlled shutdown upon error conditions.

- 100% Compatible with ISO 7816–3 Standard

- Wide Battery Supply Voltage Range: 1.8 V < V<sub>BAT</sub> < 6.6 V

- Programmable V<sub>CC</sub> Supply for 3.0 V or 5.0 V Card Operation

- Power Management for Very Low Quiescent Current in Standby Mode (30 μA max)

- Microprocessor Wakeup Signal Generated Upon Card Insertion

- Self Contained DC–DC Converter to Generate V<sub>CC</sub> using a Minimum of Passive Components

- Controlled Powerup/Down Sequence for High Signal Integrity on the Card I/O and Signal Lines

- Programmable Card Clock Generator

- Chip Select Capability for Parallel Coupler Operation

- High ESD Protection on Card Pins (4.0 kV, Human Body Model)

- Fault Monitoring V<sub>BATlow</sub>, V<sub>CClow</sub> and I<sub>CClim</sub>

- All Card Outputs Current Limited and Short Circuit Protected

- Tested Operating Temperature Range: -25°C to +85°C

- Pb-Free Packages are Available

#### ON Semiconductor®

http://onsemi.com

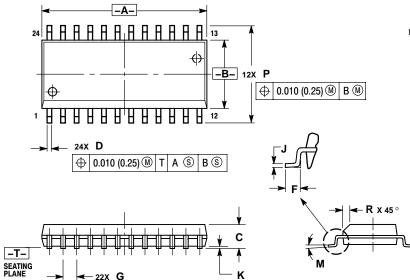

SO-24W DW SUFFIX CASE 751E

24

**MARKING**

**DIAGRAMS**

888888888888

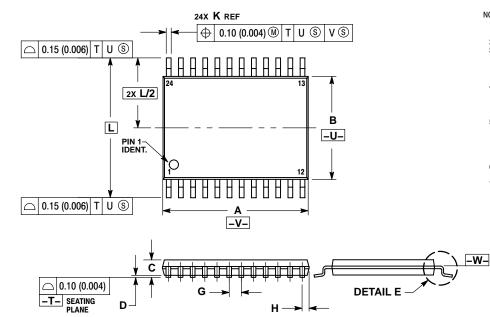

TSSOP-24 DTB SUFFIX CASE 948K

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

G = Pb–Free Device

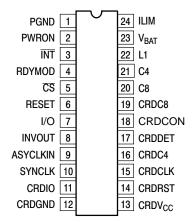

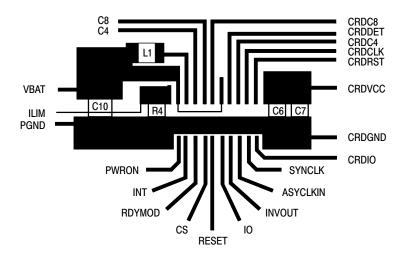

#### **PIN CONNECTIONS**

(Top View)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 24 of this data sheet.

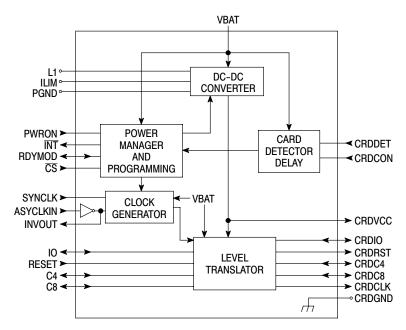

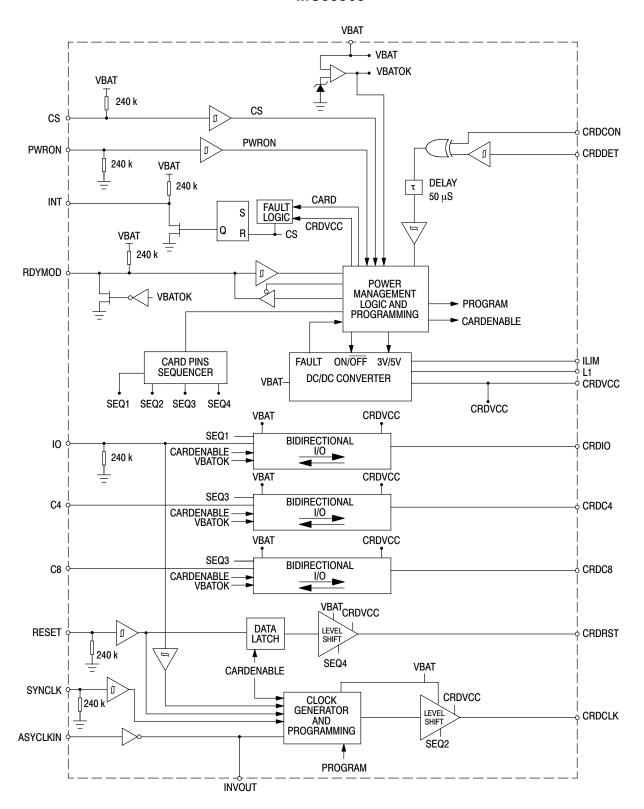

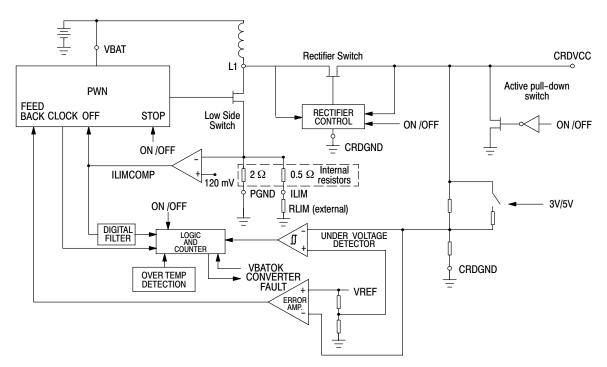

Figure 1. Simplified Functional Block Diagram

#### MAXIMUM RATINGS (Note 1)

| Symbol                                 | Rating                                                                                                                                         | Value                                           | Unit       |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|

| $V_{BAT}$                              | Battery Supply Voltage                                                                                                                         | 7.0                                             | V          |

| I <sub>BAT</sub>                       | Battery Supply Current                                                                                                                         | ±200                                            | mA         |

| $V_{CC}$                               | Power Supply Voltage                                                                                                                           | 6.0                                             | V          |

| I <sub>CC</sub>                        | Power Supply Current                                                                                                                           | ±150                                            | mA         |

| V <sub>IN</sub><br>I <sub>IN</sub>     | Digital Input Pins 2, 4, 5, 6, 7, 9, 10, 17, 18, 20, 21                                                                                        | −0.5 to V <sub>BAT</sub> +0.5 but < 7.0<br>±5.0 | V<br>mA    |

| V <sub>OUT</sub><br>I <sub>OUT</sub>   | Digital Output Pins 3, 4, 8                                                                                                                    | -0.5 to V <sub>BAT</sub> +0.5 but < 7.0<br>±10  | V<br>mA    |

| V <sub>Card</sub><br>I <sub>Card</sub> | Card Interface Pins 11, 13, 14, 15, 16, 19                                                                                                     | -0.5 to V <sub>CC</sub> + 0.5<br>±25            | V<br>mA    |

| IL                                     | Coil Driver Pin 22, ILIM (Pin 24)<br>Power Ground (Pin 1)                                                                                      | ±200<br>±100                                    | mA         |

| V <sub>ESD</sub>                       | ESD Capability: (Note 2)<br>Standard Pins 2, 3, 4, 5, 6, 7, 8, 9, 10, 17, 18, 20, 21, 22, 23, 24<br>Card Interface Pins 11, 13, 14, 15, 16, 19 | 2.0<br>4.0                                      | kV<br>kV   |

| P <sub>Ds</sub><br>R <sub>θJAs</sub>   | SO-24 Package: Power Dissipation @ T <sub>A</sub> = 85°C Thermal Resistance Junction-to-Air                                                    | 285<br>140                                      | mW<br>°C/W |

| P <sub>Dt</sub><br>R <sub>θJAt</sub>   | TSSOP-24 Package: Power Dissipation @ T <sub>A</sub> = 85°C Thermal Resistance Junction-to-Air                                                 | 220<br>180                                      | mW<br>°C/W |

| T <sub>A</sub>                         | Operating Ambient Temperature Range                                                                                                            | -40 to +85                                      | °C         |

| TJ                                     | Operating Junction Temperature Range                                                                                                           | -40 to +125                                     | °C         |

| T <sub>Jmax</sub>                      | Maximum Junction Temperature (Note 3)                                                                                                          | 150                                             | °C         |

| T <sub>stg</sub>                       | Storage Temperature Range                                                                                                                      | -65 to +150                                     | °C         |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

- 1. Maximum electrical ratings are those values beyond which damage to the device may occur.  $T_A = 25^{\circ}C$ .

- 2. Human body model, R = 1500  $\Omega$ , C = 100 pF.

- 3. Maximum thermal rating beyond which damage to the device may occur.

**ELECTRICAL CHARACTERISTICS** These specifications are written in the same style as common for standard integrated circuits. The convention considers current flowing into the pin (sink current) as positive and current flowing out of the pin (source current) as negative. (Conditions:  $V_{BAT} = 4.0 \text{ V}$ ,  $V_{CC} = 5.0 \text{ V}$  nom, PWRON =  $V_{BAT}$ , Operating Mode,  $-I_{CC} = 10 \text{ mA}$ ,  $-25^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ,  $L_1 = 47 \text{ μH}$ ,  $R_{LIM} = 0 \Omega$ ,  $CRDV_{CC}$  capacitor = 10 μF, unless otherwise noted.)

| Characteristic                                                                                               | Test Conditions                                                                                                                                                                                                                                                                       | Symbol                                                    | Min               | Тур         | Max                    | Unit    |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|-------------|------------------------|---------|

| BATTERY POWER SUPPLY SECTION                                                                                 | N .                                                                                                                                                                                                                                                                                   |                                                           |                   |             |                        |         |

| Supply Voltage Range<br>Normal operating range extended oper                                                 | ating range (Note 4)                                                                                                                                                                                                                                                                  | $V_{BAT}$                                                 | 2.2<br>1.8        | -<br>-      | 6.0<br>6.6             | V       |

| MC33560 Standby Quiescent Current<br>PWRON = GND, CRDCON = GND, AS<br>All Other Logic Inputs and Outputs Ope | I <sub>oBAT</sub>                                                                                                                                                                                                                                                                     | -                                                         | -                 | 30          | μΑ                     |         |

| DC Operating Current $-I_{CC} = 10 \text{ mA}$ ; $V_{CC} = 5.0 \text{ V}$ , $V_{BAT} =$                      | I <sub>BATop</sub>                                                                                                                                                                                                                                                                    | -                                                         | -                 | 12.5        | mA                     |         |

| V <sub>BAT</sub> Undervoltage Detection:<br>Upper Threshold<br>Lower Threshold<br>Hysteresis                 | -                                                                                                                                                                                                                                                                                     | -<br>-<br>-                                               | 1.6<br>1.4<br>0.2 | -<br>-<br>- | V                      |         |

| V <sub>CC</sub> = 5.0 V NOMINAL POWER SUPP                                                                   | LY SECTION                                                                                                                                                                                                                                                                            |                                                           |                   |             |                        |         |

| Output Voltage                                                                                               | $\begin{array}{l} \text{2.2 V} \leq \text{V}_{\text{BAT}} \leq 6.0 \text{ V} \\ \text{1.0 mA} \leq -\text{I}_{\text{CC}} \leq 25 \text{ mA} \\ \text{3.0 V} \leq \text{V}_{\text{BAT}} \leq 6.0 \text{ V} \\ \text{1.0 mA} \leq -\text{I}_{\text{CC}} \leq 60 \text{ mA} \end{array}$ | Vcc                                                       | 4.75<br>4.60      | 5.0<br>5.0  | 5.25<br>5.40           | V       |

| Card V <sub>CC</sub> Undervoltage Detection:<br>Upper Threshold<br>Lower Threshold<br>Switching Hysteresis   | (RDYMOD Output)<br>(See Table 4)                                                                                                                                                                                                                                                      | V <sub>T5H</sub><br>V <sub>T5L</sub><br>V <sub>HYS5</sub> | 4.2<br>120        | 4.5<br>180  | V <sub>CC</sub> - 0.14 | V<br>mV |

| Peak Output Current                                                                                          | V <sub>CC</sub> = 4.0 V, Internally Limited (RDYMOD = L)                                                                                                                                                                                                                              | -I <sub>CClim</sub>                                       | 80                | -           | -                      | mA      |

| Current limit time-out                                                                                       | V <sub>CC</sub> = 4.0 V                                                                                                                                                                                                                                                               | t <sub>d</sub>                                            | -                 | 160         | -                      | ms      |

| Startup Current                                                                                              | V <sub>CC</sub> = 2.0 V; 0°C to +85°C<br>-40°C to 0°C                                                                                                                                                                                                                                 | -I <sub>CCst</sub>                                        | 80<br>50          | -<br>-      | -                      | mA      |

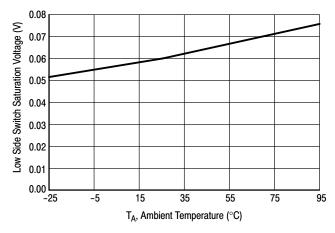

| Low Side Switch Saturation Voltage                                                                           | I <sub>L</sub> = 50 mA, Pin 22                                                                                                                                                                                                                                                        | V <sub>sat22</sub>                                        | _                 | 100         | 160                    | mV      |

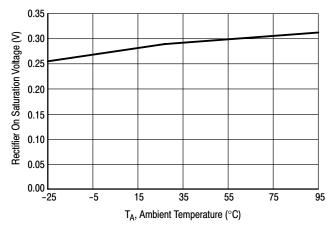

| Rectifier on Saturation Voltage                                                                              | I <sub>L</sub> = 50 mA, Pin 22 to Pin 13                                                                                                                                                                                                                                              | V <sub>Fsat22</sub>                                       | -                 | 400         | 520                    | mV      |

| Converter Switching Frequency                                                                                | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                 | f <sub>sw</sub>                                           | _                 | 120         | -                      | kHz     |

| Shutdown Current (Card access deactivated)                                                                   | PWRON = GND, $V_{CC}$ = 2.0 V                                                                                                                                                                                                                                                         | I <sub>SD</sub>                                           | 80                | -           | -                      | mA      |

| V <sub>CC</sub> = 3.0 V NOMINAL POWER SUPP                                                                   | <b>LY SECTION</b> ( $V_{BAT} = 2.5 \text{ V}$ , $-I_{CC} = 5.0 \text{ m}$                                                                                                                                                                                                             | mA)                                                       |                   |             |                        |         |

| Output Voltage                                                                                               | $2.2 \text{ V} \le \text{V}_{\text{BAT}} \le 6.0 \text{ V}$<br>$1.0 \text{ mA} \le -\text{I}_{\text{CC}} \le 10 \text{ mA}$<br>$2.5 \text{ V} \le \text{V}_{\text{BAT}} \le 6.0 \text{ V}$<br>$1.0 \text{ mA} \le -\text{I}_{\text{CC}} \le 50 \text{ mA}$                            | V <sub>CC</sub>                                           | 2.75<br>2.60      | 3.0<br>3.0  | 3.25<br>3.40           | V       |

| Card V <sub>CC</sub> Undervoltage Detection:<br>Upper Threshold<br>Lower Threshold<br>Switching Hysteresis   | (RDYMOD Output)<br>(See Table 4)                                                                                                                                                                                                                                                      | V <sub>T3H</sub><br>V <sub>T3L</sub><br>V <sub>HYS3</sub> | 2.4<br>80         | 2.7<br>110  | V <sub>CC</sub> - 0.1  | V<br>mV |

| Startup Current<br>Shutdown Current<br>(Card access deactivated)                                             | $V_{CC} = 2.0 \text{ V}$<br>PWRON = GND, $V_{CC} = 2.0 \text{ V}$                                                                                                                                                                                                                     | -I <sub>CCst</sub><br>I <sub>SD</sub>                     | 50<br>50          | -<br>-      |                        | mA      |

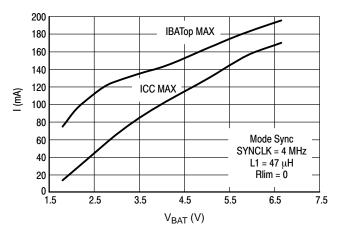

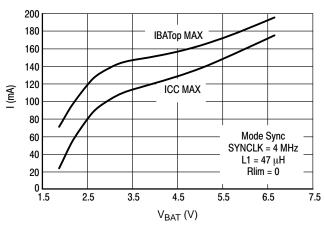

<sup>4.</sup> See Figures 2 and 3.

<sup>5.</sup> The transistors T1 on lines IO, C4 and C8 (see Figure 24) have a max  $R_{dson}$  of 250  $\Omega$

<sup>6.</sup> Pin loading = 30 pF, except INVOUT = 15 pF.

<sup>7.</sup> As the clock buffer is optimized for low power consumption and hence not symmetrical, clock signal duty cycle is guaranteed for divide by 2 and divide by 4 ratio.

<sup>8.</sup> In either direction.

**ELECTRICAL CHARACTERISTICS (continued)** These specifications are written in the same style as common for standard integrated circuits. The convention considers current flowing into the pin (sink current) as positive and current flowing out of the pin (source current) as negative. (Conditions:  $V_{BAT} = 4.0 \text{ V}$ ,  $V_{CC} = 5.0 \text{ V}$  nom, PWRON =  $V_{BAT}$ , Operating Mode,  $-I_{CC} = 10 \text{ mA}$ ,  $-25^{\circ}C \le T_{A} \le 85^{\circ}C$ ,  $L_1 = 47 \mu\text{H}$ ,  $R_{LIM} = 0 \Omega$ ,  $CRDV_{CC}$  capacitor =  $10 \mu\text{F}$ , unless otherwise noted.)

| Characteristic                                                        | Test Conditions                                                                                                                                                       | Symbol                                | Min                                                                  | Тур         | Max                                                                    | Unit |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------|-------------|------------------------------------------------------------------------|------|

| APPLICATION INTERFACE DC SEC                                          | CTION (V <sub>BAT</sub> = 5.0 V)                                                                                                                                      |                                       |                                                                      |             | •                                                                      |      |

| Input High Threshold Voltage (increasing)                             | Pins 2, 4, 5, 6, 10, 17                                                                                                                                               | V <sub>IH</sub>                       | 0.55*V <sub>BAT</sub>                                                | -           | 0.65*V <sub>BAT</sub>                                                  | V    |

| Input Low Threshold Voltage (decreasing)                              | Pins 2, 5, 6, 10<br>Pin 17<br>Pin 4                                                                                                                                   | V <sub>IL</sub>                       | 0.3*V <sub>BAT</sub><br>0.2*V <sub>BAT</sub><br>0.3*V <sub>BAT</sub> | -<br>-<br>- | 0.45*V <sub>BAT</sub><br>0.40*V <sub>BAT</sub><br>0.5*V <sub>BAT</sub> | V    |

| Switching Hysteresis                                                  | Pins 2, 4, 5, 6, 10, 17                                                                                                                                               | V <sub>HYST</sub>                     | 0.06*V <sub>BAT</sub>                                                | _           | 0.3*V <sub>BAT</sub>                                                   | V    |

| Threshold Voltage                                                     | Pin 9<br>Pin 18                                                                                                                                                       | V <sub>TH</sub>                       | 0.5*V <sub>BAT</sub><br>0.4*V <sub>BAT</sub>                         | -<br>-      | 0.6*V <sub>BAT</sub><br>0.6*V <sub>BAT</sub>                           | V    |

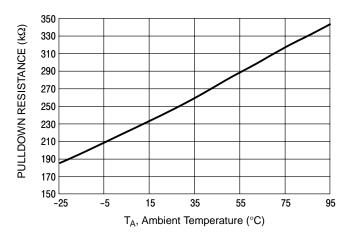

| Pulldown resistance                                                   | $V_{IN} = V_{BAT} - 1.0 \text{ V, Pins } 2, 6, 7, 10$                                                                                                                 | R <sub>down</sub>                     | 120                                                                  | 240         | 500                                                                    | kΩ   |

| Pullup resistance                                                     | V <sub>IN</sub> = 0.5 V, Pin 3, 4, 5                                                                                                                                  | $R_{up}$                              | 120                                                                  | 240         | 500                                                                    | kΩ   |

| Output High Voltage                                                   | $I_{OH} = -2.5 \mu A$ , Pin 3, Pin 4 for $\overline{CS} = H$<br>$I_{OH} = -50 \mu A$ , pins 7, 20,21<br>$I_{OH} = -0.2 \text{ mA}$ , Pin 8<br>Pin 4 ( in Output Mode) | V <sub>OH</sub>                       | V <sub>BAT</sub> – 1                                                 | -           | -                                                                      | V    |

| Output Low Voltage                                                    | I <sub>OL</sub> = 1.0 mA, Pins 7, 20, 21<br>I <sub>OL</sub> = 0.2 mA, Pins 3, 4, 8                                                                                    | V <sub>OL</sub>                       | _                                                                    | -           | 0.4                                                                    | V    |

| Input Leakage Current                                                 | V <sub>IN</sub> = 2.5 V, <del>CS</del> = H,<br>Pins 9, 17, 18, 20, 21                                                                                                 | ±I <sub>leak</sub>                    | -                                                                    | -           | 2.0                                                                    | μΑ   |

| CARD INTERFACE DC SECTION (\                                          | / <sub>BAT</sub> = 5.0 V)                                                                                                                                             |                                       |                                                                      |             |                                                                        |      |

| Output High Voltage                                                   | $I_{OH}$ = -20 $\mu$ A, Pins 11, 16, 19 $I_{OL}$ = 0.2 mA, Pins 14, 15                                                                                                | V <sub>OH</sub>                       | V <sub>CC</sub> – 0.9                                                | -           | _                                                                      | V    |

| Output Low Voltage                                                    | I <sub>OL</sub> = 1.0 mA, Pins 11, 16, 19<br>I <sub>OL</sub> = 0.2 mA, Pins 14, 15                                                                                    | V <sub>OL</sub>                       | -                                                                    | -           | 0.4                                                                    | V    |

| I/O Pullup Resistance, Operating Mode, $\overline{CS}$ =L , PWRON = H | V <sub>OL</sub> = 0.5 V, Pins 11, 16, 19                                                                                                                              | -                                     | -                                                                    | 18          | -                                                                      | kΩ   |

| Card pins security voltage<br>(Card access deactivated)               | PWRON = GND, lin = 10 mA,<br>Pins 11, 14, 15, 16, 19                                                                                                                  | V <sub>security</sub>                 | -                                                                    | -           | 2.0                                                                    | V    |

| DIGITAL DYNAMIC SECTION (VBAT                                         | = 5.0 V, Normal Operating Mode) (Note 6)                                                                                                                              |                                       |                                                                      |             |                                                                        |      |

| Input Clock Frequency                                                 | Pin 9, Duty Cycle = 50%                                                                                                                                               | f <sub>asyclk</sub>                   | -                                                                    | _           | 20                                                                     | MHz  |

| Card Clock Frequency                                                  | Pin 15                                                                                                                                                                | f <sub>crdclk</sub>                   | -                                                                    | _           | 20                                                                     | MHz  |

| Card Clock Duty Cycle (Note 7)                                        | Pin 15, 50% to 50% V <sub>CC</sub> ,<br>f <sub>io</sub> = 16 MHz                                                                                                      | r <sub>clk</sub>                      | 45                                                                   | -           | 55                                                                     | %    |

| Card Clock Rise and Fall Time                                         | Pin 15, 10% ↔ 90% V <sub>CC</sub>                                                                                                                                     | t <sub>rclk</sub> , t <sub>fclk</sub> | _                                                                    | _           | 10                                                                     | ns   |

| I/O Data Transfer Frequency                                           | Pin [7, 11], [21, 16], [20, 19] (Note 8)                                                                                                                              | f <sub>io</sub>                       | _                                                                    | 1.0         | _                                                                      | MHz  |

| I/O Duty Cycle                                                        | Pin [7, 11], [21, 16], [20, 19] (Note 8) 50% to 50% V <sub>CC</sub>                                                                                                   | r <sub>io</sub>                       | 45                                                                   | -           | 55                                                                     | %    |

| I/O Rise and Fall Time                                                | Pin [7, 11], [21, 16], [20, 19] (Note 8)<br>10% ↔ 90% V <sub>CC</sub>                                                                                                 | t <sub>rio</sub> , t <sub>fio</sub>   | -                                                                    | -           | 150                                                                    | ns   |

| I/O Transfer Time                                                     | Pin [7, 11], [21, 16], [20, 19] (Note 8) 50% to 50% $V_{CC}$ , $L \rightarrow H$ , $H \rightarrow L$                                                                  | t <sub>tr</sub>                       | -                                                                    | -           | 100                                                                    | ns   |

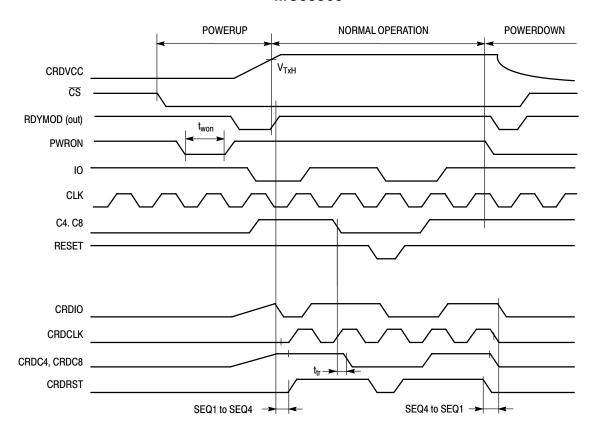

| Card Signal Sequence Interval                                         | Pins 11, 14, 15, 16, 19<br>V <sub>CC</sub> Powerup / Powerdown                                                                                                        | t <sub>dseq</sub>                     | -                                                                    | 0.2         | 1.0                                                                    | μs   |

- 4. See Figures 2 and 3.

- 5. The transistors T1 on lines IO, C4 and C8 (see Figure 24) have a max  $R_{dson}$  of 250  $\Omega$

- Pin loading = 30 pF, except INVOUT = 15 pF.

- 7. As the clock buffer is optimized for low power consumption and hence not symmetrical, clock signal duty cycle is guaranteed for divide by 2 and divide by 4 ratio.

- 8. In either direction.

**ELECTRICAL CHARACTERISTICS (continued)** These specifications are written in the same style as common for standard integrated circuits. The convention considers current flowing into the pin (sink current) as positive and current flowing out of the pin (source current) as negative. (Conditions:  $V_{BAT} = 4.0 \text{ V}$ ,  $V_{CC} = 5.0 \text{ V}$  nom, PWRON =  $V_{BAT}$ , Operating Mode,  $-I_{CC} = 10 \text{ mA}$ ,  $-25^{\circ}C \le T_{A} \le 85^{\circ}C$ ,  $L_1 = 47 \mu\text{H}$ ,  $R_{LIM} = 0 \Omega$ ,  $CRDV_{CC}$  capacitor =  $10 \mu\text{F}$ , unless otherwise noted.)

| Characteristic                                                                     | Test Conditions                          | Symbol                                    | Min      | Тур    | Max        | Unit     |  |

|------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------|----------|--------|------------|----------|--|

| DIGITAL DYNAMIC SECTION (V <sub>BAT</sub> = 5.0 V, Normal Operating Mode) (Note 6) |                                          |                                           |          |        |            |          |  |

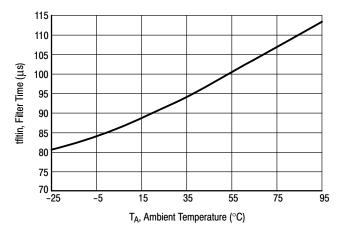

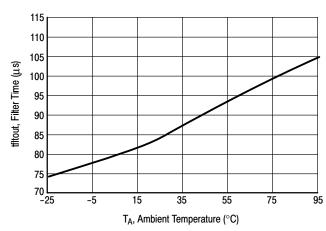

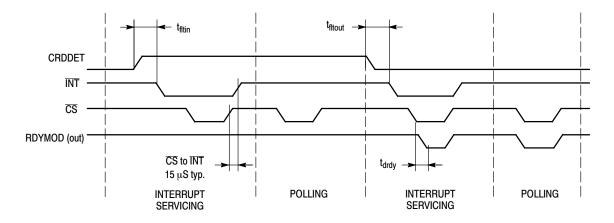

| Card Detection Filter Time:<br>Card Insertion<br>Card Extraction                   |                                          | t <sub>fltin</sub><br>t <sub>fltout</sub> | 50<br>50 | -<br>- | 150<br>150 | μs<br>μs |  |

| Internal Reset Delay                                                               | RES, V <sub>CC</sub> Powerup / Powerdown | t <sub>dres</sub>                         | -        | 20     | -          | μS       |  |

| Ready Delay Time                                                                   | Pin 4                                    | t <sub>drdy</sub>                         | -        | -      | 2.0        | μs       |  |

| PWRON low Pulse Width                                                              | CS = L, Pin 2                            | t <sub>won</sub>                          | 2.0      | -      | -          | μs       |  |

| DIGITAL DYNAMIC SECTION (VBAT                                                      | 5.0 V, programming mode) (Note 6)        |                                           |          |        |            |          |  |

| Data Setup Time<br>RDYMOD, PWRON, RESET, IO                                        | Pins 2, 4, 6, 7                          | t <sub>smod</sub>                         | 1.0      | -      | _          | μS       |  |

| Data Hold Time<br>RDYMOD, PWRON, RESET, IO                                         | Pins 2, 4, 6, 7                          | t <sub>hmod</sub>                         | 1.0      | -      | -          | μs       |  |

| CS low Pulse Width                                                                 | Pin 5                                    | t <sub>wcs</sub>                          | 2.0      | _      | _          | μS       |  |

- 4. See Figures 2 and 3.

- 5. The transistors T1 on lines IO, C4 and C8 (see Figure 24) have a max  $R_{dson}$  of 250  $\Omega$

- 6. Pin loading = 30 pF, except INVOUT = 15 pF.

- 7. As the clock buffer is optimized for low power consumption and hence not symmetrical, clock signal duty cycle is guaranteed for divide by 2 and divide by 4 ratio.

- 8. In either direction.

Figure 2. Maximum Battery and Card Supply Current vs. V<sub>BAT</sub> (V<sub>CC</sub> = 5.0 V)

Figure 3. Maximum Battery and Card Supply Current vs. V<sub>BAT</sub> (V<sub>CC</sub> = 3.0 V)

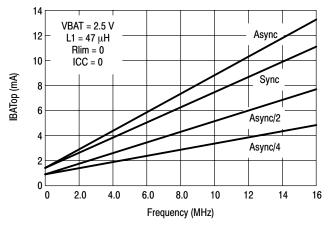

Figure 4. Battery Current vs. Input Clock Frequency  $(I_{CC} = 0, V_{BAT} = 4.0 \text{ V})$

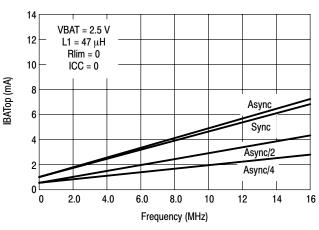

Figure 5. Battery Current vs. Input Clock Frequency  $(I_{CC} = 0, V_{BAT} = 2.5 \text{ V})$

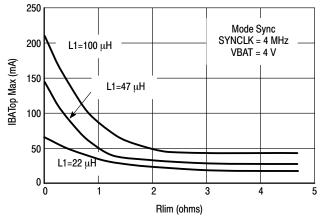

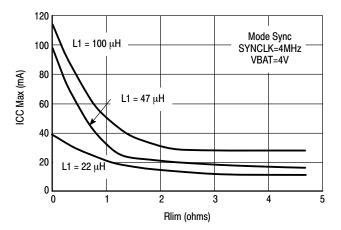

Figure 6. Maximum Battery Current vs.  $R_{LIM}$  ( $V_{CC} = 5.0 \text{ V}, V_{BAT} = 4.0 \text{ V}$ )

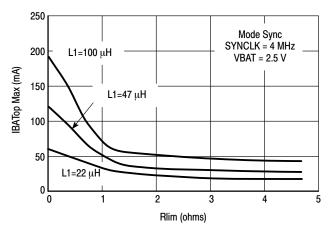

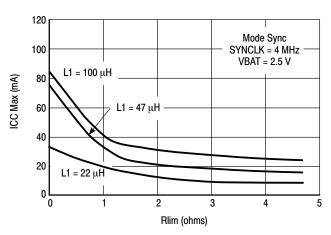

Figure 7. Maximum Battery Current vs.  $R_{LIM}$  ( $V_{CC} = 3.0 \text{ V}, V_{BAT} = 2.5 \text{ V}$ )

Figure 8. Maximum Card Supply Current vs.  $R_{LIM}$  ( $V_{CC} = 5.0 \text{ V}$ ,  $V_{BAT} = 4.0 \text{ V}$ )

Figure 9. Maximum Card Supply Current vs.  $R_{LIM}$  ( $V_{CC} = 3.0 \text{ V}, V_{BAT} = 2.5 \text{ V}$ )

Figure 10. Low Side Switch Saturation Voltage (I<sub>L</sub> = 50 mA) vs. Temperature

Figure 11. Rectifier On Saturation Voltage  $(I_L = 50 \text{ mA}) \text{ vs. Temperature}$

Figure 12. Card Detection (Insertion) Filter Time vs. Temperature

Figure 13. Card Detection (Extraction) Filter Time vs. Temperature

Figure 14. Pulldown Resistance vs. Temperature

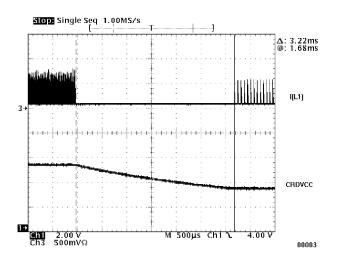

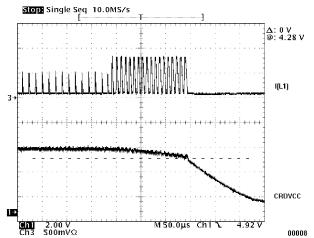

Figure 15. Transition from 5.0 V to 3.0 V Card Supply

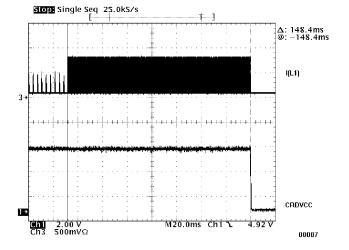

Figure 17. Overcurrent Shutoff (t<sub>d</sub> = 160 ms)

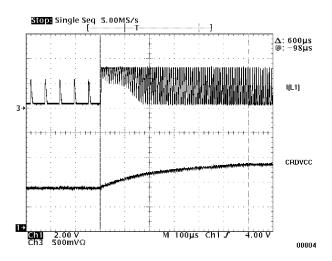

Figure 16. Transition from 3.0 V to 5.0 V Card Supply

Figure 18. Undervoltage Shutoff ( $V_{T5L} = 4.6 \text{ V}$ )

Figure 19. Functional Block Diagram

#### Table 1 PIN FUNCTION DESCRIPTION

| Pin  | Symbol     | Туре                        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CON  | ROLLER INT | ERFACE                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2    | PWRON      | INPUT<br>Pulldown           | This pin is used to start operation of the internal DC–DC converter. In programming mode, this pin is used to set the "Output Voltage" switch. (See Table 2).                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3    | INT        | OUTPUT<br>Pullup            | This open collector pin indicates a change in the card presence circuit status. When a card is inserted or extracted, the pin goes to logic level "0". The signal is reset to logic level "1" upon the rising edge of CS or upon the rising edge of PWRON. In the case of a multislot application, two or more INT outputs are connected together and the microcontroller has to poll all the MC33560s to identify which slot was detected.                                                                                                                                        |

| 4    | RDYMOD     | I/O and Pullup              | This bidirectional pin has tri–state output and Schmitt trigger input.  * When RDYMOD is forced to 0, the MC33560 can be set to programming mode by a negative transition on \overline{\overline{\scrt{CS}}}.  * When RDYMOD is connected to a high impedance, the MC33560 is in normal operating mode, and RDYMOD is in output mode (See Tables 2 and 4):  - With \overline{\overline{\scrt{CS}}} = L and PWRON=H, RDYMOD indicates the status of the DC-DC converter.  - With \overline{\overline{\scrt{CS}}} = L and PWRON=L, RDYMOD indicates the status of the card detector. |

| 5    | CS         | INPUT Pullup                | This is the MC33560 chip select signal. Pins 2, 6, 7, 10, 20, 21 are disabled when $\overline{\text{CS}} = \text{H}$ . When RDYMOD = L, the MC33560 enters programming mode upon the falling edge of $\overline{\text{CS}}$ . (Figure 20)                                                                                                                                                                                                                                                                                                                                          |

| 6    | RESET      | INPUT<br>Pulldown           | The signal present at this input pin is translated to Pin 14 (the card reset signal) when $\overline{CS} = L$ . The signal on this pin is latched when $\overline{CS} = H$ . This pin is also used in programming mode. (See Table 2)                                                                                                                                                                                                                                                                                                                                              |

| 7    | I/O        | I/O                         | This pin connects to the Serial I/O port of a microcontroller. A bi–directional level translator adapts the serial I/O signal between the smartcard and the microcontroller. The level translator is enabled when $\overline{\text{CS}}$ = L. The signal on thispin is latched when $\overline{\text{CS}}$ =H. This pin is also used in programming mode. (See Table 2)                                                                                                                                                                                                            |

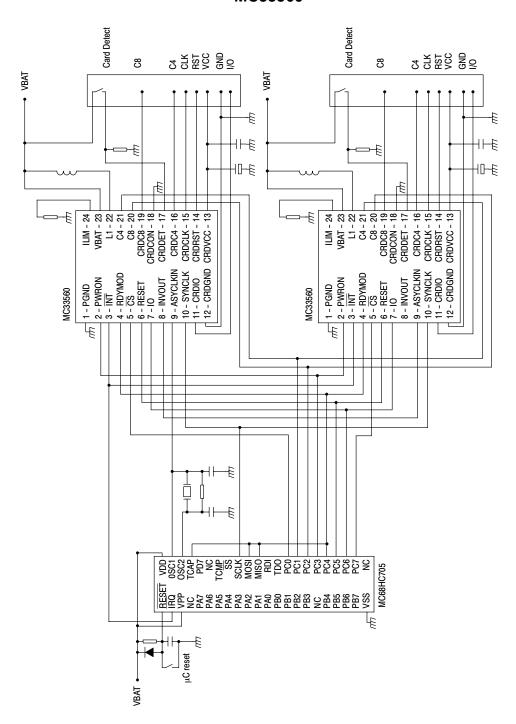

| 8    | INVOUT     | CLK<br>OUTPUT               | The ASYCLKIN (Pin 9) signal is buffered and inverted to generate the output signal INVOUT. This output is used for multislot applications, where the ASYCLKIN inputs and INVOUT outputs are daisy–chained. (See the multislot application example in Figure 31)                                                                                                                                                                                                                                                                                                                    |

| 9    | ASYCLKIN   | CLK INPUT<br>high impedance | This pin can be connected to the microcontroller master clock or any clock signal for asynchronous cards. The signal is fed to the internal clock selector circuit, and is translated to CRDCLK at the same frequency, or divided by 2 or 4, depending on programming. (See Table 3)                                                                                                                                                                                                                                                                                               |

| 10   | SYNCLK     | CLK INPUT<br>Pulldown       | This function is used for communication with synchronous cards, and the pin is generally connected to the controller serial interface clock signal. The signal is fed to the internal clock selector circuit, and is translated to CRDCLK upon appropriate programming of the MC33560 (See Table 3). When selected at programming, the signal on this pin is latched when $\overline{\text{CS}} = \text{H}$ .                                                                                                                                                                      |

| 20   | C8         | I/O                         | General purpose input/output. It has the same behavior as I/O, except for programming. It can be connected to a bidirectional port of the microcontroller. The level translator is enabled when CS = L, and the signal is latched when CS = H. (Compare with Pin 19)                                                                                                                                                                                                                                                                                                               |

| 21   | C4         | I/O                         | General purpose input/output. It has the same behavior as I/O, except for programming. It can be connected to a bidirectional port of the microcontroller. The level translator is enabled when $\overline{CS} = L$ , and the signal is latched when $\overline{CS} = H$ . (Compare with Pin 16)                                                                                                                                                                                                                                                                                   |

| CARI | INTERFACE  |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11   | CRDIO      | I/O                         | This pin connects to the serial I/O pin of the card connector. A bidirectional level translator adapts the serial I/O signal between the card and the microcontroller. (Compare with Pin 7)                                                                                                                                                                                                                                                                                                                                                                                        |

| 14   | CRDRST     | OUTPUT                      | This pin connects to the RESET pin of the card connector. A level translator adapts the RESET signal driven by the microcontroller. (Compare with Pin 6)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15   | CRDCLK     | OUTPUT                      | This pin connects to the CLK pin of the card connector. The CRDCLK signal is the output of the clock selector circuit. The clock selection is programmed using Pins 2, 6 and 7 with RDYMOD forced to "0".                                                                                                                                                                                                                                                                                                                                                                          |

| 16   | CRDC4      | I/O                         | General purpose input/output. It has the same behavior as CRDIO. It can be connected to the C4 pin of the card connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17   | CRDDET     | INPUT high impedance        | This pin connects to the card detection switch of the card connector. Card detection phase is determined with Pin 18. This pin needs an external pullup or pulldown resistor to operate properly.                                                                                                                                                                                                                                                                                                                                                                                  |

| 18   | CRDCON     | INPUT high impedance        | This pin connects to PGND or $V_{BAT}$ , or possibly to an output port of the microcontroller. With this pin set to a logic "0", the presence of a card is signalled with a logic "1" on Pin 17. With this pin set to a logic "1", the presence of a card is signalled with a logic "0" on Pin 17.                                                                                                                                                                                                                                                                                 |

**Table 1. PIN FUNCTION DESCRIPTION**

**POWER**

**POWER**

$V_{BAT}$

ILIM

24

| Pin  | Symbol             | Туре            | Name/Function                                                                                                                                              |  |  |  |

|------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CARI | CARD INTERFACE     |                 |                                                                                                                                                            |  |  |  |

| 19   | CRDC8              | I/O             | General purpose input/output. It has the same behavior as CRDIO. It can be connected to the C8 pin of the card connector.                                  |  |  |  |

| CUR  | RENT LIMIT AN      | ND THERMAL PROT | ECTION                                                                                                                                                     |  |  |  |

| 1    | PGND               | POWER           | This pin is the return path for the current flowing into Pin 22 (L1). It must be connected to CRDGND using appropriate grounding techniques.               |  |  |  |

| 12   | CRDGND             | POWER           | This pin is the signal ground. It must be connected to the ground pin of the card connector. It is the reference level for all analog and digital signals. |  |  |  |

| 13   | CRDV <sub>CC</sub> | POWER           | This pin connects to the $V_{CC}$ pin of the card connector. It is the reference level for a logic "1" of Pins 11, 14, 15, 16 and 19.                      |  |  |  |

| 22   | L1                 | POWER           | This pin connects to an external inductance for the DC–DC converter. Please refer to the description of the DC–DC converter functional block.              |  |  |  |

#### PROGRAMMING AND STATUS FUNCTIONS

depending on the peak coil current needed to supply the card.

minimum value.

This pin is connected to the supply voltage. Logic level "1" of Pins 2 to 10, 17, 18, 20 and 21 is

This pin can be connected to the PGND pin, or to a resistor connected to PGND, or left open,

referenced to V<sub>BAT</sub>. Operation of the MC33560 is inhibited when V<sub>BAT</sub> is lower than the

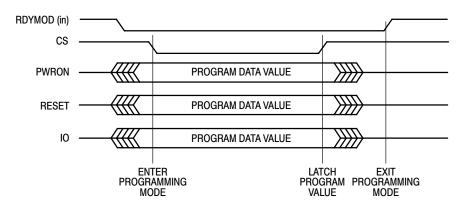

The MC33560 features a programming interface and a status interface. Figure 20 shows how to enter and exit programming mode; Table 2 shows which pins are used to access the various functions.

Figure 20. MC33560 Programming Sequence

Table 2. PIN USE FOR PROGRAMMING AND STATUS FUNCTIONS

|                    | Programs CRDV-<br>CC<br>TO 3 V/5 V | Select V <sub>CC</sub><br>ON/OFF | Select<br>Clock Input       | Program ASYCLKIN<br>Divide Ratio | Poll Card<br>Status | Poll CRDV <sub>CC</sub><br>Status |

|--------------------|------------------------------------|----------------------------------|-----------------------------|----------------------------------|---------------------|-----------------------------------|

| RDYMOD<br>(In/Out) | Force to 0                         | READ                             | Force to 0                  | Force to 0                       | READ                | READ                              |

| CS (In)            | rising edge                        | 0                                | rising edge                 | rising edge                      | 0                   | 0                                 |

| PWRON              | 0/1                                | 0/1                              | Programs CRDV <sub>CC</sub> | Programs CRDV <sub>CC</sub>      | 0 or Hi–z           | 1                                 |

| RESET(In)          | Programs CLK<br>Input/Divide Ratio | NOT USED                         | 0/1                         | 0/1                              | NOT USED            | NOT USED                          |

| I/O(In)            | Programs CLK<br>Input/Divide Ratio | NOT USED                         | 0/1                         | 0/1                              | NOT USED            | NOT USED                          |

#### CARD V<sub>CC</sub> AND CARD CLOCK PROGRAMMING

The CRDV<sub>CC</sub> and ASYCLK programming options allow the system clock frequency to be matched to the card clock frequency and to select 3.0 V or 5.0 V CRDV<sub>CC</sub> supply. Table 3 shows the values of **PWRON**, **RESET** and **I/O** for the possible options. The default power reset condition is state 4 (synchronous clock and CRDV<sub>CC</sub> =5.0 V). All states are latched for each output variable in programming mode at the positive transition of  $\overline{CS}$  (Figure 20).

Table 3. CARD V<sub>CC</sub> AND CARD CLOCK TRUTH TABLE

| STATE# | PWRON | RESET | I/O | CRDV <sub>CC</sub> | CRDCLK     |

|--------|-------|-------|-----|--------------------|------------|

| 0      | L     | L     | L   | 3 V                | SYNCLK     |

| 1      | L     | L     | Н   | 3 V                | ASYCLKIN/4 |

| 2      | L     | Н     | Н   | 3 V                | ASYCLKIN/2 |

| 3      | L     | Н     | L   | 3 V                | ASYCLKIN   |

| 4      | Н     | L     | L   | 5 V                | SYNCLK     |

| 5      | Н     | L     | Н   | 5 V                | ASYCLKIN/4 |

| 6      | Н     | Н     | Н   | 5 V                | ASYCLKIN/2 |

| 7      | Н     | Н     | L   | 5V                 | ASYCLKIN   |

NOTE: Card clock integrity is maintained during all frequency commutations (no spikes). State 4 is the default state at power on.

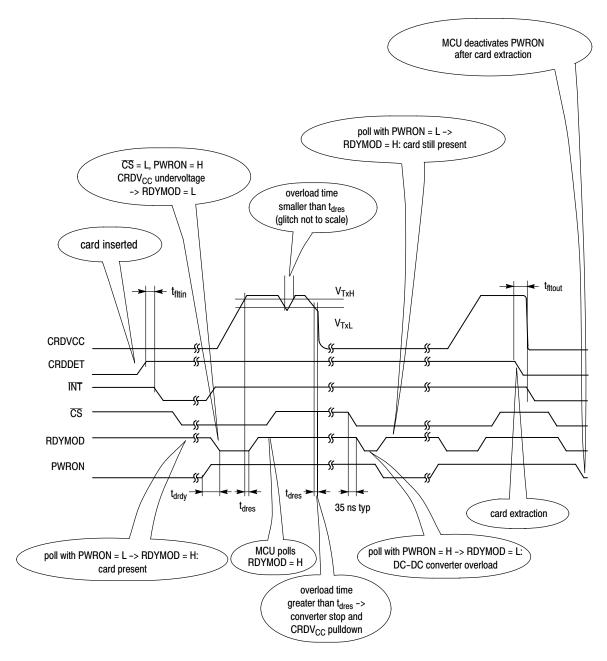

#### DC-DC CONVERTER AND CARD DETECTOR STATUS

The MC33560 status can be polled when  $\overline{\mathbf{CS}} = \mathbf{L}$ . Please consult Table 2 for a description of input and output signals. The significance of the status message is described in Table 4.

**Table 4. RDYMOD STATUS MESSAGES**

| PWRON<br>(Input) | RDYMOD<br>(Output) | Message                  |

|------------------|--------------------|--------------------------|

| LOW              | LOW                | No card                  |

| LOW              | HIGH               | Card present             |

| HIGH             | LOW                | DC-DC converter overload |

| HIGH             | HIGH               | DC-DC converter OK       |

#### **DETAILED OPERATING DESCRIPTION**

#### INTRODUCTION

The MC33560 Smartcard interface IC has been designed to provide all necessary functions for safe data transfers between a microcontroller and a smartcard or memory card.

A card detector scans for the presence of a card and generates a debounced wake-up signal to the microcontroller.

Communication and control signal levels are translated between the digital interface and the card interface by the voltage level translator, and the card clock is matched to the system clock frequency by the programmable card clock generator. The power management unit enables the DC–DC converter for card power supply, supervises the powerup/down sequence of the card's I/O and signal lines, and keeps the power consumption very low in standby mode.

All card interface pins have adequate ESD protection, and fault monitoring ( $V_{BATlow}$ ,  $V_{CClow}$ ,  $I_{CClim}$ ) guarantees hazard free card reader operation.

Several MC33560s can be operated in parallel, using the same control and data bus, through the use of the chip select signal CS.

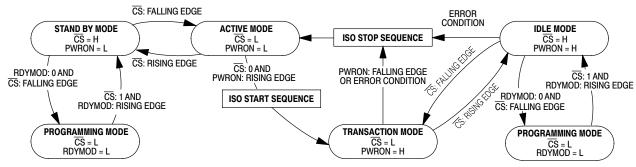

Figure 21. MC33560 Operating Modes

#### **OPERATING MODES**

The MC33560 has five operating modes:

- Standby

- Programming

- Active

- Transaction

- Idle

The transitions between these different states are shown in Figure 21 above.

#### STANDBY MODE

Standby mode allows the MC33560 to detect card insertion and monitor the power supply while keeping the power consumption at a minimum. It is obtained with  $\overline{CS} = H$  and PWRON = L.

When the MC33560 detects a card,  $\overline{INT}$  is asserted low to wake up the Microcontroller.

#### PROGRAMMING MODE

The programming mode allows the user to configure the card  $V_{CC}$  and the card clock signal for his specific application. The card supply,  $CRDV_{CC}$ , can be programmed to 3 V or 5 V, and the card clock signal can be defined to be either synchronous, or asynchronous divided by 1, 2 or 4.

Programming mode is obtained with **RDYMOD** = **L** followed by a negative transition on  $\overline{CS}$ . The programming options are shown in Table 3. Programmed values are latched on a positive transition of  $\overline{CS}$  with **RDYMOD** = **L**.

#### **ACTIVE MODE**

In active mode, the MC33560 is selected, the **RDYMOD** pin becomes an output, and the MC33560 status can be polled. Power is not applied to the card.

The microcontroller polls the MC33560 by asserting  $\overline{\textbf{CS}} = \textbf{L}$  and reading the **RDYMOD** pin.

If a card is present, the microcontroller starts the DC–DC converter by asserting **PWRON=H**. This starts the automatic power on sequence: when CRDV<sub>CC</sub> reaches the undervoltage level (V<sub>T5H</sub> or V<sub>T3H</sub>, depending on programming), the card sequencer validates **CRDIO**, **CRDRST**, **CRDCLK**, **CRDC4**, **CRDC8** pins according to the ISO7816–3 sequence (Figure 26). The MC33560 is now in transaction mode, and the system is ready for data exchange via the three I/O lines and the **RESET** line.

#### TRANSACTION MODE

In transaction mode, the MC33560 maintains power and the selected clock signal applied to the card, and the levels of the I/O, RESET, C4 and C8 signals between the microcontroller and the card are translated depending on the supply voltages  $V_{BAT}$  and  $V_{CC}$ .

The DC-DC converter status can be monitored on the **RDYMOD** pin.

#### **IDLE MODE**

Idle mode is used when maintaining a card powered up without communicating with it. When an asynchronous clock is used, the selected clock signal is applied to the card.

#### **POWERDOWN OPERATION**

Powerdown can be initiated by the controlling microprocessor, by stopping the DC–DC converter with PWRON = L while  $\overline{CS} = L$ , or by the MC33560 itself when an error condition has been detected (CRDV<sub>CC</sub> undervoltage, overcurrent longer than 160 ms typ., overtemperature, "hot" card extraction). The communication session is terminated in a given sequence defined in ISO7816–3.

The MC33560 then goes into active mode, in which its status can be polled.

Standby mode is reached by deselecting the MC33560  $\overline{(CS} = H)$ .

## FUNCTIONAL BLOCKS CARD DETECTOR

This block monitors the card contact **CRDDET** (during insertion and extraction), filters the incoming waveform and generates an interrupt signal  $\overline{INT}$  after each change. In order to identify which coupler activated the  $\overline{INT}$  line (multicoupler application) the microcontroller scans both circuits via  $\overline{CS}$  and reads the **RDYMOD** pin.

The programming input **CRDCON** tells the level detector which type of mechanical contact is implemented (normally open or normally closed). Special care is taken to hold the current consumption very low on this part of the circuit which is continuously powered by the  $V_{BAT}$  supply.

The **CRDDET** pin has high impedance input, and an external resistor must be connected to pullup or pulldown, depending on **CRDCON**. This resistor is chosen according to the maximum leakage current of the card connector and the PCB.

The card detector has an internal 50  $\mu$ s debouncing delay. The micro controller has to insert an additional delay (in the ms range) to allow the card contacts to stabilize in the card connector before setting **PWRON** = **H**.

When the card detector circuit detects a card extraction, it activates the powerdown sequence and stops the converter, regardless of the **PWRON** signal. The 50  $\mu$ s delay of the debouncer is enough to ensure that all card signals have reached a safe value before communication with the card takes place.

#### **CARD STATUS**

The controlling microprocessor is informed of the MC33560 status by interrupt and by polling. When a card is extracted or inserted, the  $\overline{INT}$  line is asserted low. The interrupt is cleared upon the rising edge of  $\overline{CS}$  or upon the rising edge of **PWRON** ( $\overline{INT}$  line set to high state).

The microprocessor can poll the status at any time by reading the **RDYMOD** pin with proper **PWRON** setting (see Tables 2 and 4).

Since  $\overline{\textbf{INT}}$  and RDYMOD have a high value pullup resistor (240 k $\Omega$  typical), their rise time can be as long as 10  $\mu$ s if parasitic capacitance is high and no other pullup circuitry is connected.

#### **POWER MANAGER**

The task of the power manager is to activate only those circuit functions which are needed for a determined operating mode in order to minimize power consumption (Figure 19).

In standby mode (**PWRON** = **L**) the power manager keeps only the "card present" detector alive. All card interface pins are forced to ground potential.

In the event of a powerup request from the microcontroller (PWRON L to H transition,  $\overline{CS}$  = L) the power manager starts the DC-DC converter. As soon as the  $CRDV_{CC}$  supply reaches the operating voltage range, the circuit activates the card signals in the following sequence:

$CRDV_{CC}$ , CRDIO, CRDCLK, CRDC4/C8, CRDRST At the end of the transaction (**PWRON** reset to **L**,  $\overline{CS} = L$ ) or forced card extraction, the  $CRDV_{CC}$  supply powers down and the card signal deactivation sequence takes place: CRDRST, CRDC4/C8, CRDCLK, CRDIO,  $CRDV_{CC}$

When  $\overline{CS} = L$ , the bi-directional signal lines (I/O, C4 and C8) are put into high impedance state to avoid signal collision with the microcontroller in transmission mode.

#### **BATTERY UNDERVOLTAGE DETECTOR**

The task of this block is to monitor the supply voltage, and to allow operation of the DC–DC converter only with valid voltage (typically 1.5 V). The comparator has been designed to have stability better than 20 mV in the temperature range.

#### DC-DC CONVERTER

Upon request from the power manager, the DC-DC converter generates the **CRDV**<sub>CC</sub> supply for the smartcard.

The output voltage is programmable for 3.0 V or 5.0 V (see Table 3) to guarantee full cross compatibility of the reader for 5.0 V and 3.0 V smartcards. The wide voltage supply range, 1.8 V <  $V_{BAT}$  < 6.6 V, accommodates a broad range of coupler applications with different battery configurations (single cell or multiple cells, serial or parallel connections).

The  $\mathbf{CRDV_{CC}}$  is current–limited and short–circuit–proof. To avoid excessive battery loading during a card short–circuit, a current integration function forces the powerdown sequence (Figure 28). To retry the session, the microprocessor works through the power on sequence as defined in the power manager section.

#### DC-DC CONVERTER OPERATING PRINCIPLES

The DC-DC converter architecture used in the MC33560 allows step-up and step-down voltage conversion to be done. The unique regulation architecture permits an automatic transition from step-up to step-down, and from zero to full load, without affecting the output characteristics.

**DC-DC** Converter Description: The converter architecture is very similar to the boost architecture, with an active rectifier in place of the diode. The switching transistor is connected to ground through a resistor network in order to adjust the maximum peak current (Figure 22). A transistor connected to the converter output (**CRDV**<sub>CC</sub>) forces this pin to a low voltage when the converter is not operating. This prevents erratic voltage supply to the smartcard when not in use.

The MC33560 has a built in oscillator; the DC-DC converter requires only one inductor and the output filtering capacitor to operate.

**Stepup Operation:** When the card supply voltage is lower than the battery voltage, the converter operates like a boost converter; the active rectifier behavior is similar to that of a diode.

**Stepdown Operation:** When the card supply voltage is higher than the battery voltage, the rectifier control circuit puts the power rectifying transistor in conduction when the  $L_1$  voltage reaches  $V_{BAT} + V_{FSAT22}$ . The voltage across the rectifying transistor is higher than in step—up operation. The efficiency is lower, and similar to a linear regulator.

**Fault Detection:** The DC–DC converter has several features that help to avoid electrical overstress of the MC33560 and of the smartcard, and help to ensure that data transmission with the smartcard occurs only when its supply voltage is within predetermined limits. These functions are:

- Overtemperature Detection,

- Current Limitation, and

- Card Supply Undervoltage Detection.

The level at which current will be limited is defined by the maximum card supply current programmed with the external components L1 and RLIM.

The undervoltage detection levels for 3.0 V and 5.0 V card supply are preset internally to the MC33560.

Figure 22. DC-DC Converter Functional Block

The overcurrent and undervoltage protection features are complementary, and will shut the circuit off either if the overcurrent is high enough to bring the  $CRDV_{CC}$  output below the preset threshold, either after 160 ms (typ.)

In addition, the DC–DC converter will be allowed to start only if the battery supply voltage is high enough to allow normal operation (1.8 V).

The undervoltage comparator has a hysteresis and a delay of typically 20 ms to ensure stable operation. The current detector is a comparator associated with two resistors: one  $2.0~\Omega$  attached to PGND and usually connected to analog ground, and a  $0.5~\Omega$  attached to ILIM, usually connected to ground through an external resistor to adjust the maximum peak current. The voltage developed across this resistor network is then compared to a 120 mV (typical) reference voltage, and the comparator output performs a cycle–by–cycle peak current limitation by switching off the low side transistor when the voltage exceeds 120 mV.

The internal **ILIMCOMP** signal is monitored to stop the converter if current limitation is continuously detected during 160 ms (typical). This allows normal operation with high filtering capacitance and low peak current, even at converter startup. As a result, a short circuit to ground on the card connector or a continuous overcurrent is reported by **RDYMOD** 160 ms (typical) after powerup.

Unexpected Card Extraction: The MC33560 detects card extraction and runs a powerdown sequence if card power is still on when extraction occurs. An active pulldown switch clamps  $CRDV_{CC}$  to GND within 150  $\mu s$  (max) after extraction is detected. The external capacitors will then be discharged. With typical capacitor values of 10  $\mu F$  and 47 nF as indicated in the application schematic, the time needed to discharge  $CRDV_{CC}$  to a voltage below 0.4 V can be

estimated to less than 750  $\mu s.$  The total time aftercard extraction detection until CRDV\_{CC} reaches 0.4 V is then estimated to 900  $\mu s$  (maximum). All smartcard connector contacts will be deactivated before CRDV\_{CC} deactivation. This ensures that no electrical damage will be caused to the smartcard under abnormal extraction conditions.

**3.0 V/5.0 V Programming:** It is possible to set the card supply voltage to 3.0 V or 5.0 V at any time, before DC–DC converter start, or during converter operation. When switching from 3.0 V to 5.0 V, a 160 ms (typical) delay blanks the undervoltage fault detection to allow filter capacitor charging.

**PWM:** The free–running integrated oscillator has two working modes:

Variable on–state and fixed frequency (typically 120 KHz) for average to heavy loads.

Variable on-state and variable frequency for light loads.

The frequency can be as low as a few kHz if no load is connected to  $\mathbf{CRDV}_{\mathbf{CC}}$ .

The charging current of the timing capacitor is related to the  $V_{BAT}$  supply voltage, to allow better line regulation, and to increase stability.

Filtering Capacitor: A high value allows efficient filtering of card current spikes. Low values allow low startup charging current. Care must be taken not to combine low capacitor value with high current limiting, as this can generate high ripple. Usual values range from 4.7  $\mu F$  to 47  $\mu F$ , depending on current limiting.

Selecting the External Components L1 and RLIM: The choice of inductor L1 and resistor R4 is made by using Figure 8 (5.0 V card) and/or Figure 9 (3.0 V card) on page 8:

First, determine the maximum current that the application requires to supply to the card (ICCmax, on the y-axis)

Then, select one curve that crosses the selected  $ICC_{max}$  level. The curve is associated with an inductance value (22  $\mu$ H, 47  $\mu$ H, or 100  $\mu$ H).

Finally, use the intersection of the curve and the ICCmax level to find the  $R_{lim}$  value on the x-axis.

Good starting values are : L1 = 47  $\mu$ H;  $R_{lim}$  = 0.5  $\Omega$

Note also that, for a high inductance value (100  $\mu$ H), the filtering capacitor is generally charged before inductance current reaches current limitation, while for allow inductance value, the current limitation is activated after a few converter cycles.

**Battery Requirements:** Having determined the  $L_1$  and  $R_{lim}$  values, the maximum current drawn from the battery supply is shown by the curves in Figures 6 and 7.

When the application is powered by a single 3.0 V battery, special care has to be taken to extend its lifetime. When lithium batteries approach the end-of-life, their internal resistance increases, while voltage decreases. This phenomenon can prevent the startup of the DC-DC converter if the current limiting is set too high, because of the filtering capacitor charging current.

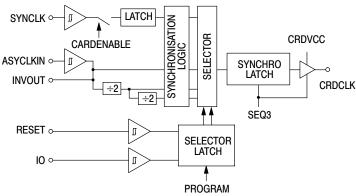

#### **CLOCK GENERATOR**

The primary purpose of the clock generator module is to match the smartcard operating frequency to the system frequency. The source frequency can be provided to **ASYCLKIN** by the microcontroller itself or from an external oscillator circuit.

In programming mode (RDYMOD=L and  $\overline{CS}$  asserted low) the three input variables PWRON, I/O and RESET are used to configure the two output variables CRDV<sub>CC</sub> and CRDCLK as described in Table 3. This circuit setup is latched during the positive transition of  $\overline{CS}$ .

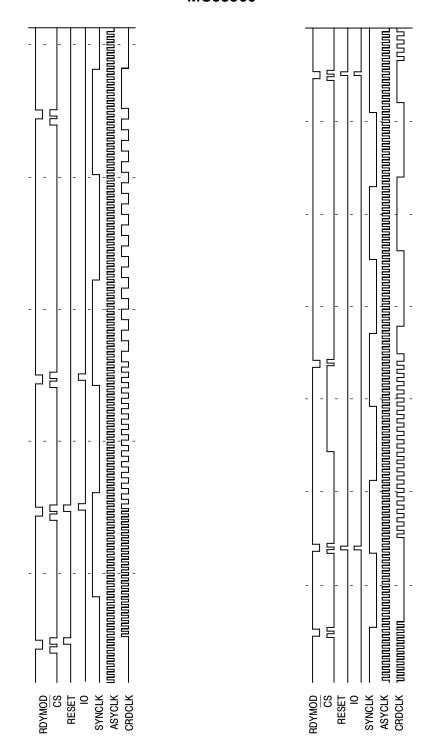

Furthermore, in asynchronous mode the system clock frequency **ASYCLKIN** can be divided by a factor of 1, 2 or 4. The circuit controls the frequency commutation to guarantee that the card clock signal remains free from spikes and glitches. In addition, this circuit ensures that **CRDCLK** signal pulses will not be shorter than the shortest and/or longer than the longest of the clock signals present before and after programming changes.

The **INVOUT** output is provided to drive other circuits without additional load to the microprocessor quartz oscillator. It can also be used to build a local RC oscillator. This driver has been optimized for low consumption; it has no hysteresis, and input levels are not symmetrical. If the **ASYCLKIN** pin is connected to a sine wave, the duty cycle will not always be 50% at **INVOUT**.

#### **CLOCK GENERATOR OPERATING PRINCIPLES**

**Synchronous Clock:** This clock is used mainly for memory cards. It can also be used for asynchronous (microprocessor) cards, allowing the use of two different clock sources. The status of **SYNCLK** is latched at **CRDCLK** when  $\overline{CS}$  goes high, so that data (the **I/O** pin) and clock are always consistent at the card connector, whatever the  $\overline{CS}$  status is. When using the synchronous clock, the clock output becomes active only when the MC33560 is selected with  $\overline{CS}$ .

Asynchronous Clock: This clock is used mainly for microprocessor cards. When applied, the clock output remains active even when the MC33560 is not selected with  $\overline{CS}$ , in order to keep the microprocessor running and avoid an unwanted reset. The ASYCLKIN signal is buffered at the INVOUT pin, so that several MC33560 systems can use the same clock with one load only.

Depending on programming, the frequency is fed directly, or divided by 2 or by 4 to the **CRDCLK** pin. If the duty cycle of the applied clock signal is not exactly symmetrical, it is recommended that the clock signal be divided by two or four to guarantee 50% duty cycle.

Clock Signal Synchronization and Consistency (Figure 29). The clock divider includes synchronization logic that controls the switch from synchronous clock to asynchronous (and vice—versa), from any division ratio to any other ratio, during  $\overline{\textbf{CS}}$  changes and at powerup. The synchronization logic guarantees that each clock cycle on the **CRDCLK** pin is finished before changing clock selection (and has always the adequate duration), regardless of the moment the programming is changed.

At powerup, when **ASYCLKIN** is selected, the clock signal at the **CRDCLK** pin has an entire length, according to the selected divide ratio, whatever the **ASYCLKIN** signal is versus the internal sequencer timing.

Figure 23. Clock Generator Functional Block

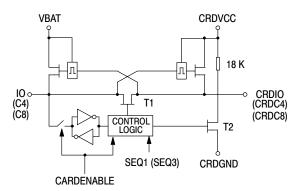

#### BIDIRECTIONAL LEVEL TRANSLATOR

This module (used on **I/O/CRDIO**, **C4/CRDC4**, **C8/CRDC8**, Figure 24) adapts the signal voltage levels of the I/O and control lines between the micro controller (supplied by  $V_{BAT}$ ) and the smartcard (supplied by  $CRDV_{CC}$ )

When  $\overline{\textbf{CS}}$  is low, with  $\textbf{CRDV}_{\textbf{CC}}$  on, and start sequencing completed, this module is transparent for the data, and acts as if the card was directly connected to the reader microcontroller. The core of the level shifter circuit defined for the bidirectional CRDIO, CRDC4 and CRDC8 lines consists of a NMOS switch which can be driven to the logic low state from either side (microcontroller or card). If both sides work in transmission mode with opposite phase, then signal collision on the line is not avoidable. In this case, the peak current is limited to a safe value for the integrated circuit and the smartcard.

During high–to–low transitions, the NMOS transistor impedance (T1 = 250  $\Omega$  maximum) is low enough to charge parasitic capacitance, and have a high enough dv/dt. On low to high transition, the NMOS transistor is not active above a certain voltage, and an acceleration circuit is activated to ensure a high dv/dt.

When the chip is disabled ( $\overline{CS} = H$ ) with the voltage supply  $CRDV_{CC}$  still active, the I/O, C4 and C8 lines keep their last logic state.

When the converter is off, a transistor forces the **CRDIO**, **CRDC4** and **CRDC8** lines to a low state, thus preventing any unwanted voltage level to be applied to the data lines when the card is not in use.

Figure 24. Bidirectional Translator Functional Block

#### **SECURITY FEATURES**

The MC33560 has a number of unique security functions to guarantee that no electrical damage will be caused to the smartcard:

- Battery supply minimum voltage threshold

- Card supply undervoltage and overcurrent detection with automatic shutdown

- Card pin overvoltage clamp to CRDV<sub>CC</sub>

- Card presence detector for "clean" and fast shutdown

- Consistent card signal sequencing at startup and powerdown, according to ISO7816, even on error conditions

- Consistent clock signal, even when division ratio or synchronization clock signal are changed "on the fly" during a card session (Figure 29)

- Active pulldown on all card pins, including CRDV<sub>CC</sub>, when not in normal operating mode.

A current limiting function and an overtemperature detector are limiting power dissipation.

#### **ESD PROTECTION**

Due to the nature of smartcards, the card interface pins must absorb high Electro Static Discharge (ESD) energy during card insertion. In addition, the control circuits attached to these pins must safely withstand short circuits and voltage transients during forced card extraction.

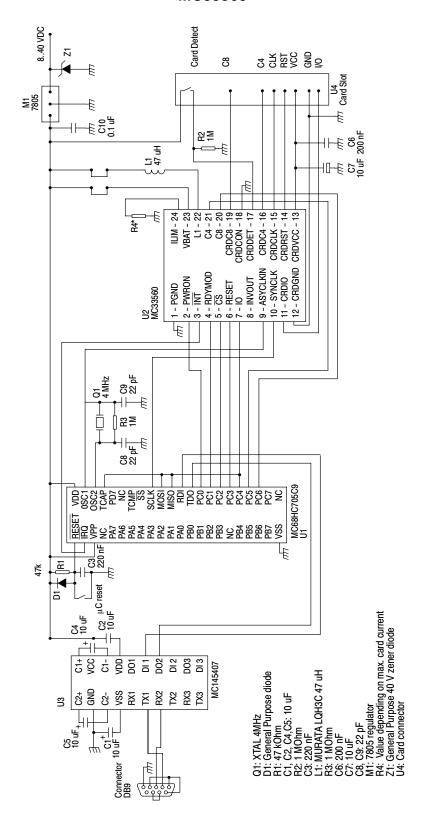

Therefore, the MC33560 features enhanced ESD protection, current limitation and short circuit protection on all smartcard interface pins, including **C4** and **C8**.