## **ISP1302**

# Universal Serial Bus On-The-Go transceiver with carkit support

Rev. 01 — 24 May 2007

**Product data sheet**

## 1. General description

The ISP1302 is a Universal Serial Bus (USB) On-The-Go (OTG) transceiver device that supports *USB Carkit Specification (CEA-936-A), November 2005.* It is fully compliant with *Universal Serial Bus Specification Rev. 2.0* and *On-The-Go Supplement to the USB Specification Rev. 1.2.* The ISP1302 can transmit and receive serial data at full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) data rates.

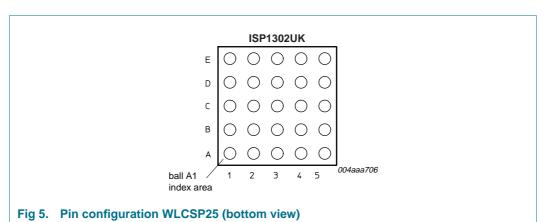

The ISP1302 is available in HVQFN24 and WLCSP25 packages.

## 2. Features

- Fully complies with:

- Universal Serial Bus Specification Rev. 2.0

- On-The-Go Supplement to the USB Specification Rev. 1.2

- ◆ On-The-Go Transceiver Specification (CEA-2011)

- ◆ USB Carkit Specification (CEA-936-A), November 2005

- Can transmit and receive serial data at full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) data rates

- Supports OTG Host Negotiation Protocol (HNP) and Session Request Protocol (SRP)

- Supports I<sup>2</sup>C-bus (up to 400 kHz) serial interface to access control and status registers

- Supports Universal Asynchronous Receiver-Transmitter (UART) pass-through on the DP and DM lines

- Supports service mode with 2.8 V UART signaling on the DP and DM lines

- Built-in analog switches to support analog audio signals multiplexed on the DP and DM lines

- Built-in DC biasing for audio signals on the DP and DM lines

- Supports both 4-wire and 5-wire signaling protocol for carkit application

- Supports data-during-audio mode for smart carkit application

- Built-in charge pump regulator outputs 5 V at current up to 50 mA

- 3.0 V to 4.5 V power supply input range (V<sub>CC</sub>)

- Supports wide range digital interfacing I/O voltage (V<sub>CC(I/O)</sub>) 1.4 V to 3.6 V

- Full industrial grade operation from -40 °C to +85 °C

- Available in small HVQFN24 and WLCSP25 halogen-free and lead-free packages

## **USB OTG transceiver with carkit support**

## 3. Applications

- Mobile phones

- Digital camera

- Personal digital assistant

## 4. Ordering information

## Table 1. Ordering information

| Type number | Package |                                                                                                            |           |  |  |  |  |  |

|-------------|---------|------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|             | Name    | Description                                                                                                | Version   |  |  |  |  |  |

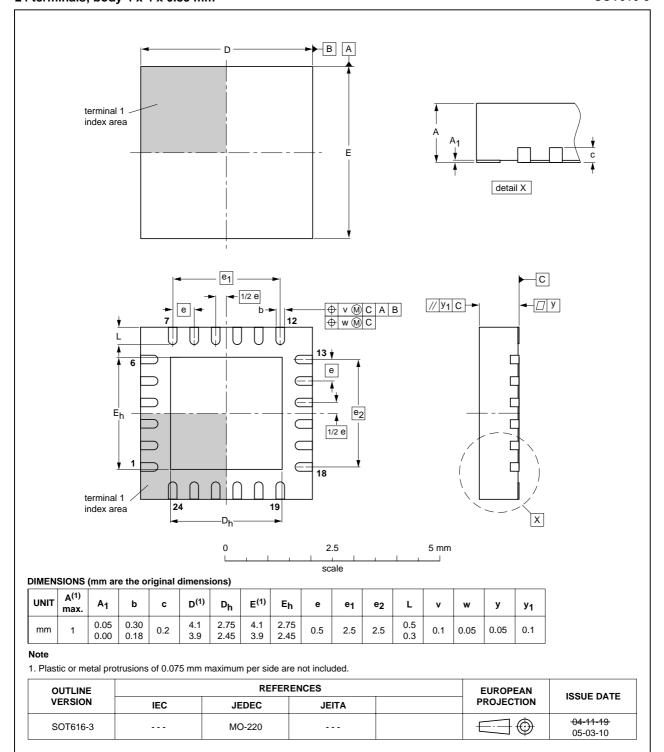

| ISP1302HN   | HVQFN24 | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body $4\times4\times0.85$ mm | SOT616-3  |  |  |  |  |  |

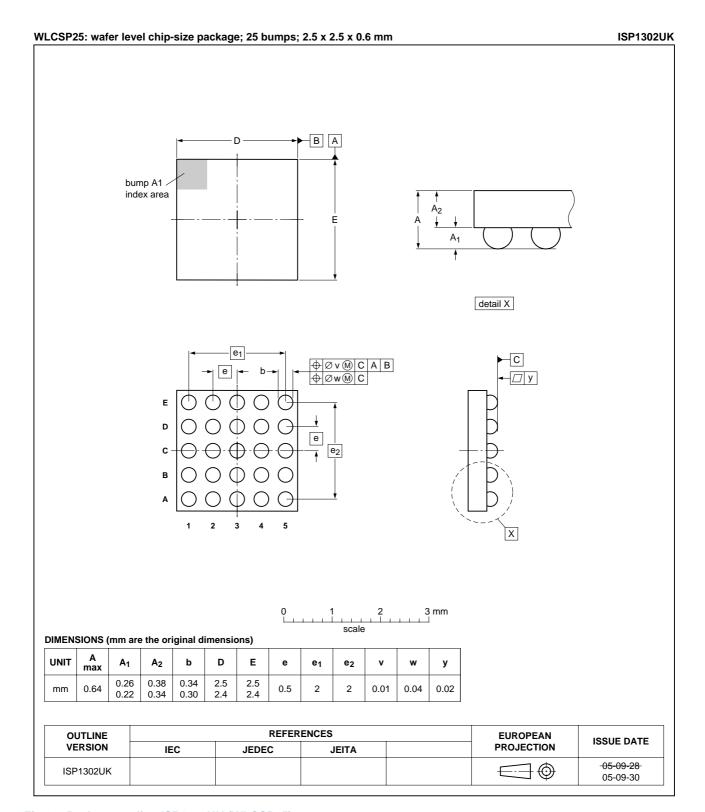

| ISP1302UK   | WLCSP25 | wafer level chip-size package; 25 bumps; $2.5 \times 2.5 \times 0.6$ mm                                    | ISP1302UK |  |  |  |  |  |

SP1302\_1 © NXP B.V. 2007. All rights reserved.

## **USB OTG transceiver with carkit support**

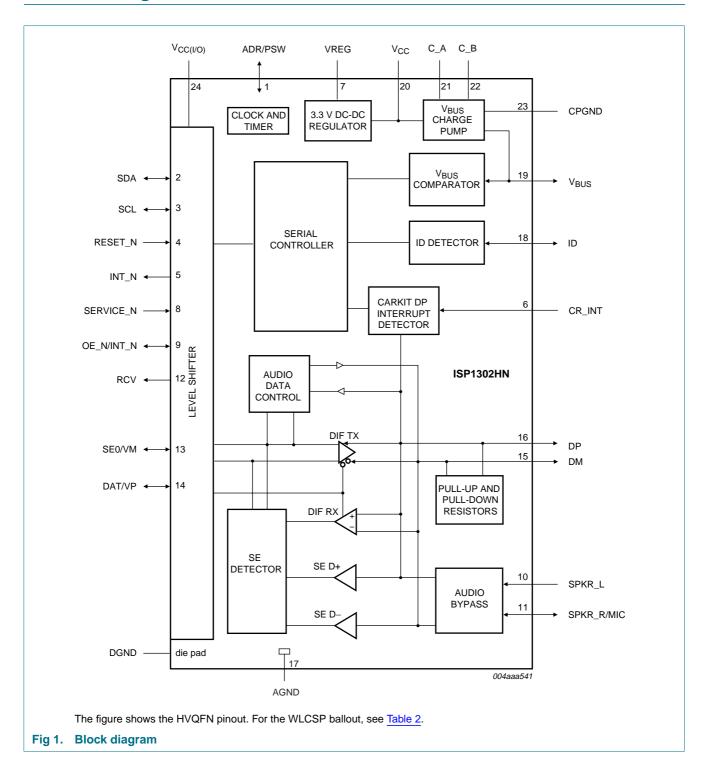

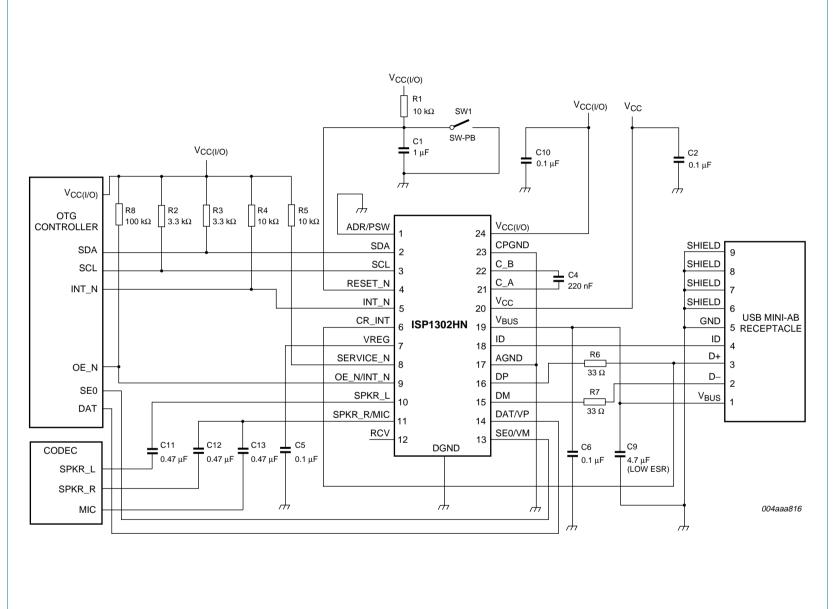

## 5. Block diagram

**USB OTG transceiver with carkit support**

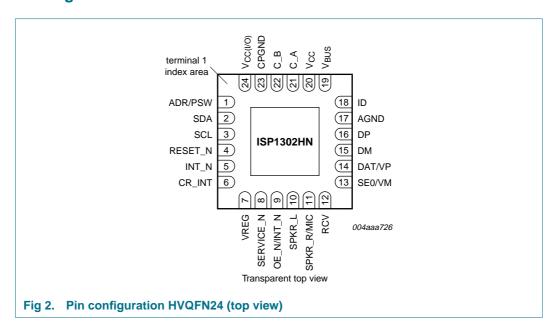

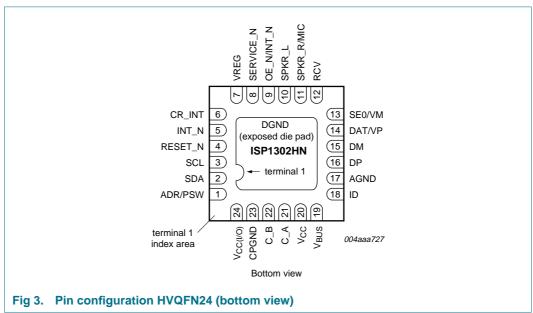

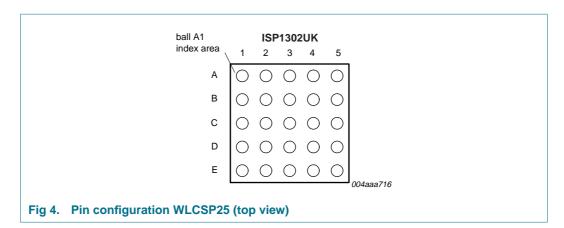

## 6. Pinning information

## 6.1 Pinning

## **USB OTG transceiver with carkit support**

## 6.2 Pin description

Table 2. Pin description

| Symbol <sup>[1]</sup> | Pin<br>HVQFN24 | Ball<br>WLCSP25 | Type <sup>[2]</sup> | Reset value | Description                                                                                                                                                 |

|-----------------------|----------------|-----------------|---------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR/PSW               | 1              | C1              | I/O                 | high-Z      | <b>ADR input</b> — Sets the least-significant I <sup>2</sup> C-bus address bit of the ISP1302; latched on the rising edge of the RESET_N pin                |

|                       |                |                 |                     |             | <b>PSW output</b> — Enables or disables the external charge pump after reset                                                                                |

|                       |                |                 |                     |             | An internal series resistor is implemented for this pin. If the PSW (output) function is not used, then this pin can directly be connected to DGND or VREG. |

|                       |                |                 |                     |             | This pin will output 3.3 V when driven HIGH.                                                                                                                |

|                       |                |                 |                     |             | For details, see Section 7.13.                                                                                                                              |

|                       |                |                 |                     |             | bidirectional; push-pull input; 3-state output                                                                                                              |

| SDA                   | 2              | D2              | I/OD                | high-Z      | serial I <sup>2</sup> C-bus data input and output                                                                                                           |

|                       |                |                 |                     |             | bidirectional; push-pull input; open-drain output                                                                                                           |

| SCL                   | 3              | D3              | I/OD                | high-Z      | serial I <sup>2</sup> C-bus clock input and output                                                                                                          |

|                       |                |                 |                     |             | bidirectional; push-pull input; open-drain output                                                                                                           |

| RESET_N               | 4              | C2              | I                   | -           | asynchronous reset input, active LOW                                                                                                                        |

| INT_N                 | 5              | B1              | OD                  | high-Z      | interrupt output; active LOW                                                                                                                                |

|                       |                |                 |                     |             | open-drain output                                                                                                                                           |

| ISP1302_1             |                |                 |                     |             | © NXP B.V. 2007. All rights reserved.                                                                                                                       |

## **USB OTG transceiver with carkit support**

Table 2.

Pin description ...continued

| Symbol <sup>[1]</sup> | Pin<br>HVQFN24 | Ball<br>WLCSP25 | Type <sup>[2]</sup> | Reset value | Description                                                                                                                                                                         |

|-----------------------|----------------|-----------------|---------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR_INT                | 6              | C4              | Al                  | -           | directly connect to the DP pin of the USB connector; if the carkit feature is not used, this pin can be connected to ground                                                         |

| VREG                  | 7              | A2              | Р                   | -           | output of the voltage regulator; place a 0.1 $\mu\text{F}$ capacitor between this pin and ground                                                                                    |

| SERVICE_N             | 8              | A1              | I                   | -           | <ul> <li>input; sets default operation mode of the ISP1302:</li> <li>If a LOW is latched on reset (including power-on reset), default mode is UART with 2.8 V signaling.</li> </ul> |

|                       |                |                 |                     |             | <ul> <li>If a HIGH is latched on reset (including power-on reset),<br/>default mode is USB with 3.3 V signaling.</li> </ul>                                                         |

|                       |                |                 |                     |             | Operation mode can be changed after reset by changing the value of the Mode register bits.                                                                                          |

| OE_N/INT_N            | 9              | B3              | I/O                 | high-Z      | this pin can be programmed as:                                                                                                                                                      |

|                       |                |                 |                     |             | <b>OE_N input</b> — Enables driving DP and DM when in USB mode                                                                                                                      |

|                       |                |                 |                     |             | <pre>INT_N output — Indicates interrupt when bit OE_INT_EN = 1 and SUSPEND_REG = 1</pre>                                                                                            |

|                       |                |                 |                     |             | bidirectional; push-pull input; 3-state output                                                                                                                                      |

| SPKR_L                | 10             | A3              | Al                  | -           | analog audio input signal for the left speaker channel; connect to ground if not in use                                                                                             |

| SPKR_R/MIC            | 11             | A4              | AI/O                | -           | analog audio input signal for the right speaker channel or audio output signal for the microphone channel; connect to ground if not in use                                          |

| RCV                   | 12             | A5              | 0                   | 0           | differential receiver output; reflects the differential value of DP and DM                                                                                                          |

|                       |                |                 |                     |             | push-pull output                                                                                                                                                                    |

| SE0/VM                | 13             | B4              | I/O                 | high-Z      | <b>SE0 input and output</b> — SE0 functions in DAT_SE0 USB mode                                                                                                                     |

|                       |                |                 |                     |             | <b>VM</b> input and output — VM functions in VP_VM USB mode                                                                                                                         |

|                       |                |                 |                     |             | TxD input — UART mode                                                                                                                                                               |

|                       |                |                 |                     |             | bidirectional; push-pull input; 3-state output                                                                                                                                      |

| DAT/VP                | 14             | B5              | I/O                 | high-Z      | <b>DAT input and output</b> — DAT functions in DAT_SE0 USB mode                                                                                                                     |

|                       |                |                 |                     |             | VP input and output — VP functions in VP_VM USB mode RxD output — UART mode                                                                                                         |

|                       |                |                 |                     |             | bidirectional; push-pull input; 3-state output                                                                                                                                      |

| DM                    | 15             | D5              | AI/O                | high-Z      | this pin can be programmed as:                                                                                                                                                      |

|                       |                |                 |                     |             | <ul> <li>USB D– (data minus pin)</li> </ul>                                                                                                                                         |

|                       |                |                 |                     |             | <ul> <li>transparent UART TxD or</li> </ul>                                                                                                                                         |

|                       |                |                 |                     |             | <ul> <li>transparent audio SPKR_L</li> </ul>                                                                                                                                        |

| DP                    | 16             | D4              | AI/O                | high-Z      | this pin can be programmed as:                                                                                                                                                      |

|                       |                |                 |                     |             | <ul> <li>USB D+ (data plus pin)</li> </ul>                                                                                                                                          |

|                       |                |                 |                     |             | <ul> <li>transparent UART RxD or</li> </ul>                                                                                                                                         |

|                       |                |                 |                     |             | <ul> <li>transparent audio SPKR_R/MIC</li> </ul>                                                                                                                                    |

| AGND                  | 17             | C3              | Р                   | -           | analog ground                                                                                                                                                                       |

## **USB OTG transceiver with carkit support**

Table 2.

Pin description ...continued

| Symbol[1]            | Pin<br>HVQFN24     | Ball<br>WLCSP25 | Type <sup>[2]</sup> | Reset value | Description                                                                                                                                       |

|----------------------|--------------------|-----------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ID                   | 18                 | C5              | AI/O                | -           | identification detector input and output; connected to the ID pin of the USB mini receptacle; internal 100 k $\Omega$ pull-up resistor            |

| V <sub>BUS</sub>     | 19                 | E5              | AI/O                | high-Z      | $V_{BUS}$ line input and output of the USB interface; charge pump output; place an external decoupling capacitor of 0.1 $\mu F$ close to this pin |

| V <sub>CC</sub>      | 20                 | E4              | Р                   | -           | supply voltage (3.0 V to 4.5 V)                                                                                                                   |

| C_A                  | 21                 | E3              | AI/O                | -           | charge pump flying capacitor pin 2; connect a 220 nF capacitor between C_B and C_A for 50 mA output current                                       |

| C_B                  | 22                 | E2              | AI/O                | -           | charge pump flying capacitor pin 1; connect a 220 nF capacitor between C_B and C_A for 50 mA output current                                       |

| CPGND                | 23                 | E1              | Р                   | -           | ground for the charge pump                                                                                                                        |

| V <sub>CC(I/O)</sub> | 24                 | D1              | Р                   | -           | supply voltage for the I/O interface logic signals (1.4 V to 3.6 V)                                                                               |

| DGND                 | exposed<br>die pad | B2              | Р                   | -           | digital ground                                                                                                                                    |

<sup>[1]</sup> Symbol names ending with underscore N (for example, NAME\_N) indicate active LOW signals.

<sup>[2]</sup> AI = analog input; AI/O = analog input/output; I = input; O = output; I/O = digital input/output; I/OD = input/open-drain output; OD = open-drain output; P = power or ground.

#### **USB OTG transceiver with carkit support**

## 7. Functional description

#### 7.1 Serial controller

The serial controller includes the following functions:

- Serial controller interface

- · Device identification registers

- · Control registers

- Interrupt registers

- Interrupt generator

The serial controller acts as an I<sup>2</sup>C-bus slave, and uses the SCL and SDA pins to communicate with the OTG Controller.

For details on the serial controller, see Section 9.

## 7.2 V<sub>BUS</sub> charge pump

The charge pump supplies current to the  $V_{BUS}$  line. It can operate in any of the following modes:

- Output 5 V at current above 50 mA

- Pull-up V<sub>BUS</sub> to 3.3 V through a resistor (R<sub>UP(VBUS)</sub>) to initiate V<sub>BUS</sub> pulsing SRP

- Pull-down V<sub>BUS</sub> to ground through a resistor (R<sub>DN(VBUS)</sub>) to discharge V<sub>BUS</sub>

#### 7.3 V<sub>BUS</sub> comparators

V<sub>BUS</sub> comparators provide indications regarding the voltage level on V<sub>BUS</sub>.

#### 7.3.1 V<sub>BUS</sub> valid comparator

This comparator is used by an A-device to determine whether the voltage on  $V_{BUS}$  is at a valid level for operation. The minimum threshold for the  $V_{BUS}$  valid comparator is 4.4 V. Any voltage on  $V_{BUS}$  below this threshold is considered a fault. A hardware debounce timer ( $t_{d(VA\_VBUS\_VLD)}$ ) is implemented for the  $V_{BUS}$  valid comparator. This timer is enabled when the internal charge pump is turned on (bit  $VBUS\_DRV = 1$ ) and is disabled when the internal charge pump is turned off (bit  $VBUS\_DRV = 0$ ). During power-up, it is expected that the comparator output will be ignored.

#### 7.3.2 Session valid comparator

The session valid comparator is used to determines when  $V_{BUS}$  is high enough for a session to start. Both the A-device and the B-device use this comparator to detect when a session is started. These devices also use this comparator to indicate when a session is completed. The session valid threshold is between 0.8 V to 2.0 V for A-device, and between 0.8 V to 4.0 V for B-device.

#### 7.3.3 Session end comparator

The session end comparator determines when  $V_{BUS}$  is below the B-device session end threshold of 0.2 V to 0.8 V.

#### **USB OTG transceiver with carkit support**

#### 7.4 ID detector

In normal power mode (when both  $V_{CC}$  and  $V_{CC(I/O)}$  are present), the ID detector senses the condition of the ID line and can differentiate between the following conditions:

- The ID pin is floating (bit ID FLOAT = 1).

- The ID pin is shorted to ground (bit ID\_GND = 1).

- The ID pin is connected to ground through resistor  $R_{DN(ID)}$  = 102 k $\Omega$  (bit ID\_102K = 1).

- The ID pin is connected to ground through resistor  $R_{DN(ID)} = 200 \text{ k}\Omega$  (bit ID 200K = 1).

- The ID pin is connected to ground through resistor  $R_{DN(ID)} = 440 \text{ k}\Omega$  (bit ID\_440K = 1).

In power-down mode, only ID\_FLOAT detector is active and can wake-up the chip. The remaining detectors are turned off.

<u>Table 3</u> shows the type of device connected, depending on the status of the ID and  $V_{BUS}$  pins.

Table 3. ID pin status for various applications

| SESS_VLD | ID_FLOAT | ID_GND | ID_102K | ID_200K | ID_440K | Device connected  |

|----------|----------|--------|---------|---------|---------|-------------------|

| 0        | 1        | 0      | 0       | Χ       | Χ       | nothing connected |

| 0        | 0        | 1      | 0       | 0       | 0       | OTG A-device      |

| 0        | 0        | 0      | 1       | 0       | 0       | phone accessory   |

| 1        | 0        | 0      | 0       | 1       | 0       | charger type 1    |

| 1        | 0        | 0      | 0       | 0       | 1       | charger type 2    |

| 1        | 1        | 0      | 0       | 0       | 0       | carkit or PC      |

The recommended procedure to detect the ID status using software is:

- 1. When nothing is connected, ID is floating and ID\_FLOAT = 1. The chip can be set in power-down mode.

- 2. Enable the ID\_FLOAT (rising edge and falling edge) and SESS\_VLD (rising edge) interrupts.

- 3. If a plug that causes a change in ID\_FLOAT or SESS\_VLD is inserted, an interrupt occurs. Interrupt Latch register bit ID\_FLOAT or SESS\_VLD is set.

- 4. The software waits for sometime, for example: 100 ms, to allow mechanical debounce.

- 5. The software reads the Interrupt Source register and the OTG Status register, and checks bits SESS\_VLD, ID\_GND, ID\_102K, ID\_200K and ID\_440K.

- 6. The device type is determined according to <a>Table 3</a>.

The ID detector has a switch that can be used to ground pin ID. This switch is controlled by bit ID\_PULLDN of the OTG Control register, and bits PH\_ID\_INT and PH\_ID\_ACK of the Audio Control register. See Table 4.

#### **USB OTG transceiver with carkit support**

Table 4. ID pull-down control

| ID_PULLDN | PH_ID_ACK | PH_ID_INT | Switch between ID and ground                                                                                           |

|-----------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------|

| 0         | 0         | 0         | off                                                                                                                    |

| 0         | 0         | 1         | on for time $t_{PH\_ID\_INT}$ , then off and bit PH_ID_INT autoclears to 0                                             |

| 0         | 1         | 0         | wait for time $t_{PH\_ID\_WT}$ , turn on the switch for $t_{PH\_ID\_INT}$ , then off and bit PH_ID_ACK autoclears to 0 |

| 0         | 1         | 1         | not defined                                                                                                            |

| 1         | Χ         | Χ         | on                                                                                                                     |

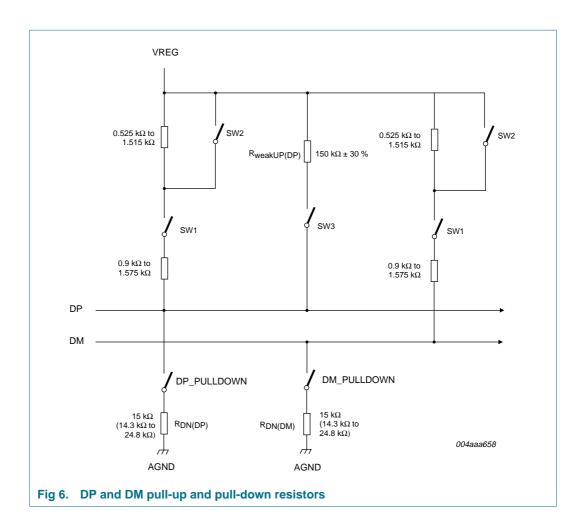

## 7.5 Pull-up and pull-down resistors

<u>Figure 6</u> shows the switchable pull-up and pull-down resistors that are internally connected to the DP and DM lines. The DP pull-up resistor (SW1) is controlled by bit DP\_PULLUP of the OTG Control register.

The pull-up resistor is context variable as described in document *ECN\_27%\_Resistor*. The pull-up resistor value depends on the USB bus condition:

- When the bus is idle, the resistor is 900  $\Omega$  to 1575  $\Omega$  (SW2 = on).

- When the bus is transmitting or receiving, the resistor is 1425  $\Omega$  to 3090  $\Omega$  (SW2 = off).

DP also implements a weak pull-up resistor ( $R_{weakUP(DP)}$ ) that is controlled using bit DP\_WKPU\_EN of the Misc Control register.

The DP pull-down resistor ( $R_{DN(DP)}$ ) is connected to the DP line, if bit DP\_PULLDOWN in the OTG Control register is set.

The DM pull-down resistor ( $R_{DN(DM)}$ ) is connected to the DM line, if bit DM\_PULLDOWN in the OTG Control register is set.

#### **USB OTG transceiver with carkit support**

### 7.6 3.3 V DC-DC regulator

The built-in DC-DC regulator conditions the input power supply (V<sub>CC</sub>) for use in the core of the ISP1302.

When  $V_{CC}$  is greater than 3.6 V, the regulator will output 3.3 V  $\pm$  10 %.

When  $V_{CC}$  is less than 3.6 V and bit REG\_BYPASS\_DIS = 0, the regulator will be automatically bypassed so that pin VREG will be shorted to pin  $V_{CC}$ .

When  $V_{CC}$  is less than 3.6 V and bit REG\_BYPASS\_DIS = 1, the regulator will output a voltage between  $V_{CC}$  and  $V_{CC}$  – 0.2 V.

The output of the regulator can be monitored on pin VREG. A capacitor (0.1  $\mu$ F) must be connected between pin VREG and ground.

#### 7.7 Carkit DP interrupt detector

The carkit DP interrupt detector is a comparator that detects the carkit interrupt signal on the CR\_INT pin in analog audio mode. Bit DP\_INT will be set if the voltage level on the CR\_INT pin is below the carkit interrupt threshold  $V_{th(DP)L}$  (0.4 V to 0.6 V).

The carkit interrupt detector is enabled in audio mode only (bit AUDIO\_EN = 1).

## **USB OTG transceiver with carkit support**

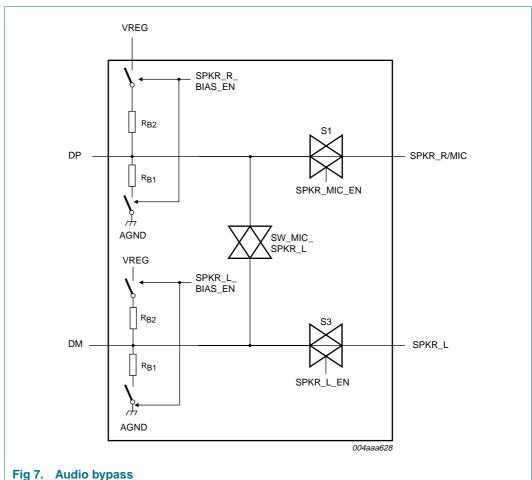

## 7.8 Audio bypass

The audio bypass block includes audio switches and DC bias circuits, see Figure 7.

Audio switches provide a low impedance path for analog audio signals from the phone processor to be routed to the DP and DM lines. The impedance of the switches will be between 50  $\Omega$  and 150  $\Omega$ . Figure 7 shows audio switches and DC biasing circuits.

#### J.

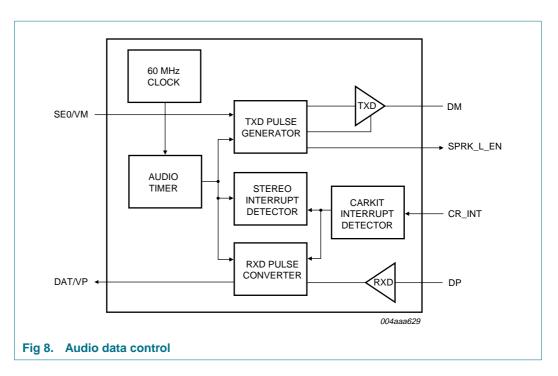

## 7.9 Audio data control

<u>Figure 8</u> shows a diagram that includes the audio data controller. Each block within the audio data controller is described in the following subsections.

#### **USB OTG transceiver with carkit support**

#### 7.9.1 Audio timer

The audio timer has two main functions. The first function is to generate the timing for the positive and negative interrupt pulses. The second function is to generate a time base that can be used to detect a carkit interrupt while in stereo mode, and reset the RxD NRZ signal during data-during-audio.

#### 7.9.2 TxD pulse generator

The TxD pulse generator is enabled when the OTG carkit transceiver is outputting data-during-audio.

When a rising or falling edge is detected on SE0/VM, the TxD pulse generator uses the AUD\_TMR\_OUT signal to perform the following sequence:

- 1. 3-state the left speaker buffer.

- 2. Enable the TxD buffer.

- 3. Output a HIGH level for the duration of the positive pulse width.

- 4. Output a LOW level for the duration of the negative pulse width.

- 5. Disable the TxD buffer.

- 6. Enable the left speaker buffer.

The delay between a data edge on SE0/VM and a pulse pair being output on DM will jitter by as much as one audio timer period because the audio timer is free running. This is acceptable because the audio timer period is between 200 ns to 500 ns, and the UART data rate is always less than or equal to 115 kbit/s.

#### **USB OTG transceiver with carkit support**

#### 7.9.3 Stereo interrupt detector

The stereo interrupt detector generates an interrupt when the CR\_INT pin has been continuously below the carkit interrupt detector threshold for a time of t<sub>PH\_STLO\_DET</sub> (30 ms to 100 ms); refer to *USB Carkit Specification (CEA-936-A), November 2005.*

#### 7.9.4 RxD pulse converter

When data-during-audio mode is enabled, the RxD pulse converter converts the negative pulses on the DP line to an NRZ signal that is output to the DAT/VP line. Each time a pulse is received, the output on DAT/VP is inverted. If DAT/VP remains at logic 0 for a time of t<sub>DAT\_AUD\_POL</sub> (20 ms to 30 ms), then the output on DAT/VP will automatically return to logic 1; refer to *USB Carkit Specification (CEA-936-A)*, *November 2005*.

#### 7.10 Autoconnect

The HNP in the OTG supplement specifies the following sequence of events to transfer the role of the host from the A-device to the B-device:

- 1. The A-device sets the bus in the suspend state.

- 2. The B-device simulates a disconnect by de-asserting its DP pull-up.

- 3. The A-device detects SE0 on the bus and asserts its DP pull-up.

- 4. The B-device detects that the DP line is HIGH and assumes the role of the host.

The OTG supplement specifies that the time between the B-device de-asserting its DP pull-up and the A-device asserting its pull-up must be less than 3 ms. For an A-device with a slow interrupt response time, 3 ms may not be enough to write an I<sup>2</sup>C-bus command to the ISP1302 to assert DP pull-up. An alternative method is for the A-device transceiver to automatically assert DP pull-up after detecting an SE0 from the B-device.

The sequence of events is as follows: After finishing data transfers between the A-device and the B-device and before suspending the bus, the A-device sends SOFs. The B-device receives these SOFs, and does not transmit any packet back to the A-device. During this time, the A-device sets the BDIS\_ACON\_EN bit in the ISP1302. This enables the ISP1302 to look for SE0 whenever the A-device is not transmitting (that is, whenever the OE\_N/INT\_N pin of the ISP1302 is not asserted). After the BDIS\_ACON\_EN bit is set, the A-device stops transmitting SOFs and allows the bus to go to the idle state. If the B-device disconnects, the bus goes to SE0, and the ISP1302 logic automatically turns on the A-device pull-up. To disable the DP pull-up resistor, clear bit BDIS\_ACON\_EN.

#### 7.11 USB transceiver

#### 7.11.1 Differential driver

The operation of the driver is described in Table 5.

## **USB OTG transceiver with carkit support**

© NXP B.V. 2007. All rights reserved.

Table 5. Transceiver driver operating setting

| Pin        |            | Bit     |         | Differential driver                                                                           |  |

|------------|------------|---------|---------|-----------------------------------------------------------------------------------------------|--|

| RESET_N[1] | OE_N/INT_N | SUSPEND | DAT_SE0 |                                                                                               |  |

| HIGH       | LOW        | 0       | 0       | output value from DAT/VP to DP and SE0/VM to DM                                               |  |

| HIGH       | LOW        | 0       | 1       | output value from DAT/VP to DP and DM if SE0/VM is LOW; otherwise drive both DP and DM to LOW |  |

| HIGH       | LOW        | 1       | Χ       | output value from DAT/VP to DP and DM                                                         |  |

| HIGH       | HIGH       | Χ       | Χ       | high-Z                                                                                        |  |

| LOW        | X          | Χ       | Χ       | high-Z                                                                                        |  |

<sup>[1]</sup> Include the internal power-on-reset pulse (active HIGH).

Table 6 shows the behavior of the transmit operation in detail.

Table 6. USB functional mode: transmit operation

| USB mode | Inputs |        | Outputs |      |  |

|----------|--------|--------|---------|------|--|

|          | DAT/VP | SE0/VM | DP      | DM   |  |

| DAT_SE0  | LOW    | LOW    | LOW     | HIGH |  |

| DAT_SE0  | HIGH   | LOW    | HIGH    | LOW  |  |

| DAT_SE0  | LOW    | HIGH   | LOW     | LOW  |  |

| DAT_SE0  | HIGH   | HIGH   | LOW     | LOW  |  |

| VP_VM    | LOW    | LOW    | LOW     | LOW  |  |

| VP_VM    | HIGH   | LOW    | HIGH    | LOW  |  |

| VP_VM    | LOW    | HIGH   | LOW     | HIGH |  |

| VP_VM    | HIGH   | HIGH   | HIGH    | HIGH |  |

#### 7.11.2 Differential receiver

The operation of the differential receiver is described in <a href="Table 7">Table 7</a>.

Table 7. Differential receiver operation settings

| Pin        | Bit     |         | Differential receiver                                      |

|------------|---------|---------|------------------------------------------------------------|

| OE_N/INT_N | SUSPEND | DAT_SE0 |                                                            |

| HIGH       | 0       | 1       | output differential value from DP and DM to DAT/VP and RCV |

| HIGH       | 0       | 0       | output differential value from DP and DM to RCV            |

The detailed behavior of the receive transceiver operation is shown in Table 8.

Table 8. USB functional mode: receive operation

| USB mode | Bit SUSPEND | Inputs |      | Outputs |        |                   |

|----------|-------------|--------|------|---------|--------|-------------------|

|          |             | DP     | DM   | DAT/VP  | SE0/VM | RCV               |

| DAT_SE0  | 0           | LOW    | LOW  | RCV     | HIGH   | last value of RCV |

| DAT_SE0  | 0           | HIGH   | LOW  | HIGH    | LOW    | HIGH              |

| DAT_SE0  | 0           | LOW    | HIGH | LOW     | LOW    | LOW               |

| DAT_SE0  | 0           | HIGH   | HIGH | RCV     | LOW    | last value of RCV |

| DAT_SE0  | 1           | LOW    | LOW  | LOW     | HIGH   | X                 |

**NXP Semiconductors**

#### **USB OTG transceiver with carkit support**

| Table 8. | USB. | tunctional | mode | e: receive operationcontinued | 1 |

|----------|------|------------|------|-------------------------------|---|

| USB mode |      | Rit SUSP   | FND  | Innuts                        |   |

| USB mode | Bit SUSPEND | Inputs |      | Outputs | Outputs |                   |  |

|----------|-------------|--------|------|---------|---------|-------------------|--|

|          |             | DP     | DM   | DAT/VP  | SE0/VM  | RCV               |  |

| DAT_SE0  | 1           | HIGH   | LOW  | HIGH    | LOW     | X                 |  |

| DAT_SE0  | 1           | LOW    | HIGH | LOW     | LOW     | Χ                 |  |

| DAT_SE0  | 1           | HIGH   | HIGH | HIGH    | LOW     | X                 |  |

| VP_VM    | 0           | LOW    | LOW  | LOW     | LOW     | last value of RCV |  |

| VP_VM    | 0           | HIGH   | LOW  | HIGH    | LOW     | HIGH              |  |

| VP_VM    | 0           | LOW    | HIGH | LOW     | HIGH    | LOW               |  |

| VP_VM    | 0           | HIGH   | HIGH | HIGH    | HIGH    | last value of RCV |  |

| VP_VM    | 1           | LOW    | LOW  | LOW     | LOW     | X                 |  |

| VP_VM    | 1           | HIGH   | LOW  | HIGH    | LOW     | X                 |  |

| VP_VM    | 1           | LOW    | HIGH | LOW     | HIGH    | Χ                 |  |

| VP_VM    | 1           | HIGH   | HIGH | HIGH    | HIGH    | X                 |  |

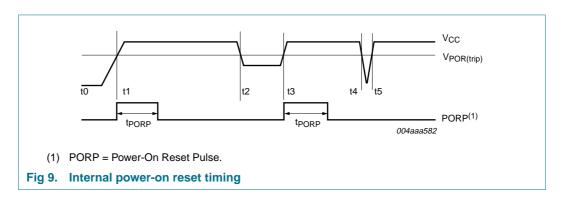

## 7.12 Power-On Reset (POR)

When V<sub>CC</sub> is powered on, an internal POR is generated. The internal POR pulse width (t<sub>PORP</sub>) will typically be 200 ns. The pulse is started when V<sub>CC</sub> rises above V<sub>POR(trip)</sub>.

The power-on reset function can be explained by viewing the dips at t2 to t3 and t4 to t5 on the V<sub>CC</sub> curve (see Figure 9).

t0 — The internal POR starts with a LOW level.

t1 — The detector will see the passing of the trip level and a delay element will add another t<sub>PORP</sub> before it drops to LOW.

t2 to t3 — The internal POR pulse will be generated whenever V<sub>CC</sub> drops below V<sub>POR(trip)</sub> for more than 11  $\mu$ s.

t4 to t5 — The dip is too short (< 11 µs) and the internal POR pulse will not react and will remain LOW.

## 7.13 I<sup>2</sup>C-bus device address and external charge pump control

The ADR/PSW pin has two functions. Both functions are described as follows.

© NXP B.V. 2007. All rights reserved.

#### **USB OTG transceiver with carkit support**

The first function of the ADR/PSW pin is to set the  $I^2C$ -bus address. On the rising edge of the RESET\_N pin, the level on ADR/PSW is latched and stored in ADR\_REG, which represents the Least Significant Bit (LSB) of the  $I^2C$ -bus address. If ADR\_REG = 0, the  $I^2C$ -bus address for the ISP1302 is 010 1100 (2Ch); if ADR\_REG = 1, the  $I^2C$ -bus address for the ISP1302 is 010 1101 (2Dh). The power-on reset value of ADR\_REG = 0.

The second function of the ADR/PSW pin is to control an external charge pump. The ADR/PSW pin can be programmed as an active HIGH or active LOW PSW output. The polarity of the PSW output is determined by ADR\_REG. If ADR\_REG = 0, then PSW will be active HIGH; if ADR\_REG = 1, then PSW will be active LOW. The PSW output will be enabled only when Mode Control 2 register bit PSW\_OE = 1. By default, PSW can only drive HIGH if the hardware reset pulse is not issued on RESET\_N.

The combinations of  $I^2C$ -bus address and the PSW polarity are limited, as shown in Table 9.

Table 9. Possible combinations of I<sup>2</sup>C-bus address and the PSW polarity

| ADR/PSW level on the rising edge of RESET_N | I <sup>2</sup> C-bus address | PSW polarity |

|---------------------------------------------|------------------------------|--------------|

| LOW                                         | 2Ch                          | active HIGH  |

| HIGH                                        | 2Dh                          | active LOW   |

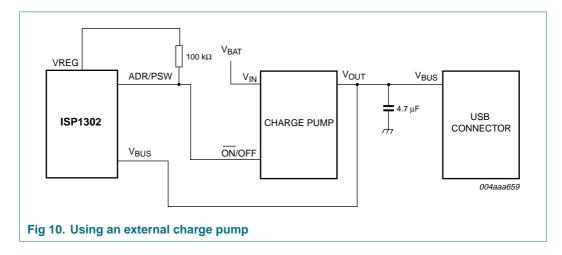

The ISP1302 built-in charge pump supports  $V_{BUS}$  current at 50 mA. If the application needs more current support, an external charge pump may be needed. In this case, the ADR/PSW pin can act as a power switch for the external charge pump. Figure 10 shows an example of using an external charge pump.

#### **USB OTG transceiver with carkit support**

## 8. Modes of operation

The ISP1302 supports three types of modes:

- Power modes

- USB modes

- Transparent modes

#### 8.1 Power modes

#### 8.1.1 Normal mode

In this mode, both  $V_{CC}$  and  $V_{CC(I/O)}$  are connected and their voltage levels are within the operation range.

There are three levels of power saving schemes in the ISP1302:

- Active-power mode: power is on; all circuits are active.

- USB suspend mode: to reduce power consumption, the USB differential receiver is powered down.

- Power-down mode: set by writing logic 1 to bit PWR\_DN of the Mode Control 2 register. The clock generator and all biasing circuits are turned off to reduce power consumption to the minimum possible. For details on waking up the clock, see Section 10.

#### 8.1.2 Disable mode

In disable mode,  $V_{CC(I/O)}$  is cut-off and  $V_{CC}$  is powered. In this mode, the ISP1302 is in the power-down state.

The USB differential driver will be 3-stated as long as V<sub>CC(I/O)</sub> is not present.

#### 8.1.3 Isolate mode

In isolate mode,  $V_{CC}$  is cut-off and  $V_{CC(I/O)}$  is powered. In this mode, the ISP1302 will drive a stable level to all digital output pins, and all bidirectional digital pins will be set in 3-state.

Table 10 shows a summary of power modes.

Table 10. ISP1302 power modes summary

| $v_{cc}$ | V <sub>CC(I/O)</sub> | PWR_DN (bit) | $I_{CC} = I_{CC(pd)}$ | Comment                      |

|----------|----------------------|--------------|-----------------------|------------------------------|

| Off      | off                  | Χ            | yes                   | power off                    |

| Off      | on                   | Χ            | yes                   | isolate mode                 |

| On       | off                  | Χ            | yes                   | disable mode (power-down)    |

| On       | on                   | 0            | no                    | normal mode (full operation) |

| On       | on                   | 1            | yes                   | normal mode (power-down)     |

Table 11 shows the pin states in disable and isolate modes.

SP1302\_1 © NXP B.V. 2007. All rights reserved.

#### **USB OTG transceiver with carkit support**

Table 11. ISP1302 pin states in disable and isolate modes

| Pin name                                                                       | Disable mode (V <sub>CC</sub> = on, V <sub>CC(I/O)</sub> = off) | Isolate mode (V <sub>CC</sub> = off, V <sub>CC(I/O)</sub> = on) |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| V <sub>CC</sub> , VREG                                                         | powered                                                         | not present                                                     |

| V <sub>CC(I/O)</sub>                                                           | not present                                                     | powered                                                         |

| DP                                                                             | 15 k $\Omega$ pull-down resistor enabled                        | high-Z                                                          |

| DM                                                                             | 15 k $\Omega$ pull-down resistor enabled                        | high-Z                                                          |

| RCV                                                                            | high-Z                                                          | drive LOW                                                       |

| RESET_N, SDA, SCL, ADR/PSW,<br>SE0/VM, DAT/VP, INT_N,<br>OE_N/INT_N, SERVICE_N | high-Z                                                          | high-Z                                                          |

| SPKR_R/MIC, SPKR_L, ID, V <sub>BUS</sub> , CR_INT, C_A, C_B                    | high-Z                                                          | high-Z                                                          |

#### 8.2 USB modes

The two USB modes of the ISP1302 are:

- VP VM bidirectional mode

- DAT\_SE0 bidirectional mode

In VP\_VM USB mode, pin DAT/VP is used for the VP function, pin SE0/VM is used for the VM function, and pin RCV is used for the RCV function.

In DAT\_SE0 USB mode, pin DAT/VP is used for the DAT function, pin SE0/VM is used for the SE0 function, and pin RCV is not used.

Table 12 specifies the functionality of the device during the two USB modes.

Table 12. USB functional modes: I/O values

| USB mode[1] | Bit     | Pin        |         |         |        |  |

|-------------|---------|------------|---------|---------|--------|--|

|             | DAT_SE0 | OE_N/INT_N | DAT/VP  | SE0/VM  | RCV    |  |

| VP_VM       | 0       | LOW        | TxD+[2] | TxD-[2] | RxD[6] |  |

|             |         | HIGH       | RxD+[3] | RxD-[3] | RxD[6] |  |

| DAT_SE0     | 1       | LOW        | TxD[4]  | FSE0[5] | RxD[6] |  |

|             |         | HIGH       | RxD[6]  | RSE0[7] | RxD[6] |  |

<sup>[1]</sup> Some of the modes and signals are provided to achieve backward compatibility with IP cores.

<sup>[2]</sup> TxD+ and TxD- are single-ended inputs to drive the DP and DM outputs, respectively, in single-ended mode.

<sup>[3]</sup> RxD+ and RxD- are the outputs of the single-ended receivers connected to DP and DM, respectively.

<sup>[4]</sup> TxD is the input to drive DP and DM in DAT\_SE0 mode.

<sup>[5]</sup> FSE0 is to force an SE0 on the DP and DM lines in DAT\_SE0 mode.

<sup>[6]</sup> RxD is the output of the differential receiver.

<sup>[7]</sup> RSE0 is an output, indicating that an SE0 is received on the DP and DM lines.

#### **USB OTG transceiver with carkit support**

## 8.3 Transparent modes

#### 8.3.1 Transparent UART mode

When in transparent UART mode, an SoC (with the UART controller) communicates through the ISP1302 to another UART device that is connected to its DP and DM lines. The ISP1302 operates as a logic level translator between the following pins:

- For the TxD signal: from SE0/VM (V<sub>CC(I/O)</sub> level) to DM (VREG level).

- For the RxD signal: from DP (VREG level) to DAT/VP (V<sub>CC(I/O)</sub> level).

The ISP1302 is in transparent UART mode, if bit UART\_EN of the Mode Control 1 register is set.

#### 8.3.2 Transparent audio mode

In transparent audio mode, the ISP1302 will disable its DP and DM driver. The carkit interrupt detector is enabled. Built-in analog switches, DC biasing circuits, and the data-during-audio feature can be enabled by setting corresponding bits in the Carkit Control register:

- Stereo mode: SPKR\_L on DM and SPKR\_R on DP.

- Mono and MIC mode: SPKR\_L on DM and MIC on DP.

The ISP1302 is in transparent audio mode if bit UART\_EN of the Mode Control 1 register is cleared, bit AUDIO\_EN of the Mode Control 2 register is set, and bit TRANSP\_EN of the Mode Control 1 register is cleared.

#### 8.3.3 Transparent general-purpose buffer mode

In transparent general-purpose buffer mode, the DAT/VP and SE0/VM pins are connected to the DP and DM pins, respectively. The direction of the data transfer can be controlled using bits TRANSP\_BDIR1 and TRANSP\_BDIR0 of the Mode Control 2 register as specified in Table 14.

The ISP1302 is in transparent general-purpose buffer mode, if bit UART\_EN = 0, bit AUDIO EN = 0, bit DAT SE0 = 1 and bit TRANSP EN = 1.

#### 8.3.4 Data-during-audio mode

This mode is a combination of audio mode and UART mode. The SPKR\_R, SPKR\_L and MIC audio signals will be bypassed through the DP and DM lines. UART data bytes can be transmitted or received on the DP and DM lines when the audio signal is running.

To transmit data, if the SE0/VM input changes level (either from HIGH to LOW or from LOW to HIGH), a HIGH pulse will be generated on the DM line. The pulse voltage is above 2.9 V. The pulse width is between 200 ns and 500 ns. The data-during-audio transmitting is enabled when the ISP1302 is in transparent audio mode and bit  $TX_{PULSE\_EN} = 1$ .

To receive data, if a LOW pulse is detected on the DP line, the ISP1302 will toggle the level on the DAT/VP pin. The data-during-audio receiving is enabled when the ISP1302 is in transparent audio mode and bit RX PULSE EN = 1.

Table 13 provides a summary of device operating modes.

## **USB OTG transceiver with carkit support**

Table 13. Summary of device operating modes

| Mode                                    | Bit     |          |           |         | Description                                                                                                       |  |

|-----------------------------------------|---------|----------|-----------|---------|-------------------------------------------------------------------------------------------------------------------|--|

|                                         | UART_EN | AUDIO_EN | TRANSP_EN | DAT_SE0 |                                                                                                                   |  |

| USB mode                                | 0       | 0        | 0         | X       | USB ATX enabled                                                                                                   |  |

| Transparent general-purpose buffer mode | 0       | 0        | 1         | 1       | USB ATX disabled. $SE0/VM \leftrightarrow DM$ $DAT/VP \leftrightarrow DP$ $see                                  $ |  |

| Transparent audio mode                  | 0       | 1        | 0         | X       | USB ATX disabled. $ SPKR\_L \rightarrow DM \\ SPKR\_R/MIC \leftrightarrow DP $                                    |  |

| Transparent UART mode                   | 1       | X        | X         | X       | USB ATX disabled. $ SE0/VM \rightarrow DM                                 $                                       |  |

Table 14. Transparent general-purpose buffer mode

| Bit TRANSP_BDIR[1:0] | Direction of the data flow |                         |

|----------------------|----------------------------|-------------------------|

| 00                   | $DAT/VP \to DP$            | $SE0/VM \to DM$         |

| 01                   | $DAT/VP \to DP$            | SE0/VM ← DM             |

| 10                   | $DAT/VP \leftarrow DP$     | SE0/VM $\rightarrow$ DM |

| 11                   | $DAT/VP \leftarrow DP$     | SE0/VM ← DM             |

## **USB OTG transceiver with carkit support**

## 9. Serial controller

## 9.1 Register map

Table 15 provides an overview of serial controller registers.

Table 15. Register overview

| Register                  | Width (bits) | Access | Memory address[1] | Functionality               | Reference                |  |  |

|---------------------------|--------------|--------|-------------------|-----------------------------|--------------------------|--|--|

| Vendor ID                 | 16           | R      | 00h to 01h        | device                      | Section 9.1.1 on page 22 |  |  |

| Product ID                | 16           | R      | 02h to 03h        | identification<br>registers |                          |  |  |

| Version ID                | 16           | R      | 14h to 15h        | - registers                 |                          |  |  |

| Mode Control 1            | 8            | R/S/C  | <b>Set</b> — 04h  | control and                 | Section 9.1.2 on page 23 |  |  |

|                           |              |        | Clear — 05h       | status registers            |                          |  |  |

| Mode Control 2            | 8            | R/S/C  | <b>Set</b> — 12h  |                             |                          |  |  |

|                           |              |        | Clear — 13h       |                             |                          |  |  |

| Audio Control             | 8            | R/S/C  | <b>Set</b> — 16h  |                             |                          |  |  |

|                           |              |        | Clear — 17h       |                             |                          |  |  |

| OTG Control               | 8            | R/S/C  | <b>Set</b> — 06h  |                             |                          |  |  |

|                           |              |        | Clear — 07h       |                             |                          |  |  |

| Misc Control              | 8            | R/S/C  | <b>Set</b> — 18h  |                             |                          |  |  |

|                           |              |        | Clear — 19h       |                             |                          |  |  |

| Carkit Control            | 8            | R/S/C  | Set — 1Ah         |                             |                          |  |  |

|                           |              |        | Clear — 1Bh       |                             |                          |  |  |

| Transmit Positive Width   | 8            | R/W    | 1Ch               |                             |                          |  |  |

| Transmit Negative Width   | 8            | R/W    | 1Dh               |                             |                          |  |  |

| Receive Polarity Recovery | 8            | R/W    | 1Eh               |                             |                          |  |  |

| Carkit Interrupt Delay    | 8            | R/W    | 1Fh               |                             |                          |  |  |

| OTG Status                | 8            | R      | 10h               |                             |                          |  |  |

| Interrupt Source          | 8            | R      | 08h               | interrupt                   | Section 9.1.3 on page 29 |  |  |

| Interrupt Latch           | 8            | R/S/C  | Set — 0Ah         | registers                   |                          |  |  |

|                           |              |        | Clear — 0Bh       |                             |                          |  |  |

| Interrupt Enable Low      | 8            | R/S/C  | Set — 0Ch         |                             |                          |  |  |

|                           |              |        | Clear — 0Dh       |                             |                          |  |  |

| Interrupt Enable High     | 8            | R/S/C  | Set — 0Eh         |                             |                          |  |  |

|                           |              |        | Clear — 0Fh       |                             |                          |  |  |

<sup>[1]</sup> The R/W/S/C access type represents a field that can be read, written, set or cleared (set to 0). A register can be read from either of the set or clear addresses. Writing to a write address indicates that values will be directly written to the register. Writing logic 1 to a set address sets the associated bit. Writing logic 1 to a clear address clears the associated bit. Writing logic 0 to either a set or clear address has no effect.

## 9.1.1 Device identification registers

#### 9.1.1.1 Vendor ID register

Table 16 provides the bit description of the Vendor ID register.

ISP1302\_1 © NXP B.V. 2007. All rights reserved.

#### **USB OTG transceiver with carkit support**

Table 16. Vendor ID register (address R = 00h to 01h) bit description

| Bit     | Symbol         | Access | Value | Description                   |

|---------|----------------|--------|-------|-------------------------------|

| 15 to 0 | VENDORID[15:0] | R      | 04CCh | NXP Semiconductors' Vendor ID |

## 9.1.1.2 Product ID register

The bit description of the Product ID register is given in Table 17.

Table 17. Product ID register (address R = 02h to 03h) bit description

| Bit     | Symbol          | Access | Value | Description               |

|---------|-----------------|--------|-------|---------------------------|

| 15 to 0 | PRODUCTID[15:0] | R      | 1302h | Product ID of the ISP1302 |

#### 9.1.1.3 Version ID register

Table 18 shows the bit allocation of the register.

Table 18. Version ID register (address R = 14h to 15h) bit allocation

| Bit         15         14         13         12         11         10         9         8           Symbol         PACKAGEID[3:0]           Reset         X[1]           Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                                                                                                                 |        | •              | •     |          | *  |     |               |          |   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|-------|----------|----|-----|---------------|----------|---|--|--|

| Reset         X[1]           Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R <th>Bit</th> <th>15</th> <th>14</th> <th>13</th> <th>12</th> <th>11</th> <th>10</th> <th>9</th> <th>8</th>  | Bit    | 15             | 14    | 13       | 12 | 11  | 10            | 9        | 8 |  |  |

| Access         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R <th>Symbol</th> <th colspan="4">PACKAGEID[3:0]</th> <th></th> <th colspan="5">LEGACYID[3:0]</th> | Symbol | PACKAGEID[3:0] |       |          |    |     | LEGACYID[3:0] |          |   |  |  |

| Bit         7         6         5         4         3         2         1         0           Symbol         MAJORID[3:0]         MINORID[3:0]         X[1]           Reset         X[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset  |                |       |          | Х  | [1] |               |          |   |  |  |

| Symbol         MAJORID[3:0]         MINORID[3:0]           Reset         X[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Access | R              | R     | R        | R  | R   | R             | R        | R |  |  |

| Reset X <sup>[1]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit    | 7              | 6     | 5        | 4  | 3   | 2             | 1        | 0 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Symbol |                | MAJOF | RID[3:0] |    |     | MINOF         | RID[3:0] |   |  |  |

| Access R R R R R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reset  |                |       |          | Х  | [1] |               |          |   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Access | R              | R     | R        | R  | R   | R             | R        | R |  |  |

<sup>[1]</sup> The reset value depends on the version number of the chip.

Table 19. Version ID register (address R = 14h to 15h) bit description

| Bit      | Symbol         | Description                                                                                                     |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------|

| 15 to 12 | PACKAGEID[3:0] | Package information:                                                                                            |

|          |                | <b>0</b> — HVQFN24                                                                                              |

|          |                | 1 — WLCSP25                                                                                                     |

| 11 to 8  | LEGACYID[3:0]  | Legacy version ID:                                                                                              |

|          |                | 0 — New method of defining the version ID                                                                       |

|          |                | 1 to 15 — Legacy method of defining the version ID                                                              |

| 7 to 4   | MAJORID[3:0]   | Version ID, major number; this number starts with 1 and increments by 1 if there is a major update to the chip. |

| 3 to 0   | MINORID[3:0]   | Version ID, minor number; this number starts with 0 and increments by 1 if there is a minor update to the chip. |

## 9.1.2 Control registers

## 9.1.2.1 Mode Control 1 register

The bit allocation of the Mode Control 1 register is given in Table 20.

## **USB OTG transceiver with carkit support**

Table 20. Mode Control 1 register (address S = 04h, C = 05h) bit allocation

| Bit    | 7        | 6       | 5             | 4                | 3             | 2       | 1       | 0     |

|--------|----------|---------|---------------|------------------|---------------|---------|---------|-------|

| Symbol | reserved | UART_EN | OE_INT_<br>EN | BDIS_<br>ACON_EN | TRANSP_<br>EN | DAT_SE0 | SUSPEND | SPEED |

| Reset  | 0        | 0/1     | 0             | 0                | 0             | 0       | 0       | 0     |

| Access | R/S/C    | R/S/C   | R/S/C         | R/S/C            | R/S/C         | R/S/C   | R/S/C   | R/S/C |

Table 21. Mode Control 1 register (address S = 04h, C = 05h) bit description

| Bit | Symbol     | Description                                                                                                                                                                                                                   |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -          | reserved                                                                                                                                                                                                                      |

| 6   | UART_EN    | When set, the ATX is in transparent UART mode. The default value of this bit depends on the SERVICE_N pin. On reset, if SERVICE_N = HIGH, the reset value of UART_EN = 0; if SERVICE_N = LOW, the reset value of UART_EN = 1. |

| 5   | OE_INT_EN  | When set and when in suspend mode, pin OE_N/INT_N becomes an output and is asserted when an interrupt occurs.                                                                                                                 |

| 4   | BDIS_ACON_ | This bit has two functions:                                                                                                                                                                                                   |

|     | EN         | For an A-device, this bit works as BDIS_ACON_EN. It enables the A-device to connect if the B-device disconnect is detected; see Section 7.10.                                                                                 |

|     |            | 0 — DP pull-up resistor is controlled by the DP_PULLUP bit in the OTG<br>Control register.                                                                                                                                    |

|     |            | 1 — DP pull-up resistor will connect on the B-device disconnect.                                                                                                                                                              |

|     |            | For a B-device, this bit works as ACON_BSE0_EN. It enables the B-device to drive SE0 on DP and DM, if the A-device connect is detected.                                                                                       |

|     |            | <ul><li>0 — B-device will stop driving SE0.</li></ul>                                                                                                                                                                         |

|     |            | 1 — B-device will start to drive SE0, if the A-device connect is detected.                                                                                                                                                    |

| 3   | TRANSP_EN  | When set, the ATX is in transparent general-purpose buffer mode.                                                                                                                                                              |

| 2   | DAT_SE0    | 0 — VP_VM mode                                                                                                                                                                                                                |

|     |            | 1 — DAT_SE0 mode                                                                                                                                                                                                              |

| 1   | SUSPEND    | Sets the transceiver in low-power mode.                                                                                                                                                                                       |

|     |            | <b>0</b> — Active-power mode                                                                                                                                                                                                  |

|     |            | 1 — Low-power mode (differential receiver is disabled if SPEED = 1)                                                                                                                                                           |

| 0   | SPEED      | Set the rise time and the fall time of the transmit driver in USB modes.                                                                                                                                                      |

|     |            | 0 — Low-speed mode                                                                                                                                                                                                            |

|     |            | 1 — Full-speed mode                                                                                                                                                                                                           |

## 9.1.2.2 Mode Control 2 register

For the bit allocation of this register, see Table 22.

Table 22. Mode Control 2 register (address S = 12h, C = 13h) bit allocation

|        |          | • •    |          | *                |                  |       |       |        |

|--------|----------|--------|----------|------------------|------------------|-------|-------|--------|

| Bit    | 7        | 6      | 5        | 4                | 3                | 2     | 1     | 0      |

| Symbol | reserved | PSW_OE | AUDIO_EN | TRANSP_<br>BDIR1 | TRANSP_<br>BDIR0 | rese  | erved | PWR_DN |

| Reset  | 0        | 0      | 0        | 0                | 0                | 1     | 0     | 0      |

| Access | R/S/C    | R/S/C  | R/S/C    | R/S/C            | R/S/C            | R/S/C | R/S/C | R/S/C  |

## **USB OTG transceiver with carkit support**

Table 23. Mode Control 2 register (address S = 12h, C = 13h) bit description

|        |                      | , , , ,                                                                                                               |