# DATA SHEET

# UCB1300 Advanced modem/audio analog front-end

Product specification Supersedes data of 1999 Jul 20 2000 Jun 26

## Advanced modem/audio analog front-end

**UCB1300**

#### **FEATURES**

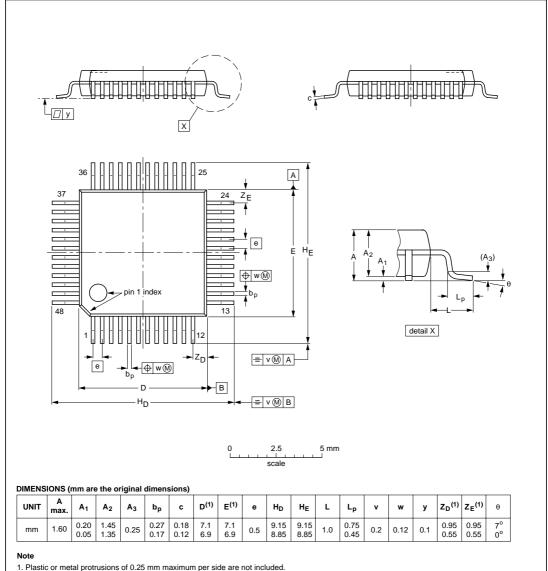

- 48 pin LQFP (SOT313-2) small body SMD package and low external component count results in minimal PCB space requirement

- 12-bit sigma delta audio codec with programmable sample rate, input and output voltage levels, capable of connecting directly to speaker and microphone, including digitally controlled mute, loopback and clip detection functions

- 14-bit sigma delta telecom codec with programmable sample rate, including digitally controlled input voltage level, mute, loopback and clip detection functions. The telecom codec can be directly connected to a Data Access Arrangement (DAA) and includes a built in sidetone suppression circuit

- Complete 4 wire resistive touch screen interface circuit supporting position, pressure and plate resistance measurements

- 10-bit successive approximation ADC with internal track and hold circuit and analog multiplexer for touch screen read-out and monitoring of four external high voltage (7.5V) analog voltages

- · High speed, 4 wire serial interface data bus (SIB) for communication to the system controller

- 3.3V supply voltage and built in power saving modes make the UCB1300 optimal for portable and battery powered

applications

- · Maximum operating current 25 mA

- 10 general purpose IO pins

#### **APPLICATIONS**

- · Handheld Personal Computers, Personal Intelligent Communicators, Personal Digital Assistants

- Smart Mobile Phones

- · Screen/Web Phones

- Internet Access Terminal

- Modems

#### **GENERAL DESCRIPTION**

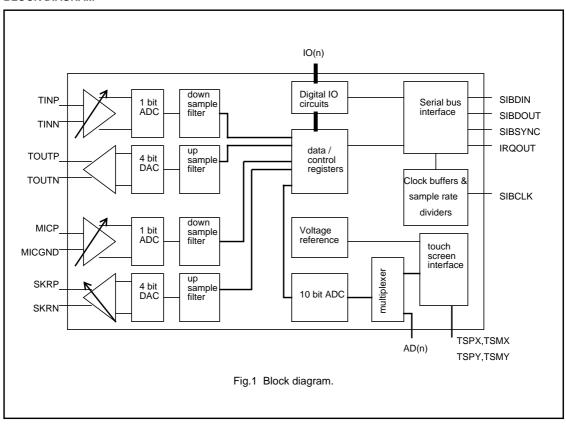

The UCB1300 is a single chip, integrated mixed signal audio and telecom codec. The single channel audio codec is designed for direct connection of a microphone and a speaker. The built-in telecom codec can directly be connected to a DAA and supports high speed modem protocols. The incorporated analog-to-digital converter and the touch screen interface provides complete control and read-out of an 4 wire resistive touch screen. The 10 general purpose I/O pins provide programmable inputs and/or outputs to the system.

The UCB1300 has a serial interface bus (SIB) intended to communicate to the system controller. Both the codec input data and codec output data and the control register data are multiplexed on this SIB interface.

## Advanced modem/audio analog front-end

**UCB1300**

#### ORDERING INFORMATION

| TYPE      |        | PACKAGE                                                              |          |  |  |

|-----------|--------|----------------------------------------------------------------------|----------|--|--|

| NUMBER    | NAME   | DESCRIPTION                                                          | VERSION  |  |  |

| UCB1300BE | LQFP48 | plastic low profile quad flat package; 48 leads; body 7 × 7 × 1.4 mm | SOT313-2 |  |  |

#### **BLOCK DIAGRAM**

## Advanced modem/audio analog front-end

**UCB1300**

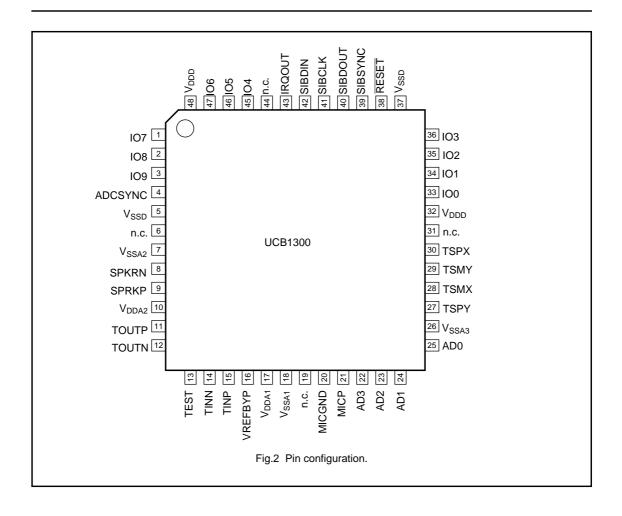

#### **PINNING**

| SYMBOL            | PIN | DESCRIPTION                      | RESET<br>STATE | TYPE <sup>(1)</sup> |

|-------------------|-----|----------------------------------|----------------|---------------------|

| IO7               | 1   | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| IO8               | 2   | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| IO9               | 3   | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| ADCSYNC           | 4   | ADC synchronization pulse input  | -              | I <sub>C</sub>      |

| V <sub>SSD</sub>  | 5   | digital ground                   | -              | S <sup>(2)</sup>    |

| n.c               | 6   | not connected                    | -              | -                   |

| V <sub>SSA2</sub> | 7   | analog speaker driver ground     | -              | S                   |

| SPKRN             | 8   | negative speaker output          | Hi-Z           | O <sub>A</sub>      |

| SPKRP             | 9   | positive speaker output          | Hi-Z           | O <sub>A</sub>      |

| V <sub>DDA2</sub> | 10  | analog speaker driver supply     | -              | S                   |

| TOUTP             | 11  | positive telecom codec output    | Hi-Z           | O <sub>A</sub>      |

| TOUTN             | 12  | negative telecom codec output    | Hi-Z           | O <sub>A</sub>      |

| TEST              | 13  | test mode protection             | '0'            | I <sub>C</sub>      |

| TINN              | 14  | negative telecom codec input     | Hi-Z           | I <sub>A</sub>      |

| TINP              | 15  | positive telecom codec input     | Hi-Z           | I <sub>A</sub>      |

| VREFBYP           | 16  | external reference voltage input | Hi-Z           | I/O <sub>A</sub>    |

| V <sub>DDA1</sub> | 17  | analog supply                    | -              | S                   |

| V <sub>SSA1</sub> | 18  | analog ground                    | -              | S                   |

| n.c               | 19  | not connected                    | -              | -                   |

| MICGND            | 20  | microphone ground switch input   | Hi-Z           | I <sub>A</sub>      |

| MICP              | 21  | microphone signal input          | Hi-Z           | I <sub>A</sub>      |

| AD3               | 22  | analog voltage inputs            | Hi-Z           | I <sub>A</sub>      |

| AD2               | 23  | analog voltage inputs            | Hi-Z           | I <sub>A</sub>      |

| AD1               | 24  | analog voltage inputs            | Hi-Z           | I <sub>A</sub>      |

| AD0               | 25  | analog voltage inputs            | Hi-Z           | I <sub>A</sub>      |

| V <sub>SSA3</sub> | 26  | analog touch screen ground       | -              | S                   |

| TSPY              | 27  | positive Y-plate touch screen    | Hi-Z           | I/O <sub>A</sub>    |

| TSMX              | 28  | negative X-plate touch screen    | Hi-Z           | I/O <sub>A</sub>    |

| TSMY              | 29  | negative Y-plate touch screen    | Hi-Z           | I/O <sub>A</sub>    |

| TSPX              | 30  | positive X-plate touch screen    | Hi-Z           | I/O <sub>A</sub>    |

| n.c               | 31  | not connected                    | -              | -                   |

| $V_{DDD}$         | 32  | digital supply                   | -              | S                   |

| IO0               | 33  | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| IO1               | 34  | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| IO2               | 35  | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| IO3               | 36  | general purpose I/O pins         | input          | I/O <sub>C</sub>    |

| V <sub>SSD</sub>  | 37  | digital ground                   | -              | S                   |

| RESET             | 38  | asynchronous reset input         | -              | I <sub>C</sub>      |

| SIBSYNC           | 39  | SIB synchronization input        | -              | I <sub>C</sub>      |

## Advanced modem/audio analog front-end

**UCB1300**

| SYMBOL    | PIN | DESCRIPTION                | RESET<br>STATE     | TYPE <sup>(1)</sup> |

|-----------|-----|----------------------------|--------------------|---------------------|

| SIBDOUT   | 40  | SIB data output            | '1' <sup>(6)</sup> | O <sub>C</sub>      |

| SIBCLK    | 41  | SIB serial interface clock | _                  | I <sub>C</sub>      |

| SIBDIN    | 42  | SIB data input             | _                  | I <sub>C</sub>      |

| IRQOUT    | 43  | interrupt output           | ·0'                | O <sub>C</sub>      |

| n.c       | 44  | not connected              | _                  | _                   |

| IO4       | 45  | general purpose I/O pins   | input              | I/O <sub>C</sub>    |

| IO5       | 46  | general purpose I/O pins   | input              | I/O <sub>C</sub>    |

| IO6       | 47  | general purpose I/O pins   | input              | I/O <sub>C</sub>    |

| $V_{DDD}$ | 48  | digital supply             | _                  | S                   |

#### **Notes**

- 1.  $I/O_C = CMOS$  bidirectional;  $I_D =$  digital input; S = supply;  $O_A =$  analog output;  $I_C = CMOS$  input;  $I_A =$  analog input;  $I/O_A =$  analog bidirectional;  $O_C = CMOS$  output.

- 2. V<sub>SSD</sub> (pins 5 and 37) and V<sub>SSA1</sub> (pin 18) are connected internally within the UCB1300.

- 3. SKPRN/SPKRP (pins 8 and 9), TINN/TINP (pins 14 and 15) and TOUTP/TOUTN are differential pairs

- 4. TEST (pin 13) is connected to an internal pull-down resistor. This pin should be held LOW during normal operation of the circuit.

5

- 5. The 'not connected' pins (pins 6, 19, 31 and 44) are reserved for future applications and should be left floating.

- 6. SIBDOUT reset state is 1 until the SIB bus is running. SIBDOUT will be active once the SIB bus has started.

2000 Jun 26

## Advanced modem/audio analog front-end

**UCB1300**

6

2000 Jun 26

## Advanced modem/audio analog front-end

**UCB1300**

#### **FUNCTIONAL DESCRIPTION**

The UCB1300 consists of several analog and digital sub-circuits which can be programmed via the Serial Interface Bus (SIB). This enables the user to set the UCB1300 functionality according to actual application requirements.

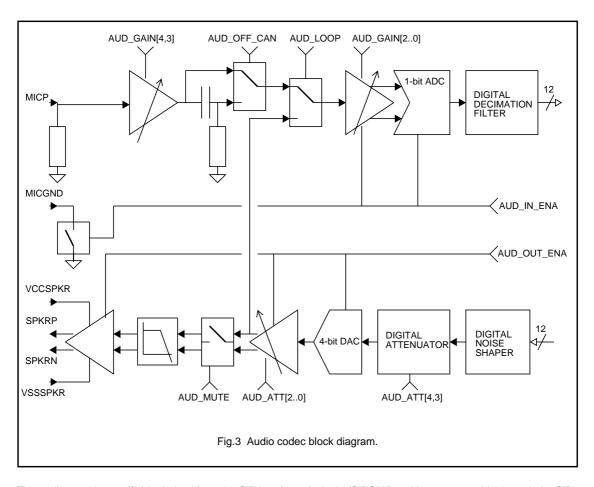

#### **AUDIO CODEC**

The audio codec contains an input channel, built up with a 64 times oversampling sigma delta analog to digital converter (ADC) with digital decimation filters and a programmable gain microphone preamplifier. The programmable gain microphone amplifier features a built-in offset cancellation stage, which reduces the distortion of this stage at high gain settings, caused by the offset voltages of the internal amplifiers or leakage on the board. It can be deactivated (reg13, bit 13) for improved performance at low gain settings. A general rule is that below a gain setting of 16 (24dB gain) the offset cancellation circuit will reduce THD and signal bandwidth and should then be deactivated.

The output path consists of a digital up-sample filter, a 64 time oversampling 4-bit digital-to-analog converter (DAC) circuit followed by a BTL speaker driver, capable of driving a 16  $\Omega$  speaker. The output path features a digital programmable attenuation and a mute function.

The audio codec also incorporates a loopback mode, in which codec output path and the input path are connected in series.

## Advanced modem/audio analog front-end

**UCB1300**

The audio sample rate ( $f_{sa}$ ) is derived from the SIB interface clock pin (SIBCLK) and is programmable through the SIB interface using AUD\_DIV[n]. The audio sample rate is given by the following equation:

$$f_{sa} = \frac{(2 \times f_{SIBCLK})}{(64 \times AUD\_DIV[n])}$$

(7< AUD\_DIV[n] < 128)

For example, a serial clock of 9.216 MHz, with a divisor of 12, results in an audio sample rate of 24.0 kHz. Both the rising and the falling edges of SIBCLK are used in case AUD\_DIV[n] is set to an odd number, which demands a 50% duty cycle of SIBCLK to obtain time equidistant sampling.

8

2000 Jun 26

## Advanced modem/audio analog front-end

**UCB1300**

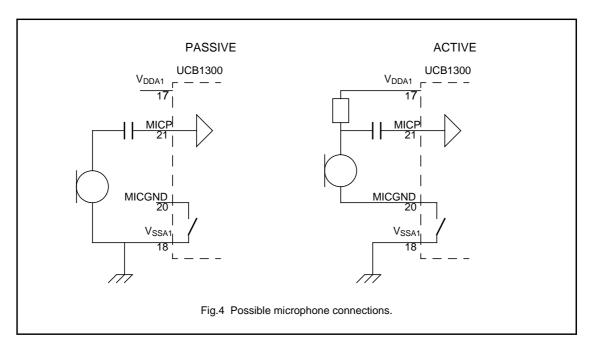

The UCB1300 audio codec input path accepts microphone signals directly, only a DC blocking capacitor is needed since the MICP input is biased around 1.4V. The 'ground' side of the microphone is either connected to the analog ground (V<sub>SSA1</sub>) or to the MICGND pin. The latter will decrease the current consumption of active microphones, since the MICGND pin is made Hi-Z when the audio codec input path is disabled.

The full scale input voltage of the audio input path is programmable in 1.5 dB steps by setting the appropriate number in AUDIO\_GAIN[n] in the audio control register A. Using very high gains may require the use of the internal offset cancellation circuit programmable in reg 13 to avoid clipping in the ADC.

A clip detection circuit will inform the user whenever the input voltage exceeds the maximum input voltage, since this will lead to a high distortion. In that case AUD\_CLIP\_STAT in the audio control register B is set. When ACLIP\_RIS\_INT is set, an interrupt is generated on the IRQOUT pin on the rising edge of the clip detect signal. When ACLIP\_FAL\_INT is set, an interrupt is generated on the falling edge of the clip detect signal.

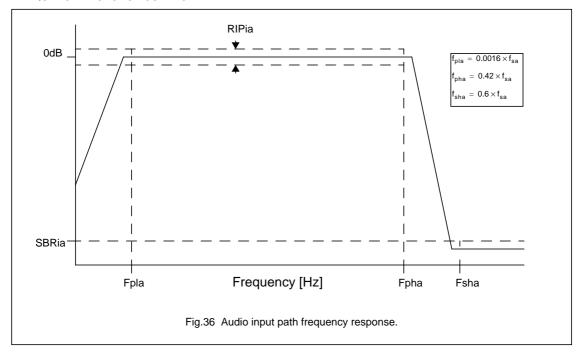

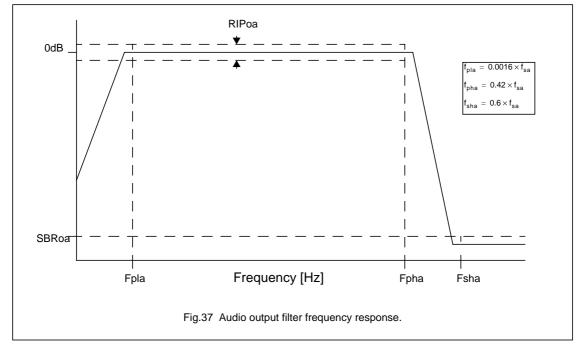

The frequency response of the audio codec depends mainly on the selected sample rate, since the bandwidth is limited in the down and up sampling filters. These digital filters both contain several FIR and IIR low pass filters and a DC removal filter (high pass filter). A third-order smoothing filter is implemented in the DAC path, between DAC and speaker driver stage to reduce the spurious frequencies at the speaker outputs.

9

2000 Jun 26

## Advanced modem/audio analog front-end

**UCB1300**

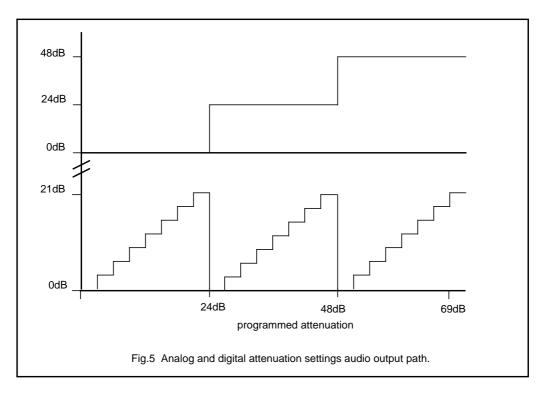

The output level can be attenuated in 3 dB steps down to -69 dB. The first 8 attenuation steps (0 to 21 dB) are implemented in the analog domain. The digital up sample filter contains a 24 dB and a 48 dB attenuation setting. This arrangement preserves the resolution, thus the 'audio quality' of the audio output signal for attenuation settings till 21 dB.

The speaker driver is muted when AUDIO\_MUTE in the audio control register B is set. The speaker driver will remain activated in that case, however no signal is produced by the speaker driver circuit.

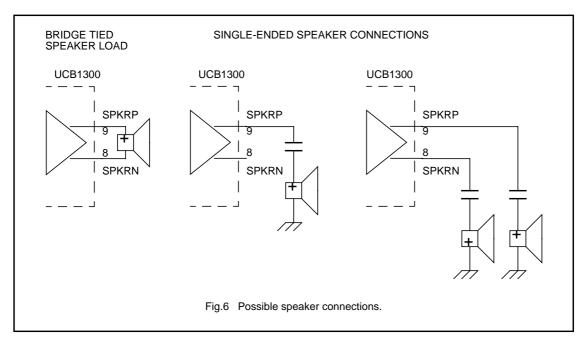

The speaker driver is designed to directly drive a Bridge Tied Load (BTL). This yields the highest output power and this arrangement does not require external DC blocking capacitors. The speaker driver also accepts single-ended connection of a speaker, in which case the maximum output power is reduced to a quarter of the BTL situation. Consequently this way of connecting the speaker to the speaker driver reduces the power consumption of the speaker driver in the UCB1300 by a factor of 2. Fig.6 shows possible ways to connect a speaker to the driver. Loading the amplifiers with a capacitive load may cause high frequency oscillations and should be done cautiously.

## Advanced modem/audio analog front-end

**UCB1300**

The audio input and output path are activated independently. The input path is enabled when AUDIO\_IN\_ENA is set, the output path is enabled when AUD\_OUT\_ENA is set in the audio control register B. This provides the user the means to reduce the current consumption of the UCB1300 if one part of the audio codec is not used in the application.

The audio codec has a loopback mode for system test purposes, which is activated when the AUDIO\_LOOP bit in the audio control register B is set. This is an analog loopback which internally connects the output of the audio output path to the input of the audio input path, (see Fig.3). In this mode the normal microphone input is ignored, but the speaker driver can be operated normally.

**UCB1300**

#### **TELECOM CODEC**

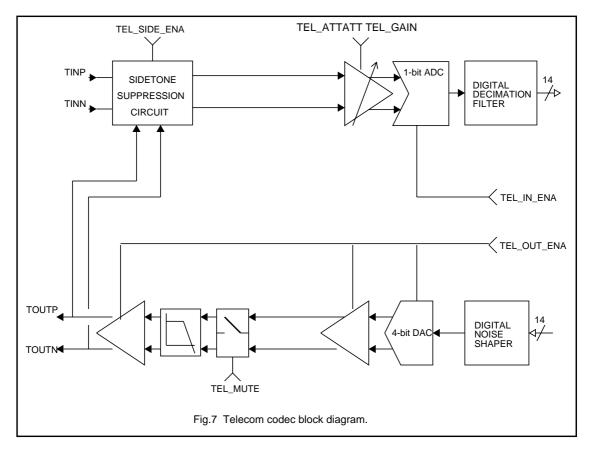

The telecom codec contains an input channel, built up from a 64 times oversampling sigma delta analog-to-digital converter (ADC) with digital decimation filters, programmable attenuation gain and built-in sidetone suppression circuit.

The output path consist of a digital up-sample filter, a 64 times oversampling 4-bit digital-to-analog converter (DAC) circuit followed by a differential output driver, capable of directly driving a  $600~\Omega$  isolation transformer. The output path includes a mute function. The telecom codec also incorporates a loopback mode, in which codec output path and the input path are connected in series.

The telecom sample rate (f<sub>st</sub>) is derived from the SIB interface clock pin (SIBCLK) and is programmable through the SIB interface. The telecom sample rate is given by the following formula:

$$f_{st} = \frac{(2 \times F_{SIBCLK})}{(64 \times TEL\_DIV[n])}$$

(15 < TEL\_DIV[n] < 128)

For example, a SIBCLK of 9.216 MHz, with a divisor of 40, results in a telecom sample rate of 7.2 kHz. Both the rising and the falling edges of the SIBCLK are used in case TEL\_DIV[n] is set to an odd number. In that case a 50% duty cycle of the SIBCLK signal is mandatory to obtain time equidistant sampling.

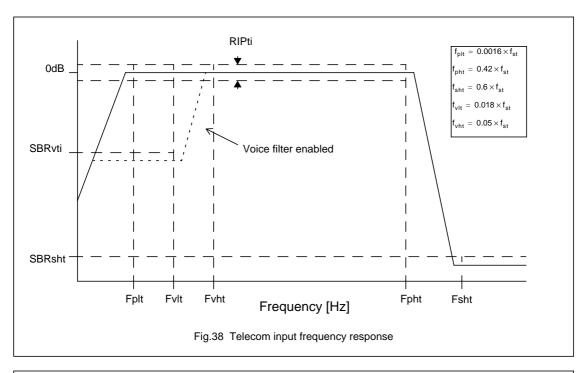

The input path of the telecom codec has a programmable attenuation gain. It also implements a voice band filter, which consists of a digital low pass filter, which is a part of the decimation filter. Therefore the pass band of the voice band filter

## Advanced modem/audio analog front-end

**UCB1300**

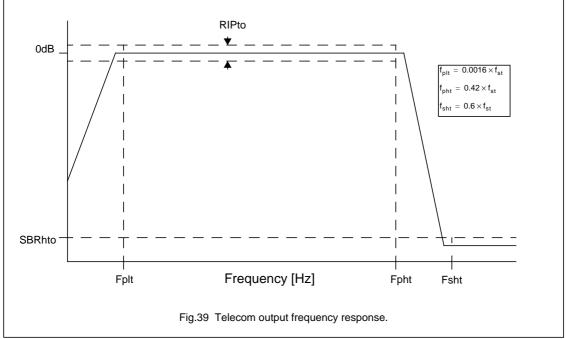

is determined by the selected telecom codec sample rate. This voice band filter is activated by setting TEL\_VOICE\_ENA in the telecom control register B. The resulting telecom input filter curves are given in Fig.38 and Fig.39.

The output section of the telecom codec is designed to interface with a 600  $\Omega$  line through an isolation transformer. The built-in mute function is activated by TEL\_MUTE in the telecom control register B. The output driver remains active in the mute mode, however no output signal is produced. Loading the drivers with a capacitive load may cause high frequency oscillations and should be done cautiously.

## Advanced modem/audio analog front-end

**UCB1300**

#### **TOUCH SCREEN MEASUREMENT MODES**

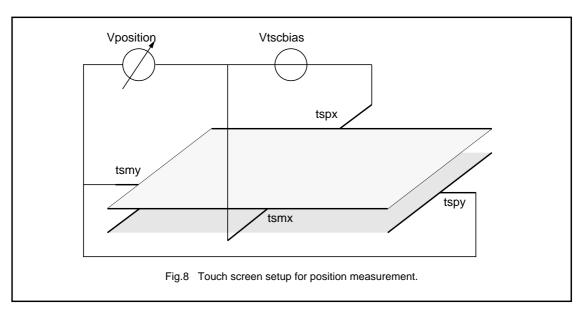

The UCB1300 contains an on-chip interface for a 4 wire resistive touch screen. This interface supports three modes of touch screen measurements: position, pressure and plate resistance.

#### **POSITION MEASUREMENT**

Two position measurements are needed to determine the location of the pressed spot. First an X measurement, secondly a Y measurement. The X plate is biased during the X position measurement of the X plate and the voltage on one or both Y terminals (TSPY, TSMY) measured. The circuit can then be represented by a potentiometer, with the TSPY and/or TSMY electrode being the 'wiper'. The measured voltage on the TSPY/TSMY terminal is proportional to the X position of the pressed spot of the touch screen.

In the Y position mode the X plate and Y plate terminals are interchanged, thus the Y plate is biased while the voltage on the TSPX and/or TSMX terminal is measured.

## Advanced modem/audio analog front-end

**UCB1300**

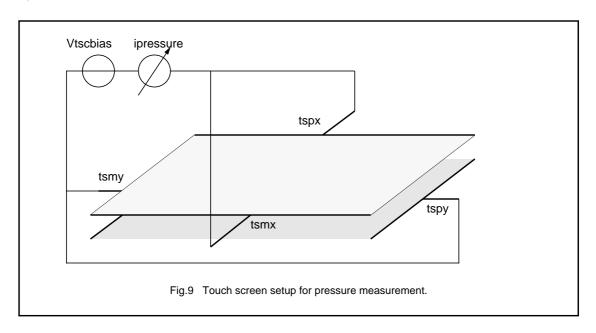

#### PRESSURE MEASUREMENT

The pressure used to press the touch screen can be determined. In fact, the contact resistance between the X and Y plate is measured, which is a good indication of the size of the pressed spot and the applied pressure. A soft stylus, e.g. a finger, leads to a rather large contact area between the two plates when a large pressure is applied. A hard stylus, e.g. a pen, leads to less variation in measured contact resistance since the contact area is rather small.

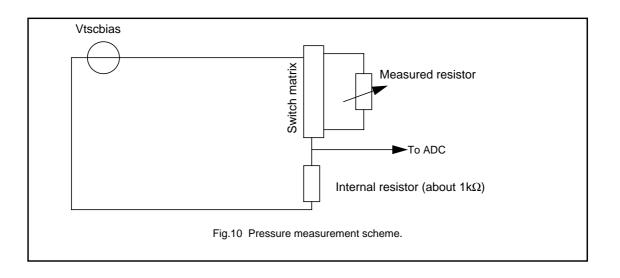

One plate is biased at one or both terminals during this pressure measurement, whereas the other plate is grounded, again on one or both terminals. The current flowing through the touch screen is a direct indication for the resistance between both plates. A compensation for the series resistance, formed by the touch screen plates itself will improve the accuracy of this measurement. The measurement is done with a resistive voltage divider. The internal resistor should be taken into account to evaluate the settling time of the pressure measurement given the board capacitors connected to the ADC tap point in pressure mode.

## Advanced modem/audio analog front-end

**UCB1300**

## Advanced modem/audio analog front-end

**UCB1300**

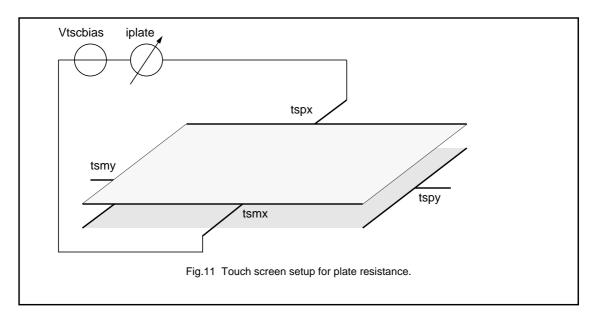

#### PLATE RESISTANCE MEASUREMENT

The plate resistance of a touch screen typically varies a lot due to processing spread. Knowing the actual plate resistance makes it possible to compensate for the plate resistance effects in pressure resistance measurements. The plate resistance decreases when two or more spots on the touch screen are pressed. In that case, a part of one plate, e.g. the X plate, is shorted by the other plate, which decreases the actual plate resistance

The plate resistance measurement is executed in the same way as the pressure resistance measurement. In this case only one of the two plates is biased and the other plate is kept floating. The current through the connected plate is again a direct indication of the connected resistance.

## Advanced modem/audio analog front-end

**UCB1300**

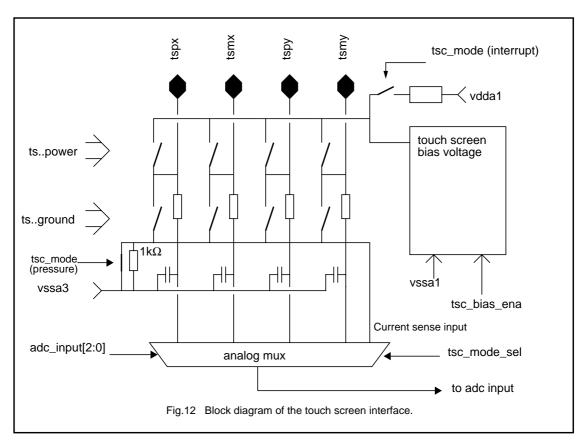

#### **TOUCH SCREEN INTERFACE**

The UCB1300 contains a universal resistive touch screen interface for 4-wire resistive touch screen, capable of performing position, pressure and plate resistance measurements. In addition, the touch screen can be programmed to generate interrupts when the touch screen is pressed. The last mode is also active when the UCB1300 is set in the stand-by mode.

The touch screen interface connects to the touch screen by four wires: TSPX, TSMX, TSPY and TSMY. Each of these pins can be programmed to be floating, powered or grounded in the touch screen switch matrix. The setting of each touch screen pin is programmable through the touch screen control register. Possible conflicting settings (grounding and powering of a touch screen pin at the same time) are detected by the UCB1300. In that case, the touch screen pin will be grounded.

In position mode, opening the TS..gnd switch can take a long time. To avoid unpredictable delays after changing the plates configuration, the touch screen interface should be programmed to pressure mode for the duration 1 SIB frame before resuming a position measurement.

The UCB1300's internal voltage reference ( $V_{ref}$ ) is used as reference voltage for the touch screen bias circuit. This makes the touch screen biasing independent of supply voltage and temperature variations. Four low pass filters, one on each touch screen terminal, are built in to minimize the noise coupled from the LCD into the touch screen signals. An LCD typically generates large noise glitches on the touch screen, since they are closely coupled. The influence of the glitches

## Advanced modem/audio analog front-end

**UCB1300**

can nevertheless be minimized by performing measurements when the LCD is quiet. This can be done by synchronizing the measurement and the video driver with the ADCSYNC pin.

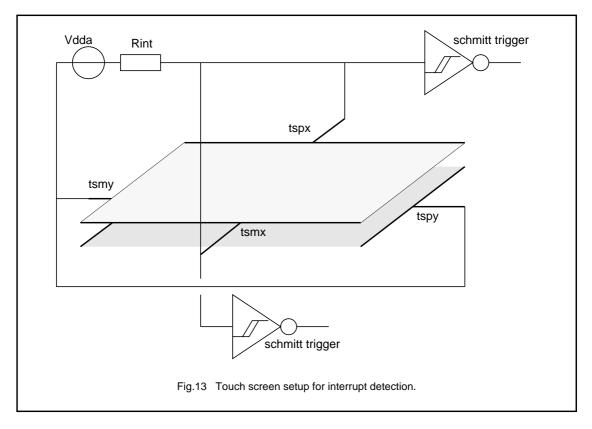

In addition to the measurements mentioned above, the touch screen can also act as an interrupt source. In this mode the X plate of the touch screen has to be powered and the Y plate has to be grounded. In this case the touch screen is not biased by the active touch screen bias circuit, but by a resistor to V<sub>DDA1</sub>. This configuration simply biases the touch screen and the UCB1300 does not consume power unless the touch screen is touched. The voltage on the X plate terminals drops if the screen is pressed. This voltage drop is detected by Schmitt-trigger circuits, of which the outputs are connected to the interrupt control block. A touch screen interrupt is generated either when the touch screen is pressed (falling edge enabled) or when the touch screen is released (rising edge enabled). It can be used to activate the system around the UCB1300 to start a touch screen read-out sequence. The internal Schmitt-trigger circuits are connected to the TSPX and TSMX signals after the built-in low pass filters. This reduces the number of spurious interrupts, due to the coupling between the LCD screen and the touch screen sensors.

Each of the four touch screen signals can be selected as input for the built-in 10-bit ADC, which is used to determine the voltage on the selected touch screen pin. The flexible switch matrix and the multi-functional touch screen bias circuit enables the user of the UCB1300 to set each desired touch screen configuration.

## Advanced modem/audio analog front-end

**UCB1300**

The setting of the touch screen bias circuit and the ADC input multiplexer is determined by the setting of TSC\_MOD[n] in the touch screen control register according the following table.

#### TOUCH SCREEN MODE SELECTION

| TSC_MODE[N] | SELECTED BITS | TOUCH SCREEN BIAS<br>SOURCE   | ADC MULTIPLEXER SETTING (TOUCH SCREEN INPUTS) |

|-------------|---------------|-------------------------------|-----------------------------------------------|

| 00          | interrupt     | resistor to V <sub>DDA1</sub> | defined by ADC_INPUT[n]                       |

| 01          | pressure      | touch screen bias circuit     | touch screen current monitor                  |

| 1X          | position      | touch screen bias circuit     | defined by ADC_INPUT[n]                       |

#### SUMMARY OF TOUCH SCREEN MODES; note 1

| TOUCH SCREEN<br>MEASUREMENT | TSPX                   | TSMX                    | TSPY                    | TSMY                    | TOUCH<br>SCREEN<br>MODE | TOUCH<br>SCREEN<br>BIAS |

|-----------------------------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| X position                  | powered <sup>(2)</sup> | grounded <sup>(2)</sup> | ADC_INPUT[n]            | ADC_INPUT[n]            | position                | enabled                 |

| Y position                  | ADC_INPUT[n]           | ADC_INPUT[n]            | powered <sup>(2)</sup>  | grounded <sup>(2)</sup> | position                | enabled                 |

| pressure - 1                | powered <sup>(2)</sup> | powered <sup>(2)</sup>  | grounded <sup>(2)</sup> | grounded <sup>(2)</sup> | pressure                | enabled                 |

| pressure - 2                | powered                | floating                | grounded                | floating                | pressure                | enabled                 |

| pressure - 3                | floating               | grounded                | powered                 | floating                | pressure                | enabled                 |

| pressure - 4                | floating               | powered                 | floating                | grounded                | pressure                | enabled                 |

| pressure - 5                | grounded               | floating                | floating                | powered                 | pressure                | enabled                 |

| X-plate resistance          | powered <sup>(2)</sup> | grounded <sup>(2)</sup> | floating                | floating                | pressure                | enabled                 |

| Y-plate resistance          | floating               | floating                | powered <sup>(2)</sup>  | grounded <sup>(2)</sup> | pressure                | enabled                 |

| interrupt                   | powered                | powered                 | grounded                | grounded                | interrupt               | disabled <sup>(3)</sup> |

#### **Notes**

- 1. Control register address 9 is used for touch screen mode selection.

- 2. The powered and grounded touch screen pins may be interchanged.

- 3. In this mode, the touch screen bias must be disabled by the user to prevent false interrupts.

## Advanced modem/audio analog front-end

**UCB1300**

#### 10-BIT ADC

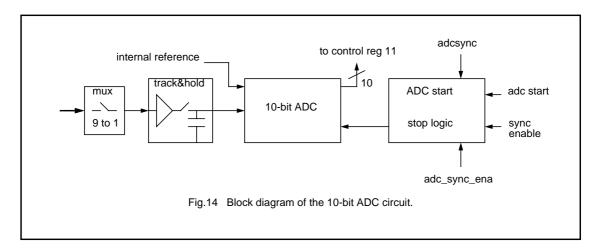

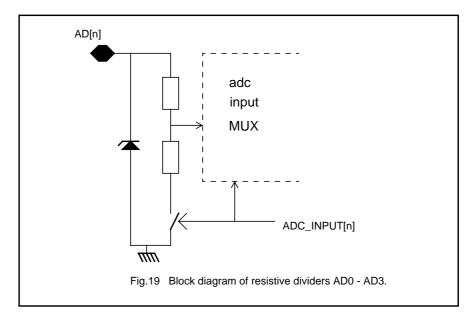

The UCB1300 includes a 10-bit successive approximation analog-to-digital converter (ADC) with built-in track and hold circuit and an analog multiplexer to select one of the 4 analog inputs (AD0 - AD3), the 4 touch screen inputs (TSPX, TSMX, TSPY, TSMY) or the pressure output of the touch screen bias circuit. The ADC is used to read-out the touch screen inputs and it measures the voltage on the four analog high voltage inputs AD0 - AD3. The analog multiplexer contains 4 resistive dividers to attenuate the high voltage on the AD0 - AD3 inputs to the ADC input range.

The ADC is controlled completely through the SIB interface, but the UCB1300 contains internal logic to ease the control of the ADC and to minimize the number of SIB frame read/write actions.

A complete ADC control sequence analog to digital conversion consists of several phases. Firstly, the ADC has to be enabled; secondly, the input selector must be set to the proper input; thirdly, the ADC conversion has to be started; and finally, the ADC result has to be read from register 11.

The ADC is activated by setting ADC\_ENA in register 10. The ADC circuit, including the track and hold circuit does not consume any power as long as this bit is reset. The analog input multiplexer is controlled by ADC\_INPUT[n] and the ADC is actually started with the ADC\_START bit. When TSPX and TSMX are in the interrupt mode, the ADC cannot be started, even to measure AD0-3.

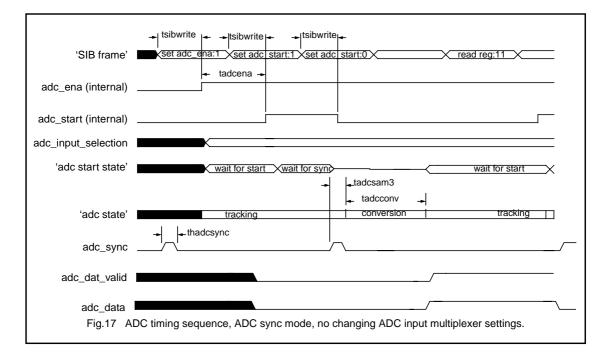

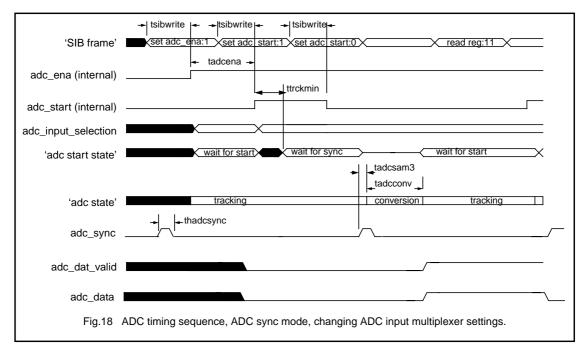

The UCB1300 has two different modes to start the ADC conversion, which are selected by the ADC\_SYNC\_ENA bit. The default mode is the non-synchronization mode, in which the conversion is started directly with a 0-to-1 transition of ADC\_START. Secondly the ADC is started at a rising edge of the signal applied to the ADCSYNC pin if ADC\_SYNC\_ENA is set. Activating the ADC while keeping the start logic in the started state (ADC\_START = 1) will lead to unpredictable behavior and the value of the ADC data register will not be meaningful. Always activate a start sequence for each acquisition (0-to-1 transition on the internal ADC\_START signal).

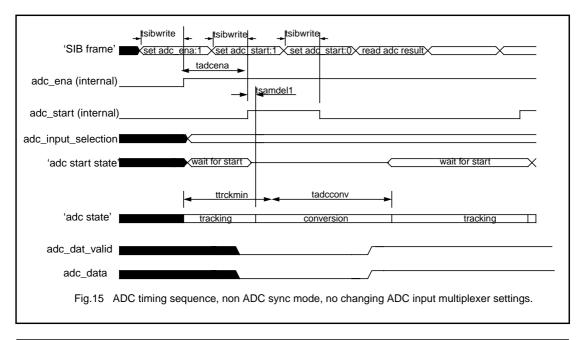

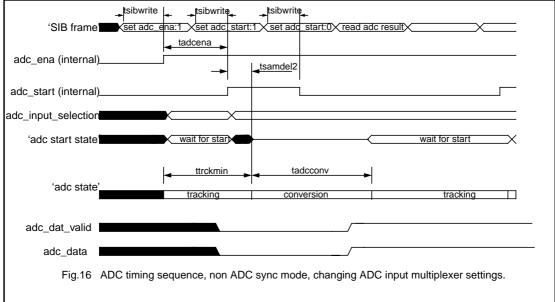

The internal track and hold circuit requires a certain settling time to track the input signal correctly. This can be ensured from the software by writing first a SIB frame with the ADC multiplexer setting before the SIB frame with the ADC\_START command is transferred. The UCB1300 ADC start/stop logic will detect whether the ADC input multiplexer is changed in the same SIB frame as the ADC start command is given. In that case, it will delay the actual start of the ADC circuit to ensure that the track and hold settling time requirements are met. This leads to the following two timing diagrams:

## Advanced modem/audio analog front-end

**UCB1300**

The ADC timing diagrams indicate that in the non-ADC sync mode the ADC result can be read in the SIB frame following the SIB frame with the ADC start command, if the ADC multiplexer setting is not changed. If the ADC input multiplexer setting is changed, the ADC result can be read in the second SIB frame following the SIB frame with the ADC start command.

## Advanced modem/audio analog front-end

**UCB1300**

The second ADC start mode gives the opportunity to start the ADC at the rising edge of the signal connected to the ADCSYNC pin. The 0-to-1 transition of the ADC\_START bit will arm the ADC, such that it will start in the first detected rising edge of the ADCSYNC signal. Also in this mode, the internal start/stop logic will detect whether the ADC multiplexer settings are changed simultaneously with the ADC start bit and it will add a delay to ensure sufficient setting time for the internal track and hold circuit. A rising edge of the signal connected to the ADCSYNC pin occurring during this tracking time is ignored; the ADC conversion is started on the first rising edge detected after this delay time. This leads to the following two timing diagrams of the ADC conversion.

## Advanced modem/audio analog front-end

**UCB1300**

The ADC sync mode is particularly useful when the internal ADC has to be synchronized to the external system. Typically it is used to synchronize the read-out of the touch screen to the driving of the LCD screen, which is normally placed beneath the touch screen. Many spikes and a lot of 'noise' are superimposed on the touch screen signals, due to the close coupling of the touch screen and the LCD.

The result of the conversion is stored in register 11 of the SIB interface, after the completion of the conversion. An interrupt may be generated whenever a conversion is completed (ADC\_FLA\_INT and/or ADC\_RIS\_INT bits in register 2 and 3) to ease the synchronization between the UCB1300 and the system controller. The ADC result is reset to 0x000, whenever the ADC is started or armed till the ADC conversion is completed. ADC\_DAT\_VAL in the SIB register 11 indicates the status of the ADC; it equals '0' when an ADC sequence is started, which implies that the ADC result is not valid and it equals '1' when the ADC conversion is completed and the result is stored in the SIB register 11.

## Advanced modem/audio analog front-end

**UCB1300**

The applied voltage on the four analog inputs of the UCB1300 (AD0 - AD3) is attenuated before it is applied to the ADC input multiplexer using on-chip resistive dividers. These high voltage inputs are optimized to handle voltages larger than the applied supply voltage. The built-in resistive voltage dividers are only activated if the corresponding analog input is selected. The resistive dividers are made floating when the input is not selected by the ADC input multiplexer, such that the input leakage of these high voltage analog pins is minimized. This makes these analog inputs very suitable to monitor battery voltages.

## Advanced modem/audio analog front-end

**UCB1300**

#### **ON-CHIP REFERENCE CIRCUIT**

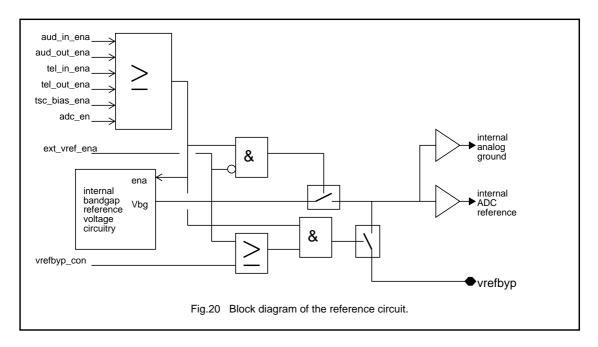

The UCB1300 contains an on-chip reference voltage source, which generates the reference voltages for the 10-bit ADC and the virtual analog ground. Alternatively the UCB1300 can be driven from an external reference voltage source.

The internal reference voltage is connected to the VREFBYP pin, where an external capacitor could be connected to filter this reference voltage, if VREF\_CON (register 10) is set. **THIS IS NOT RECOMMENDED** since the internal impedance of the reference (several 100 M $\Omega$ ) will be sensitive to board leakage and the turn on time constant will be very long. When choosing a capacitor, the internal impedance (around 50 k $\Omega$ ) should be taken into account.

An external voltage reference connected to the VREFBYP pin is used as voltage reference by the UCB1300 circuit, if the EXT\_REF\_ENA bit (register 10) is set. Two bits in the ADC control register determine the mode of operation of this reference voltage circuit. VREFBYP\_CON connects the internal reference voltage to the VREFBYP pin, while EXT\_VREF\_ENA disables the internal reference voltage and switches the UCB1300 into the external voltage reference mode.

## Advanced modem/audio analog front-end

**UCB1300**

#### SERIAL INTERFACE BUS

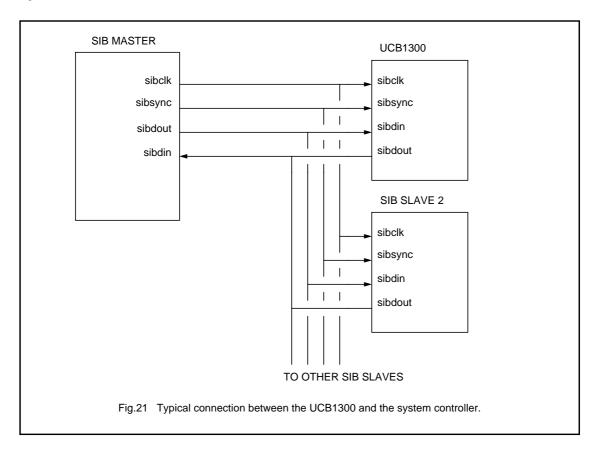

The UCB1300 Serial Interface Bus (SIB) is compatible with industry standard serial ports and devices, and is designed to connect directly to a system controller. The SIB protocol allows one or more slave devices to be connected to the system controller. The data transfer is always synchronous and it is frame based. The SIB interface consists of four signals: SIBDIN, SIBDOUT, SIBCLK and SIBSYNC.

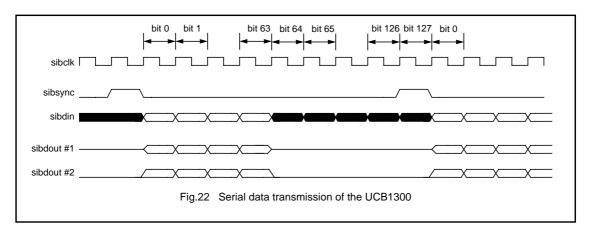

Each SIB frame consists of at least 64 clock cycles. Typically 128 bits are used, divided into 2 sub frames of 64 bits each. The first word (the bits 0 to 63) is read and/or written by the UCB1300, the remaining bits may be used for communication between the system controller and another slave device. The SIBDOUT pin of the UCB1300 is 3-stated for the bit 64 and higher in the SIB frame to prevent bus conflicts with other slave devices. However, when SIB\_ZERO (control register 1) is set, the SIBDOUT pin is forced to zero from bit 64 onwards to prevent the SIBDOUT line from floating. This feature is needed when the UCB1300 is the only slave device connected to the bus.

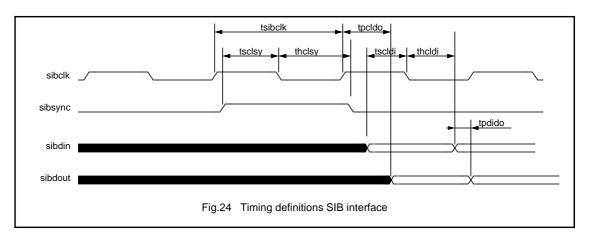

The UCB1300 always samples incoming data on the SIBDIN pin on the falling edge of SIBCLK and it outputs data on the SIBDOUT pin on the rising edge of the SIBCLK. The start of a new SIB frame is indicated by a pulse on the SIBSYNC line just before the start of this new SIB frame.

## Advanced modem/audio analog front-end

**UCB1300**

The applied clock signal to the SIBCLK pin is used as clock signal inside the UCB1300; all internal clock signals are derived from that. It is required that the SIBCLK signal is applied if one or more analog or digital functions are activated in the UCB1300; only the interrupt controller is implemented asynchronously. SIBCLK may be stopped when all digital and analog functions are disabled; in that case the lowest possible power consumption is met. The SIBCLK should not be stopped during a SIB frame, but only at the end of the SIB-frame, to ensure that all analog and digital functions are stopped properly.

**Note:** The interrupt controller is still active, due to its asynchronous implementation. Therefore, the UCB1300 can still generate interrupts to the system controller, when the SIBCLK is stopped.

The generation of the audio and telecom sample clocks requires that the SIBCLK signal is symmetrical: a non-symmetrical SIBCLK will lead to non-equidistant sample moments, when an odd frequency divisor is set in either of the audio or telecom control registers.

## Advanced modem/audio analog front-end

**UCB1300**

#### SIB DATA FORMAT

The first 64 bits in the SIB-frame are read and written by the UCB1300. They contain audio and telecom codec data fields, several control bits, and a control register data field, as defined in table below.

#### SIB DATA FORMATS

| SIB FRAME<br>BIT | SIBDIN FIELD DEFINITION                            | SIBDOUT FIELD DEFINITION                                                                                                                 |

|------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 11           | audio input path data (12 bits); bit 0 = MSB       | audio output path data (12 bits); bit 0 = MSB                                                                                            |

| 12 - 16          | not read but reserved                              | fixed '0'                                                                                                                                |

| 17 - 20          | control register address (4 bits); bit 17 = MSB    | control register address (4 bits); bit 17 = MSB; is a copy of the register address as present in the SIBDIN field in the same SIB frame. |

| 21               | write bit (write 1)                                | fixed '0'                                                                                                                                |

| 22 - 29          | not read but reserved                              | fixed '0'                                                                                                                                |

| 30               | audio valid sample flag                            | audio valid flag                                                                                                                         |

| 31               | telecom valid sample flag                          | telecom valid flag                                                                                                                       |

| 32 - 45          | telecom input path data (14 bits)                  | telecom output path data (14 bits); bit 32 = MSB                                                                                         |

| 46 - 47          | not read but reserved                              | fixed '0'                                                                                                                                |

| 48 - 63          | control register write data (16 bit); bit 48 = MSB | control register read data (16 bit); bit 48 = MSB                                                                                        |

Since the data transfer is completely synchronous, a given control register may be written many times, before the device feeding the data has a chance to change the control bits. The UCB1300 does detect whether the data is changed or not.

#### **CONTROL REGISTER DATA TRANSFER**

The last 16 bits of the UCB1300 word is made up of control register data. The selection of the control register and whether it is read or written is defined by the control register address field [bit 17:20] and the "write" bit [bit 21]. For a read action of a control register, the control register address field has to be set to the desired control register address and the "write" bit has to be set to zero in the SIBDIN stream. The read data is sent by the UCB1300 within the control register data field of SIBDOUT during the same frame as the read request occurred. In addition, during a read cycle, the control register data field of SIBDIN is ignored by the UCB1300, which implies that no modifications of the UCB1300 settings can be performed when the "write" bit equals zero in the SIBDIN data-stream.

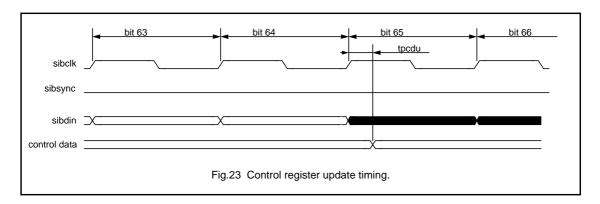

For a write cycle ("write" bit = 1), the control register data contents of SIBDIN are written to the UCB1300 register selected by the register address field after reception of the complete first word (the update is performed during the 64th bit in the SIB frame). This implies that the control register data contents of SIBDOUT data-stream in a SIB frame represents the previous contents of the selected control register.

The control register address in the SIBDOUT data-stream is a copy of the selected control register in the SIB data-stream. These bits show an additional delay, since they pass through additional circuitry.

The control register data is actually written in the control registers after the transfer of the first SIB word is completed. This implies that the control register data is updated during bit 64 of the SIB frame. The control data is only updated when the write bit is '1' in the SIB frame. The control data will not be updated when the write bit equals '0'. This simplifies the read out of control register data, since it is not required to send 'valid' data in the control register data field when a control register is read if the write bit is kept at '0'.

## Advanced modem/audio analog front-end

**UCB1300**

The control register data in the SIBDOUT stream is sampled just before the SIB frame is started. This implies that the returned control register data represents the 'old' control data, in case new data was provided in the SIBDIN data stream.

## Advanced modem/audio analog front-end

**UCB1300**

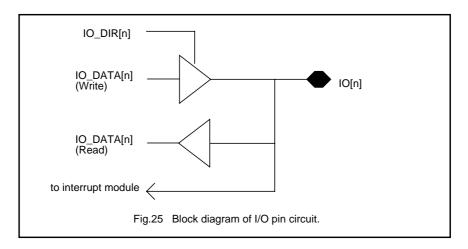

#### **GENERAL PURPOSE I/O**

The UCB1300 has 10 programmable digital input/output (I/O) pins. These pins can be independently programmed as input or output using IO\_DIR[0:9] in control register 1. The output data is determined by the content of IO\_DATA[n] in control register 0, while the actual status of these pins can be read from the IO\_DATA[n] bits in control register 0.

The data on the IO0-IO9 pins are fed into the interrupt control block, where they can generate an interrupt on the rising and/or falling edge of these signals.

## Advanced modem/audio analog front-end

**UCB1300**

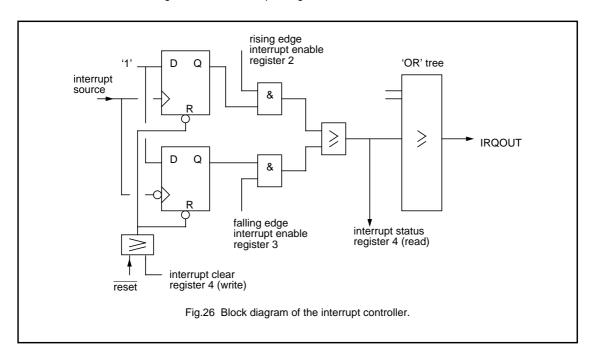

#### INTERRUPT CIRCUIT

The UCB1300 contains a programmable interrupt control block, which can generate an interrupt for a 0-to-1 and/or a 1-to-0 transition on one or more of the IO0-IO9 pins, the audio and telecom clip detect, the adc\_ready signal, and the TSPX and TSMX signals.

The interrupt generation mode is set by IO\_RIS\_INT[n] in register 2 and INT\_FAL\_ENA[n] in control register 3. The actual interrupt status of each signal can be read from control register 4. The interrupt status is cleared whenever a 0-to-1 transition is written in control register 4 for the corresponding bit.

The IRQOUT pin presents the 'OR' function of all interrupt status bits and can be used to give an interrupt to the system controller.

The interrupt controller is implemented asynchronously. This provides the possibility to generate interrupts when the SIBCLK is stopped, e.g. an interrupt can be generated in power down mode, when the touch screen is pressed or when the state of one of the IO pins changes.

## Advanced modem/audio analog front-end

**UCB1300**

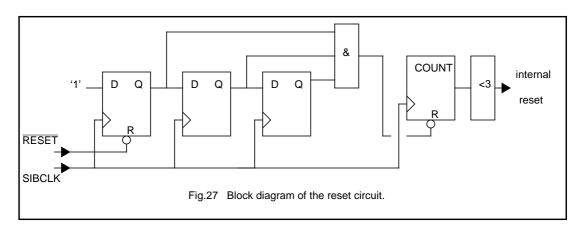

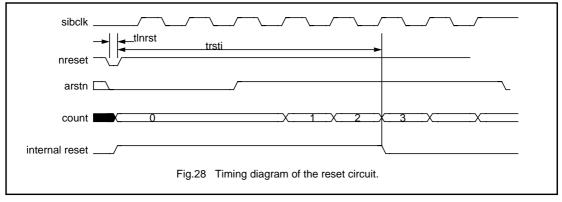

#### **RESET CIRCUIT**

RESET is captured in the UCB1300 using a asynchronous pulse stretching circuit. RESET may be pulled down when the SIBCLK is still stopped. The internal circuit remembers this reset signal and generates an internal reset signal for at least 5 SIBCLK periods.

## Advanced modem/audio analog front-end

**UCB1300**

#### POWER ROUTING STRATEGY

The UCB1300 has nine power supply pins, since the UCB1300 contains five power supply regions within the circuit. The analog and digital parts have their separate power supplies to reduce the interference between these parts. The speaker driver circuit is powered separately  $(V_{DDA2}/V_{SSA2})$  from the other analog circuit parts, and the touch screen switch matrix has its own ground pin  $(V_{SSA3})$ . This separation in the analog part reduces the interference between the speaker driver and the touch screen switch matrix, which has relatively large and fluctuating current consumption and the remaining parts of the analog circuit.

## Advanced modem/audio analog front-end

**UCB1300**

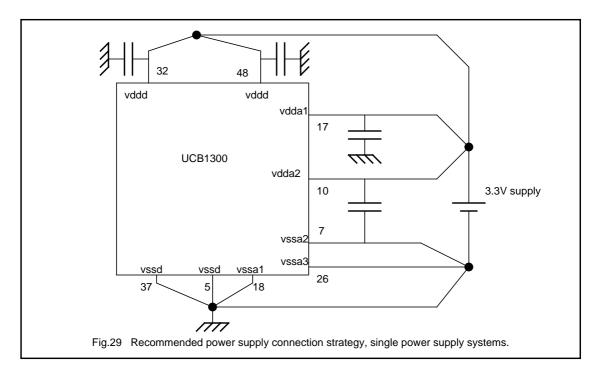

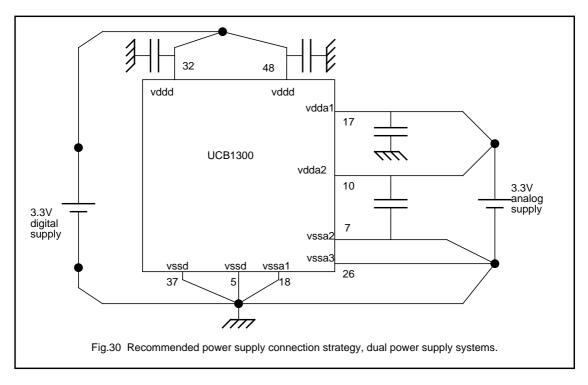

The  $V_{SSD}$  pins and the  $V_{SSA1}$  pin are connected within the UCB1300 circuit. It is recommended to connect the  $V_{SSD}$  pins and the  $V_{SSA1}$  directly to a ground plane on the PCB. The split in power supply connections should be maintained on the PCB to get optimal separation. Fig.29 shows the recommended PCB power supply strategy if only one single supply is used, while Fig.30 shows the recommended power supply connection for a dual power supply system with separate analog and digital supplies.

## Advanced modem/audio analog front-end

**UCB1300**

#### APPLICATION INFORMATION

In this chapter some application information is provided. Additional information is also available in the following application notes (available at www.philips.semiconductors.com)

- AN807: UCB1300 audio codec

- AN809: Differences between UCB1300 and UCB1200

- AN810: DAA printed circuit board layout

- AN812: Data access arrangement (DAA)

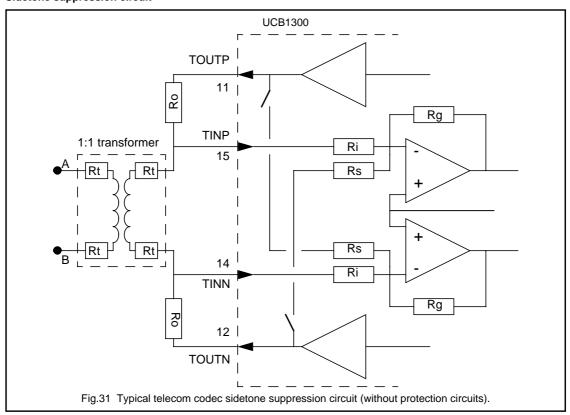

#### Sidetone suppression circuit

An important built-in feature of the telecom codec is the sidetone suppression circuit. The sidetone suppression circuit is activated when TEL\_SIDE\_ENA in the telecom control register B is set. The telecom input signal contains a large part of the telecom output signal, when the sidetone suppression circuit is disabled. The available dynamic range of the telecom input is occupied largely by the telecom output voltage.

The sidetone suppression circuit subtracts a part of the telecom output signal from the telecom input signal when activated. In that case, the available dynamic range is used more effectively than without sidetone suppression.

The built-in side tone suppression circuit, shown in Fig.31, has a fixed subtraction ratio, set be the resistors  $R_s$  and  $R_i$ , which equals 600/456. This ratio is calculated from the following relations:

## Advanced modem/audio analog front-end

**UCB1300**

The impedance seen by the telephone line equals:

$$Z_{line} \, = \, 2 \, \times \! \left( R_t + R_t + \frac{R_o \, \times \, R_i}{R_o + R_i} \right), \label{eq:Zline}$$

in which  $R_t$  represents winding resistance of the transformer, divided by 2. Assuming  $R_i \gg R_o$ , then:

$$R_{line} \, = \, R_t + R_t + R_o = \frac{600}{2} = 300 \Omega$$

A typical transformer has 156  $\Omega$  winding impedance, thus R<sub>o</sub> should be 144  $\Omega$ . The ratio of the telecom input and output voltage is therefore:

$$V_{i(tel)} = V_{o(tel)} \times \frac{156 + 300}{156 + 300 + 144} = V_{o(tel)} \times \frac{456}{600}$$

### Advanced modem/audio analog front-end

**UCB1300**

### Codec data transfer

The UCB1300 codec operates at samples which depend on the applied SIBCLK frequency and the programmed audio and telecom divisors. The codec data transfer between the UCB1300 and the system controller has to be synchronized with the UCB1300 sample counters and the SIB bus data transfer protocol to prevent conversion errors, resulting in high distortion.

Correct codec data transfer is obtained easily when the UCB1300 is connected to one of the controllers in the PR3000 series, but the UCB1300 can also be connected to other controllers, if the following data protocol is used.

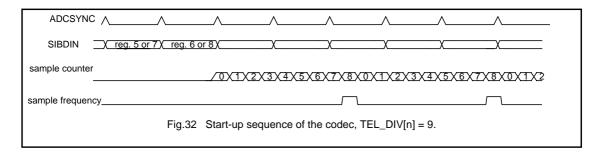

#### START OF CODEC DATA TRANSFER

The UCB1300 internal sample counters are started at the beginning of the first SIB frame following the SIB frame in which the codec input and/or output path is enabled. This implies that the sample rate divisor has to be programmed before the codec input and/or output path is enabled, Fig.32. Changing the sample rate on the fly, that is, without disabling both the codec input and output path before the divisor is reprogrammed, will disturb the codec data transfer synchronization between the UCB1300 and its controller, and is therefore not allowed.

### Advanced modem/audio analog front-end

**UCB1300**

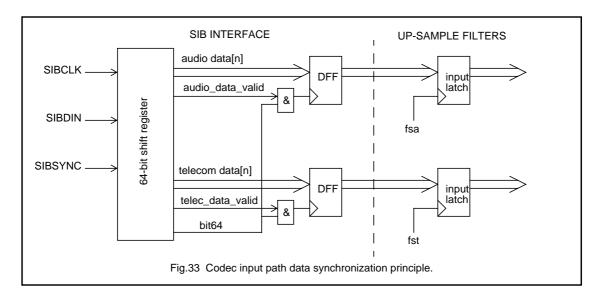

CODEC DATA TRANSFER INTO THE UCB1300

Both the audio and the telecom data is transferred within the SIB frame (bit 11-0 and bit 47-32). This data is accompanied by two data valid flags (bit 30: audio data valid; bit 31: telecom data valid). The codec data in the SIB frames is only processed in the UCB1300 if the appropriate data valid flag is set in the frame; the data is discarded when the data flag equals '0'. Figure 33 shows the basic codec data synchronization principle used in the UCB1300.

Figure 33 shows that audio and telecom data is made available for the codec up sample filters during the 64th bit in the SIB frame. This implies that the codec data has to be transferred in one of the SIB frames preceding the codec sample moment.

**Note:** If the programmed divisor equals a multiple of 4, the codec data transfer is synchronized to the SIB frame repetition rate (e.g. AUD\_DIV[n] =  $8 \Rightarrow 1$  sample is needed in 2 SIB frames, AUD\_DIV[n] =  $12 \Rightarrow 1$  sample is needed in 3 SIB frames, etc.).

### Advanced modem/audio analog front-end

UCB1300

#### CODEC DATA TRANSFER FROM THE UCB1300

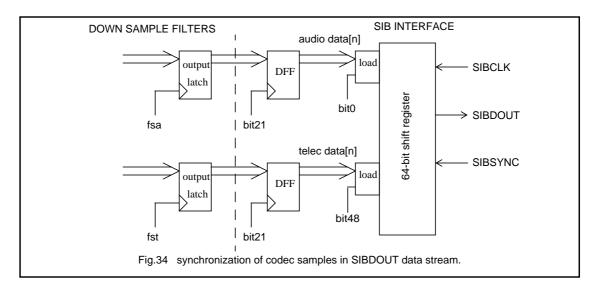

The data resulting from the UCB1300 codec ADC (input) paths is transfer to the system controller at the programmed codec sample rate. However the codec data is synchronized with the SIB frame repetition rate. Figure 34 shows the basic synchronization principle used inside the UCB1300. Codec data will be present in each SIB frame produced by the UCB1300: the sample will be repeated in the following SIB frames till a new sample has become available.

The codec samples in the SIBDOUT stream are also accompanied by a audio and telecom data valid bit (bit 30 and bit 31). These data valid flags are zero if the corresponding codec ADC paths are disabled and during the start up period of the codec's, when unreliable samples are generated. By default (after reset), the data valid bits will be continuously '1' when reliable samples are generated.

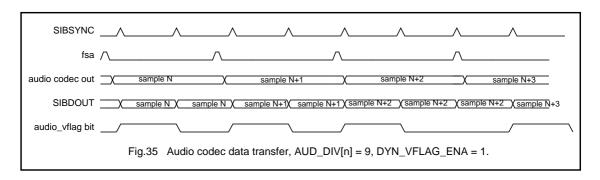

However when DYN\_VFLAG\_ENA is set, the data valid bits will be '1' during one of the SIB frames, containing identical samples (this is the case when a high divisor is programmed). The audio\_vflag bit will be high during the last sample in a series of identical samples, while the telecom\_vflag bit is high at the first sample in a series of identical bits. An example of the timing diagram is shown in Figure 35.

## Advanced modem/audio analog front-end

**UCB1300**

### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134); notes 1 and 2

| SYMBOL            | PARAMETER                                  | MIN. | MAX.                  | UNIT |

|-------------------|--------------------------------------------|------|-----------------------|------|

| $V_{DD}$          | supply voltage                             | -0.5 | +5.0                  | V    |

| V <sub>I</sub>    | DC input voltage (except inputs AD0 - AD3) | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| V <sub>I</sub>    | DC input voltage AD0 - AD3                 | -0.5 | +8.5                  | V    |

| Vo                | DC output voltage                          | -    | V <sub>DD</sub> + 0.5 | V    |

| I <sub>I(d)</sub> | diode input current                        | -    | 10                    | mA   |

| I <sub>O(d)</sub> | diode output current                       | -    | 10                    | mA   |

| Io                | continuous output current, digital outputs | -    | 4                     | mA   |

| T <sub>stg</sub>  | storage temperature range                  | -55  | +150                  | °C   |

### **Notes**

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at these or any conditions other than those described in

the Absolute Maximum Rating section of this specification is not implied.

- Parameters are valid over the ambient operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SSD</sub> (pin 37), unless otherwise noted.

### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                               | VALUE | UNIT |

|----------------------|---------------------------------------------------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient in free air | 67    | K/W  |

## Advanced modem/audio analog front-end

**UCB1300**

### **DC CHARACTERISTICS**

$V_{SSD} = V_{SSA1} = V_{SSA2} = V_{SSA3} = 0 \text{ V}; T_{amb} = 25 \text{ °C}; f_{i(sibclk)} = 9.216 \text{ MHz}; V_{l(ref)} = 1.2 \text{ V}; \text{ all voltages referenced to } V_{SSD}$  (pin 5); unless otherwise specified.

| SYMBOL                 | PARAMETER                                      | CONDITIONS                                      | MIN.                | TYP. | MAX.                 | UNIT |

|------------------------|------------------------------------------------|-------------------------------------------------|---------------------|------|----------------------|------|

| $V_{DDD}$              | digital supply voltage                         |                                                 | 3.0                 | 3.3  | 3.6                  | V    |

| V <sub>DDA1</sub>      | analog supply voltage - excl. speaker driver   |                                                 | 3.0                 | 3.3  | 3.6                  | V    |

| V <sub>DDA2</sub>      | analog supply voltage -<br>speaker driver only |                                                 | 3.0                 | 3.3  | 3.6                  | V    |

| V <sub>SSA2</sub>      | analog ground - speaker driver                 |                                                 | -0.4                | 0    | +0.4                 | V    |

| V <sub>SSA3</sub>      | analog ground - touch screen switch matrix     |                                                 | -0.4                | 0    | +0.4                 | V    |

| I <sub>DDD</sub>       | digital supply current <sup>(1)</sup>          | full functionality                              |                     | 19   | -                    | mA   |

|                        |                                                | only audio codec activated                      | -                   | 17   | -                    | mA   |

|                        |                                                | only telecom codec activated                    | -                   | 19   | -                    | mA   |

|                        |                                                | only touch screen activated                     | -                   | 15   | -                    | mA   |

|                        |                                                | only ADC activated                              | -                   | 15   | -                    | mA   |

|                        |                                                | no functions activated; f <sub>sibclk</sub> off | -                   | -    | 10                   | μΑ   |

| I <sub>DDA1</sub>      | analog supply current(1)(2)                    | full functionality                              | -                   | 4.6  | -                    | mA   |

|                        |                                                | only audio codec activated                      | -                   | 3.7  | -                    | mA   |

|                        |                                                | only telecom codec activated                    | -                   | 4.4  | -                    | mA   |

|                        |                                                | only touch screen activated                     | -                   | 1.0  | -                    | mA   |

|                        |                                                | only touch screen in interrupt mode             | -                   | -    | 100                  | μА   |

|                        |                                                | only ADC activated                              | -                   | 1.0  | -                    | mA   |

|                        |                                                | no analog functions activated                   | -                   | <10  | -                    | μΑ   |

| I <sub>DDA2</sub>      | total speaker driver supply <sup>(1)(2)</sup>  | speaker driver enabled                          | -                   | 0.6  | -                    | mA   |

|                        | current                                        | speaker driver disabled                         | -                   | -    | 10                   | μΑ   |

| V <sub>IL</sub>        | LOW level input voltage                        |                                                 | -0.5                | -    | +0.3V <sub>DDD</sub> | V    |

| V <sub>IH</sub>        | HIGH level input voltage                       |                                                 | $0.7V_{DDD}$        | -    | 0.5V <sub>DDD</sub>  | V    |

| V <sub>OL</sub>        | LOW level output voltage                       | $I_{OL} = 2 \text{ mA}$                         | -                   | -    | 0.2V <sub>DDD</sub>  | V    |

| V <sub>OH</sub>        | HIGH level output voltage                      | I <sub>OH</sub> = 2 mA                          | 0.8V <sub>DDD</sub> | -    | -                    | V    |

| f <sub>i(sibclk)</sub> | serial interface clock frequency               |                                                 | 0                   | 10   | 15                   | MHz  |

| T <sub>amb</sub>       | operating ambient temperature range            |                                                 | -20                 | -    | 70                   | °C   |

### **Notes**

- 1. Indicative value measured during the initial characterization.

- 2. Excluding connected touch screen and speaker load currents.

## Advanced modem/audio analog front-end

**UCB1300**

### **AC CHARACTERISTICS**

$V_{SSD} = V_{SSA1} = V_{SSA2} = V_{SSA3} = 0 \text{ V; } V_{DDD} = V_{DDA1} = V_{DDA2} = 3.3 \text{ V} \pm 10\%; T_{amb} = 25 \text{ °C; } V_{I(ref)} = 1.2 \text{ V; } f_{i(sibclk)} = 9.216 \text{ MHz; unless otherwise specified.}$

| SYMBOL                 | PARAMETER                        | CONDITIONS                                                                                                             | MIN. | TYP. | MAX. | UNIT |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Audio Input; no        | tes 1 and 2                      |                                                                                                                        | •    | •    | •    | •    |

| f <sub>sa</sub>        | audio sample frequency           |                                                                                                                        | -    | -    | 26   | kHz  |

| V <sub>I(RMS)</sub>    | input voltage (RMS value)        | 0 dB gain setting                                                                                                      | 90   | 100  | 125  | mV   |

| V <sub>I(BIAS)</sub>   | DC bias voltage                  | MICP input                                                                                                             | 1.35 | 1.4  | 1.5  | V    |

| Z <sub>i</sub>         | input impedance                  |                                                                                                                        | 20   | 25   | -    | kΩ   |

| Z <sub>(18-20)</sub>   | impedance MICGND -<br>VSSA1      |                                                                                                                        | -    | -    | 200  | Ω    |

| G <sub>step</sub>      | gain step size                   |                                                                                                                        | 1    | 1.5  | 2    | dB   |

| N <sub>step</sub>      | number of gain settings          |                                                                                                                        | -    | 32   | -    | -    |

| G <sub>v</sub>         | gain                             | (AUD_GAIN=011111)                                                                                                      | 15   | 22.5 | 28   | dB   |

| E <sub>G</sub>         | gain error                       | each gain step                                                                                                         | -1   | -    | 1    | dB   |

| RES                    | resolution                       |                                                                                                                        | -    | 12   | -    | bit  |

| LE <sub>(d)(ADC)</sub> | ADC differential linearity error |                                                                                                                        | -    | -    | 1    | LSB  |

| THD                    | total harmonic distortion        | input gain = 0 dB<br>(AUD_GAIN = 00000);                                                                               | -    | -65  | -40  | dB   |

|                        |                                  | input signal = 1 mVrms<br>input gain = 22.5 dB<br>(AUD_GAIN[n] = 01111);<br>AC coupling disabled<br>(AUD_OFF_CAN = 0); | -    | -36  | -26  | dB   |

|                        |                                  | input signal = 0.4mVrms<br>input gain = 46.5 dB<br>(AUD_GAIN[n] = 11111);<br>AC coupling enabled<br>(AUD_OFF_CAN = 1); |      | -29  |      | dB   |

| S/N                    | signal-to-noise ratio            | input gain = 0 dB<br>(AUD_GAIN = 00000)                                                                                | 50   | 68   | -    | dB   |

|                        |                                  | input signal = 1mVrms;<br>input gain = 22.5 dB<br>(AUD_GAIN[n] = 01111);                                               | 25   | 32   | -    | dB   |

|                        |                                  | input signal = 0.4mVrms;<br>input gain = 46.5 dB<br>(AUD_GAIN[n] = 11111);                                             |      | 22   |      | dB   |

| PBRR                   | pass-band ripple rejection       | $f_{pla} < f_{sig} < f_{pha}$ <sup>(3)</sup>                                                                           | -    | -    | 1.2  | dB   |

| SBR                    | stop-band rejection              | $f_{sha} < f_{sig} < 20 \text{ kHz}^{(3)}$                                                                             | 50   | -    | -    | dB   |

| D <sub>offset</sub>    | digital offset                   | no signal applied to MICP                                                                                              | -    | -    | 50   | LSB  |

# Advanced modem/audio analog front-end

**UCB1300**

| SYMBOL                 | PARAMETER                              | CONDITIONS                                                                                                  | MIN. | TYP. | MAX. | UNIT |

|------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Audio Output;          | notes 4 and 5                          |                                                                                                             |      |      |      |      |

| V <sub>O(RMS)</sub>    | output voltage (RMS value)             | attenuation = 0 dB,<br>differentially measured<br>between SKPRN and<br>SPRKP                                | 1.0  | 1.25 | 1.5  | V    |

| E <sub>offset</sub>    | offset error (peak-to-peak value)      |                                                                                                             | -    | -    | 100  | mV   |

| V <sub>O(BIAS)</sub>   | DC bias voltage                        | SPKRP/SKPRN                                                                                                 | 1.2  | 1.4  | 1.6  | V    |

| $\alpha_{step}$        | attenuation step size (analog section) |                                                                                                             | 2.5  | 3.0  | 3.5  | dB   |

| N <sub>step</sub>      | number of attenuation steps            |                                                                                                             | -    | 24   | -    | -    |

| α                      | attenuation                            |                                                                                                             | 63   | 69   | 75   | dB   |

| RES                    | resolution                             |                                                                                                             | -    | 12   | -    | bit  |

| LE <sub>(d)(DAC)</sub> | DAC differential linearity error       |                                                                                                             | -    | -    | 1    | LSB  |

| THD                    | total harmonic distortion              |                                                                                                             | -    | -    | -35  | dB   |

|                        |                                        | 1 kΩ headphone load                                                                                         | -    | -    | -45  | dB   |

| S/N                    | signal-to-noise ratio                  | 16 Ω speaker; 100 Hz to 20 kHz bandwidth                                                                    | 40   | -    | -    | dB   |

| PBRR                   | pass-band ripple rejection             | $f_{pla} < f_{sig} < f_{pha}^{(6)}$                                                                         | -    | -    | 1.2  | dB   |

| SBR                    | stop-band rejection                    | $f_{sha} < f_{sig} < 20 \text{ kHz}^{(6)}$                                                                  | 50   | -    | -    | dB   |

| OBR <sub>(RMS)</sub>   | out-of-band rejection (RMS value)      | f > 20 kHz                                                                                                  | -    | -    | 50   | mV   |

| Z <sub>speaker</sub>   | speaker impedance                      |                                                                                                             | 8    | 16   | -    | Ω    |

| Telecom Input;         | notes 2 and 7                          |                                                                                                             |      |      |      |      |

| f <sub>st</sub>        | sample frequency                       |                                                                                                             | -    | -    | 10   | kHz  |

| V <sub>I(RMS)</sub>    | input voltage (RMS value)              | differentially applied to<br>TINN and TINP;<br>no I/P attenuation enabled<br>(TEL_ATT = 0,<br>TEL_GAIN = 0) | 330  | 370  | 410  | mV   |

| $V_{I(BIAS)}$          | DC bias voltage                        | TINN/TINP                                                                                                   | 1.2  | -    | 1.6  | V    |

| i                      | input attenuation                      | input attenuation<br>amplification enabled<br>(TEL_ATT = 1)                                                 | -6.5 | -6   | -5.5 | dB   |

| $\alpha_{i}$           | input attenuation gain                 | input attenuation<br>amplification enabled<br>(TEL_ATTAMPL = 1,<br>TEL_ATT = 0)                             | 5.5  | 6    | 6.5  | dB   |

| Z <sub>i</sub>         | input impedance                        |                                                                                                             | 25   | -    | -    | kΩ   |

| S/N                    | signal-to-noise ratio                  |                                                                                                             | 65   | 75   | -    | dB   |

| THD                    | total harmonic distortion              |                                                                                                             | -    | -76  | -65  | dB   |

# Advanced modem/audio analog front-end

**UCB1300**

| SYMBOL                 | PARAMETER                                             | CONDITIONS                                                                                     | MIN. | TYP. | MAX. | UNIT |

|------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| LE <sub>(d)(ADC)</sub> | ADC differential linearity error                      |                                                                                                | -    | -    | 2    | LSB  |

| RES                    | resolution                                            |                                                                                                | -    | 14   | -    | bit  |

| PBRR                   | pass-band ripple rejection                            | $f_{\text{plt}} < f_{\text{sig}} < f_{\text{pht}}$ ; no voice filter <sup>(8)(16)</sup>        | -    | -    | 1.2  | dB   |

|                        |                                                       | $f_{\text{vht}} < f_{\text{sig}} < f_{\text{pht}}$ ; voice filter activated <sup>(8)(16)</sup> | -    | -    | 1.2  | dB   |

| SBR                    | stop-band rejection                                   | $f_{sig} < f_{vlt}$ ; voice filter activated <sup>(8)(16)</sup>                                | 30   | -    | -    | dB   |

|                        |                                                       | $f_{sht} < f_{sig}^{(8)(16)}$                                                                  | 50   | -    | -    | dB   |

| D <sub>offset</sub>    | digital offset                                        | no signal applied to MICP                                                                      | -    | -    | 50   | LSB  |

| S <sub>sup</sub>       | sidetone suppression effectiveness                    | $600~\Omega$ line impedance; 1:1 transformer with 156 $\Omega$ winding resistance              | 20   | -    | -    | dB   |

| Telecom outpu          | it; note 5                                            |                                                                                                |      |      |      |      |

| f <sub>st</sub>        | sample frequency                                      |                                                                                                | T-   | 8    | -    | kHz  |

| V <sub>O(RMS)</sub>    | output voltage (RMS value)                            | differentially measured between TOUTP and TOUTN                                                | 1.35 | -    | 1.85 | V    |

| V <sub>O(BIAS)</sub>   | DC bias voltage                                       | TOUTP/TOUTN; telecom O/P path enabled                                                          | 1.2  | -    | 1.6  | V    |

| RES                    | resolution                                            |                                                                                                | -    | 14   | -    | bit  |

| S/N                    | signal-to-noise ratio                                 |                                                                                                | 65   | 75   | -    | dB   |

| THD                    | total harmonic distortion                             |                                                                                                | -    | -76  | -65  | dB   |

| PBRR                   | pass-band ripple rejection                            |                                                                                                | T-   | -    | 1.2  | dB   |

| SBR                    | stop-band rejection                                   | $f_{sht} < f < f_{st}^{(9)}$                                                                   | 70   | -    | -    | dB   |

| OBR <sub>(RMS)</sub>   | out-of-band rejection<br>(RMS value)                  | $f > f_{st}^{(9)(16)}$                                                                         | -    | -    | 25   | mV   |

| Z <sub>o(load)</sub>   | load impedance                                        |                                                                                                | 600  |      |      | Ω    |

| E <sub>offset</sub>    | offset error                                          | note 10                                                                                        | -    | -    | 100  | mV   |

| Touch screen           | -                                                     |                                                                                                | •    | '    |      |      |

| V <sub>I(BIAS)</sub>   | bias voltage                                          | touch screen position mode selected                                                            | 1.6  | 1.8  | 2.0  | V    |

| 1                      | touch screen current                                  | touch screen position mode selected                                                            | 10   | -    | -    | mA   |

| R <sub>i</sub>         | Max. touch screen resistance to generate an interrupt | touch screen interrupt<br>mode selected                                                        | -    | -    | 2500 | Ω    |

| R <sub>gs</sub>        | ground switch on resistance                           |                                                                                                | -    | -    | 50   | Ω    |

| R <sub>ps</sub>        | power switch on resistance                            |                                                                                                | -    | -    | 50   | Ω    |

# Advanced modem/audio analog front-end

**UCB1300**

| SYMBOL                  | PARAMETER                                                     | CONDITIONS                                                           | MIN.                 | TYP.                   | MAX.                   | UNIT |

|-------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|----------------------|------------------------|------------------------|------|

| t <sub>STRTU</sub>      | start up time of touch<br>screen bias voltage<br>generator    |                                                                      | -                    | -                      | 25                     | μs   |

| Eidle                   | Idle pressure reading                                         | pressure mode selected, open (no current drawn)                      |                      | 30                     | 120                    | LSB  |

| ∆light_touch            | Pressure reading:<br>light-touch - 1.25xEidle <sup>(18)</sup> | pressure mode selected, 2.2k $\Omega$ for light touch, open for idle | 40                   | 250                    |                        | LSB  |

| ADC; notes 11 an        | d 12                                                          |                                                                      | •                    | •                      | •                      | •    |

| RES                     | resolution                                                    |                                                                      | -                    | 10                     | -                      | bit  |