# Product Preview

# Low Voltage PLL Clock Driver

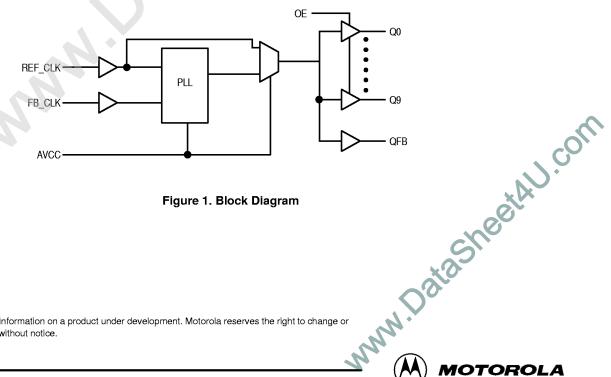

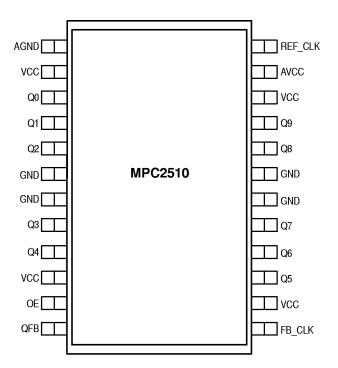

The MPC2510 is a 3.3V compatible, PLL based zero delay buffer targeted for high performance clock tree designs. With 11 outputs at frequencies of up to 125MHz and output skews of 200ps the MPC2510 is ideal for the most demanding clock tree designs. The device employs a fully differential PLL design to minimize cycle-to-cycle and phase jitter. The device is compliant to the 1.2 revision of the PC100 design document.

- Fully Integrated PLL

- Output Frequency up to 125MHz in PLL Mode

- Outputs Disable to a Logic Low

- TQFP Packaging

- 50ps Cycle-to-Cycle Jitter

- On Board Series Damping Resistors

The analog V<sub>CC</sub> pin of the device also serves as a PLL bypass select pin. When driven low the AVCC pin will route the REF\_CLK input around the PLL directly to the outputs. The OE input is a logic enable for all of the outputs except QFB. A low on the OE pin forces Q0-Q9 to a logic low state.

The MPC2510 is fully 3.3V compatible and requires no external loop filter components. All control inputs accept LVCMOS or LVTTL compatible levels while the outputs provide LVCMOS levels with the ability to drive terminated  $50\Omega$  transmission lines. The output impedance of the MPC2510 is  $\approx 40\Omega$  with IV curves that are PC100 Rev 1.2 compliant. The device is packaged in a 24-lead TSSOP package to provide the optimum combination of board density and performance.

# MPC2510

## **LOW VOLTAGE** PLL ZERO DELAY BUFFER

Figure 1. Block Diagram

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

© Motorola, Inc. 1998

11/98

### **FUNCTION TABLES**

| AVCC   | Function                  |

|--------|---------------------------|

| 1<br>0 | PLL Enabled<br>PLL Bypass |

|        |                           |

| OE     | Function                  |

Figure 2. 24-Lead Pinout (Top View)

## **ABSOLUTE MAXIMUM RATINGS\***

| Symbol            | Parameter                 | Min  | Max                   | Unit |

|-------------------|---------------------------|------|-----------------------|------|

| Vcc               | Supply Voltage            | -0.3 | 4.6                   | ٧    |

| V <sub>I</sub>    | Input Voltage             | -0.3 | V <sub>DD</sub> + 0.3 | ٧    |

| ΙΝ                | Input Current             |      | ±20                   | mA   |

| T <sub>Stor</sub> | Storage Temperature Range | -40  | 125                   | °C   |

<sup>\*</sup> Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute-maximum-rated conditions is not implied.

MOTOROLA 2

## DC CHARACTERISTICS (T<sub>A</sub> = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC}$ = $3.3V \pm 5\%$ )

| Symbol          | Characteristic                   | Min | Тур | Max  | Unit | Condition                       |

|-----------------|----------------------------------|-----|-----|------|------|---------------------------------|

| V <sub>IH</sub> | Input HIGH Voltage LVCMOS Inputs | 2.0 |     | 3.6  | ٧    |                                 |

| V <sub>IL</sub> | Input LOW Voltage LVCMOS Inputs  |     |     | 0.8  | ٧    |                                 |

| VOH             | Output HIGH Voltage              | 2.4 |     |      | ٧    | I <sub>OH</sub> = -6mA, Note 1. |

| V <sub>OL</sub> | Output LOW Voltage               |     |     | 0.55 | ٧    | I <sub>OL</sub> = 6mA, Note 1.  |

| IN              | Input Current                    |     |     | ±120 | μΑ   |                                 |

| C <sub>IN</sub> | Input Capacitance                |     |     | 4    | pF   |                                 |

| C <sub>pd</sub> | Power Dissipation Capacitance    |     |     |      | pF   | Per Output                      |

| lcc             | Maximum Quiescent Supply Current |     | 40  |      | mA   | All VCC Pins                    |

| ICCPLL          | Maximum PLL Supply Current       |     | 15  |      | mA   | VCCA Pin Only                   |

<sup>1.</sup> The MPC953 outputs can drive series terminated  $50\Omega$  transmission lines on the incident edge.

## PLL INPUT REFERENCE CHARACTERISTICS ( $T_A = 0$ to $70^{\circ}C$ )

| Symbol           | Characteristic             | Min   | Max | Unit | Condition |

|------------------|----------------------------|-------|-----|------|-----------|

| f <sub>ref</sub> | Reference Input Frequency  | 66.66 | 125 | MHz  |           |

| frefDC           | Reference Input Duty Cycle | 25    | 75  | %    |           |

# AC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C, V<sub>CC</sub> = 3.3V $\pm$ 5%)

| Symbol                          | Characteristic                                             | Min   | Тур | Max   | Unit | Condition                 |

|---------------------------------|------------------------------------------------------------|-------|-----|-------|------|---------------------------|

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                      | 0.10  |     | 1.0   | ns   | 0.8 to 2.0V               |

| t <sub>pw</sub>                 | Output Duty Cycle                                          | 45    | 50  | 55    | %    |                           |

| tsk(O)                          | Output-to-Output Skews                                     |       |     | 200   | ps   |                           |

| f <sub>max</sub>                | Maximum Output Frequency PLL Mode                          | 66.66 |     | 125   | MHz  |                           |

| t <sub>pd</sub> (lock)          | Input to Ext_FB Delay (with PLL Locked) (Including Jitter) | X–150 | Х   | X+150 | ps   | f <sub>ref</sub> = 100MHz |

| <sup>t</sup> PLZ,HZ             | Output Disable Time                                        |       | 7   |       | ns   |                           |

| tPZL                            | Output Enable Time                                         |       | 7   |       | ns   |                           |

| <sup>t</sup> jitter             | Cycle-to-Cycle Jitter (Peak-to-Peak)                       |       | 50  |       | ps   |                           |

| tlock                           | Maximum PLL Lock Time                                      |       |     | 10    | ms   |                           |

3

#### **Power Supply Filtering**

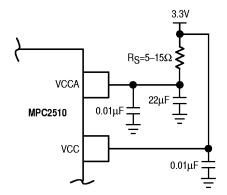

The MPC2510 is a mixed analog/digital product and as such it exhibits some sensitivities that would not necessarily be seen on a fully digital product. Analog circuitry is naturally susceptible to random noise, especially if this noise is seen on the power supply pins. The MPC2510 provides separate power supplies for the output buffers (VCCO) and the phase–locked loop (VCCA) of the device. The purpose of this design technique is to try and isolate the high switching noise digital outputs from the relatively sensitive internal analog phase–locked loop. In a controlled environment such as an evaluation board this level of isolation is sufficient. However, in a digital system environment where it is more difficult to minimize noise on the power supplies a second level of isolation may be required. The simplest form of isolation is a power supply filter on the VCCA pin for the MPC2510.

Figure 3 illustrates a typical power supply filter scheme. The MPC2510 is most susceptible to noise with spectral content in the 1KHz to 10MHz range. Therefore the filter should be designed to target this range. The key parameter that needs to be met in the final filter design is the DC voltage drop that will be seen between the VCC supply and the VCCA pin of the MPC2510. From the data sheet the IVCCA current (the current sourced through the VCCA pin) is typically 15mA (20mA maximum), assuming that a minimum of 3.0V must be maintained on the VCCA pin very little DC voltage drop can be tolerated when a 3.3V V<sub>CC</sub> supply is used. The resistor shown in Figure 3 must have a resistance of  $10-15\Omega$  to meet the voltage drop criteria. The RC filter pictured will provide a broadband filter with approximately 100:1 attenuation for noise whose spectral content is above 20KHz. As the noise frequency crosses the series resonant point of an individual

capacitor it's overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL. It is recommended that the user start with an  $8{\text -}10\Omega$  resistor to avoid potential  $V_{CC}$  drop problems and only move to the higher value resistors when a higher level of attenuation is shown to be needed.

Figure 3. Power Supply Filter

Although the MPC2510 has several design features to minimize the susceptibility to power supply noise (isolated power and grounds and fully differential PLL) there still may be applications in which overall performance is being degraded due to system power supply noise. The power supply filter schemes discussed in this section should be adequate to eliminate power supply noise related problems in most designs.

MOTOROLA 4

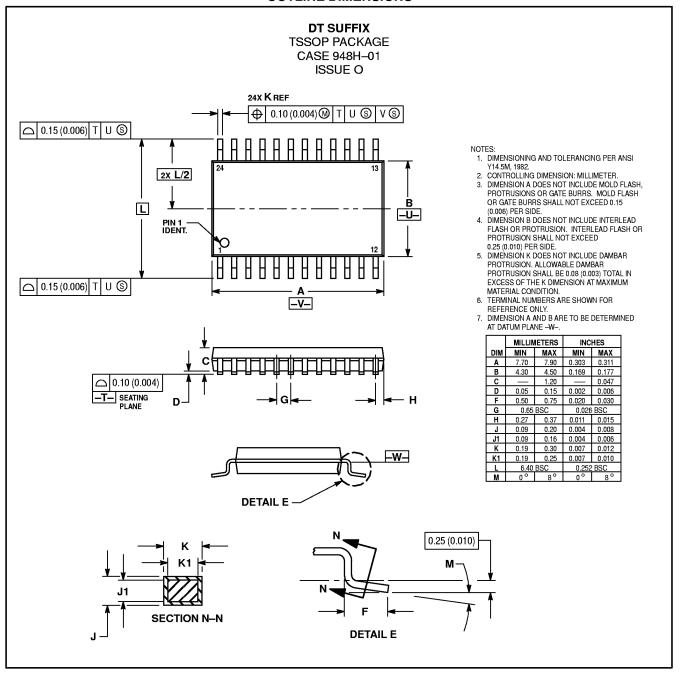

### **OUTLINE DIMENSIONS**