# DP8344B Biphase Communications Processor—BCP®

### **General Description**

The DP8344B BCP is a communications processor designed to efficiently process IBM® 3270, 3299 and 5250 communications protocols. A general purpose 8-bit protocol is also supported.

The BCP integrates a 20 MHz 8-bit Harvard architecture RISC processor, and an intelligent, software-configurable transceiver on the same low power microCMOS chip. The transceiver is capable of operating without significant processor interaction, releasing processor power for other tasks. Fast and flexible interrupt and subroutine capabilities with on-chip stacks make this power readily available.

The transceiver is mapped into the processor's register space, communicating with the processor via an asynchronous interface which enables both sections of the chip to run from different clock sources. The transmitter and receiver run at the same basic clock frequency although the receiver extracts a clock from the incoming data stream to ensure timing accuracy.

The BCP is designed to stand alone and is capable of implementing a complete communications interface, using the processor's spare power to control the complete system. Alternatively, the BCP can be interfaced to another processor with an on-chip interface controller arbitrating access to data memory. Access to program memory is also possible, providing the ability to download BCP code.

A simple line interface connects the BCP to the communications line. The receiver includes an on-chip analog comparator, suitable for use in a transformer-coupled environment,

although a TTL-level serial input is also provided for applications where an external comparator is preferred.

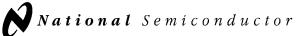

A typical system is shown below. Both coax and twinax line interfaces are shown, as well as an example of the (optional) remote processor interface.

### **Features**

- Transceiver

- Software configurable for 3270, 3299, 5250 and general 8-bit protocols

- Fully registered status and control

- On-chip analog line receiver

#### Processor

- 20 MHz clock (50 ns T-states)

- Max. instruction cycle: 200 ns

- 33 instruction types (50 total opcodes)

- ALU and barrel shifter

- 64k x 8 data memory address range

- 64k x 16 program memory address range

- (note: typical system requires <2k program memory) Programmable wait states

- Soft-loadable program memory

- Interrupt and subroutine capability

- Stand alone or host operation Flexible bus interface with on-chip arbitration logic

General

- Low power microCMOS; typ. I<sub>CC</sub> = 25 mA at 20 MHz

- 84-pin plastic leaded chip carrier (PLCC) package

© 1995 National Semiconductor Corporation TL/F/9336 RRD-B30M105/Printed in U. S. A

November 1991

The DP8344B is an enhanced version of the DP8344A, exhibiting improved switching performance and additional functionality. The device has been been characterized in a number of applications and found to be a compatible replacement for the DP8344A. Differences between the DP8344A and DP8344B are noted by shading of the text on the pages of this data sheet. For more information, refer to Section 6.6.

Note: In this document [XXX] denotes a control or status bit in a register, {YYY} denotes a register.

### **Table of Contents**

### 1.0 COMMUNICATIONS PROCESSOR OVERVIEW

- 1.1 Communications Protocols

- 1.2 Internal Architecture Overview

- 1.3 Timing Overview

- 1.4 Data Flow

- 1.5 Remote Interface Overview

#### 2.0 CPU DESCRIPTION

- 2.1 CPU Architectural Description

- 2.1.1 Register Set

- 2.1.1.1 Banked Registers

- 2.1.1.2 Timing Control Registers

- 2.1.1.3 Interrupt Control Registers

- 2.1.1.4 Timer Registers

- 2.1.1.5 Transceiver Registers

- 2.1.1.6 Condition Code/Remote Handshaking Register

- 2.1.1.7 Index Registers

- 2.1.1.8 Stack Registers

- 2.1.2 Timer

- 2.1.2.1 Timer Operation

- 2.1.3 Instruction Set

- 2.1.3.1 Harvard Architecture Implications

- 2.1.3.2 Addressing Modes

- 2.1.3.3 Instruction Set Overview

### 2.2 Functional Description

- 2.2.1 ALU

- 2.2.2 Timing

- 2.2.3 Interrupts

- 2.2.4 Oscillator

3.1.1.1 IBM 3270 3.1.1.2 IBM 3299

3.0 TRANSCEIVER

3.1.1 Protocols

- 3.1.1.3 IBM 5250

- 3.1.1.4 General Purpose 8-Bit

- 3.2 Transceiver Functional Description

3.1 Transceiver Architectural Description

- 3.2.1 Transmitter

- 3.2.2 Receiver

- 3.2.3 Transceiver Interrupts

- 3.2.4 Protocol Modes

- 3.2.5 Line Interface

- 3.2.5.1 3270 Line Interface

- 3.2.5.2 5250 Line Interface

# 4.0 REMOTE INTERFACE AND ARBITRATION SYSTEM (RIAS)

- 4.1 RIAS Architectural Description

- 4.1.1 Remote Arbitration Phases

- 4.1.2 Access Types

- 4.1.3 Interface Modes

- 4.1.4 Execution Control

- 4.2 RIAS Functional Description

- 4.2.1 Buffered Read

- 4.2.2 Latched Read

- 4.2.3 Slow Buffered Write

- 4.2.4 Fast Buffered Write

- 4.2.5 Latched Write

- 4.2.6 Remote Rest Time

### Table of Contents (Continued)

#### 5.0 DEVICE SPECIFICATIONS

5.1 Pin Description

- 5.1.1 Timing/Control Signals

- 5.1.2 Instruction Memory Interface

- 5.1.3 Data Memory Interface

- 5.1.4 Transceiver Interface

- 5.1.5 Remote Interface

- 5.1.6 External Interrupts

- 5.2 Absolute Maximum Ratings

- 5.3 Operating Conditions

- 5.4 Electrical Characteristics

- 5.5 Switching Characteristics

- 5.5.1 Definitions

- 5.5.2 Timing Tables and Figures

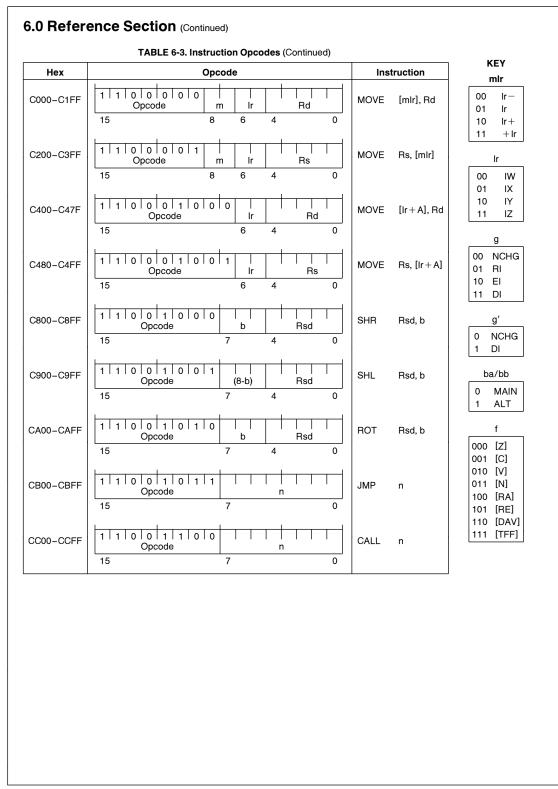

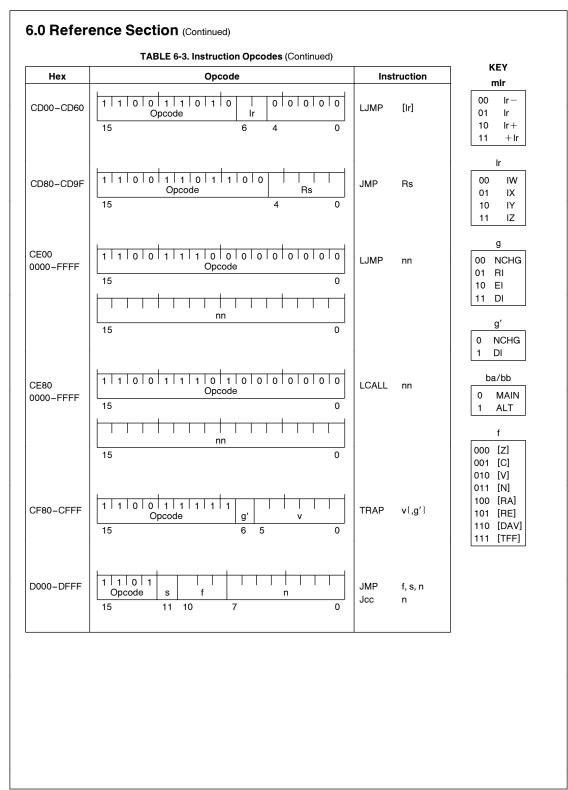

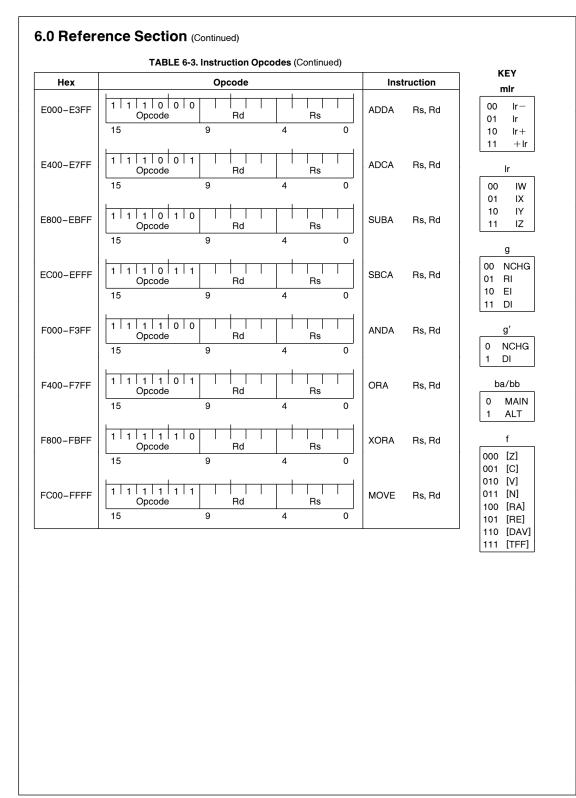

#### 6.0 REFERENCE SECTION

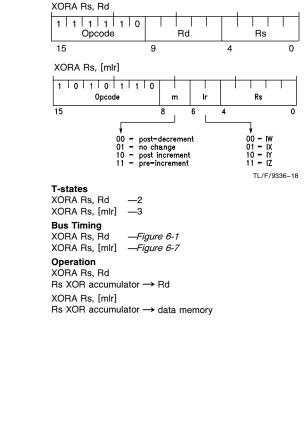

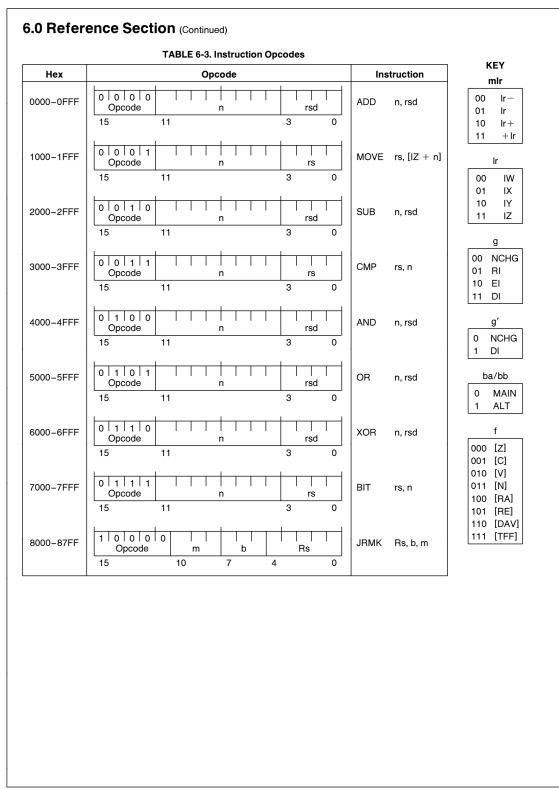

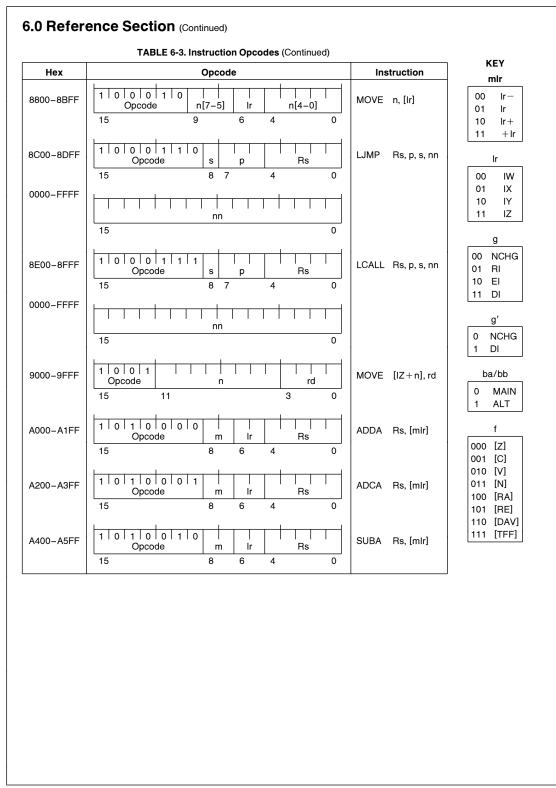

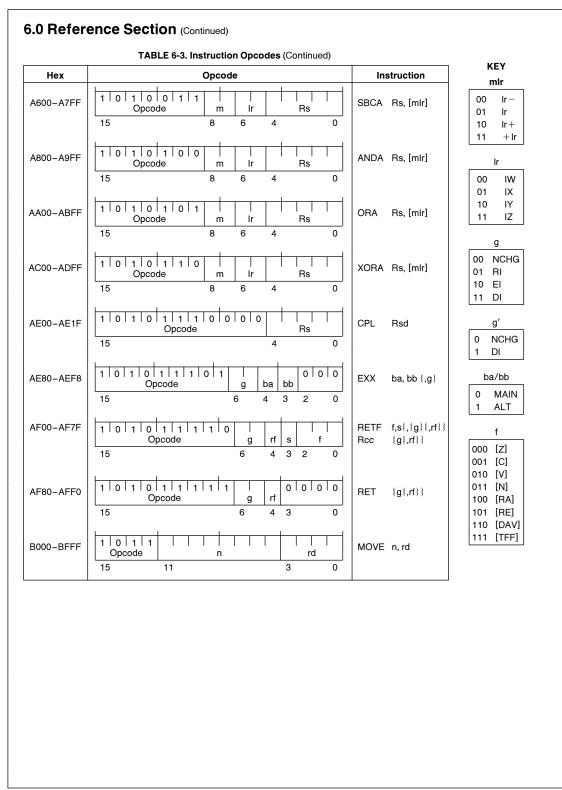

- 6.1 Instruction Set Reference

- 6.2 Register Set Reference

- 6.2.1 Bit Index

- 6.2.2 Register Description

- 6.2.3 Bit Definition Tables 6.2.3.1 Processor

- 6.2.3.2 Transceiver

- 6.3 Remote Interface Reference

- 6.4 Development Tools

- 6.4.1 Assembler System

- 6.4.2 Development Kit

- 6.4.3 Multi-Protocol Adapter Design/Evaluation Kit

- 6.4.4 Inverse Assembler

- 6.5 3rd Party Suppliers

- 6.5.1 Crystal

- 6.5.2 System Development Tools

- 6.6 DP8344A Compatibility Guide

- 6.6.1 CPU Timing Changes

- 6.6.2 Additional Functionality

- 6.6.2.1 4 T-state Read

- 6.6.2.2 A/AD Reset State 6.6.2.3 RIC

- 6.6.2.4 Transceiver

- 6.7 Reported Bugs

- 6.7.1 History

- 6.7.2 LJMP, LCALL Address Decode 6.7.2.1 Suggested Work-around

- 6.8 Glossary

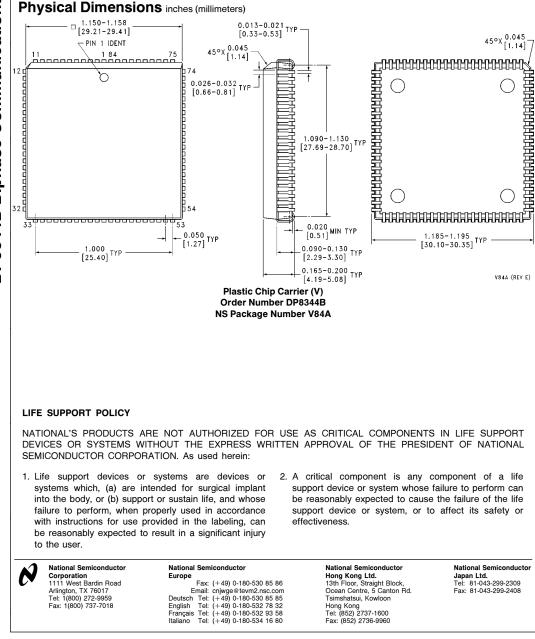

- 6.9 Physical Dimensions

## **List of Illustrations**

| Block Diagram of Typical BCP System1                        |

|-------------------------------------------------------------|

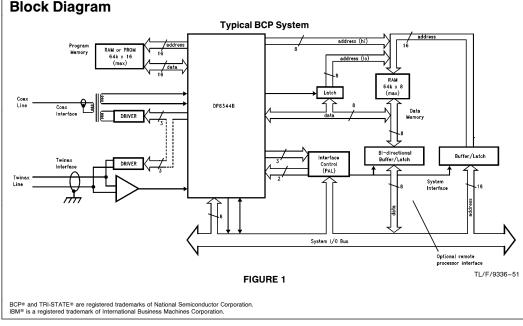

| Biphase Encoding                                            |

| IBM 3270 Message Format                                     |

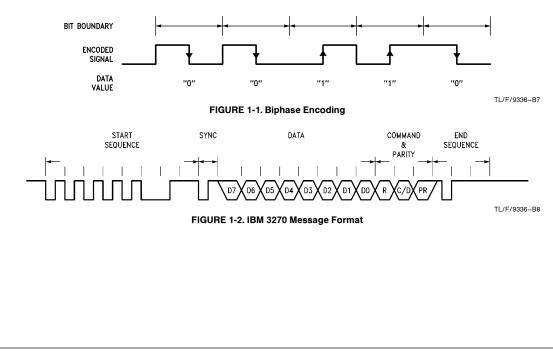

| Simplified Block Diagram                                    |

| Memory Configuration                                        |

| Effect of Memory Wait States on Timing                      |

| Register to Register Internal Data Flow                     |

| Data Memory WRITE Data Flow                                 |

| Data Memory READ Data Flow                                  |

| WRITE to Transmitter Data Flow                              |

| READ from Receiver Data Flow                                |

| Load Immediate Data Data Flow                               |

| Basic Remote Interface                                      |

|                                                             |

| Register Map                                                |

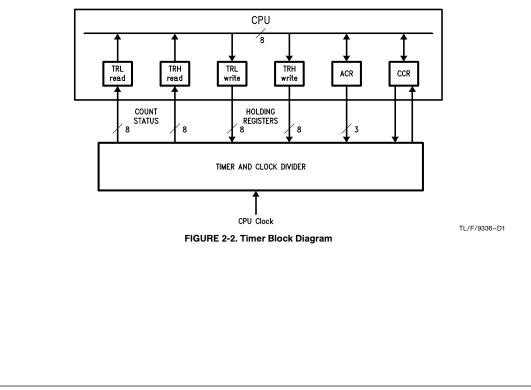

| Timer Block Diagram                                         |

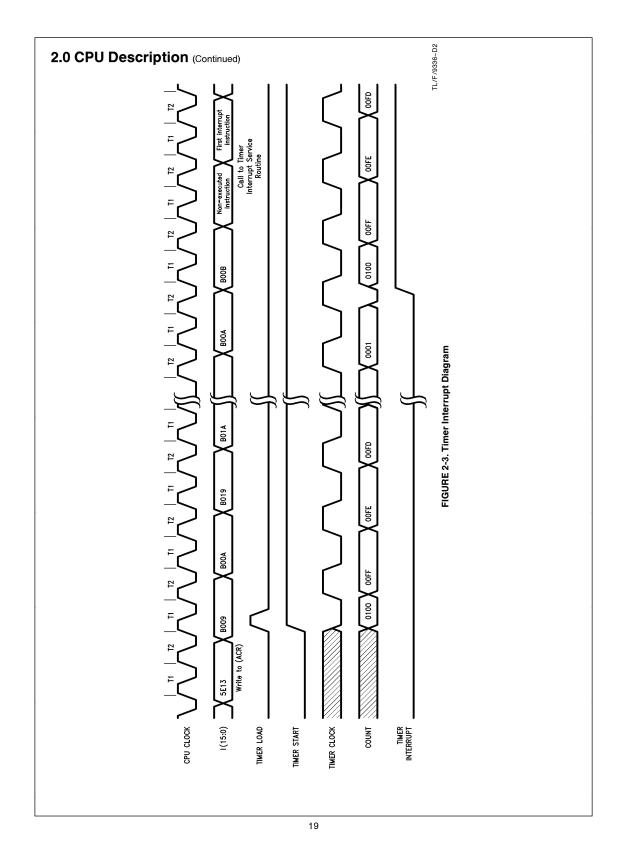

| Timer Interrupt Diagram                                     |

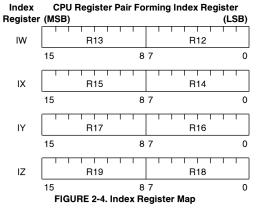

| Index Register Map                                          |

| Coding Examples of Equivalent Conditional Jump Instructions |

| JRMK Instruction Example                                    |

| Condition Code Register ALU Flags                           |

| Carry and Overflow Calculations                             |

| Shifts' Effect on Carry                                     |

| Rotates' Effect on Carry                                    |

| Multi-Byte Arithmetic Instruction Sequences                 |

| CPU-CLK Synchronization with X1                             |

|                                                             |

| Changing from OCLK/2 to OCLK                                |

| Two T-state Instruction                                     |

| Three T-state Instruction                                   |

| Three T-state Data Memory Write Instruction                 |

| Three T-state Data Memory Read Instruction                  |

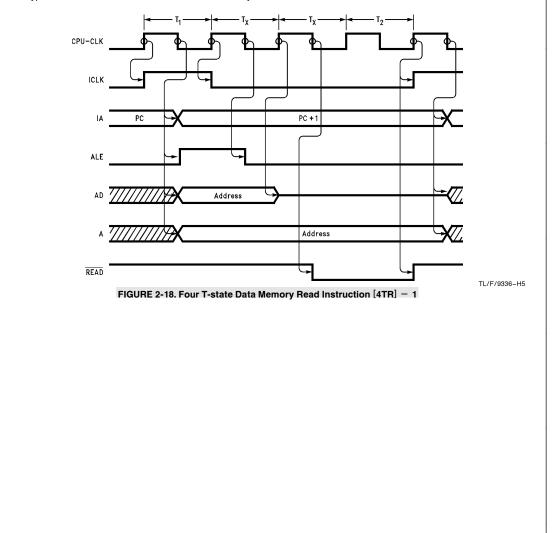

| Four T-state Data Memory Read Instruction                   |

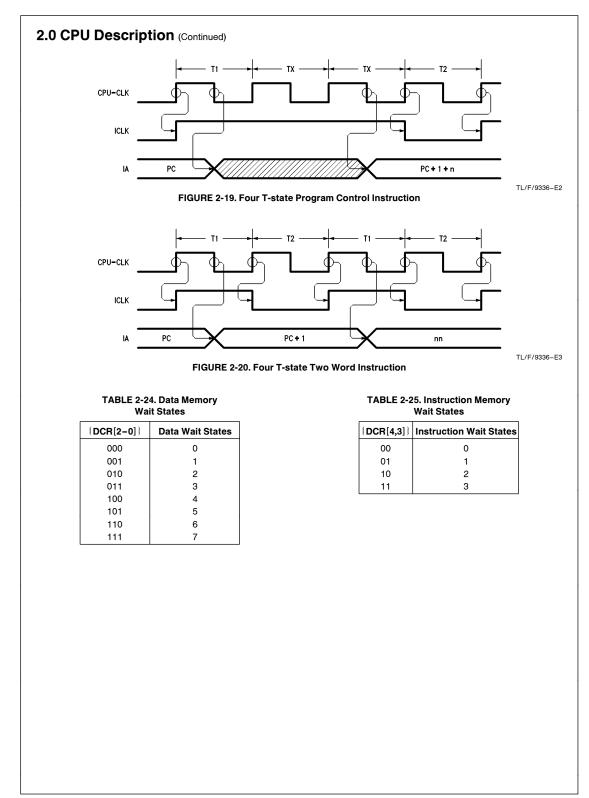

| Four T-state Program Control Instruction                    |

| Four T-state Two Word Instruction                           |

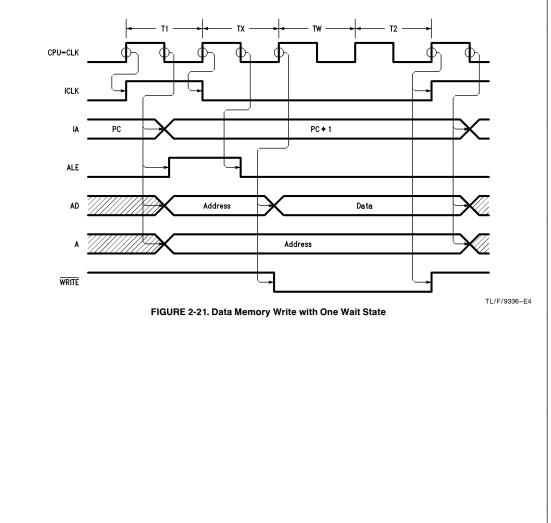

| Data Memory Write with One Wait State                       |

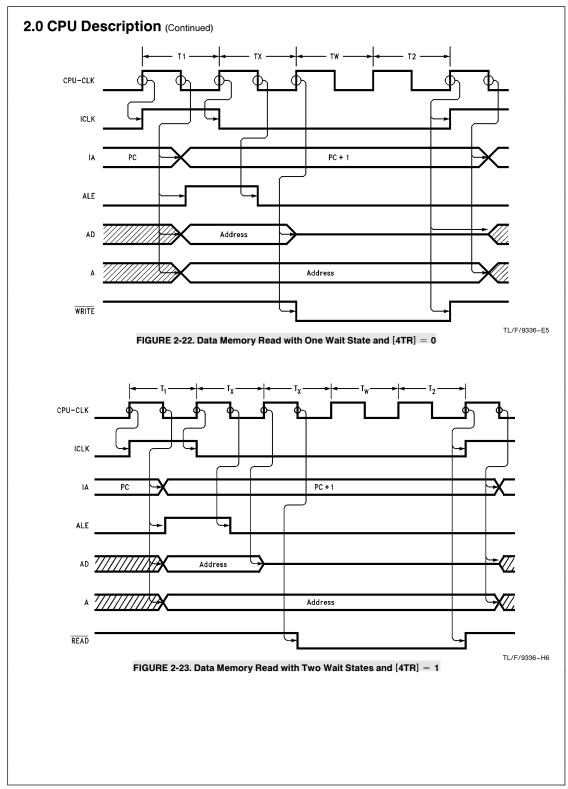

| Data Memory Read with One Wait State                        |

| Data Memory Read with Two Wait States                       |

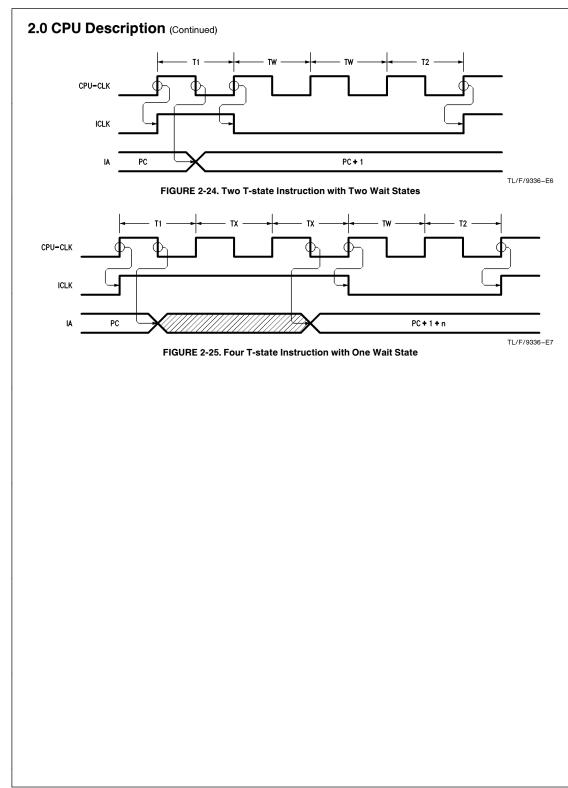

| Two T-state Instruction with Two Wait States                |

| Four T-state Instruction with One Wait State                |

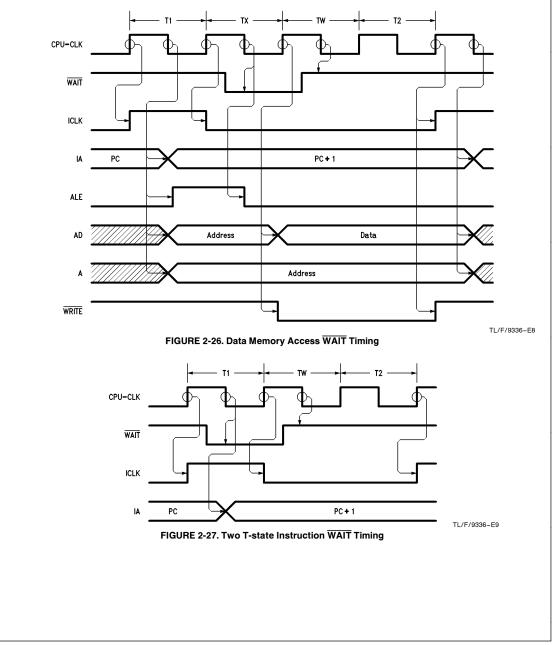

| Data Memory Access Wait Timing                              |

| Two T-state Instruction WAIT Timing2-27                     |

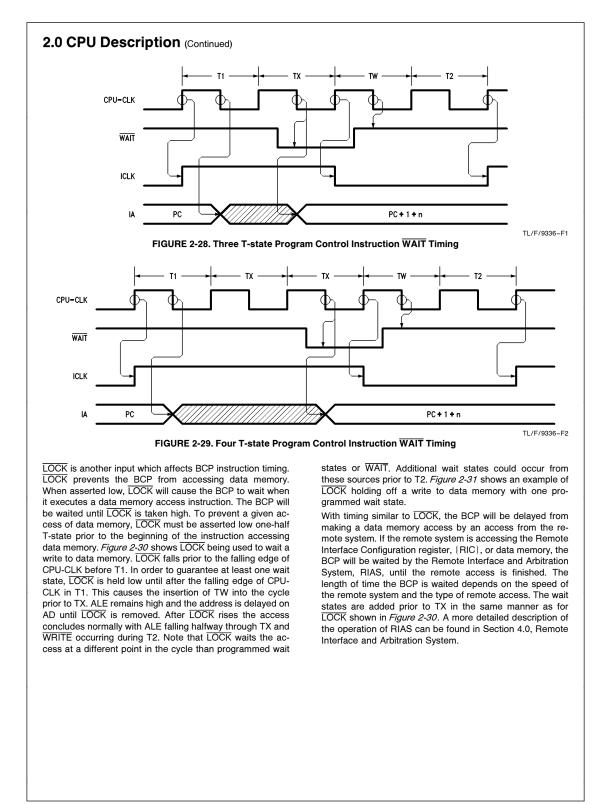

| Three T-state Program Control Instruction WAIT Timing       |

| Four T-state Program Control Instruction WAIT Timing        |

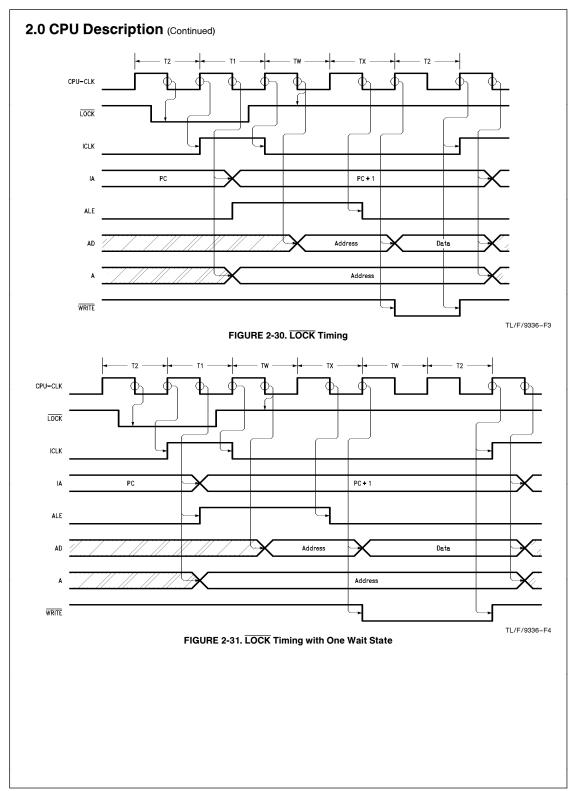

| LOCK Timing                                                 |

| LOCK Timing with One Wait State                             |

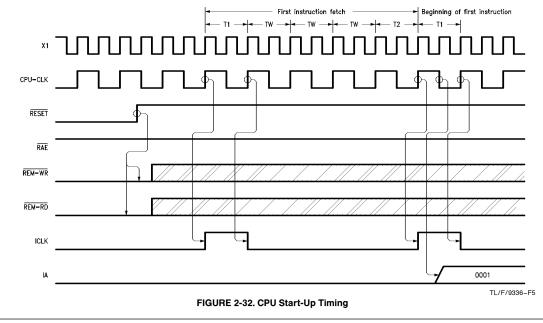

| CPU Start-Up Timing                                         |

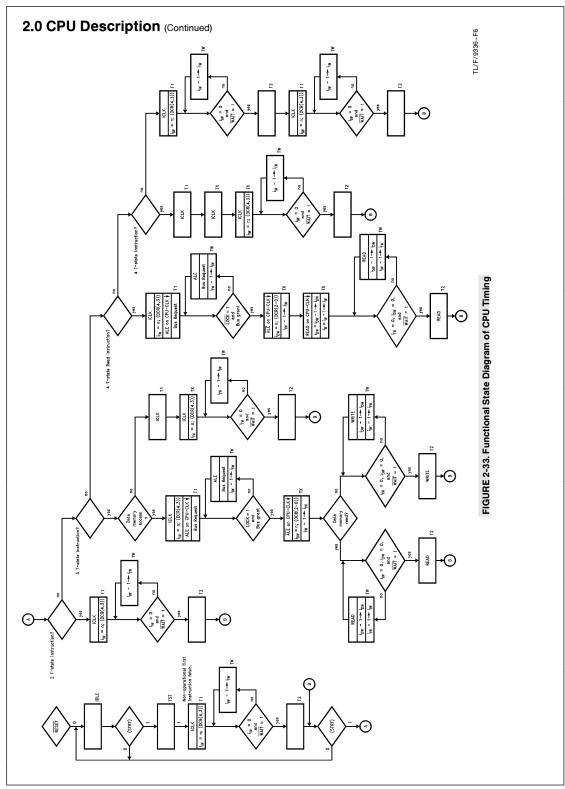

| Functional State Diagram of CPU Timing                      |

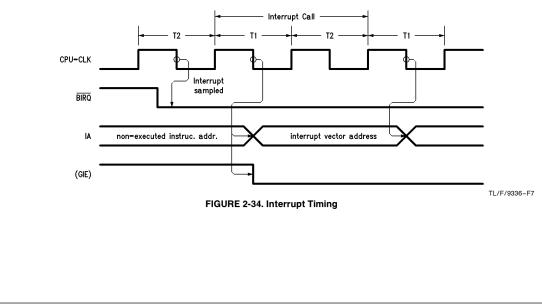

| Interrupt Timing                                            |

| DP8344B Operation with Crystal2-35                          |

| DP8344B Operation with External Clock2-36                   |

|                                                             |

## List of Illustrations (Continued)

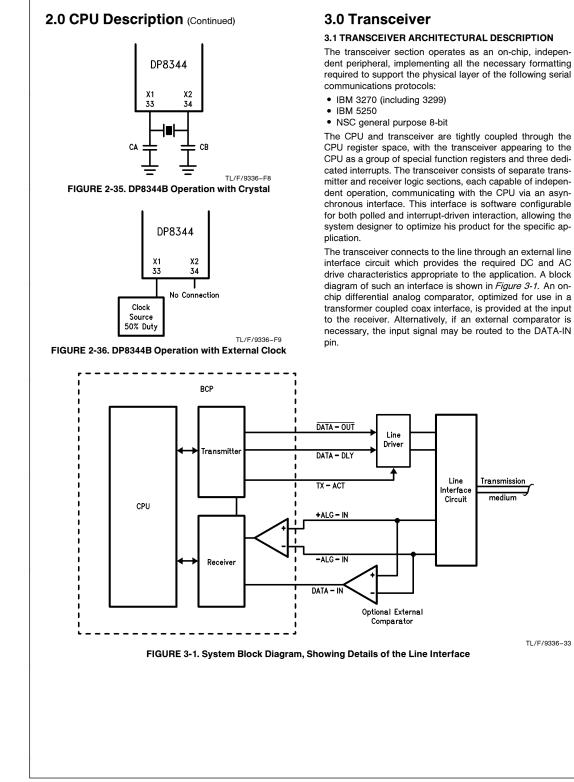

| System Block Diagram, Showing Details of Line Interface      |

|--------------------------------------------------------------|

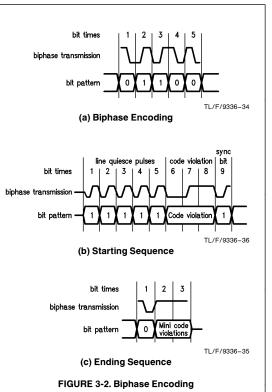

| Biphase Encoding                                             |

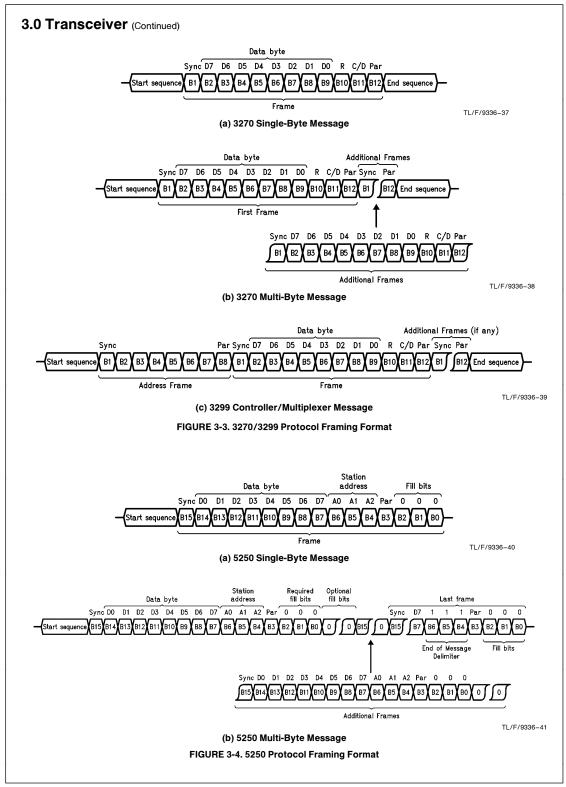

| 3270/3299 Protocol Framing Format                            |

| 5250 Protocol Framing Format                                 |

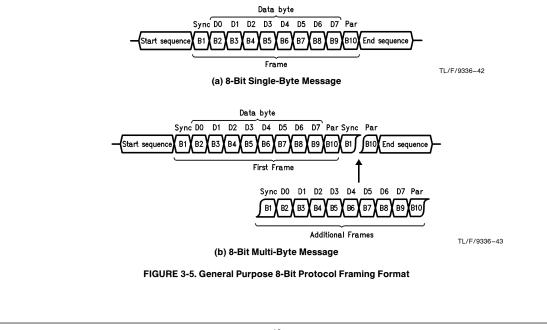

| General Purpose 8-Bit Protocol Framing Format                |

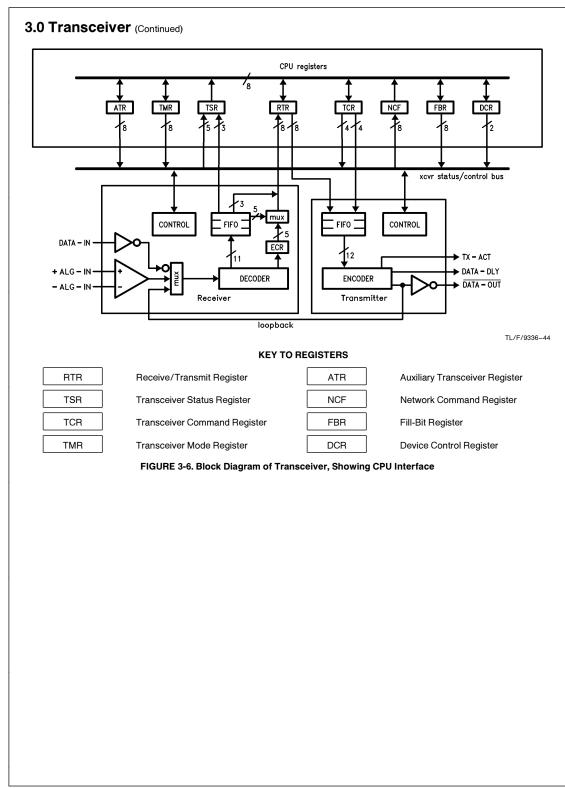

| Block Diagram of Transceiver, Showing CPU Interface          |

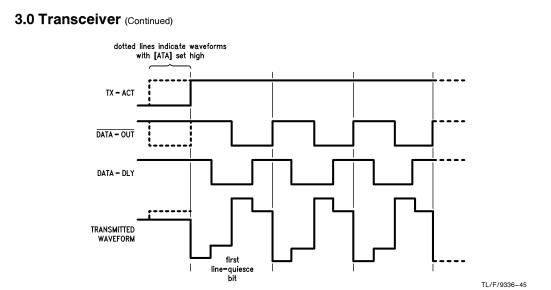

| Transmitter Output                                           |

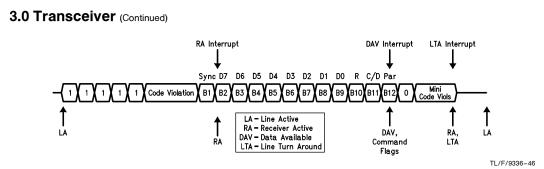

| Timing of Receiver Flags Relative to Incoming Data           |

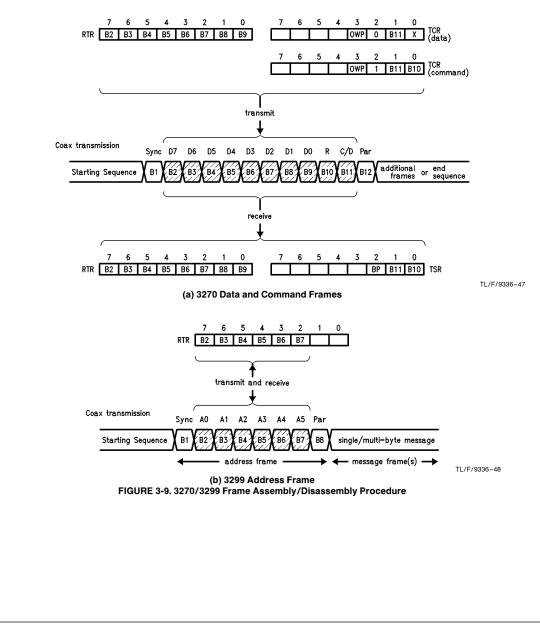

| 3270, 3299 Frame Assembly/Disassembly Description            |

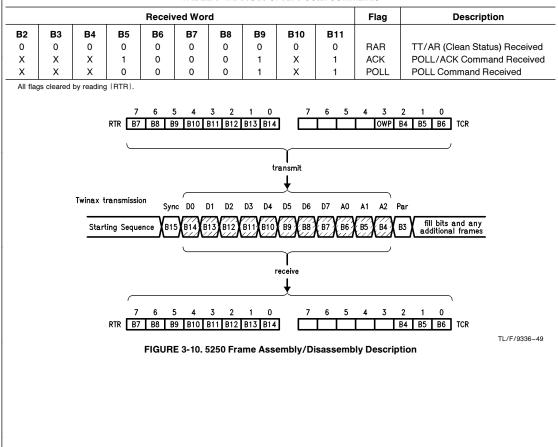

| 5250 Frame Assembly/Disassembly Description                  |

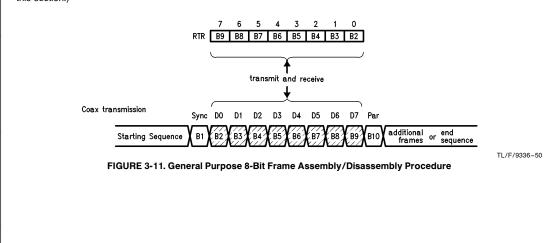

| General Purpose 8-Bit Frame Assembly/Disassembly Description |

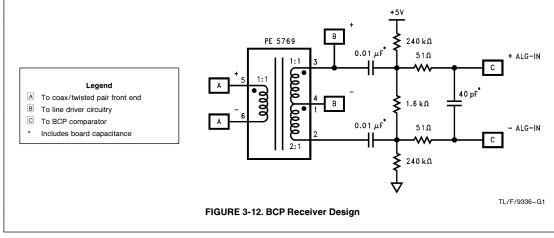

| BCP Receiver Design                                          |

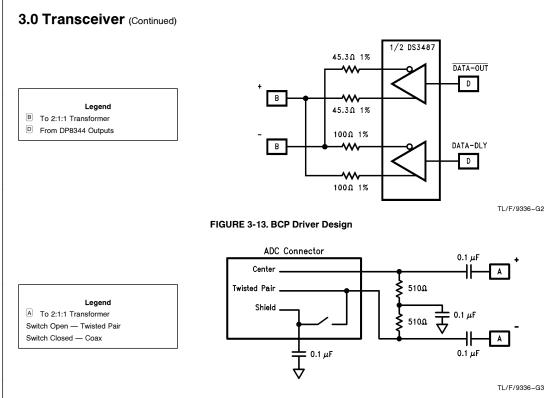

| BCP Driver Design                                            |

| BCP Coax/Twisted Pair Front End                              |

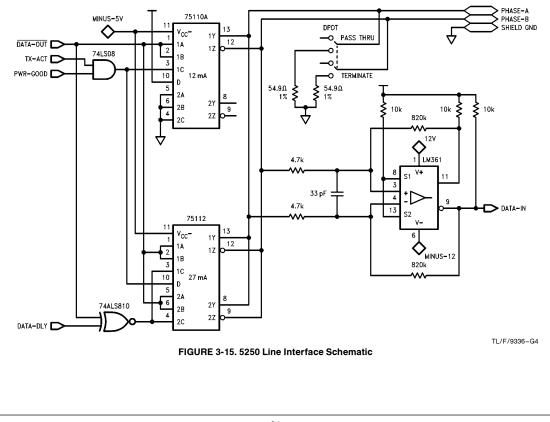

| 5250 Line Interface Schematic                                |

|                                                              |

| Remote Interface Processor                                   |

| Remote Interface Control Register                            |

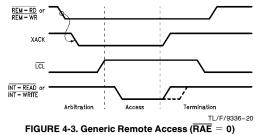

| Generic Remote Access                                        |

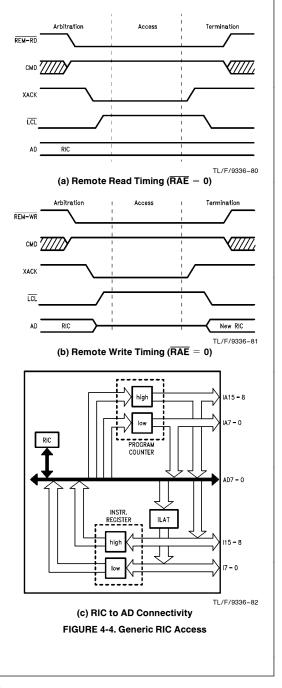

| Generic RIC Access                                           |

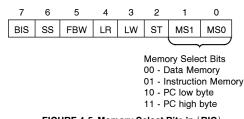

| Memory Select Bits in {RIC}                                  |

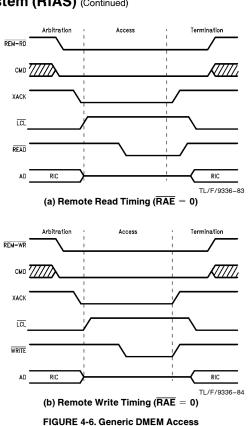

| Generic DMEM Access                                          |

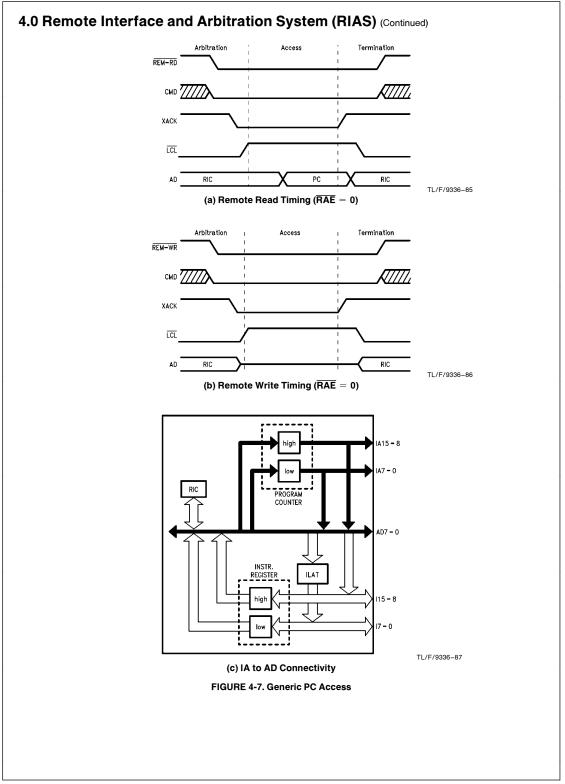

| Generic PC Access                                            |

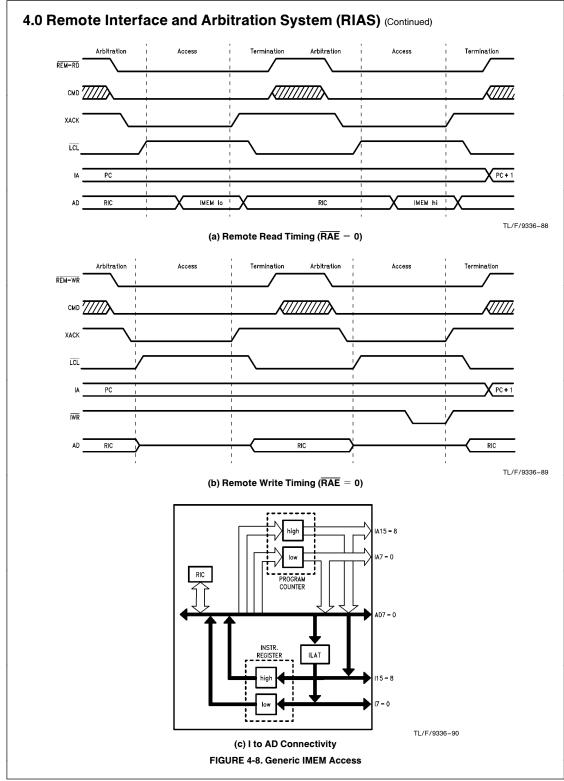

| Generic IMEM Access                                          |

| Read from Remote Processor                                   |

| Buffered Write from Remote Processor                         |

| Latched Write from Remote Processor                          |

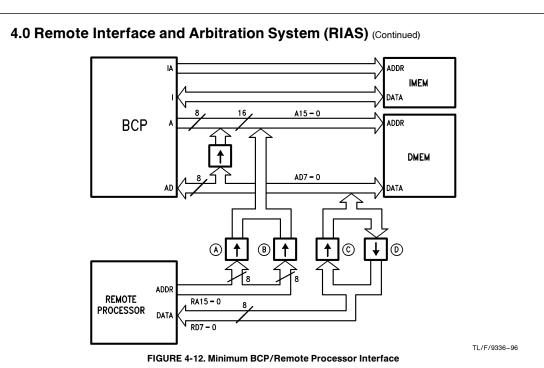

| Minimum BCP/Remote Processor Interface                       |

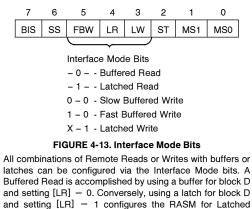

| Interface Mode Bits                                          |

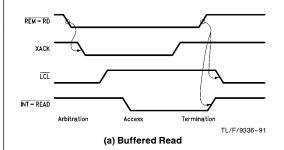

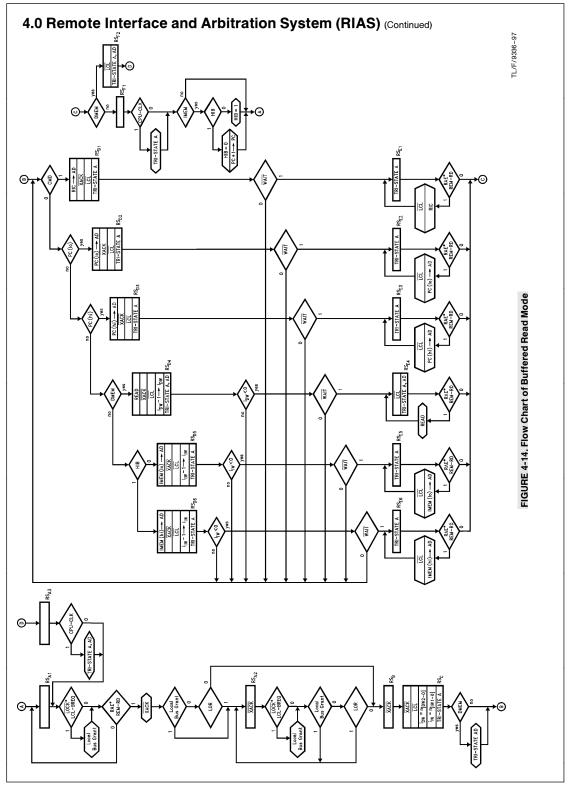

| Flow Chart of Buffered Read Mode                             |

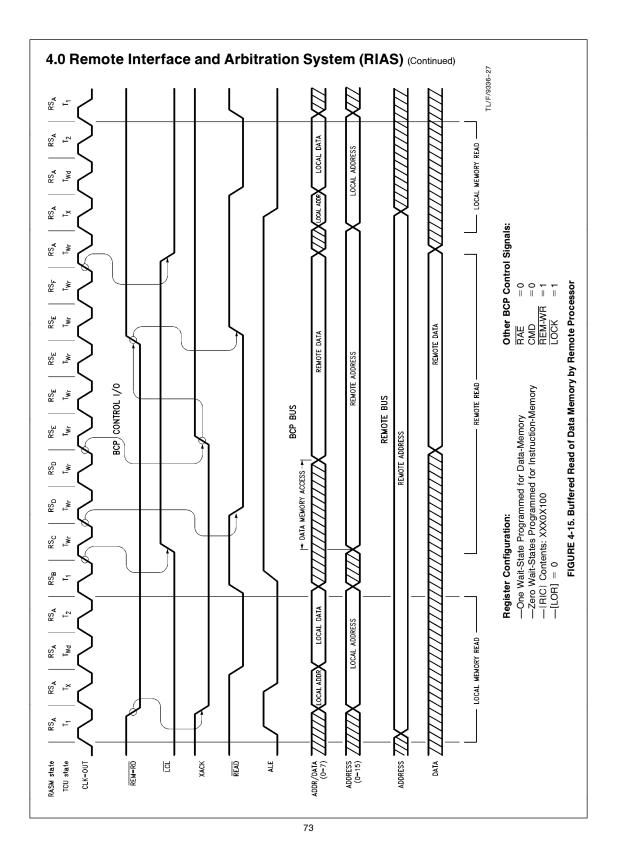

| Buffered Read of Data Memory by Remote Processor             |

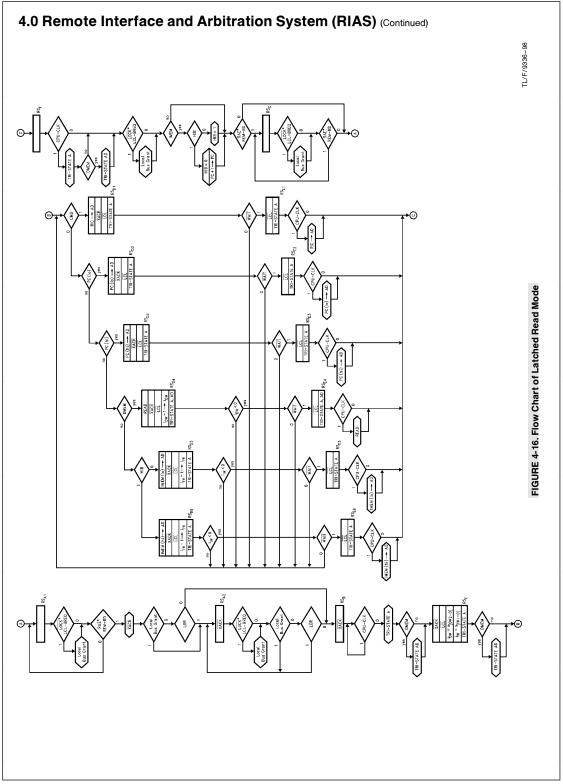

| Flow Chart of Latched Read Mode                              |

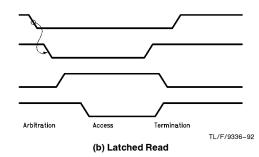

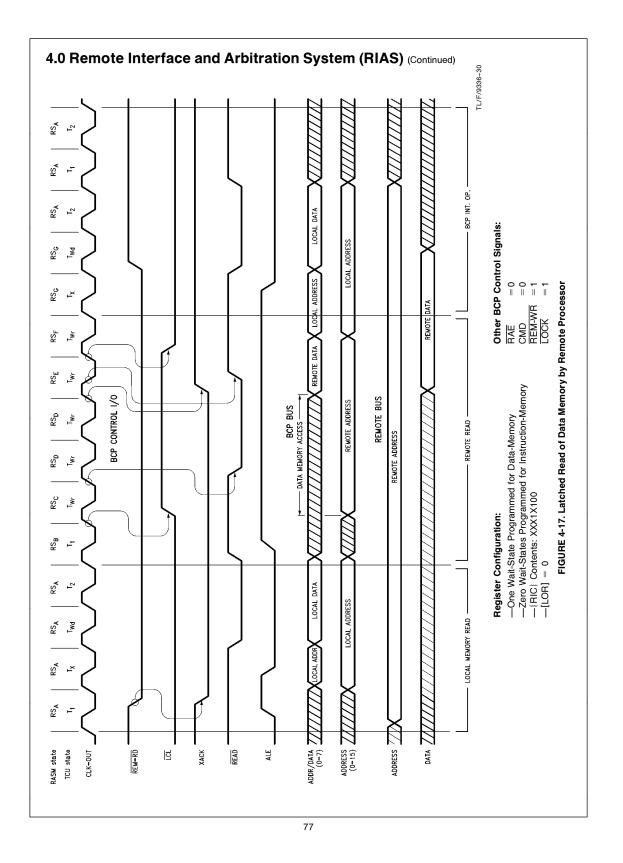

| Latched Read of Data Memory by Remote Processor              |

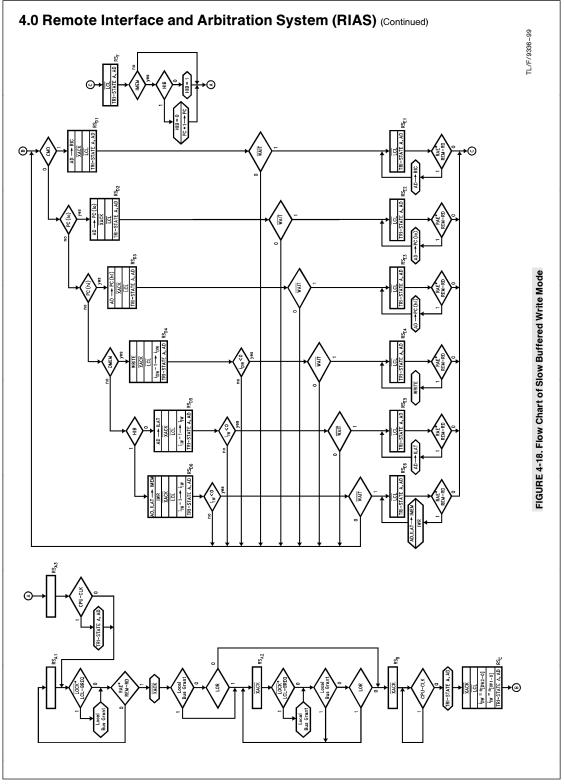

| Flow Chart of Slow Buffered Write Mode                       |

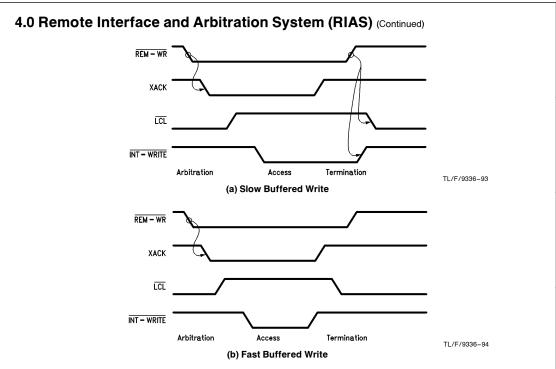

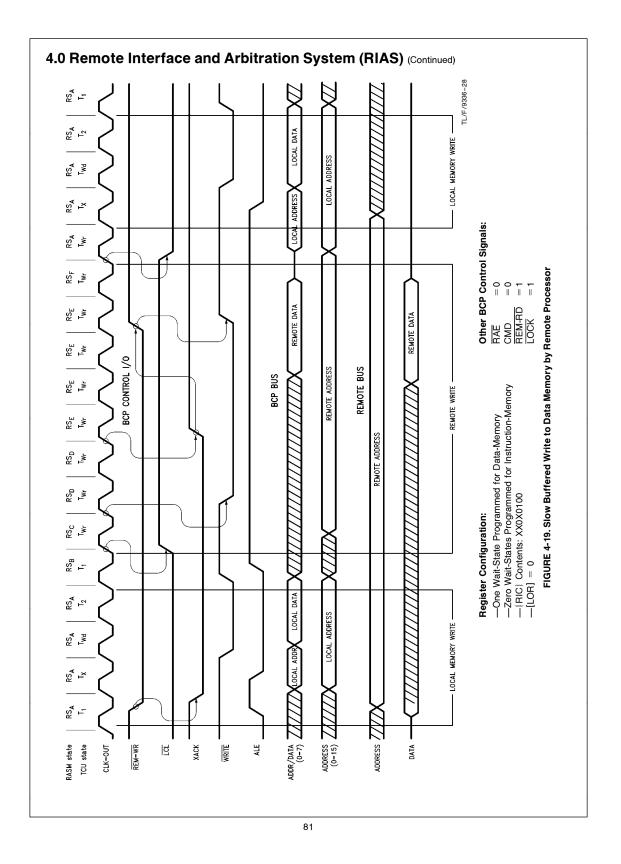

| Slow Buffered Write to Data Memory by Remote Processor       |

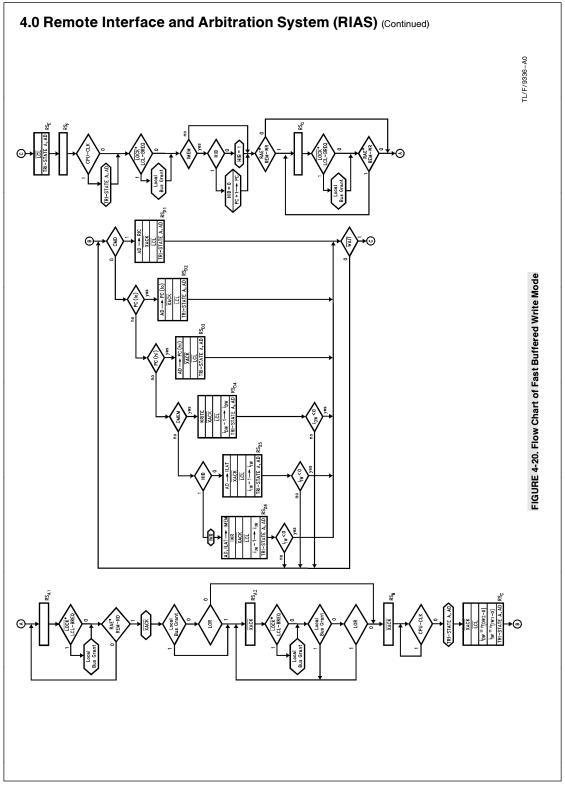

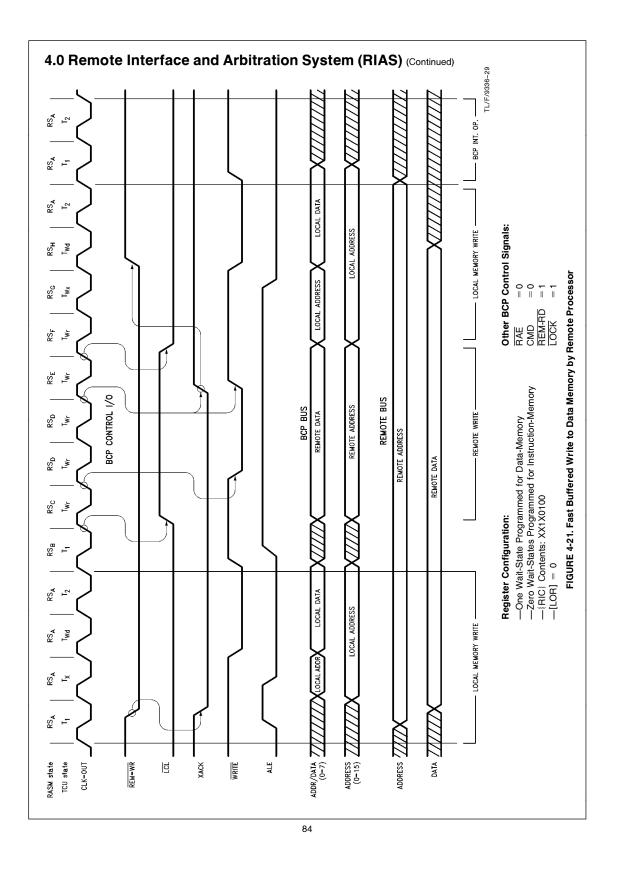

| Flow Chart of Fast Buffered Write Mode                       |

| Fast Buffered Write to Data Memory by Remote Processor       |

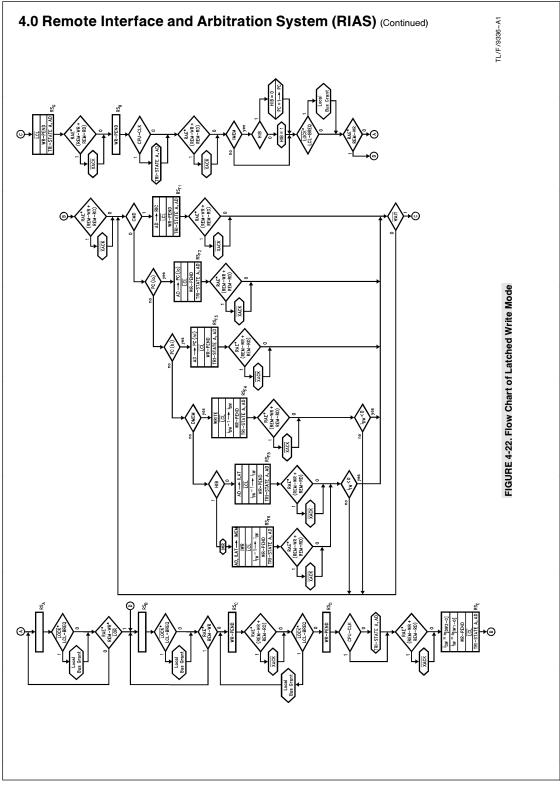

| Flow Chart of Latched Write Mode                             |

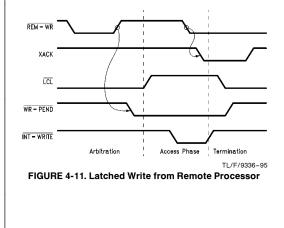

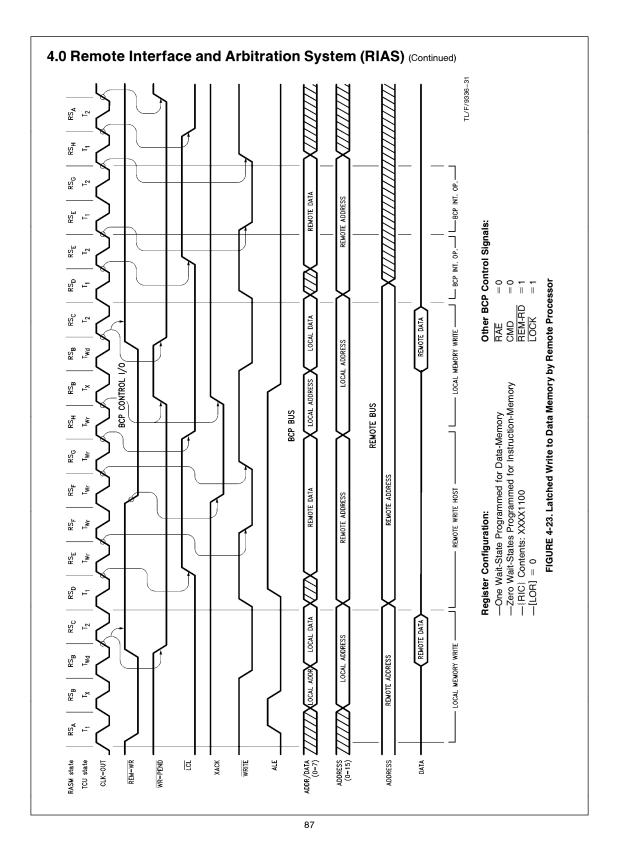

| Latched Write to Data Memory by Remote Processor             |

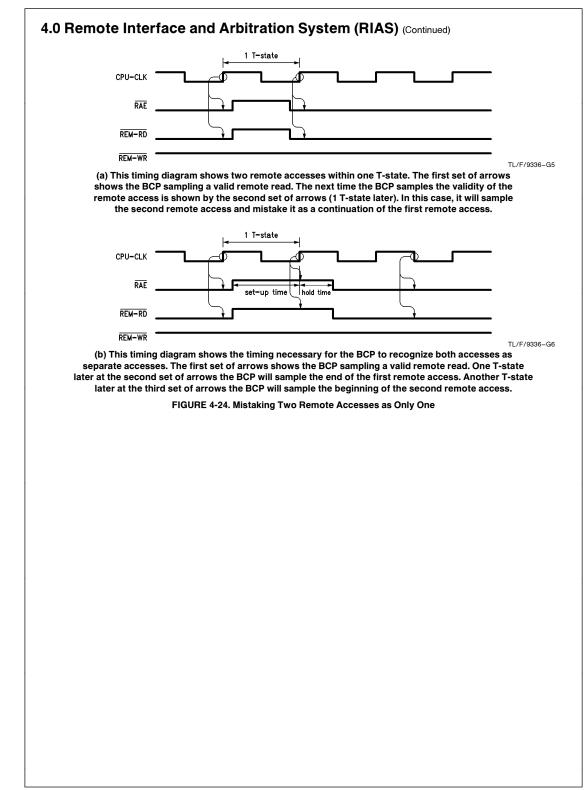

| Mistaking Two Remote Accesses as Only One                    |

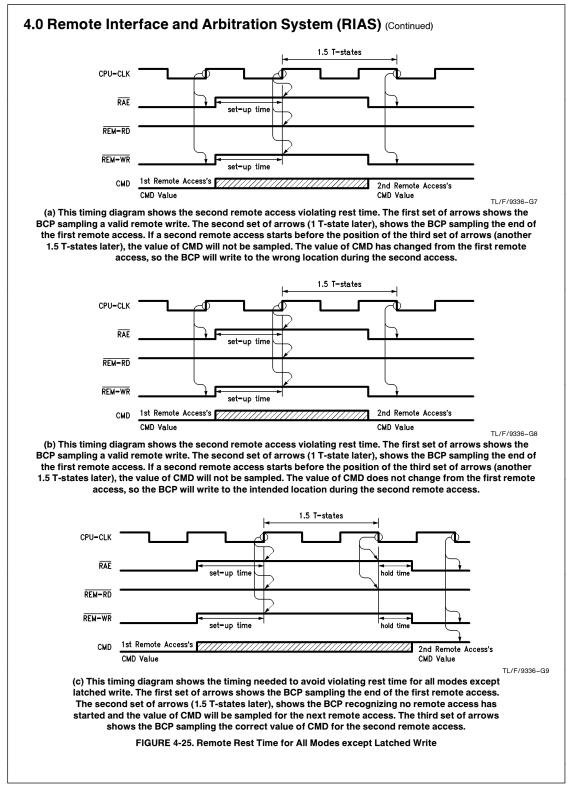

| Remote Rest Time for All Modes Except Latched Write          |

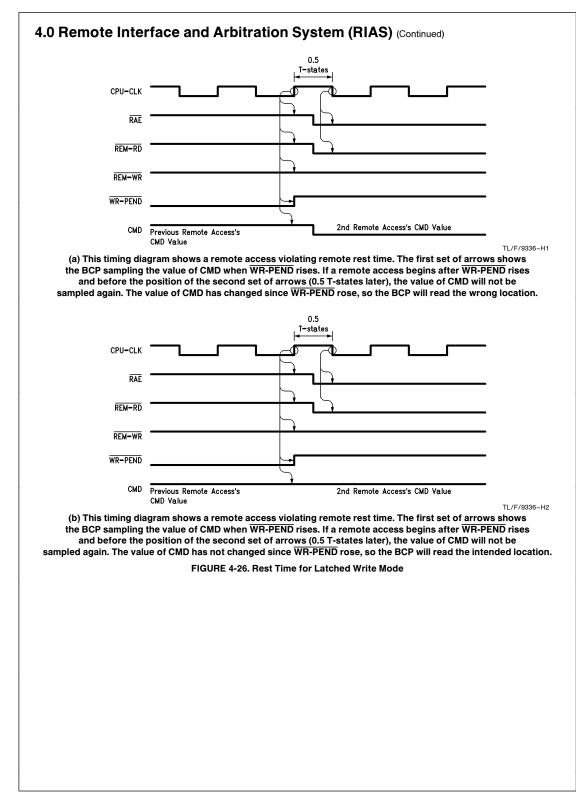

| Rest Time for Latched Write Mode    4-26                     |

|                                                              |

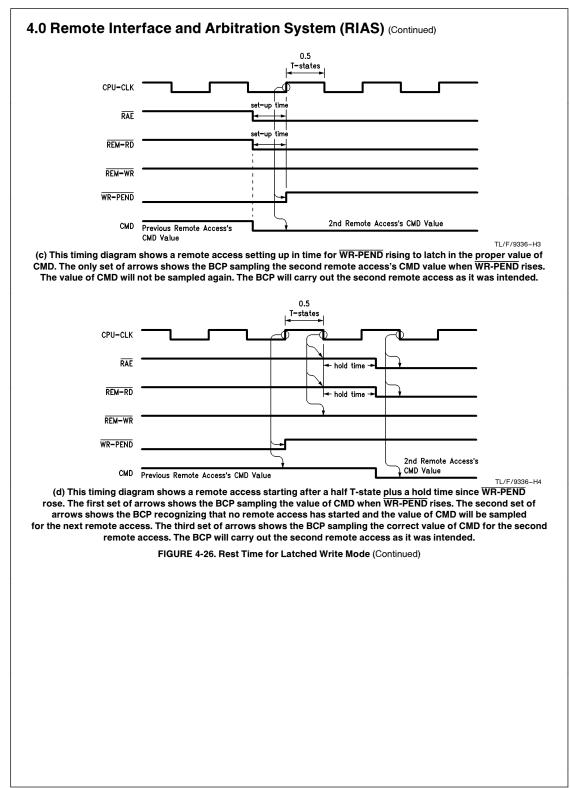

| DP8344B Top View                                             |

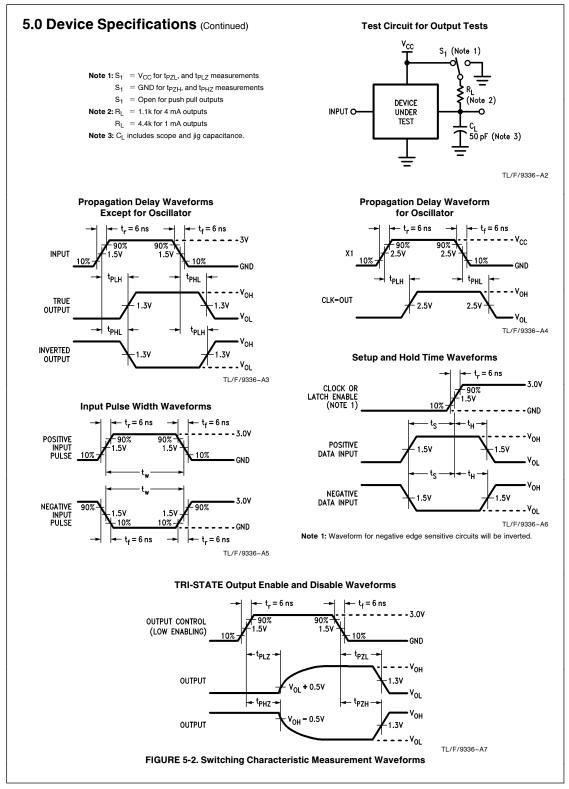

| Switching Characteristic Measurement Waveforms               |

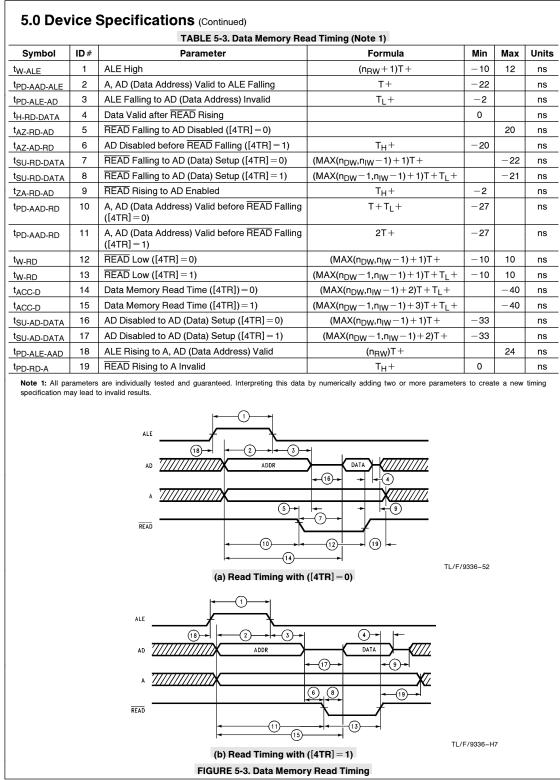

| Data Memory Read Timing                                      |

| Data Memory Write Timing                                     |

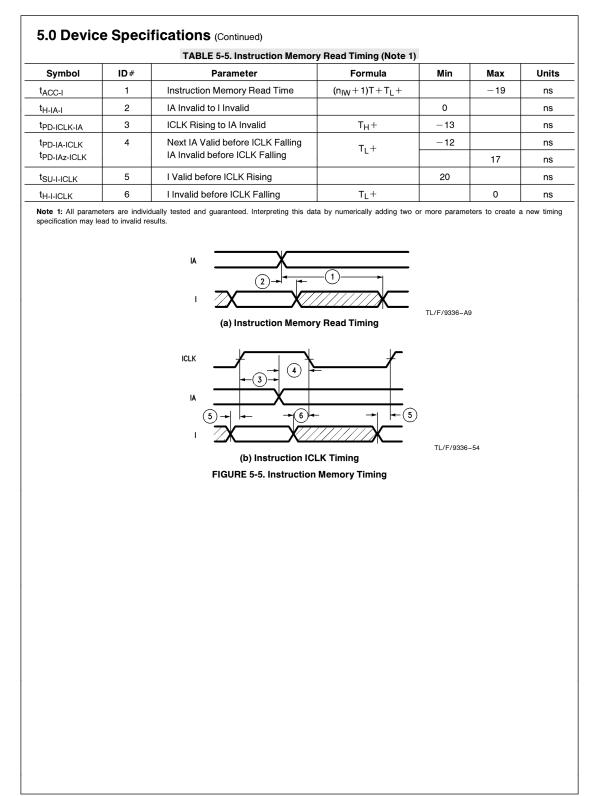

| Instruction Memory Timing                                    |

| Clock Timing                                                 |

|                                                              |

|                                                              |

## List of Illustrations (Continued)

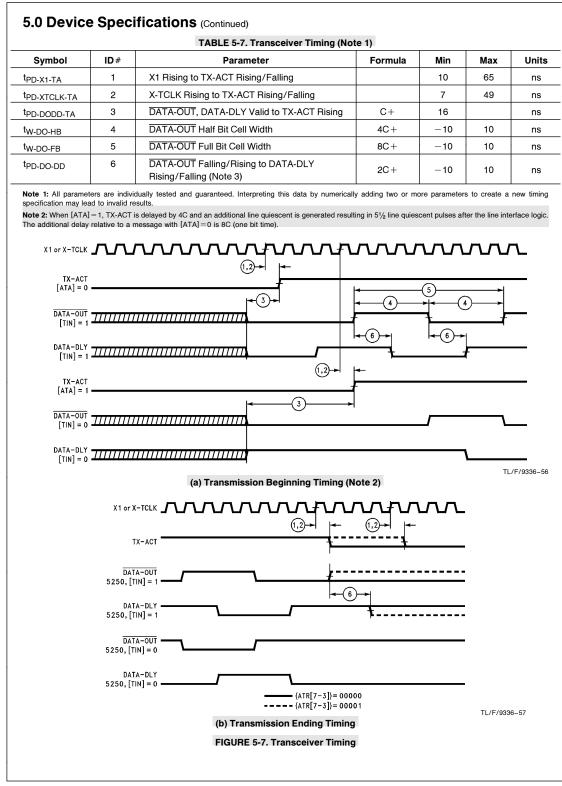

| Transceiver Timing                    |

|---------------------------------------|

| Analog and DATA-IN Timing             |

| Interrupt Timing                      |

| Control Pin Timing                    |

| Buffered Read of PC, RIC              |

| Buffered Read of DMEM                 |

| Buffered Read of IMEM                 |

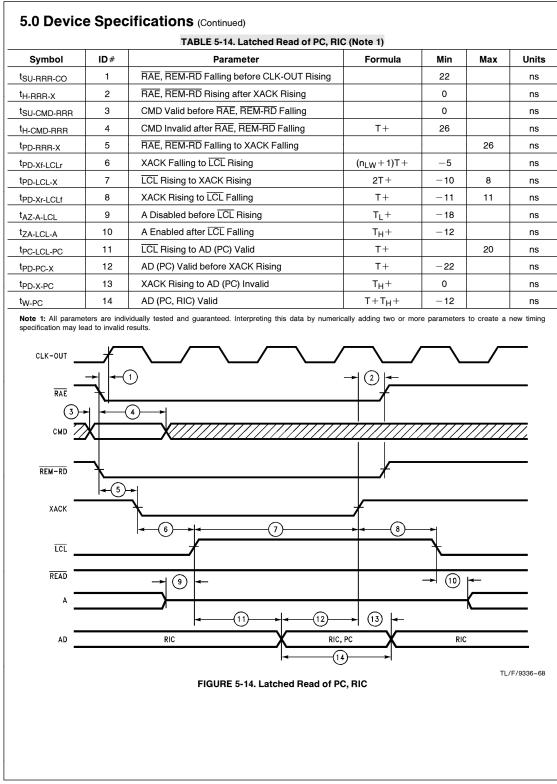

| Latched Read of PC, RIC               |

| Latched Read of DMEM                  |

| Latched Read of IMEM                  |

| Slow Buffered Write of PC, RIC        |

| Slow Buffered Write of DMEM           |

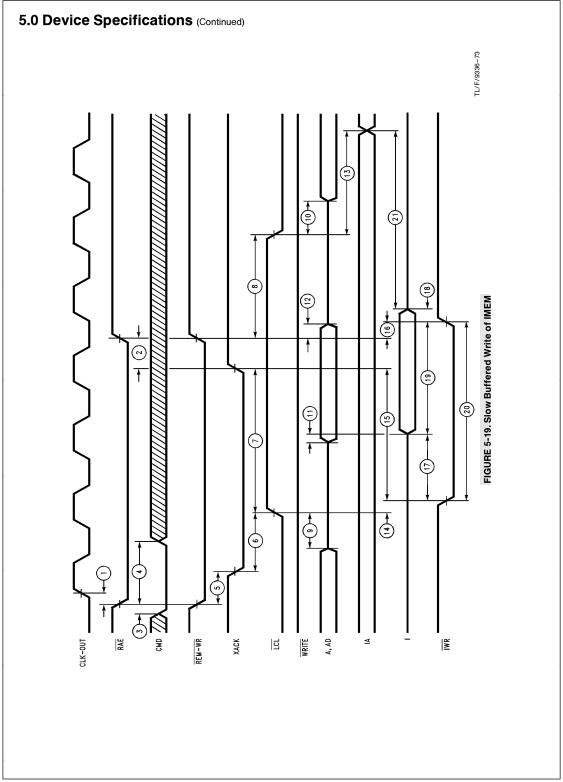

| Slow Buffered Write of IMEM           |

| Fast Buffered Write of PC, RIC   5-20 |

| Fast Buffered Write of DMEM           |

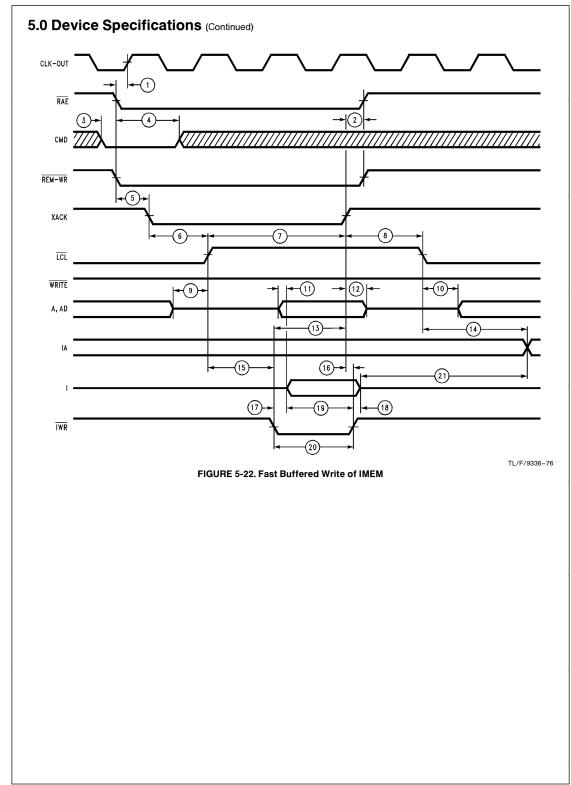

| Fast Buffered Write of IMEM           |

| Latched Write of PC, RIC              |

| Latched Write of DMEM                 |

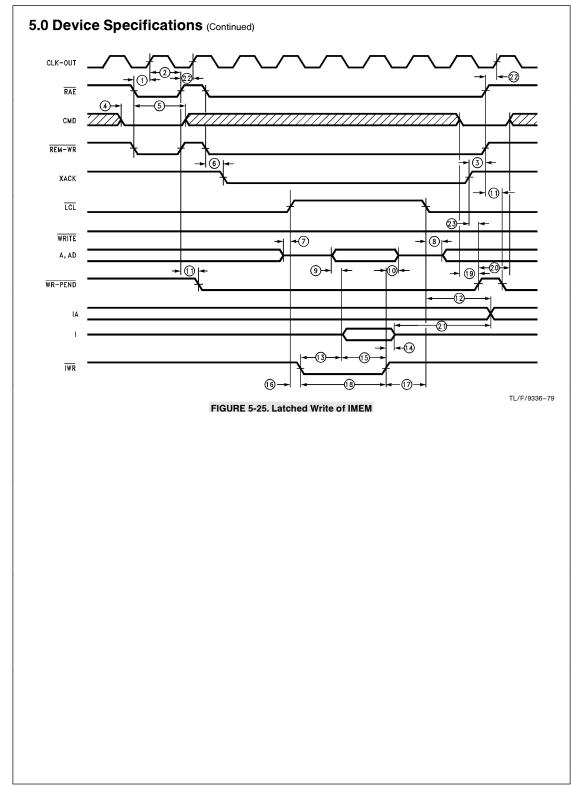

| Latched Write of IMEM                 |

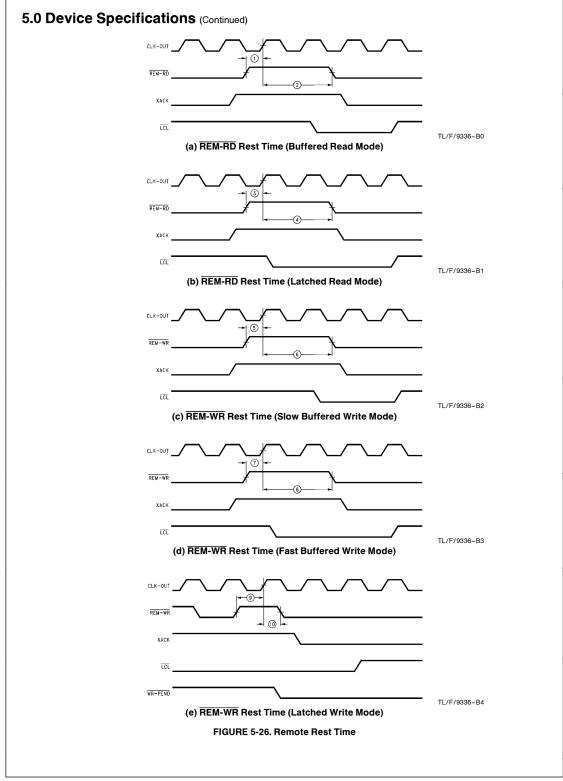

| Remote Rest Times                     |

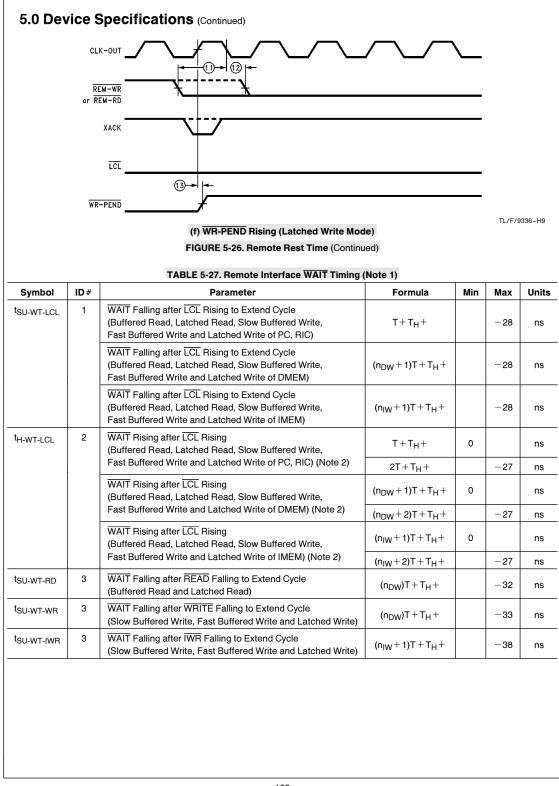

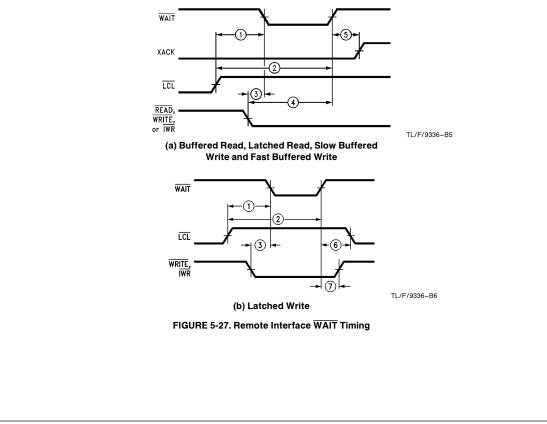

| Remote Interface WAIT Timing          |

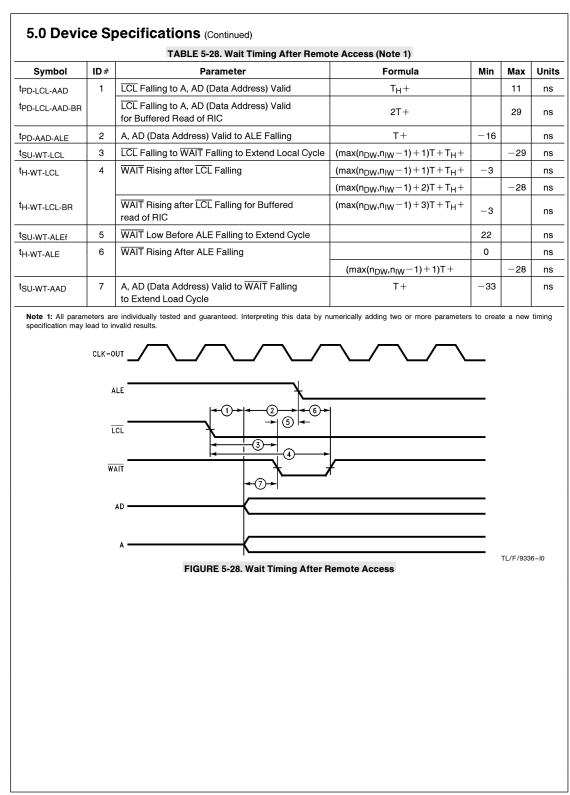

| WAIT Timing after Remote Access       |

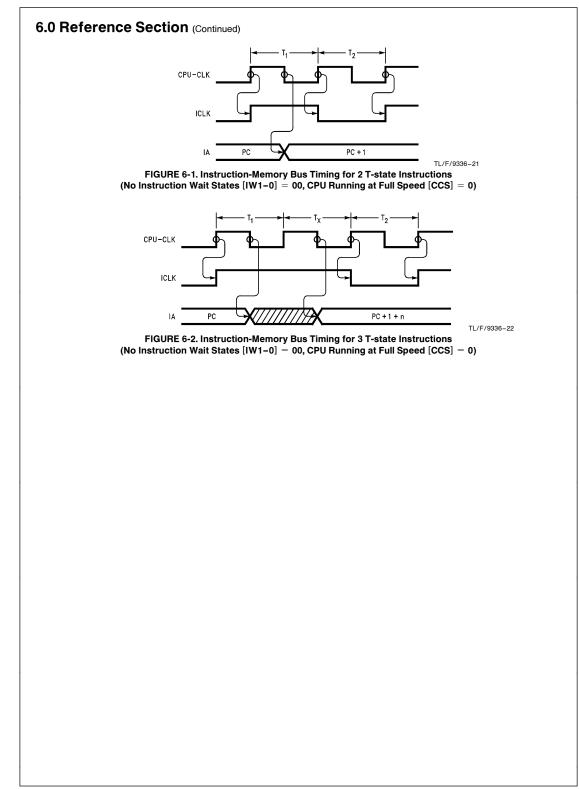

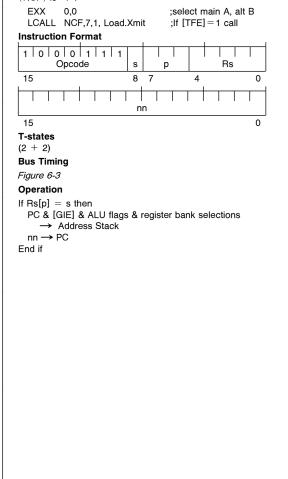

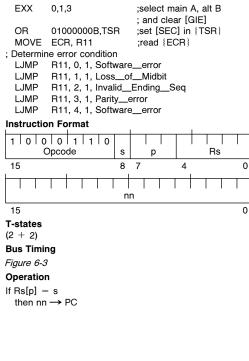

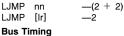

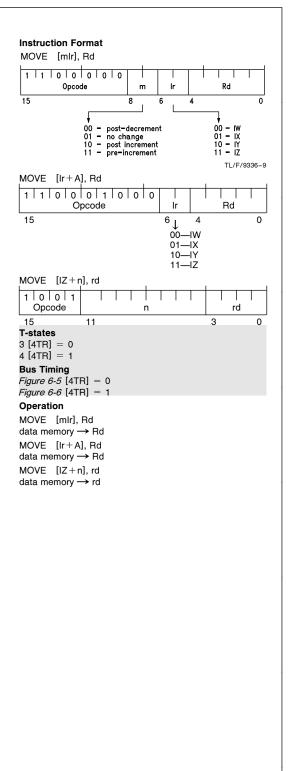

| Instruction Memory Bus Timing for 2 T-state Instructions          | 6-1 |

|-------------------------------------------------------------------|-----|

| Instruction Memory Bus Timing for 3 T-state Instructions          |     |

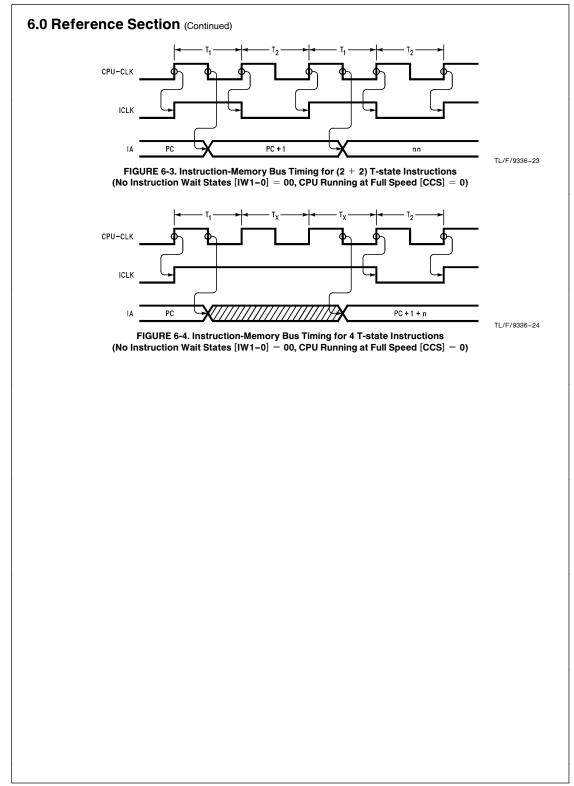

| Instruction Memory Bus Timing for (2 + 2) T-state Instructions    |     |

| Instruction Memory Bus Timing for 4 T-state Instructions          | 6-4 |

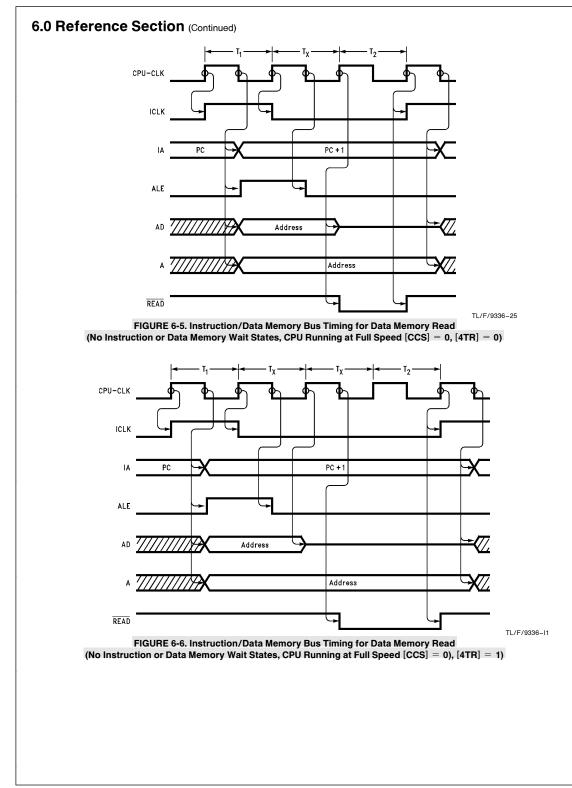

| Instruction/Data Memory Bus Timing for Data Memory Read [4TR] = 0 | 6-5 |

| Instruction/Data Memory Bus Timing for Data Memory Read [4TR] = 1 | 6-6 |

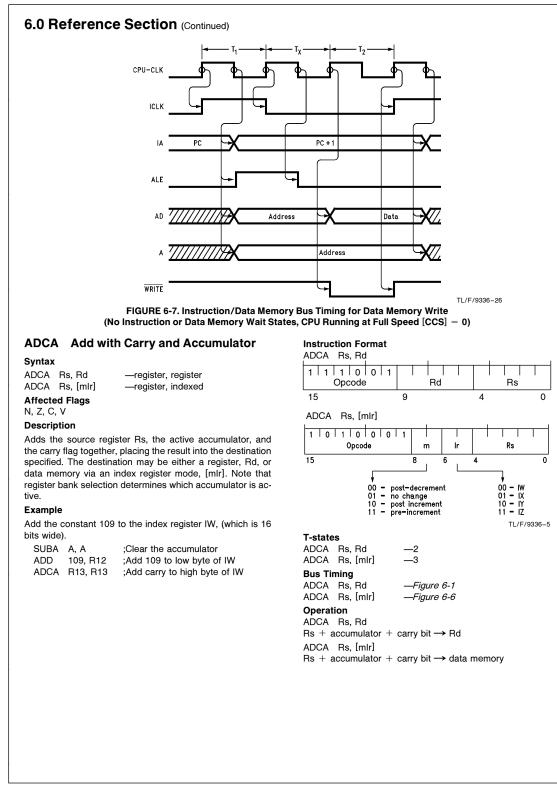

| Instruction/Data Memory Bus Timing for Data Memory Write          | 6-7 |

## List of Tables

| Register Addressing Mode Notations2-1       |  |

|---------------------------------------------|--|

| Immediate Addressing Mode Notations         |  |

| Index Register Addressing Mode Notations2-3 |  |

| Relative Index Register Mode Notations      |  |

| Data Movement Notations                     |  |

| Integer Arithmetic Instruction              |  |

| Logic Instructions                          |  |

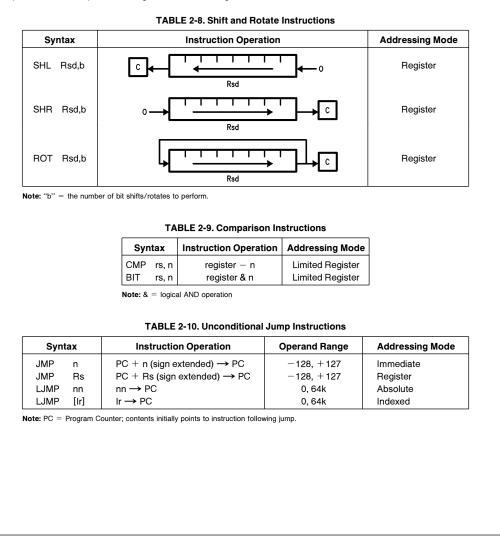

| Shift and Rotate Instructions               |  |

| Comparison Instructions                     |  |

| Unconditional Jump Instructions             |  |

| Conditional Relative Jump Instructions      |  |

| "f" Flags                                   |  |

| "cc" Conditions Tested                      |  |

| Conditional Absolute Jump Instructions      |  |

| JRMK Instruction                            |  |

| Unconditional Call Instructions             |  |

| Conditional Call Instructions               |  |

| Unconditional Return Instruction            |  |

| Conditional Return Instruction              |  |

| TRAP Instruction                            |  |

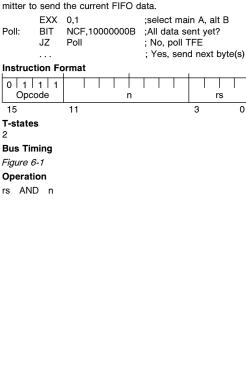

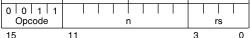

| EXX Instruction                             |  |

|                                             |  |

## List of Tables (Continued)

| LIST OF TADIES (Continued)                                                                                         |

|--------------------------------------------------------------------------------------------------------------------|

| Unsigned Comparison Results                                                                                        |

| Signed Comparison Results                                                                                          |

| Data Memory Wait States                                                                                            |

| Instruction Memory Wait States                                                                                     |

| BIRQ Control Summary                                                                                               |

| {ICR} Interrupt Mask Bits and Interrupt Priority                                                                   |

| Interrupt Vector Generation                                                                                        |

| Recommended Crystal Parameters                                                                                     |

|                                                                                                                    |

| Protocol Mode Definitions                                                                                          |

| Transceiver Interrupts                                                                                             |

| Receiver Interrupts                                                                                                |

| Decode of 3270 Coax Commands                                                                                       |

|                                                                                                                    |

| RIAS Inputs and Outputs                                                                                            |

| Note: To match Timing table number with appropriate Timing illustration, Tables 5-1 and 5-2 are purposely omitted. |

| Note: To match timing table number with appropriate timing illustration, tables 5-1 and 5-2 are purposely omitted. |

| Date Manage Dead Timing                                                                                            |

| Data Memory Read Timing                                                                                            |

| Data Memory Write Timing                                                                                           |

| Instruction Memory Timing                                                                                          |

| Clock Timing                                                                                                       |

| Transceiver Timing                                                                                                 |

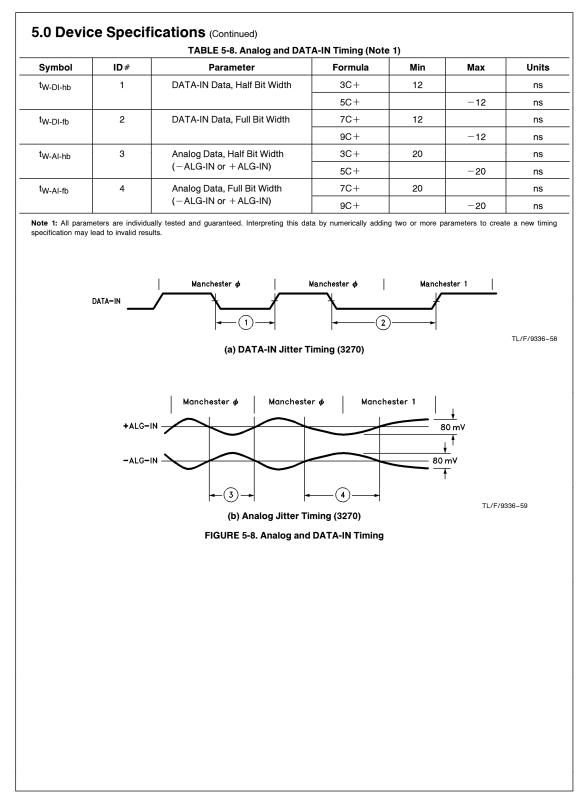

| Analog and DATA-IN Timing                                                                                          |

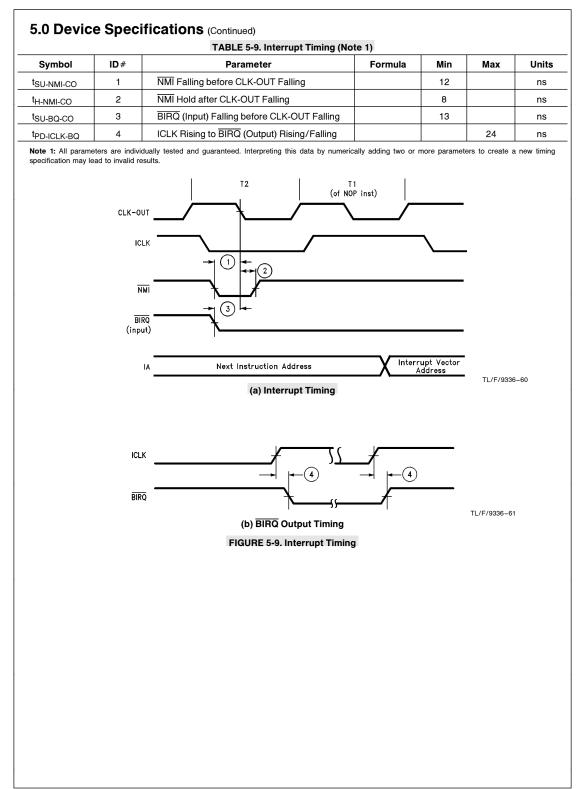

| Interrupt Timing                                                                                                   |

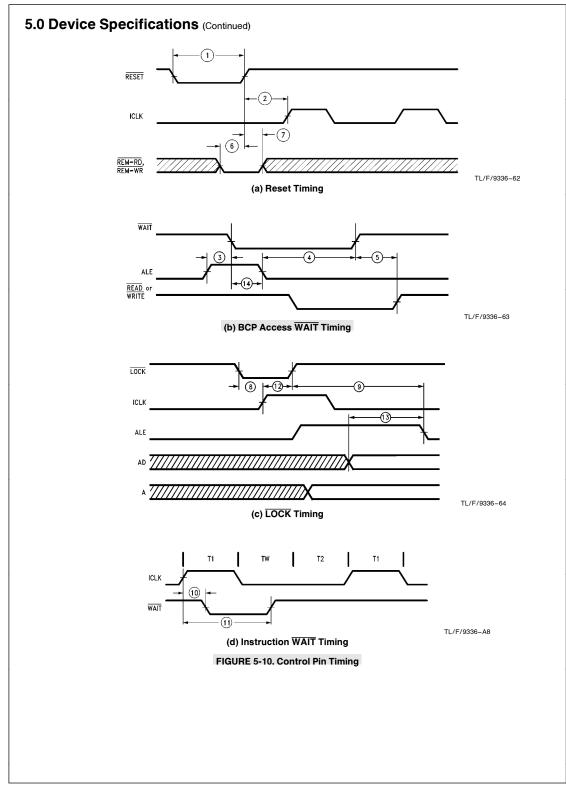

| Control Pin Timing                                                                                                 |

| Buffered Read of PC, RIC                                                                                           |

| Buffered Read of DMEM                                                                                              |

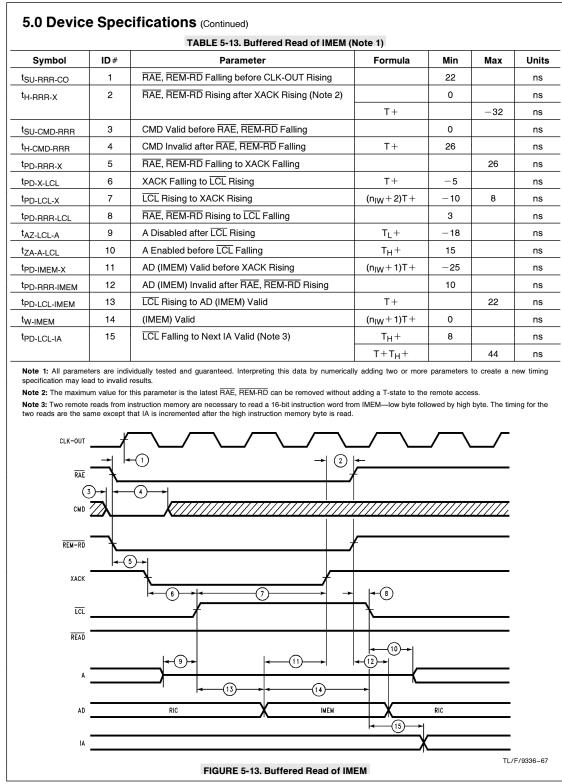

| Buffered Read of IMEM                                                                                              |

| Latched Read of PC, RIC                                                                                            |

| Latched Read of DMEM                                                                                               |

| Latched Read of IMEM                                                                                               |

| Slow Buffered Write of PC, RIC                                                                                     |

| Slow Buffered Write of DMEM5-18                                                                                    |

| Slow Buffered Write of IMEM                                                                                        |

| Fast Buffered Write of PC, RIC   5-20                                                                              |

| Fast Buffered Write of DMEM                                                                                        |

| Fast Buffered Write of IMEM                                                                                        |

| Latched Write of PC, RIC                                                                                           |

| Latched Write of DMEM                                                                                              |

| Latched Write of IMEM                                                                                              |

| Remote Rest Times                                                                                                  |

| Remote Interface WAIT Timing                                                                                       |

| WAIT Timing after Remote Access                                                                                    |

| -                                                                                                                  |

| Notational Conventions for Instruction Set                                                                         |

| Instructions vs T-states, Affected Flags and Bus Timing                                                            |

| Instruction Opcodes                                                                                                |

| DP8344B Application Notes                                                                                          |

|                                                                                                                    |

|                                                                                                                    |

|                                                                                                                    |

### **1.0 Communications Processor Introduction**

The increased demand for computer connectivity has driven National Semiconductor to develop the next generation of special purpose microprocessors. The DP8344B is the first example of a "Communications Processor" for the IBM environment. It integrates a very fast, full function microprocessor with highly specialized transceiver circuitry. The combination of speed, power, and features allows the designer to easily implement a state-of-the-art communications interface. Typical applications for a communications processor are terminal emulation boards for PCs, stand-alone terminals, printer interfaces, and cluster controllers.

The transceiver is designed to simplify the handling of specific communication protocols. This feature makes it possible to quickly develop interfaces and software with little concern for the "housekeeping" details of the protocol being used.

#### **1.1 COMMUNICATIONS PROTOCOLS**

A communication protocol is a set of rules which defines the physical, electrical, and software specifications required to successfully transfer data between two systems.

The physical specification includes the network architecture, as well as the type of connecting medium, the connectors used, and the maximum distance between connections. Networks may be configured in "loops," "stars," or "daisy chains," and they often use standard coaxial or twisted-pair cable.

The electrical specification includes the polarity and amplitude of the signal, the frequency (bit rate), and encoding technique. One common method of encoding is called "biphase" or "Manchester II." This technique combines the clock and data information into one transmission by encoding data as a "mid-bit" transition. *Figure 1-1* shows how the data transition is related to the bit boundary in a typical transmission. The polarity of the "mid-bit" transition encodes the data value, other transitions lie on bit boundaries. Bit boundaries are not always indicated by transitions, so techniques employing start sequences and sync bits are used with bi-phase transmissions to ensure proper frame alignment and synchronization.

The software specification covers the use of start sequences and sync bits, as well as defining the message format. Parity bits may be used to ensure data integrity. The message format is the "language" that is used to exchange information across the connecting medium. It defines command and control words, response times, and expected responses.

The DP8344B Bi-phase Communications Processor supports both the IBM 3270 and 5250 communication protocols, as well as IBM 3299 and a general purpose 8-bit protocol. The specialized transceiver is combined with a microprocessor whose instruction set is optimized for use in a communications environment. This makes the DP8344 a powerful single-chip solution to a wide range of communication applications.

An example of an IBM 3270 message is shown in *Figure* 1-2. The transmission begins with a very specific start sequence and sync pulse for synchronization. This is followed by the data, command, and parity bits. Finally, the end sequence defines the end of the transmission.

The IBM 3270 and 5250 are two widely used protocols. The 3270 protocol was developed for the 370 class mainframe, and it employs coaxial cable in a "star" configuration. The 5250 protocol was developed for the System/3x machines, and it uses a "daisy-chain" of twin-ax cable. A good overview of both of these environments may be found in the "Multi-Protocol Adapter System User Guide" from National Semiconductor, and in the Transceiver section of this document.

#### **1.2 INTERNAL ARCHITECTURE INTRODUCTION**

The DP8344B Biphase Communications Processor (BCP) is divided into three major functional blocks: the Transceiver, the Central Processing Unit (CPU), and the Remote Interface and Arbitration System, RIAS. *Figure 1-3* shows how these blocks are related to each other and to other system components.

The transceiver consists of an asynchronous transmitter and receiver which can communicate across a serial data path. The transmitter takes parallel data from the CPU and appends to it the appropriate framing information. The resulting message is shifted out and is available as a serial data stream on two output pins. The receiver shifts in serial messages, strips off the framing information, and makes the data available in parallel form to the CPU. The framing information supplied by the BCP provides the proper message format for several popular communication protocols. These include IBM 3270, 3299, and 5250, as well as a general purpose 8-bit mode.

The transceiver clock may be derived from the internal oscillator, either directly or through internal divide-down circuitry. There is also an input for an external transceiver clock, thus allowing complete flexibility in the choice of data rates.

The receiver input can come from three possible sources. There is a built-in differential amplifier which is suitable for most line interfaces, a single-ended digital input for use with an external comparator, and an internal loopback path for self testing. Refer to the Transceiver section for a detailed description of all transmitter and receiver functions, and to the application note on coax interfaces for the proper use of the differential amplifier.

The CPU is a general purpose, 8-bit microprocessor capable of 20 MHz operation. It has a reduced instruction set which is optimized for transceiver and data handling performance. It also has a full function arithmetic/logic unit (ALU) which performs addition, subtraction, Boolean operations, rotations and shifts. Separate instruction and data memory systems are supported, each with 16-bit address buses, for a total of 64k address space in each.

There are 44 internal registers accessible to the CPU. These include special configuration and control registers for the transceiver and processor, four 16-bit indices to data memory, and 20 8-bit general purpose registers. There is also a 16-bit timer and a 16-byte deep LIFO data stack which are accessible in the register address space. For more detailed information, see the specific sections on the Register set, the Timer, and the ALU.

The BCP can operate independently or with another processor as the host system. If such a system is required, communication with the BCP is possible by sharing data memory. The Remote Interface controls bus arbitration and access to data memory, as well as program up-loading and execution. For example, it is possible for a host system to load the BCP's instruction memory and begin program execution, then pass data back and forth through data memory accesses. The section on the Remote Interface and Arbitration System provides all of the necessary timing and control information to implement an interface between a BCP and a remote system.

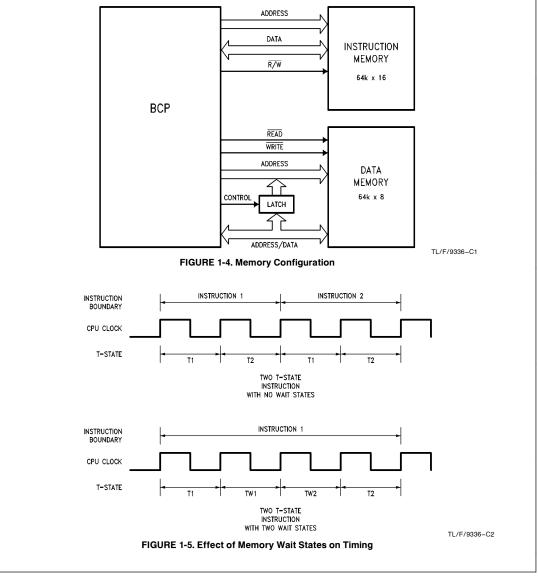

As shown in *Figure 1-4*, the BCP uses two entirely separate memory systems, one for program storage and the other for data storage. This type of memory arrangement is referred to as Harvard architecture. Each system has 16 address lines, for a maximum of 64k words in each, and its own set of data lines. The instruction (program) memory is two bytes (16 bits) wide, and the data memory is one byte (8 bits) wide.

In order to reduce the number of pins required for these signals, the address and data lines for data memory are multiplexed together. This requires an external latch and the Address Latch Enable signal (ALE) for de-multiplexing.

Simultaneous access to both data and program memory, and instruction pipelining greatly enhance the speed performance of the BCP, making it well suited for real-time processing. The pipeline allows the next instruction to be retrieved from program memory while the current instruction is being executed.

#### **1.3 TIMING INTRODUCTION**

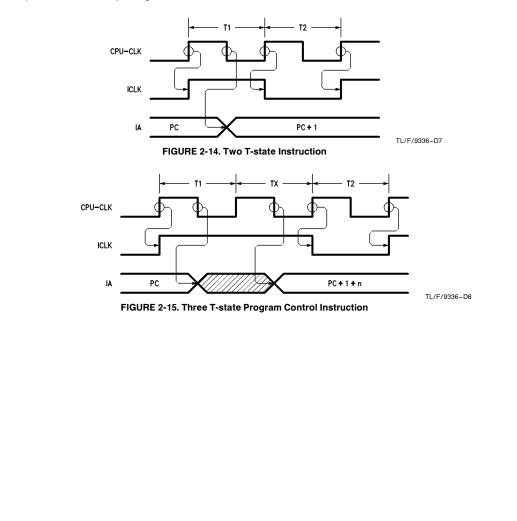

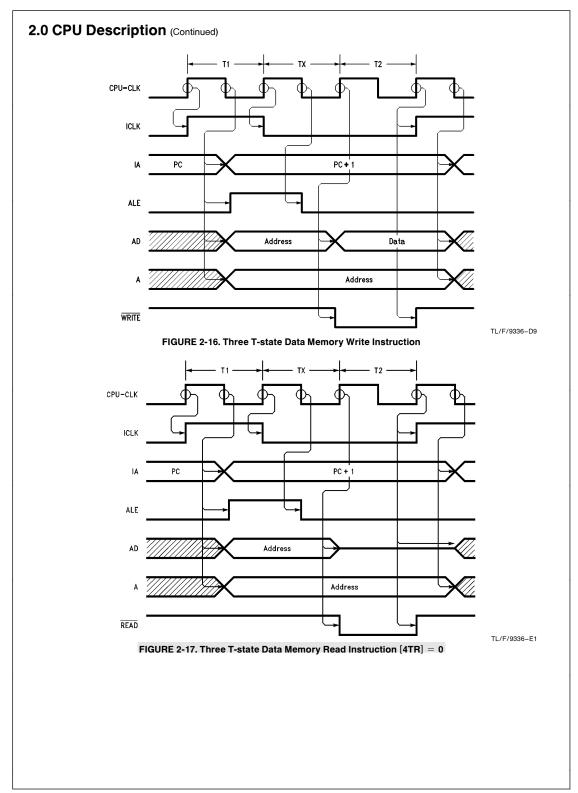

The timing of all CPU operations, instruction execution and memory access is related to the CPU clock. This clock is usually generated by a crystal and the internal oscillator, with optional divide by two circuitry. The period of the resulting CPU clock is referred to as a T-state; for example, a 20 MHz CPU clock yields a 50 ns T-state. Most CPU functions, such as arithmetic and logical operations, shifts and

rotates, and register moves, require only two T-states. Branching instructions and data memory accesses require three to four T-states.

Each memory system has a separate, programmable number of wait states to allow the use of slower memory devices. Instruction memory wait states are inserted into all instructions, as shown in *Figure 1-5*, thus they affect the overall speed of program execution. Instruction memory wait states can also apply when the Remote Interface is loading a program into instruction memory. Data memory wait states are only inserted into data memory access instructions, hence there is less degradation in overall program execution. Refer to the Timing section for detailed examples of all BCP instruction and data memory timing.

### 1.4 DATA FLOW

The CPU registers are all dual port, that is, they have separate input and output paths. This arrangement allows a single register to function as both a source and a destination within the same instruction.

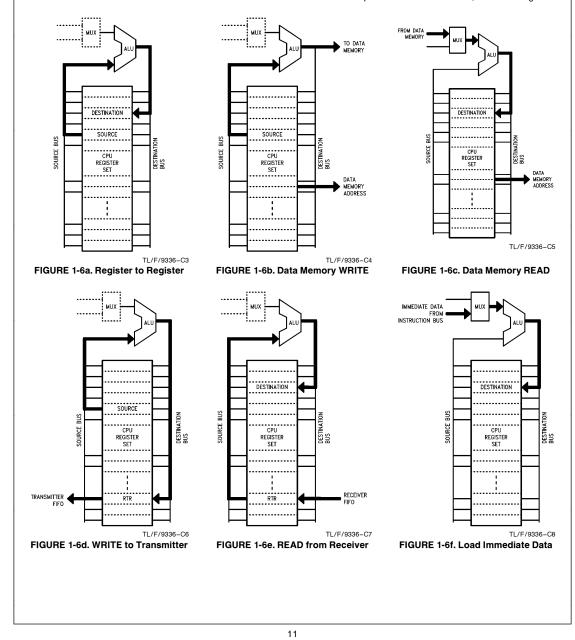

*Figures 1-6a* through *1-6f* show the internal data flow path for the BCP. The CPU registers are a central element to this path. When a register functions as an output, its contents are placed on the Source bus. When a register is an input, data from the Destination bus is written into that register.

The other key element in the data path is the ALU. This unit does all of the arithmetic and data manipulation operations, but it also has bus multiplexing capabilities. Both the Data Memory bus and a portion of the Instruction Memory bus are routed to this unit and serve as alternative sources of data. Since the data flow is always through this unit, most data moves may include arithmetic manipulations with no penalty in execution time.

*Figure 1-6a* shows the data path for all arithmetic instructions and register to register moves. The source register contents are placed on the Source bus, routed through the

ALU/MUX, and then placed on the destination bus. This data is then stored into the appropriate destination register. *Figures 1-6b* and *1-6c* show the data path for data memory accesses. For a WRITE operation, the source register contents follow the same path through the ALU/MUX, but the Destination bus is routed to output pins and on to data memory. For a READ operation, incoming data is routed onto the Destination bus by the ALU/MUX, and then stored in a register. The address for all data memory accesses is provided by one of four 16-bit index registers which can operate in a variety of automatic increment and decrement

Transfer of the data byte between the CPU and the Transceiver is accomplished through a register location. This register,  $\{RTR\}$ , appears as a normal CPU register, but writing to it automatically transfers data to the transmitter FIFO, and reading from it retrieves data from the receiver FIFO. These paths are illustrated in *Figures 1-6d* and *1-6e*.

modes.

It is also possible to load immediate data into a CPU register. This data is supplied by the program and is usually a constant such as a pointer or character. As shown in *Figure 1-6f*, a portion of the Instruction bus is routed through the ALU/MUX for this purpose.

# 1.5 REMOTE INTERFACE AND ARBITRATION SYSTEM INTRODUCTION

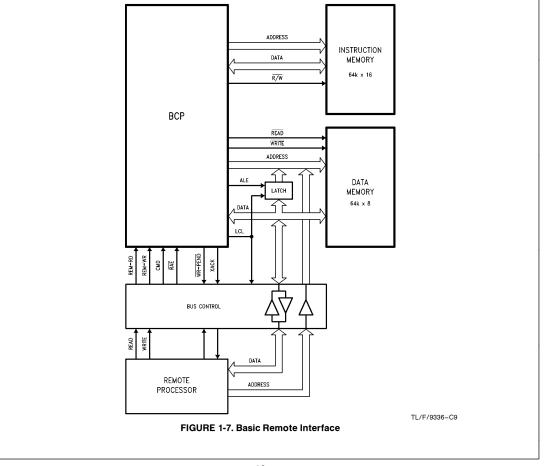

The BCP is designed to serve as a complete, stand alone communications interface. Alternately, it can be interfaced with another processor by means of the Remote Interface and Arbitration System. Communication between the BCP and the remote processor is possible by sharing data memory. Harvard architecture allows the remote system to access any BCP data memory location while the BCP continues to fetch and execute instructions, thereby minimizing performance degradation.

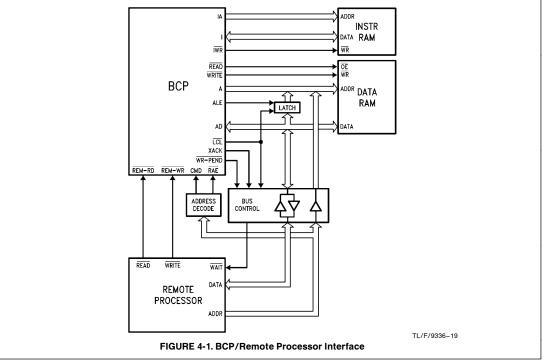

*Figure 1-7* shows a simplified remote processor interface. This includes tri-state buffers on the address and data buses of the BCP's Data Memory, and all of the control and handshaking signals required to communicate between the BCP and the host system.

There is an 8-bit control register, Remote Interface Control (RIC), accessible only to the remote system, which is used to control a variety of features, including the types of memory accesses, interface speeds, single step program execution, CPU start/stop, instruction memory loads, and so forth. Detailed information on all interface options is provided in the section on Remote Interface and Arbitration System, and in the related Reference section.

### 2.0 CPU Description

The CPU is a general purpose, 8-bit microprocessor capable of 20 MHz operation. It contains a large register set for standard CPU operations and control of the transceiver. The reduced instruction set is optimized for the communications environment. The following sections are an architectural and functional description of the DP8344B CPU.

#### 2.1 CPU ARCHITECTURAL DESCRIPTION

#### 2.1.1 Register Set

This section describes the BCP's internal CPU registers. It is a general overview of the register structure and the functions mapped into the CPU register space. It is not a detailed or exhaustive description of every bit. For such a description, please refer to Section 6.2, Register Set Reference. Also, the Remote Interface Configuration register,  $\{RIC\}$ , is not accessible to the BCP (being accessible only by the remote system) and is described in Section 6.3, Remote Interface Reference.

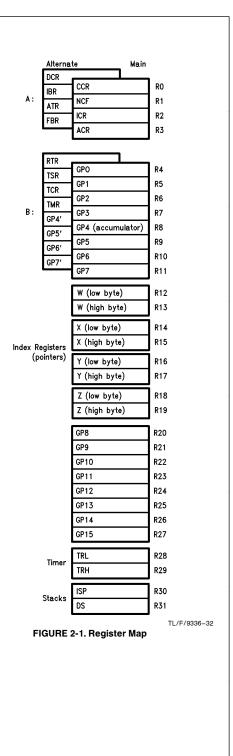

The register set of the BCP provides for a compliment of both special function and general purpose registers. The special function registers provide access to on-chip peripherals (transceiver, timer, interrupt control, etc.) while the general purpose registers maximize CPU throughput by minimizing accesses to external data memory. The CPU can address a total of 44 8-bit registers, providing access to:

- 20 general purpose registers

- 8 configuration and control registers

- 4 transceiver access registers

- 2 8-bit accumulators

- 4 16-bit pointers

- 16-bit timer

- 16 byte data stack

- · address and data stack pointers

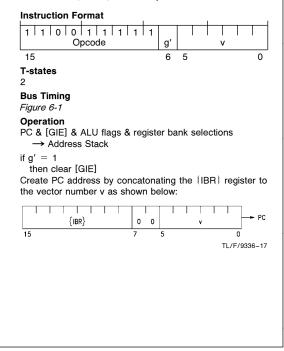

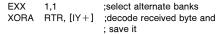

The CPU addresses internal registers with a 5-bit field, addressing 32 locations generically named R0 through R31. The first twelve locations (R0–R11) are further organized by function as two groups of banked registers (A and B) as shown in *Figure 2-1*. Each group contains both a main and an alternate bank. Only one bank is active for group A and one for bank B and thus accessible during program execution. Switching between the banks is performed by the exchange instruction EXX which selects whether Main A or Alternate A occupies R0–R3 and whether Main B or Alternate B occupies R4–R11.

Registers in the R0-R11 address space are allocated in a manner that minimizes the need to switch banks:

| Main A:      | CPU control and transceiver status |

|--------------|------------------------------------|

| Alternate A: | CPU and transceiver configuration  |

| Main B:      | 8 general purpose                  |

Alternate B: 4 transceiver access, 4 general purpose

Most of the BCP's instructions with register operand(s) can access all 32 register locations. Only instructions with an immediate operand are limited to the first sixteen register locations (R0–R15). These instructions, however, still have access to all registers required for transceiver operation, CPU status and control registers, 12 general purpose registers, and two of the index registers.

The general purpose registers are used for the majority of BCP operations. There are 8 general purpose registers in Main Bank B (R4–R11), 4 in Alternate Bank B (R8–R11), and 8 more (R20–R27) that are always accessible but are outside the limited register range. Since these registers are internal to the BCP, they can be accessed without data memory wait states, speeding up processing time. The index registers may also be used as general purpose registers if required.

For those instructions that require two operands, an accumulator (R8, one in each bank) serves as the second operand. The result of such an operation is stored back in the accumulator only if it is specified as the destination, thus allowing three operand operations such as R5 + R8  $\rightarrow$  R20. See Section 2.1.3 Instruction Set for further explanation.

Most registers have a predetermined state following a reset to the BCP. Refer to Section 6.2, Register Set Reference for a detailed summary.

#### 2.1.1.1 Banked Registers

The CPU register set was designed to optimize CPU performance in an environment which supports multiple tasks. Generally the most important and time critical of these tasks will be maintaining the serial link (servicing the transceiver section) which often requires real time processing of commands and data. Therefore, all transceiver functions have been mapped into special function registers which the CPU can access quickly and easily. Switching between this task and other tasks has been facilitated by dedicating a register bank (Alternate B) to transceiver functions. Alternate Bank B provides access to all transceiver status, control, and data, in addition to four general purpose registers for protocol related storage. Main Bank B contains eight general purpose registers for use by other tasks. Having general purpose registers in both B banks allows for quick context switching and also helps eliminate some of the overhead of saving general purpose registers. The main objective of this banked register structure is to expedite servicing of the transceiver as a background (interrupt driven) task allowing the CPU to efficiently interleave that function with other background and foreground operations.

To facilitate using the transceiver in a polled fashion (instead of using interrupts), many of the status flags necessary to handshake with the transceiver are built into the conditional jump instructions, with others available in the Main A bank (normally active) so that Alternate Bank B does not have to be switched in to poll the transceiver. Timer and BIRQ tasks may also be run using polling techniques to Main A bank.

In general, the registers have been arranged within the banks so as to minimize the need to switch banks. The power-up state is Alternate bank A, Alternate bank B allowing access to configuration registers. Again, the banks switch by using the EXX instruction which explicitly specifies which bank is active (Main or Alternate) for each register group (A and B). The EXX instruction allows selecting any of four possible bank settings with a single two T-state instruction. This instruction also has the option of enabling or disabling the maskable interrupts.

The contents of the special function registers can be divided into several groups for general discussion—timing/control, interrupt control, the transceiver, the condition codes, the index registers, the timer, the stacks, and remote interface.

#### 2.1.1.2 Timing/Control Registers

The BCP provides a means to configure its external timing through setting bits in the Device Control Register, {DCR}, and the Auxiliary Control Register, {ACR}. One of the first configuration registers to be initialized on power-up/reset is {DCR} which defines the hardware environment in which the BCP is functioning. Specifically, {DCR} controls the clock select logic for both the CPU and transceiver, in addition to the number of wait states to be used for instruction and data memory accesses.

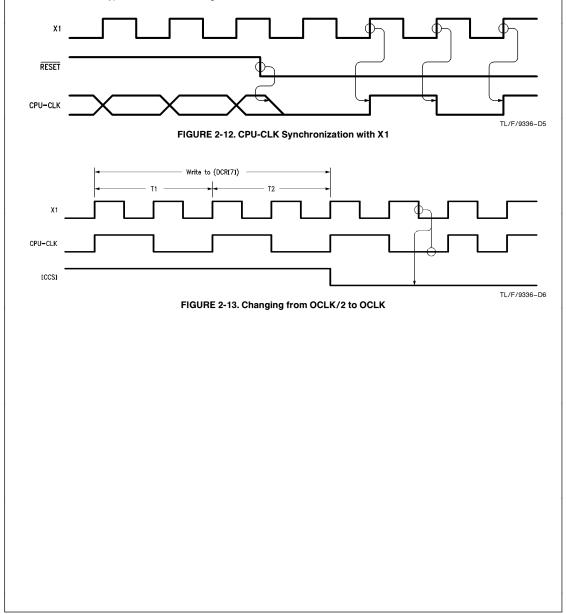

The BCP allows either one clock source operation for the CPU and the transceiver from the on-chip oscillator, or an independent clock source can run the transceiver from the eXternal Transceiver CLocK input, X-TCLK. The Transceiver Clock Select bits, [TCS1,0], select the clock source for the transceiver which is either the on-chip Oscillator CLocK. OCLK, or X-TCLK. Options for selecting divisions of the onchip oscillator frequency are also provided (see the description of {DCR} in Section 6.2, Register Set Reference. The CPU Clock Select bit, [CCS], allows the CPU to run at the OCLK frequency or at half that speed. The clock output at the pin CLK-OUT, however, is never divided and always reflects the crystal frequency OCLK. The frequency selected for the transceiver (referred to as TCLK) should always be eight times the desired serial data rate. The frequency selected for the CPU defines the length of each T-state (e.g., 20 MHz implies 50 ns T-states).

There are two independent fields for defining wait states, one for instruction memory access  $(n_{\rm IW})$  and one for data memory access  $(n_{\rm DW})$ . These fields specify to the BCP how many wait states to insert to meet the access time requirements of both memory systems. The Instruction memory Wait-state select bits, [IW1,0], and the Data memory Wait-state solect bits, [DW2-0], control the number of inserted wait states for instruction and data memory, respectively.

After a reset, the maximum number of wait states are set in {DCR},  $n_{IW} = 3$  T-states and  $n_{DW} = 7$  T-states. Wait-states are discussed in more detail in Section 2.2.2, Timing. For a complete discussion on choosing your memory and determining the number of wait states required, please refer to the application note *Choosing Your RAM for the Biphase Communication Processor*.

Another control bit in the {ACR} register is the Clock Out Disable bit, [COD]. When [COD] is asserted, the buffered clock output at pin CLK-OUT is tri-stated.

#### 2.1.1.3 Interrupt Control Registers

The configuration bank (Alternate Bank A) includes an Interrupt Base Register, {IBR}, which defines the high byte of all interrupt and trap vector addresses. Thus, the interrupt vector table can be located in any 256 byte page of the 64k range of instruction addresses. The interrupt base is normally initialized once on reset before interrupts are enabled or any traps are executed. Since  $\overline{\text{NMI}}$  is nonmaskable and may occur before {IBR} is initialized, the power-up/reset value of {IBR} (00h) should be used to accommodate  $\overline{\text{NMI}}$  during initialization. In other words, if  $\overline{\text{NMI}}$  is used in the system, the absolute address 001Ch (the  $\overline{\text{NMI}}$  vector) should contain a jump to an  $\overline{\text{NMI}}$  service routine.

The Interrupt Control Register, {ICR}, provides individual masks [IM4–0] for each of the maskable interrupts. The Global Interrupt Enable bit, [GIE], located in {ACR} works in conjunction with these individual masks to control each of the maskable interrupts.

The external pin called  $\overline{\text{BIRQ}}$  is a Bidirectional Interrupt ReQuest.  $\overline{\text{BIRQ}}$  is defined as an input or an output by the Bidirectional Interrupt Control bit, [BIC], in {ACR}. [IM3] functions as BIRQ's interrupt mask if  $\overline{\text{BIRQ}}$  is an input as defines by [BIC]. When [BIC] defines BIRQ as an output, [IM3] controls the output state of  $\overline{\text{BIRQ}}$ .

Section 2.2.3, Interrupts provides a further description of these registers.

#### 2.1.1.4 Timer Registers

The timer block interfaces with the CPU via two registers, TimeR Low byte, {TRL}, and TimeR High byte, {TRH}, which form the input/output ports to the timer. Writing to {TRL} and {TRH} stores the low and high byte, respectively, of a 16-bit time-out value into two holding registers. The word stored in the holding registers is the value that the timer will be loaded with via [TLD]. Also, the timer will automatically reload this word upon timing out. Reading {TRL} and {TRH} provides access to the count down status of the timer.

Control of timer operation is maintained via three bits in the Auxiliary Control Register {ACR}. Timer STart [TST], bit 7 in {ACR}, is the start/stop control bit. Writing a one to [TST] allows the timer to start counting down from its current value. When low, the timer stops and the timer interrupt is cleared. Timer Load [TLD], bit 6 in {ACR}, is the load control of the timer. After writing the desired values into {TRL} and {TRH}, writing a one to [TLD] will load the 16-bit word in the holding registers into the timer and initialize the timer clock to zero in preparation to start counting. Upon completing the load operation, [TLD] is automatically cleared, Timer Clock Selection [TCS], bit 5 in {ACB}, determines the clock frequency of the timer count down. When low, the timer divides the CPU clock by sixteen to form the clock for the down counter. When [TCS] is high, the timer divides the CPU clock by two. The input clock to the timer is the CPU clock and should not be confused with the oscillator clock, OCLK. The rate of the CPU clock will be either equal to OCLK or one-half of OCLK depending on the value of bit 7 in the Device Control Register, {DCR}.

When the timer reaches a count of zero, the timer interrupt is generated, the Time Out flag, [TO], (bit 7 in the Condition Code Register {CCR}), goes high, and the timer reloads the 16-bit word stored in the holding registers to recycle through a count down. The timer interrupt and [TO] can be cleared by either writing a one to [TO] in {CCR} or stopping the timer by writing a zero to [TST] in {ACR}. Refer to Section 2.1.2, Timer for more information on the timer operation.

#### 2.1.1.5 Transceiver Registers

Two registers in the Alternate A bank initialize transceiver functions. The Auxiliary Transceiver Register, {ATR}, specifies a station address used by the address recognition logic within the transceiver when using the non-promiscuous 5250 and 8-bit protocol modes. In 5250 modes, {ATR} also defines how long the TX-ACT pin stays asserted after the end of a transmitted message. The Fill Bit Register, {FBR}, specifies the number of optional fill bits inserted between frames in a multiframe 5250 message.

{ICR} contains the Receiver Interrupt Select bits, [RIS1,0]. These bits determine the receiver interrupt source selection. The source may be either Receiver FIFO Full, Data Available, or Receiver Active.

The Receive/Transmit Register, {RTR}, is the input/output port to both the transmitter and receiver FIFO's. It appears to the BCP CPU like any other register. The {RTR} register provides the least significant eight bits of data in both received and transmitted messages.

The Transceiver Mode Register, {TMR}, contains bits used to set the configuration of the transceiver. As long as the Transceiver RESet bit, [TRES], is high, the transceiver remains in reset. Internal LOOP-back operation of the transceiver can be selected by asserting [LOOP]. The RePeat ENable bit, [RPEN], allows the receiver to be active at the same time as the transmitter. When the Receiver INvert bit, [RIN], is set, all data sent to the receiver is inverted. The Transmitter INvert bit, [TIN], is analogous to [RIN] except it is for the transmitter. The protocol that the transceiver is using is selected with the Protocol Select bits, [PS2–0].

The Transceiver Command Register, {TCR}, controls the workings of the transmitter. To generate 5.5 line quiesce pulses at the start of a transmission rather than 5, the Advance Transmitter Active bit, [ATA], must be set high. Parity is automatically generated on a transmission and the Odd Word Parity bit, [OWP], determines whether that parity is even or odd. Bits 2–0 of {TCR} make up part of the Transmitter FIFO [TF10–8] along with {RTR}. Whenever a write is made to {RTR}, [TF10–8] are automatically pushed on the FIFO with the 8 bits written to {RTR}.

Other bits in {TCR} control the operation of the on-chip receiver. The number of line quiesce bits the receiver must detect to recognize a valid message is determined by the Receive Line Quiesce bit, [RLQ]. The BCP has its own internal analog comparator, but an off-chip one may be connected to DATA-IN. The receiver source is determined by the Select Line Receiver bit, [SLR]. To view transceiver errors in the Error Code Register, {ECR}, the Select Error Codes, [SEC], bit in {TCR} must be set high. When [SEC] is high, Alternate Bank B R4 is remapped from {RTR} to {ECR} so that {ECR} can be read.

Just as [TF10-8] bits get pushed onto the transmitter FIFO when a write to [RTR] occurs, the Receiver FIFO bits, [RF10-8], in the Transceiver Status Register, [TSR], reflect the state of the top word of the receive FIFO. [TSR] also contains flags that show Transmit FIFO Full, [TFF], Transmitter Active, [TA], Receiver Error, [RE], Receiver Active, [RA], and Data AVailable, [DAV]. These flags may be polled to determine the state of the transceiver. For instance, during a Receiver Active interrupt, the BCP can query the [DAV] bit to determine whether data is ready in the receiver FIFO yet.

The Error Code Register, {ECR}, contains flags for receiver errors. As previously stated, the [SEC] bit in {TRC} must be set high to read this register. Reading {ECR} or resetting the transceiver with [TRES] will clear all the errors that are present. The receiver OVerFlow flag, [OVF], is set when the receiver attempts to add another word to the FIFO when it is full. If internally checked parity and parity transmitted with a 3270 message conflict, then the PARity error bit, [PAR], is set high. The Invalid Ending Sequence bit, [IES], is set when the ending sequence in a 3270, 3299, or 8-bit message is incorrect. When the expected mid-bit transition in the Manchester waveform does not occur, a Loss of Mid-Bit Transition occurs ([LMBT]). Finally, if the transmitter is activated while the receiver is active, the Receiver DISabled while active flag, [RDIS], will be set unless [RPEN] is asserted.

The second register in Main A bank is called the Network Command Flag register, {NCF}, and contains information about the transceiver which is useful for polling the transceiver (during other tasks for example) to see if it needs servicing. These flags include bits to indicate Transmit FIFO Empty [TFE], Receive FIFO Full [RFF], Line Active [LA], and a Line Turn Around [LTA]. [LTA] indicates that a message has been received without error and a valid ending sequence has occurred. These flags facilitate polling of the transceiver section when transceiver interrupts are not used. Also included in this register is a bit called [DEME] (Data Error/Message End). In 3270/3299 modes, this bit indicates a mismatch between received and locally generated byte parity. In 5250 modes, [DEME] decodes an end of message indicator (111 in the address field). Three other bits: Received Auto Response [RAR], Acknowledge [ACK] and Poll [POLL] are decoded from a received message (at the output of the receive FIFO) and are valid only in 3270/ 3299 modes where response time is critical.

Section 3.0 Transceiver provides comprehensive coverage of this on-chip peripheral.

#### 2.1.1.6 Condition Codes/Remote Handshaking Register

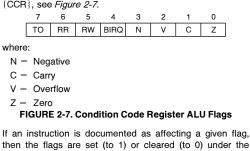

The ALU condition codes are available in the Condition Code Register {CCR}. The [Z] bit is set when a zero result is generated by an arithmetic, logical, or shift instruction. Similarly, [N] indicates the Negative result of the same operations. An oVerflow condition from an arithmetic instruction sets the [V] bit in {CCR}. The Carry bit [C] indicates a carry or borrow result from an arithmetic instruction. See Section 2.2.2, ALU for more information.

The Condition Code Register, {CCR}, also contains [BIRQ], a status bit which reflects the logic level of the bidirectional interrupt input pin BIRQ. Hence, this pin can be used as a general purpose input/output port as well as a bidirectional

interrupt request as defined by bits in {ACR} and {ICR}. If a remote CPU is present and shares data memory (dual port memory) with the BCP, handshaking can be accomplished by using the two status bits in {CCR} called [RR] and [RW], which indicate Remote Read and Remote Write accesses, respectively.

In {ACR}, a lock bit, [LOR], is available to lock out all host accesses. When this bit is set, all host accesses are disabled. Locking out remote accesses is often done during interrupts to ensure quick response times.

The Remote Interface Configuration register, {RIC}, is not available to the BCP internally. The Remote Interface Reference section provides further detail on {RIC} and interfacing a remote processor.

#### 2.1.1.7 Index Registers

Four index registers called IW, IX, IY, and IZ provide 16-bit addressing for both data memory and instruction memory. Each of these index registers is actually a pair of 8-bit registers which are individually addressable just like any other CPU register. They occupy register addresses R12 through R19. Thus, the first two pointers IW and IX (comprising R12–R15) can be accessed with immediate mode instructions (which can access only R0 to R15). Refer to Section 2.1.3.2, Addressing Modes to see how the index registers are formed from R12–R19.

Accessing data memory requires the use of one of the four index registers. All such instructions allow you to specify which pointer is to be used, except the immediate-relative moves: MOVE rs, [IZ+n] and MOVE [IZ+n],rd. These instructions always use the IZ pointer. Register indirect operations have options to alter the value of the index register; the options include pre-increment, post-increment, and post-decrement. These options facilitate block moves, searches, etc. Refer to Section 2.1.3, Instruction Set for more information about data moves.

Since the BCP's ALU is 8 bits wide, all code that manipulates the index registers must act on them eight bits at a time.

The index registers can also be used in register indirect jumps (LJMP [Ir]), useful in implementing relocatable code. Any one of the index registers can be specified to provide the 16-bit instruction address for the indirect jump.

#### 2.1.1.8 Stack Registers

The last two register addresses (R30,R31) are dedicated to provide access to the two on-chip stacks—the data stack and the address stack. The data stack is 8 bits wide and 16 words deep. It is a Last In First Out (LIFO) type and provides high speed storage for variables, pointers, etc. The address stack is 23 bits wide and 12 words deep, providing twelve levels of nesting of subroutines and interrupts. It is also a LIFO structure and stores processor status as well as return addresses from CALL instructions, TRAP instructions, and interrupts. The seven bits of processor status consist of the four ALU flags, ([C], [N], [V], and [Z]), the current bank setting (two bits), and [GIE].

Stack pointers for both the on-chip stacks are provided in R30, the Internal Stack Pointer register, {ISP}. The lower four bits are the pointer for the data stack and the upper four bits are the pointer for the address stack. Both internal stacks are circular. For example if 16 bytes are written to

the data stack, the next byte pushed will overwrite the first.  $\{ISP\}$  can be read and written to like any other register, but after a write, the BCP must execute one instruction before reading the stack whose pointer was modified.

The Data Stack register, {DS}, is the input/output port for the data stack. This port is accessed like any other register, but a write to it will "push" a byte onto the stack and a read from it will "pop" a byte from the stack. The data stack pointer is updated when a read or write of {DS} occurs.

Information bits in the instruction address stack are not mapped into the CPU's register space and, therefore, are not directly accessible. A remote system running a monitor program can access this information by forcing the BCP to single-step through a return instruction and then reading the program counter. Since the stack pointers are writeable, the remote system can access any location (return address) in the address stack to trace program flow and then restore the stack pointer to its original position.

#### 2.1.2 Timer

The BCP has an internal 16-bit timer that can be used in a variety of ways. The timer counts independently of the CPU, eliminating the waste of valuable processor bandwidth. The timer can be used in a polled or interrupt driven configuration for user software flexibility.

The timer interfaces with the CPU via two registers, TimeR Low byte, {TRL}, and TimeR High byte, {TRH}, which form the input/output ports to the timer. Writing to {TRL} and {TRH} stores the low and high byte, respectively, of a 16-bit time-out value into two holding registers. The word stored in the holding registers is the value that the timer will be load-

ed with via [TLD]. Also, the timer will automatically reload this word upon timing out. Reading {TRL} and {TRH} provides access to the count down status of the timer.

Control of timer operation is maintained via three bits in the Auxiliary Control Register {ACR}. Timer STart [TST], bit 7 in {ACR}, is the start/stop control bit. Writing a one to [TST] allows the timer to start counting down from its current value. When low, the timer stops and the timer interrupt is cleared. Timer Load [TLD], bit 6 in {ACR}, is the load control of the timer. After writing the desired values into {TRL} and {TRH}, writing a one to [TLD] will load the 16-bit word in the holding registers into the timer and initialize the timer clock to zero in preparation to start counting. Upon completing the load operation, [TLD] is automatically cleared. Timer Clock Selection [TCS], bit 5 in {ACR}, determines the clock frequency of the timer count down. When low, the timer divides the CPU clock by sixteen to form the clock for the down counter. When [TCS] is high, the timer divides the CPU clock by two. The input clock to the timer is the CPU clock and should not be confused with the oscillator clock, OCLK. The rate of the CPU clock will be either equal to OCLK or one-half of OCLK depending on the value of bit 7 in the Device Control Register, {DCR}.

When the timer reaches a count of zero, the timer interrupt is generated, the Time Out flag, [TO], (bit 7 in the Condition Code Register {CCR}), goes high, and the timer reloads the 16-bit word stored in the holding registers to recycle through a count down. The timer interrupt and [TO] can be cleared by either writing a one to [TO] in {CCR} or stopping the timer by writing a zero to [TST] in {ACR}. A block diagram of the timer is shown in *Figure 2-2*.

#### 2.1.2.1 Timer Operation

After the desired 16-bit time-out value is written into {TRL} and {TRH}, the start, load, and clock selection can be achieved in a single write to {ACR}. A restriction exists on changing the timer clock frequency in that [TCS] should not be changed while the timer is running (i.e., [TST] is high). After a write to {ACR} to load and start the timer, the timer begins counting down at the selected frequency from the value in {TRL} and {TRH}. Upon reaching a count of zero, the timer interrupt is generated and, the timer reloads the current word from {TRL} and {TRH} to cycle through a countdown again. The timing waveforms shown in Figure 2-3 show a write to {ACR} that loads, starts, selects the CPU clock rate/2 for the countdown rate, and asserts the Global Interrupt Enable [GIE]. Prior to the write to {ACR}, TRL and TRH were loaded with 00h and 01h respectively, the timer interrupt was unmasked in the Interrupt Control Register (ICR) by clearing bit 4, and zero instruction wait states were selected in {DCR}. Since the write to {ACR} asserted [GIE], the timer interrupt is enabled and the CPU will vector to the timer interrupt service routine address when the timer reaches a count of zero. The timer interrupt is the lowest priority interrupt and is latched and maintained until it is cleared in software. (See CPU Interrupts section). For very long time intervals, time-outs can be accumulated under software control by writing a one to [TO] in {CCR} allowing the timer to recycle its count down with no other intervention. For time-outs attainable with one count down, stopping the timer will clear the interrupt and [TO]. When the timer interrupt is enabled, the call to the interrupt service routine occurs at different instruction boundaries depending on when the timer interrupt occurs in the instruction cycle. If the timer times out prior to T2, where T2 is the last T-state of an instruction cycle, the call to the interrupt service routine will occur in the next instruction. When the time-out occurs in T2, the call to the interrupt service routine will not occur in the next instruction. It occurs in the second instruction following T2.

The count status of the timer can be monitored by reading {TRL} and/or {TRH}. When the registers are read, the output of the timer, not the value in the input holding registers, is presented to the ALU. Some applications might require monitoring the count status of the timer while it is counting down. Since the timer can time-out between reads of {TRL} and {TRH}, the software should take this fact into consideration. To read back what was written to {TRL} and {TRH}, the timer must first be loaded via [TLD] without starting the timer followed by a one instruction delay before reading {TRL} and {TRH} to allow the output registers to be updated for the load operation.

To determine the time-out delay for a given value in  $\{\text{TRL}\}$  and  $\{\text{TRH}\}$  other than 0000h, the following equation can be used:

$TD = (value in {TRH} {TRL}) * T * k$

where:

k = 2 when [TCS] = 1 or 16 when [TCS] = 0

T = The period of the CPU clock

$\mathsf{TD}=\mathsf{The}$  amount of time delay after the end of the instruction that asserts [TST] in {ACR}

When the value of 0000h is loaded in the timer, the maximum time-out is obtained and is calculated as follows:

#### TD =65536 \* T \* k

With the CPU running full speed with an 18.8 MHz crystal, the maximum single loop time delay attainable would be 55.6 ms ([TCS] = 0). The minimum time delay with the same constraints is 106 ns ([TCS] = 1). For accumulating time-out intervals, the total time delay is simply the number of loops accumulated multiplied by the calculated time delay. The equations above do not account for any overhead for processing the timer interrupt. The added overhead of processing the interrupt may need to be included for precision timing.

#### 2.1.3 Instruction Set

The followng paragraphs introduce the BCP's architecture by discussing addressing modes and briefly discussing the Instruction Set. For detailed explanations and examples of each instruction, refer to the Instruction Set Reference Section.

#### 2.1.3.1 Harvard Architecture Implications

The BCP utilizes a true Harvard Architecture, where the instruction and data memory are organized into two independent memory banks, each with their own address and data buses. Both the Instruction Address Bus and the Instruction Bus are 16 bits wide with the Instruction Address Bus addressing memory by words. (A word of memory is 16 bits long; i.e., 1 word = 2 bytes.) Most of the instructions are one word long. The exceptions are two words long, containing a word of instruction followed by a word of immediate data. The combination of word sized instructions and a word based instruction address bus eliminates the typical instruction alignment problems faced by many CPU's.

The Data Address Bus is 16 bits wide (with the low order 8 bits multiplexed on the Data Bus), and the Data Bus is 8 bits wide (i.e., one byte wide). The Data Address Bus addresses memory by bytes. Most of the BCP's instructions operate on byte-sized operands.

Note that although both instruction addresses and data addresses are 16 bits long, these addresses are for two different buses and, therefore, have two different numerical meanings, (i.e., byte address or word address.) Each instruction determines whether the meaning of a 16-bit address is that of an instruction word address or a data byte address. Little confusion exists though because only the program flow instructions interpret 16-bit addresses as instruction addresses.

#### 2.1.3.2 Addressing Modes

An addressing mode is the mechanism by which an instruction accesses its operand(s). The BCP's architecture supports five basic addressing modes: register, immediate, indexed, immediate-relative, and register-relative. The first two allow instructions to execute the fastest because they require no memory access beyond instruction fetch. The remaining three addressing modes point to data or instruction memory. Typical of a RISC processor, most of the instructions only support the first three addressing modes, with one of the operands always limited to the register addressing mode.

#### **Register Addressing Modes**

There are two terminologies for the register addressing modes: Register and Limited Register. Instructions that allow Register operands can access all the registers in the CPU. Note that only 32 of the 44 CPU registers are available at any given point in time because the lower 12 register locations (R0–R11) access one of two switchable register banks each. (See Section 2.1.1.1, Banked Registers for more information on the CPU register banks.) Instructions that allow the Limited Register operands can access just the first 28 registers of the CPU. Again, note that only 16 of these 28 registers are available at any given point in time. Table 2-1 shows the notations used for the Register and Limited Register operands. Some instructions also imply the use of certain registers, for example the accumulators. This is noted in the discussions of those instructions.

#### Immediate Addressing Modes

The two types of the immediate addressing modes available are: Immediate numbers and Absolute numbers. Immediate numbers are 8 bits of data, (one data byte), that code directly into the instruction word. Immediate numbers may represent data, data address displacements, or relative instruction addresses. Absolute numbers are 16-bit numbers. They code into the second word of two word instructions and they represent absolute instruction addresses. Table 2-2 shows the notations used for both of these addressing modes.

#### **TABLE 2-1. Register Addressing Mode Notations**

| Notation | Type of Register Operand                        | Registers Allowed |

|----------|-------------------------------------------------|-------------------|

| Rs       | Source Register                                 | R0-R31            |

| Rd       | Destination Register                            | R0-R31            |

| Rsd      | Register is both a Source & Destination         | R0-R31            |

| rs       | Limited Source Register                         | R0-R15            |

| rd       | Limited Destination Register                    | R0-R15            |

| rsd      | Limited Register is both a Source & Destination | R0-R15            |

#### **TABLE 2-2. Immediate Addressing Mode Notations**

| Notation | Type of Immediate Operand | Size    |

|----------|---------------------------|---------|

| n        | Immediate Number          | 8 Bits  |

| nn       | Absolute Number           | 16 Bits |

#### Indexed Addressing Modes

Indexed operands involve one of four possible CPU register pairs referred to as the index registers. *Figure 2-4* illustrates how the index registers map into the CPU Register Set. Note that the index registers are 16 bits wide.

Index registers allow for indirect memory addressing and usually contain data memory addresses, although, the LJMP instruction can use index registers to hold instruction memory addresses. Most of the instructions that allow memory indirect addressing, (i.e. the use of index registers), also allow pre-incrementing, post-incrementing, or post-decrementing of the index register contents during instruction execution, if desired. Table 2-3 lists the notations used for the index register modes.

The index registers are set to zero when the BCP's RESET pin is asserted.

# Immediate-Relative and Register-Relative Address Modes

The Immediate-Relative mode adds an unsigned 8-bit immediate number to the index register IZ forming a data byte address. The Register-Relative mode adds the unsigned 8-bit value in the current accumulator, A, to any one of the index registers forming a data byte address. Both of these indirect memory addressing modes are available only on the MOVE instruction. Table 2-4 shows the notation used for these two addressing modes.

#### 2.1.3.3 Instruction Set Overview

The BCP's RISC instruction set contains seven categories of instructions: Data Movement, Integer Arithmetic, Logic, Shift-Rotate, Comparison, Program Flow, and Miscellaneous.

#### **Data Movement Instructions**

The MOVE instruction is responsible for all the data transfer operations that the BCP can perform. Moving one byte at a time, five different types of transfer are allowed: register to register, data memory to register, register to data memory, instruction memory to register, and instruction memory to data memory. Table 2-5 lists all the variations of the MOVE instruction.

#### TABLE 2-3. Index Register Addressing Mode Notations

| Notation | Meaning                                                            |

|----------|--------------------------------------------------------------------|

| [lr]     | Index Register, Contents Not Changed                               |

| [Ir-]    | Index Register, Contents Post-Decremented                          |

| [lr+]    | Index Register, Contents Post-Incremented                          |

| [+lr]    | Index Register, Contents Pre-Incremented                           |

| [mlr]    | General Notation Indicating that Any of the Above Modes Is Allowed |

Note: [] denotes indirect memory addressing and is part of the instruction syntax.

#### **TABLE 2-4. Relative Index Register Mode Notations**

| Notation             | Type of Action Performed to Calculate a Data Memory Address                                                                                        |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [IZ + n]<br>[Ir + A] | $IZ + Immediate Number (unsigned) \rightarrow Data Memory Address Index Register + Current Accumulator (unsigned) \rightarrow Data Memory Address$ |  |

Note: [] denotes indirect memory addressing and is part of the instruction syntax.

#### **TABLE 2-5. Data Movement Instructions**

| Syntax            | Instruction Operation                        | Addressing Modes                     |

|-------------------|----------------------------------------------|--------------------------------------|

| MOVE Rs, Rd       | register → register                          | Register, Register                   |

| MOVE Rs, [mlr]    | register $\rightarrow$ data memory           | Register, Indexed                    |

| MOVE [mlr], Rd    | data memory → register                       | Indexed, Register                    |

| MOVE Rs, [Ir + A] | register $\rightarrow$ data memory           | Register, Register-Relative          |

| MOVE [Ir + A], Rd | data memory → register                       | Register-Relative, Register          |

| MOVE rs, [IZ + n] | register $\rightarrow$ data memory           | Limited Register, Immediate-Relative |

| MOVE [IZ + n], rd | data memory → register                       | Immediate-Relative, Limited Register |

| MOVE n, rd        | instruction memory $\rightarrow$ register    | Immediate, Limited Register          |

| MOVE n, [Ir]      | instruction memory $\rightarrow$ data memory | Immediate, Indexed                   |

#### Integer Arithmetic Instructions

The integer arithmetic instructions operate on 8-bit signed (two's complement) binary numbers. Two arithmetic functions are supported: Add and Subtract. Three versions of the Add and Subtract instructions exist: operand  $\pm$  accumulator, operand  $\pm$  accumulator  $\pm$  carry, and immediate operand  $\,\pm\,$  operand. The first two versions support both the register and indexed addressing modes for the destination operand. These two versions also allow the specification of a separate register or data address for the destination operand so that the sources may retain their integrity; (i.e., true three-operand instructions). Note that the currently active "B" register bank selects which accumulator is used in these instructions. The third version, immediate operand  $\pm$ operand, only supports the register addressing mode for the destination operand with the register as both a source and the destination. Table 2-6 lists the integer arithmetic instructions along with their variations.

#### Logic Instructions

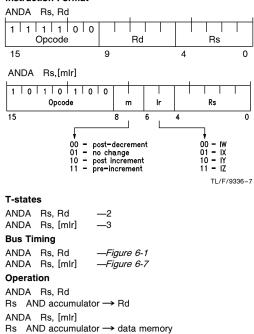

The logic instructions operate on 8-bit binary data. A full set of logic functions is supported by the BCP: AND, OR, eXclusive OR, and Complement. All the logic functions except complement allow either an immediate operand or the currently active accumulator as an implied operand. Complement only allows one register operand which is both the source and destination. The other logic instructions include the following addressing modes: register, indexed, and immediate. As with the integer arithmetic instructions, the integrity of the sources may be maintained by specifying a destination register which is different from the source. Table 2-7 lists all the logic instructions.

#### TABLE 2-6. Integer Arithmetic Instructions

| Syntax |           | Instruction Operation                              | Addressing Modes            |  |

|--------|-----------|----------------------------------------------------|-----------------------------|--|

| ADD    | n, rsd    | register + n → register                            | Immediate, Limited Register |  |

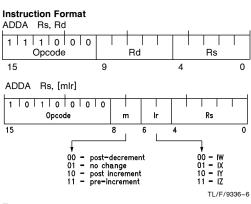

| ADDA   | Rs, Rd    | $Rs + accumulator \rightarrow Rd$                  | Register, Register          |  |

| ADDA   | Rs, [mlr] | Rs + accumulator → data memory                     | Register, Indexed           |  |

| ADCA   | Rs, Rd    | $Rs + accumulator + carry \rightarrow Rd$          | Register, Register          |  |

| ADCA   | Rs, [mlr] | Rs + accumulator + carry $\rightarrow$ data memory | Register, Indexed           |  |

| SUB    | n, rsd    | register – n → register                            | Immediate, Limited Register |  |

| SUBA   | Rs, Rd    | Rs – accumulator → Rd                              | Register, Register          |  |

| SUBA   | Rs, [mlr] | Rs – accumulator → data memory                     | Register, Indexed           |  |

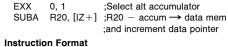

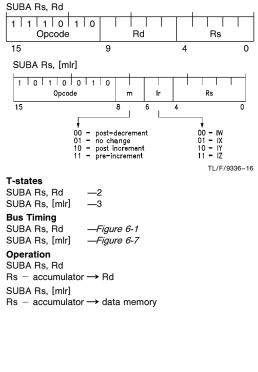

| SBCA   | Rs, Rd    | Rs – accumulator – carry $\rightarrow$ Rd          | Register, Register          |  |