# MiDAS1.1 Family: EPROM/ROM 8-bit Turbo Microcontrollers

Rev. 1.6 September 2005

Copyright CoreRiver Semiconductor Co., Ltd. 2005 All Rights Reserved

Page 1 of 211

- CoreRiver Semiconductor reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.

- Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

- The CoreRiver Semiconductor products listed in this document are intended for usage in general electronics applications. These CoreRiver Semiconductor products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury.

# **Table of Contents**

| 1  | PRODU                        | CT OVERVIEWS                                          | 9    |  |  |  |

|----|------------------------------|-------------------------------------------------------|------|--|--|--|

| 2  | FEATU                        | RES                                                   | . 11 |  |  |  |

| 3  | BLOCK                        | DIAGRAM                                               | . 13 |  |  |  |

| 4  | PIN CO                       | NFIGURATIONS                                          | . 15 |  |  |  |

| 5  | PIN DES                      | SCRIPTION                                             | . 17 |  |  |  |

| 6  |                              | ONAL DESCRIPTION                                      |      |  |  |  |

| -  |                              |                                                       |      |  |  |  |

| 6  |                              |                                                       |      |  |  |  |

|    | 6.1.1                        | Memory Organization                                   |      |  |  |  |

|    | 6.1.2                        | Special Function Registers (SFRs) Map and Description |      |  |  |  |

|    | 6.1.3                        | Instruction Set Summary                               |      |  |  |  |

|    | 6.1.4                        | CPU Timing                                            |      |  |  |  |

| 6  | 6.2 Per                      | RIPHERAL DESCRIPTION                                  |      |  |  |  |

|    | 6.2.1                        | I/O Ports                                             | 28   |  |  |  |

|    | 6.2.2                        | LVD (Low Voltage Detector)                            | 48   |  |  |  |

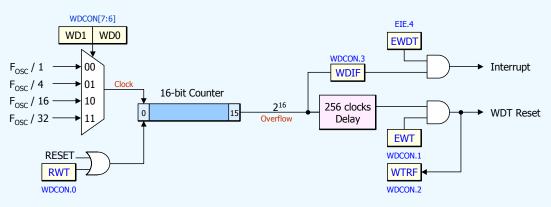

|    | 6.2.3                        | WDT (Watchdog Timer)                                  | 51   |  |  |  |

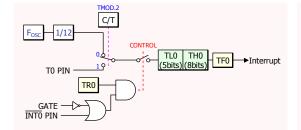

|    | 6.2.4                        | Timer 0/1                                             | 55   |  |  |  |

|    | 6.2.5                        | UART (Universal Asynchronous Rx/Tx)                   | 62   |  |  |  |

|    | 6.2.6                        | PWM (Pulse Width Modulator)                           | . 67 |  |  |  |

|    | 6.2.7                        | ADC (Analog to Digital Converter)                     | . 72 |  |  |  |

|    | 6.2.8                        | Interrupt                                             | . 79 |  |  |  |

|    | 6.2.9                        | Reset Circuit                                         | . 93 |  |  |  |

|    | 6.2.10                       | Clock Circuit (On-chip oscillators)                   | . 97 |  |  |  |

|    | 6.2.11                       | Power Management                                      | 102  |  |  |  |

| 7  | ABSOL                        | UTE MAXIMUM RATINGS                                   | 105  |  |  |  |

| 8  | DC CHA                       | ARACTERISTICS                                         | 107  |  |  |  |

| ε  | 8.1 Gen                      | VERAL DC CHARACTERISTICS                              | 107  |  |  |  |

| ε  | 3.2 AD                       | C Specifications                                      | 108  |  |  |  |

| 9  | АС СНА                       | ARACTERISTICS                                         | 109  |  |  |  |

| 10 | 0 PACKAGE DIMENSION 111      |                                                       |      |  |  |  |

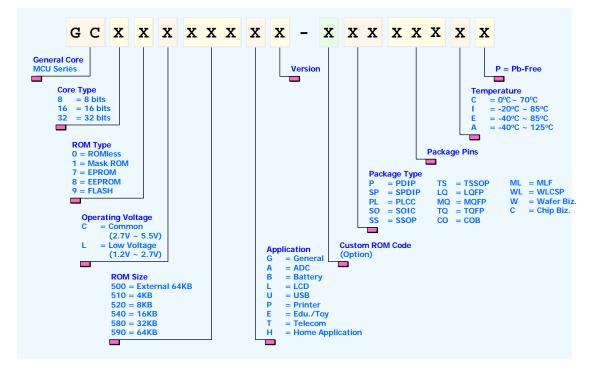

| 11 | PRODUCT NUMBERING SYSTEM 115 |                                                       |      |  |  |  |

#

| 12 | Α   | PPENDIX A: INSTRUCTION SET                                        | 117 |

|----|-----|-------------------------------------------------------------------|-----|

| 13 | A   | PPENDIX B: SFR DESCRIPTION                                        | 185 |

| 13 | .1  | P0 (80H) : Port 0 Register                                        | 185 |

| 13 | .2  | SP (81H) : STACK POINTER REGISTER                                 | 186 |

| 13 | .3  | DPL (82H) : DATA POINTER LOW REGISTER                             | 186 |

| 13 | .4  | DPH (83h) : DATA POINTER HIGH REGISTER                            | 186 |

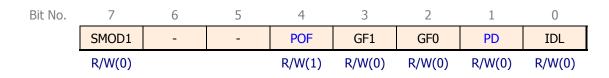

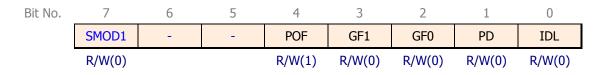

| 13 | .5  | PCON (87H) : Power Control Register                               | 187 |

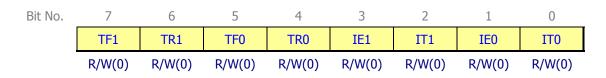

| 13 | .6  | TCON (88h) : TIMER/COUNTER 0/1 CONTROL REGISTER                   | 188 |

| 13 | .7  | TMOD (89H) : TIMER/COUNTER 0 MODE CONTROL REGISTER                | 189 |

| 13 | .8  | TL0 (8AH) : TIMER/COUNTER 0 LOW BYTE REGISTER                     | 190 |

| 13 | .9  | TL1 (8BH) : TIMER/COUNTER 1 LOW BYTE REGISTER                     | 190 |

| 13 | .10 | TH0 (8CH) : TIMER/COUNTER 0 HIGH BYTE REGISTER                    | 190 |

| 13 | .11 | TH1 (8DH) : TIMER/COUNTER 1 HIGH BYTE REGISTER                    | 190 |

| 13 | .12 | P1 (90н) : Port 1 Register                                        | 191 |

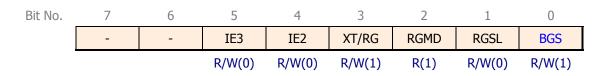

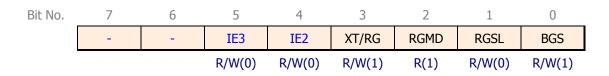

| 13 | .13 | EXIF (91h) : External Interrupt Flag Register                     | 192 |

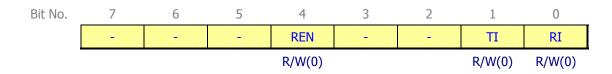

| 13 | .14 | SCON (98H) : Serial Port Control Register                         | 193 |

| 13 | .15 | SBUF (99h) : Serial Data Buffer Register                          | 193 |

| 13 | .16 | Р2 (А0н) : Port 2 Register                                        | 194 |

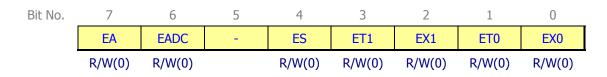

| 13 | .17 | IE (A8H) : INTERRUPT ENABLE REGISTER                              | 195 |

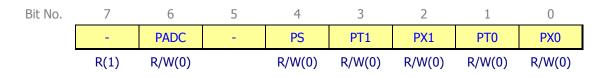

| 13 | .18 | IP (B8H) : INTERRUPT PRIORITY REGISTER                            | 196 |

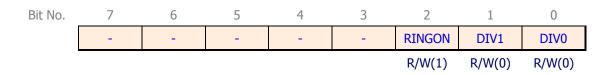

| 13 | .19 | OSCICN (BEH) : INTERNAL RING OSCILLATOR CONTROL REGISTER          | 197 |

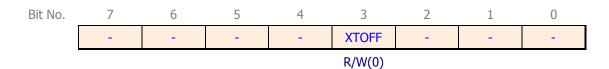

| 13 | .20 | PMR (C4h) : Power Management Register                             | 197 |

| 13 | .21 | STATUS (C5H) : CRYSTAL STATUS REGISTER                            | 198 |

| 13 | .22 | PSW (D0H) : Program Status Word Register                          | 199 |

| 13 | .23 | P0TYPE (D4H) : PORT 0 TYPE CONTROL REGISTER                       | 200 |

| 13 | .24 | P1TYPE (D5h) : Port 1 Type Control Register                       | 200 |

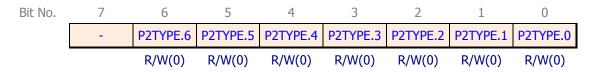

| 13 | .25 | P2TYPE (D6H) : PORT 2 TYPE CONTROL REGISTER                       | 200 |

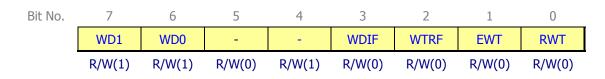

| 13 | .26 | WDCON (D8H) : WATCHDOG CONTROL REGISTER                           | 201 |

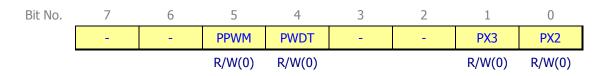

| 13 | .27 | PWMCON (DCH) : PWM CONTROL REGISTER                               | 202 |

| 13 | .28 | РWMD (DEн) : PWM DUTY DATA REGISTER                               | 203 |

| 13 | .29 | ACC/A (E0H) : ACCUMULATOR                                         | 203 |

| 13 | .30 | ADCSELH (E1H) : ADC CHANNEL SELECTION HIGH REGISTER               | 204 |

| 13 | .31 | ADCSEL (E2H) : ADC CHANNEL SELECTION LOW & MUX SELECTION REGISTER | 205 |

| 13 | .32 | ALTSEL (E3H) : ALTERNATIVE FUNCTION SELECTION REGISTER            | 206 |

| 13 | .33 | P0SEL (E4H) : PORT 0 PULL-UP CONTROL REGISTER                     | 207 |

| 13.34 | P1SEL (E5H) : PORT 1 PULL-UP CONTROL REGISTER       | 207 |

|-------|-----------------------------------------------------|-----|

| 13.35 | P2SEL (E6H) : PORT 2 PULL-UP CONTROL REGISTER       | 207 |

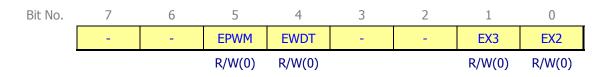

| 13.36 | EIE (E8H) : EXTENDED INTERRUPT ENABLE REGISTER      | 208 |

| 13.37 | ADCR (EEH) : ADC RESULT HIGH REGISTER               | 208 |

| 13.38 | ADCON (EFH) : ADC CONTROL & ADC RESULT LOW REGISTER | 209 |

| 13.39 | B (F0н) : B REGISTER                                | 209 |

| 13.40 | P0DIR (F4H) : PORT 0 INPUT/OUTPUT CONTROL REGISTER  | 210 |

| 13.41 | P1DIR (F5H) : PORT 1 INPUT/OUTPUT CONTROL REGISTER  | 210 |

| 13.42 | P2DIR (F6H) : PORT 2 INPUT/OUTPUT CONTROL REGISTER  | 210 |

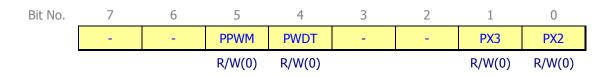

| 13.43 | EIP (F8H) : EXTENDED INTERRUPT PRIORITY REGISTER    | 211 |

# List of Figures

| Figure 3-1 Overall Block Diagram                                                             | 13 |

|----------------------------------------------------------------------------------------------|----|

| Figure 4-1 Pin Configuration                                                                 |    |

| Figure 6-1 Memory Organization                                                               |    |

| Figure 6-2 Comparative Timing of the MiDAS1.1 family and Intel 80C52                         |    |

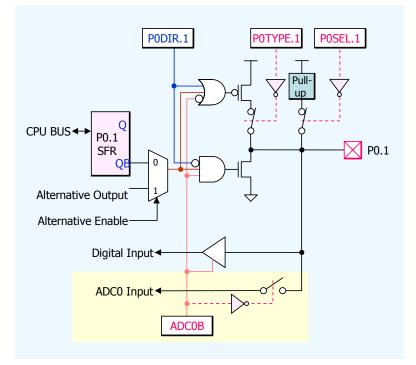

| Figure 6-3 Configuration of PORT 0                                                           |    |

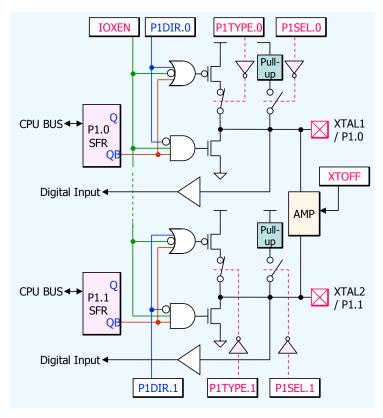

| Figure 6-4 Configuration of PORT1                                                            |    |

| Figure 6-5 Configuration of PORT2                                                            |    |

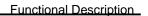

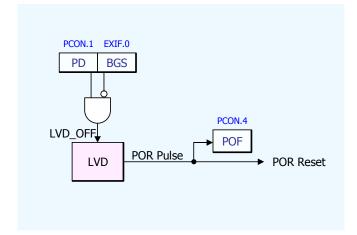

| Figure 6-6 Power-On Reset/Power-fail Reset and Power-fail interrupt (V <sub>RST</sub> =2.3V) |    |

| Figure 6-7 LVD Block Diagram                                                                 |    |

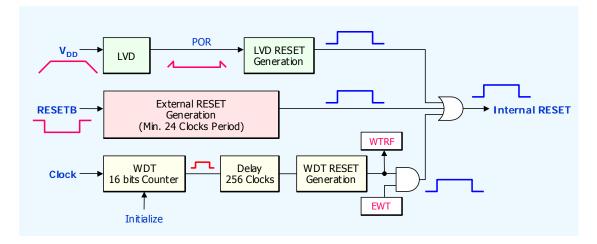

| Figure 6-8 Block Diagram for Watchdog Timer                                                  | 51 |

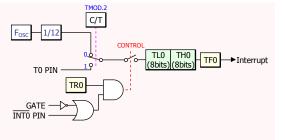

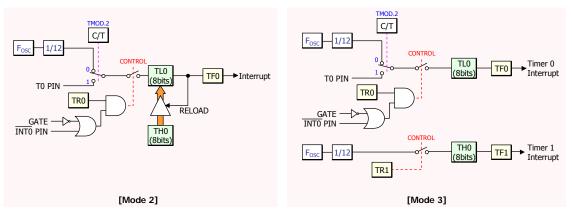

| Figure 6-9 Timer/Counter 0 in Mode 0/1/2/3                                                   | 57 |

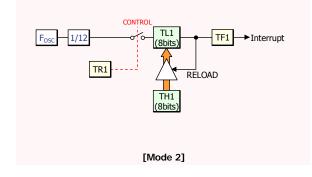

| Figure 6-10 Timer/Counter 1 in Mode 2                                                        |    |

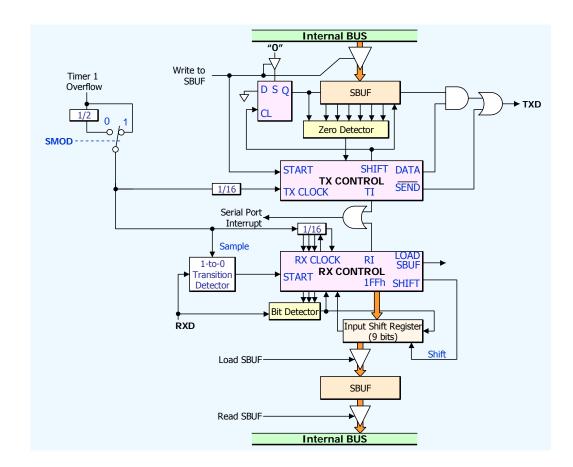

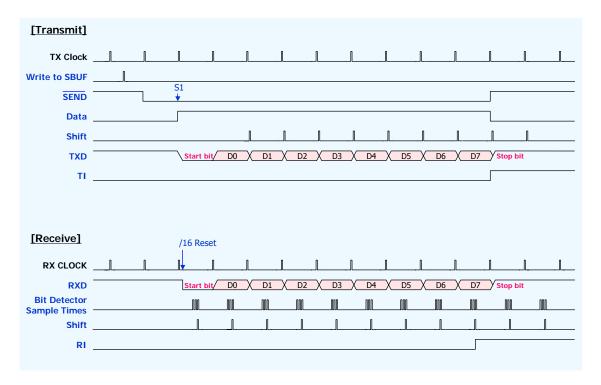

| Figure 6-11 UART Mode 1                                                                      | 63 |

| Figure 6-12 UART Mode 1 Timing                                                               |    |

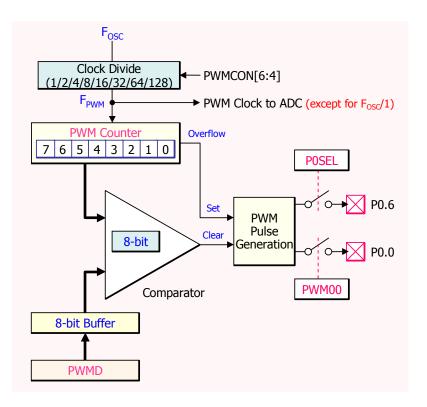

| Figure 6-13 Functional block diagram                                                         |    |

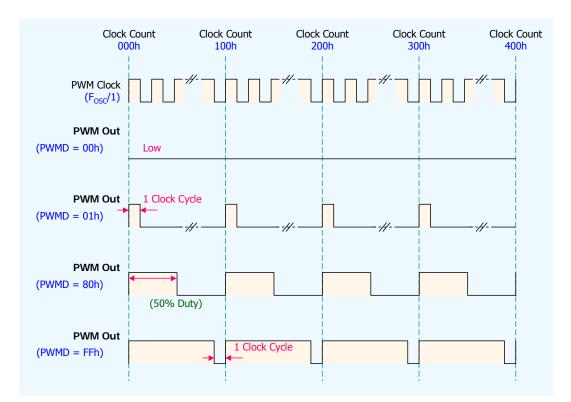

| Figure 6-14 PWM basic timing diagram                                                         | 69 |

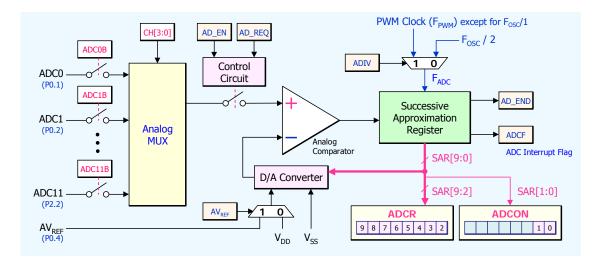

| Figure 6-15 ADC Circuit Diagram                                                              | 73 |

| Figure 6-16 A/D Converter Timing Diagram                                                     | 75 |

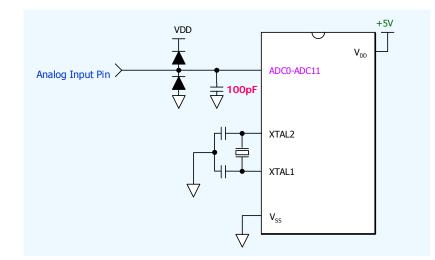

| Figure 6-17 Recommended A/D Converter Circuit for more high accuracy                         | 75 |

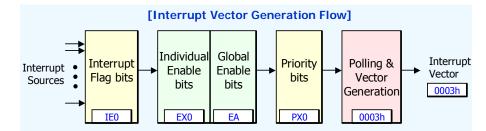

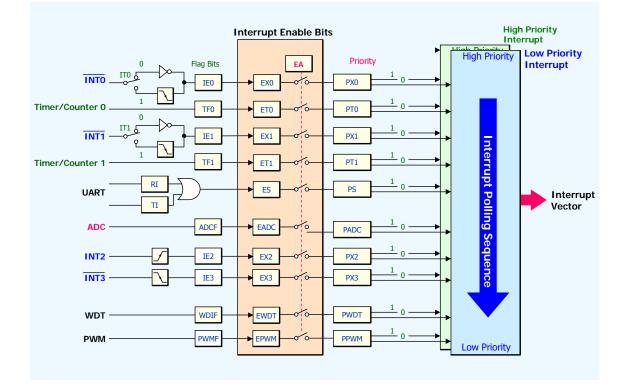

| Figure 6-18 Interrupt Vector Generation Flow                                                 | 80 |

| Figure 6-19 Hierarchy of Interrupt Priority                                                  | 81 |

| Figure 6-20 Three Reset Resources                                                            |    |

#

# MiDAS1.1 Family

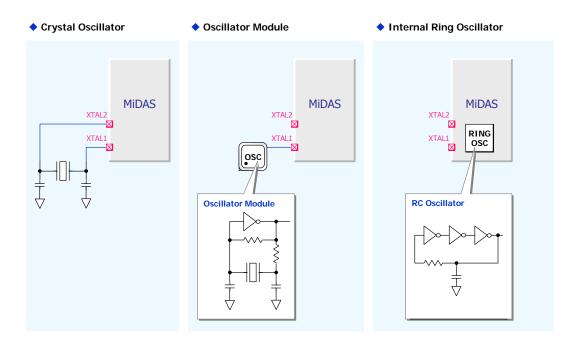

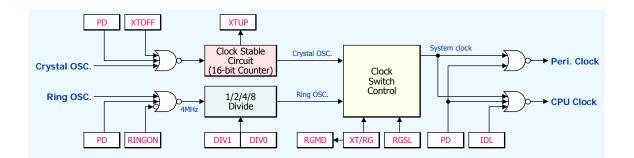

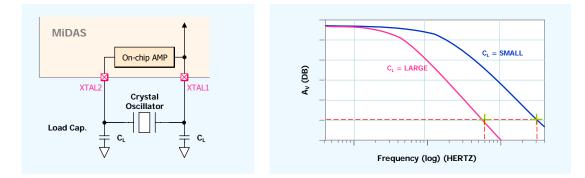

| Figure 6-21 Configuration for Clock                       | 97  |

|-----------------------------------------------------------|-----|

| Figure 6-22 Clock Circuit                                 | 98  |

| Figure 6-23 The Load Capacitor versus Operating Frequency | 98  |

| Figure 6-24 Power Management Circuit                      | 102 |

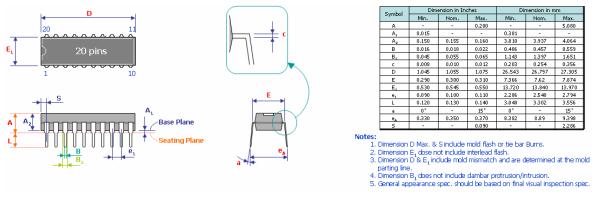

| Figure 10-1 SPDIP 20-pin Package Dimension                | 111 |

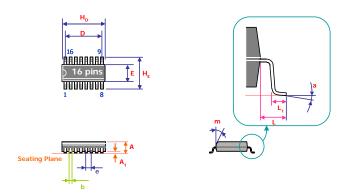

| Figure 10-2 SPDIP-16pin Package Dimension                 | 111 |

| Figure 10-3 SPDIP-8pin Package Dimension                  | 111 |

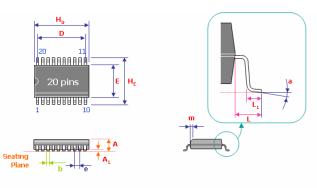

| Figure 10-4 SOIC 20-pin Package Dimension                 | 112 |

| Figure 10-5 SOIC-16pin Package Dimension                  | 112 |

| Figure 10-6 SOIC-8pin Package Dimension                   | 112 |

| Figure 10-7 TSSOP-16pin Package Dimension                 | 112 |

| Figure 11-1 Product Numbering System                      | 115 |

# **List of Tables**

| Table 5-1 Pin Description                                                          | 17  |

|------------------------------------------------------------------------------------|-----|

| Table 6-1 SFR map ( * = <mark>bit addressable SFR</mark> )                         | 21  |

| Table 6-2 Summary of SFRs ( * : undefined value )                                  | 22  |

| Table 6-3 Summary of Instruction Set                                               | 23  |

| Table 6-4 Read-Modify-Write Instructions                                           | 46  |

| Table 6-5 Alternative Functions                                                    | 47  |

| Table 6-6 Time-out Values for the Watchdog Timer                                   | 52  |

| Table 6-7 Summary of Mode in UART                                                  | 64  |

| Table 6-8 Example of Baudrate                                                      | 65  |

| Table 6-9 PWM clock rate by PWMCON[6:4]                                            | 68  |

| Table 6-10 Example of Conversion Timing versus Frequency                           | 74  |

| Table 6-11 Priority Structure of Interrupts                                        | 80  |

| Table 6-12 Recommended Load Capacitor in Crystal Oscillator (V <sub>DD</sub> = 5V) | 97  |

| Table 6-13 System Clock Configuration                                              | 98  |

| Table 6-14 Status of External Pins during IDLE and Power-down Modes                | 104 |

| Table 7-1 Absolute Maximum Ratings                                                 | 105 |

| Table 8-1 General DC Characteristics                                               | 107 |

| Table 8-2 ADC Specifications                                                       | 108 |

| Table 9-1 AC Characteristics                                                       | 109 |

| Table 12-1 Note on Instruction Set and Addressing Modes                            | 117 |

# **1 Product Overviews**

CoreRiver's MiDAS1.1 family is a group of fast 80C52 compatible microcontrollers without wasted clock and memory cycles. Four clocks per one machine cycle are consumed in a redesigned processor core. As a result, every 8052 instruction is executed about 3 times faster than that of traditional 80C52.

The MiDAS1.1 family offers three timer/counters, a serial port, up to 18 I/O ports, eleven-channel 10-bit ADC (Analog to Digital Converter), one-channel 8-bit PWM (Pulse Width Modulator), a Watchdog timer, and LVD (Low Voltage Detector) as peripherals.

The MiDAS1.1 family provides power saving modes to reduce power consumption in the power-critical applications and noise tolerant scheme.

To support an easy target system development, user-friendly MDS (MCU Development System) called as GENSYS and easy-to-use training system is also provided.

# 2 Features

- 8-bit Turbo 80C52 architecture

- 4 cycles/1 machine cycle

- Instruction level compatible with Intel 80C52

- 0/4Kbyte Mask ROM

- 0/4Kbyte Erasable Programmable ROM (EPROM)

- 128byte RAM

- Extended 2.4V to 5.5V supply voltage

- Operating Frequency

- ✓ Max. 20MHz @ 4.5 ~ 5.5V

- ✓ Max. 10MHz @ 2.4 ~ 3.3V

- -20 °C to 85 °C operating temperature

- Fully Programmable 18 I/O pins

- ✓ Pull-up controlled by S/W

- ✓ Open-drain Output

- ✓ Push-pull Output

- Low Voltage Detector (LVD)

- 16-bit Programmable Watchdog Timer (WDT)

- Two 16-bit Timer/Counters

- Full-Duplex UART

- ✓ Automatic address recognition

- 1-channel 8-bit high speed Pulse Width Modulator (PWM)

- 12-channel 10-bit Analog to Digital Converter (ADC)

- ✓ Max. 100K SPS (samples per second) @ 8MHz

- ✓ Programmable input clock frequency

- 10 interrupt sources including 4 external

- ✓ Timer 0/1, UART, ADC, PWM, WDT, and four external

- ✓ Two-level interrupt priority

- Reset scheme

- ✓ On-chip power-on-reset (POR)

- ✓ External reset

- ✓ Low voltage detector reset

- ✓ Optional Watchdog timer reset

- Power consumption

- ✓ Active current: Max 10mA @ 5V, 20MHz

- ✓ Stop current: Max 1uA

- ESD protection up to 2,000V

- Latch-up protection up to ±200mA

- Package : 8/16/20-SPDIP, 8/16/20-SOIC, and 16-TSSOP

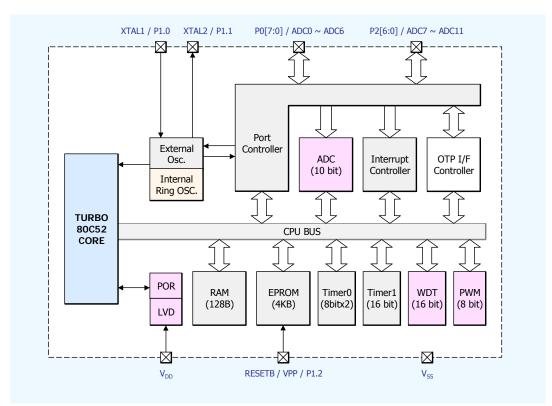

# 3 Block Diagram

Figure 3-1 shows the functional block diagram of MiDAS1.1 Family. The CPU fetches instructions from the program memory (ROM or EPROM) and executes them. Data are processed and read from or written to data memory (RAM) or integrated peripherals via special function registers(SFRs). For data processing inside the CPU, the arithmetic and logic unit (ALU) is used.

Data processing as well as reading and writing is supported by a set of registers. Except for the program counter (PC) and the four general-purpose register banks, these registers are mapped to the special function register area. The program counter resides inside the CPU, and the four register banks are mapped to the internal RAM.

Figure 3-1 Overall Block Diagram

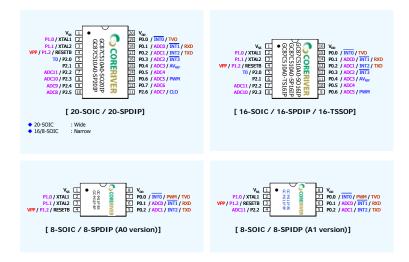

# 4 Pin Configurations

The MiDAS1.1 family supports a variety of package, e.g. 8/16/20-SPDIP, 8/16/20-SOIC and 16-TSSOP. The detailed pin configuration is shown in Figure 4-1.

Figure 4-1

**Figure 4-1 Pin Configuration**

# **5** Pin Description

# Table 5-1 Pin Description

| Symbol                    | Direction    | Description                                                                                                                                                       | Share Pins                                           |

|---------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| V <sub>DD</sub>           | Input        | Voltage power source                                                                                                                                              | -                                                    |

| V <sub>SS</sub>           | Input        | Voltage power ground                                                                                                                                              | -                                                    |

| RESETB /<br>VPP /<br>P1.2 | Input/Output | <ul> <li>External reset input signal (Default)</li> <li>Bit Programmable</li> <li>Open-drain output</li> </ul>                                                    | VPP (11.5V)                                          |

| XTAL1 / P1.0              | Input/Output | <ul> <li>Crystal input/output (Default)</li> <li>Bit Programmable with Schmitt trigger</li> </ul>                                                                 | Crystal input                                        |

| XTAL2 / P1.1              | πραγΟατρατ   | - Optional Pull-up control Enable<br>- Open-drain output<br>- Push-pull output                                                                                    | Crystal output<br>(only A0 version)                  |

| P0[7:0] Input/Output      |              | <ul> <li>Bit Programmable with Schmitt trigger</li> <li>Optional Pull-up control Enable</li> <li>Open-drain output</li> <li>Push-pull output (Default)</li> </ul> | RX, TX, TVO,<br>INT0B ~ INT3,<br>ADC0 ~ ADC6,<br>PWM |

| P2[6:0]                   | Input/Output | <ul> <li>Bit Programmable with Schmitt trigger</li> <li>Optional Pull-up control Enable</li> <li>Open-drain output</li> <li>Push-pull output (default)</li> </ul> | ADC7 ~ ADC11<br>CLO<br>AV <sub>REF</sub>             |

# **6** Functional Description

# 6.1 CPU Description

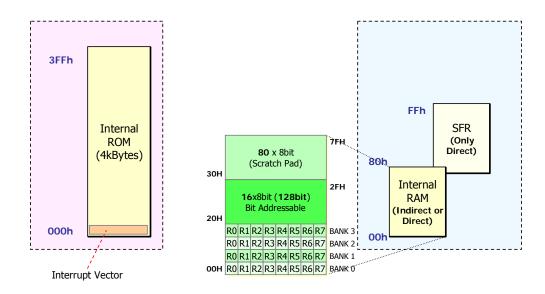

# 6.1.1 Memory Organization

MiDAS1.1 family has separate address spaces for program and data memory. The logical separation of program and data memory allows the data memory to be accessed by 8-bit addresses, which can be quickly stored and manipulated by an 8-bit CPU.

Program Memory can only be read, not written to. There can be up to 4K bytes of Program Memory.

#### Figure 6-1 Memory Organization

#### 6.1.1.1 Program Memory

The left part of Figure 6-1 shows a map of the Program Memory. After reset, the CPU begins execution from location 0000H.

As shown in Figure 6-1, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0 (INT0B), for example, is assigned to location 0003h. If External Interrupt 0 is going to be used, its service routine must begin at location 0003h. If the interrupt is not going to be used, its service

location is available as general purpose Program Memory.

The interrupt service locations are spaced at 8-byte intervals: 0003h for External Interrupt 0, 000Bh for Timer 0, 0013h for External Interrupt 1, 001Bh for Timer 1 and etc. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8-byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use.

Program Memory addresses are always 16bits wide, even though the actual amount of Program Memory used may be less than 4K bytes.

Program Memory can only be read, not written to. There can be up to 4K bytes of Program Memory.

# 6.1.1.2 Data Memory

The internal data memory address space is divided into three basic, physical separate and distinct blocks as shown in the right part of Figure 6-1:

- The lower 128byte of internal data RAM located to the address range 00h 7Fh.

- The 128byte area for special function register (SFR) located to the address range 80h FFh.

The special function registers (SFRs) are accessible only by direct addressing mode (address is part of the instruction).

# 6.1.1.2.1 Bit-addressable Memory Locations

In the lower internal data RAM, a bit-addressable area of 128 freely programmable, directly addressable bits are located at byte addresses 20h – 2Fh. Bit 0 of the data byte at 20h has bit address 00H, bit 7 of the data byte at 2Fh has bit address 7Fh.

In the special function register area, all SFRs, which are located at addresses with address bit 0-2 equal 0 (addresses 80h, 88h, 90h, ..., F0h, F8h), are bit-addressable SFRs.

# 6.1.1.2.2 Register Banks

The lower 32 locations of the lower internal data RAM are assigned to four banks with eight general purpose registers (GPRs) each. Only one of these banks can be enabled at a time to be used as general purpose registers.

# 6.1.2 Special Function Registers (SFRs) Map and Description

The MiDAS1.1 family uses Special Function Registers (SFRs) to control and monitor peripherals and their modes.

The SFRs are located at 80h-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where one wishes to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0h or 8h. The list of SFRs is as follows. Refer to Appendix B for more details about SFRs.

|     |         |         | 0      | 0      |        | 0      | 0      |       |     |

|-----|---------|---------|--------|--------|--------|--------|--------|-------|-----|

| F8h | * EIP   |         |        |        |        |        |        |       | FFh |

| F0h | * B     |         |        |        | PODIR  | P1DIR  | P2DIR  |       | F7h |

| E8h | * EIE   |         |        |        |        |        | ADCR   | ADCON | EFh |

| E0h | * ACC   | ADCSELH | ADCSEL | ALTSEL | POSEL  | P1SEL  | P2SEL  |       | E7h |

| D8h | * WDCON |         |        |        | PWMCON |        | PWMD   |       | DFh |

| D0h | * PSW   |         |        |        | POTYPE | P1TYPE | P2TYPE |       | D7h |

| C8h |         |         |        |        |        |        |        |       | CFh |

| C0h |         |         |        |        | PMR    | STATUS |        |       | C7h |

| B8h | * IP    |         |        |        |        |        | OSCICN |       | BFh |

| B0h |         |         |        |        |        |        |        |       | B7h |

| A8h | * IE    |         |        |        |        |        |        |       | AFh |

| A0h | * P2    |         |        |        |        |        |        |       | A7h |

| 98h | * SCON  | SBUF    |        |        |        |        |        |       | 9Fh |

| 90h | * P1    | EXIF    |        |        |        |        |        |       | 97h |

| 88h | * TCON  | TMOD    | TL0    | TL1    | TH0    | TH1    |        |       | 8Fh |

| 80h | * P0    | SP      | DPL    | DPH    |        |        |        | PCON  | 87h |

#### Table 6-1 SFR map ( \* = bit addressable SFR )

Note: Newly added SFRs at MiDAS1.1 family are in **bold style**.

# Table 6-2 Summary of SFRs ( \* : undefined value )

| Register Name                                | Symbol  | Address | Reset<br>Value   | Bit Addressable |

|----------------------------------------------|---------|---------|------------------|-----------------|

| Port 0                                       | P0      | 80h     | 11111111         | Yes             |

| Stack Pointer                                | SP      | 81h     | 00000111         | No              |

| Data Pointer Low Byte                        | DPL     | 82h     | 00000000         | No              |

| Data Pointer High Byte                       | DPH     | 83h     | 00000000         | No              |

| Power Control                                | PCON    | 87h     | 0**10000         | No              |

| Timer/Counter 0/1 Control                    | TCON    | 88h     | 00000000         | Yes             |

| Timer/Counter 0 Mode Control                 | TMOD    | 89h     | ****0000         | No              |

| Timer/Counter 0 Low Byte                     | TL0     | 8Ah     | 00000000         | No              |

| Timer/Counter 1 Low Byte                     | TL1     | 8Bh     | 00000000         | No              |

| Timer/Counter 0 High Byte                    | TH0     | 8Ch     | 00000000         | No              |

| Timer/Counter 1 High Byte                    | TH1     | 8Dh     | 00000000         | No              |

| Port 1                                       | P1      | 90h     | *****111         | Yes             |

| Added External Interrupt &<br>LVD Control    | EXIF    | 91h     | <b>**</b> 000101 | No              |

| Serial Control                               | SCON    | 98h     | ***0**00         | No              |

| Serial Buffer                                | SBUF    | 99h     | 00000000         | No              |

| Port 2                                       | P2      | A0h     | *1111111         | Yes             |

| Interrupt Enable control                     | IE      | A8h     | 00*0000          | Yes             |

| Interrupt Priority                           | IP      | B8h     | 10*00000         | Yes             |

| Internal Ring Oscillator Control             | OSCICN  | BEh     | ****100          | No              |

| Power Management Control                     | PMR     | C4h     | ****0***         | No              |

| Crystal Status                               | STATUS  | C5h     | ***0****         | No              |

| Program Status Word                          | PSW     | D0h     | 00000000         | Yes             |

| Port 0 Type Control                          | POTYPE  | D4h     | 11111111         | No              |

| Port 1 Type Control                          | P1TYPE  | D5h     | *****111         | No              |

| Port 2 Type Control                          | P2TYPE  | D6h     | *1111111         | No              |

| Watchdog Timer Control                       | WDCON   | D8h     | 11010000         | Yes             |

| PWM Control                                  | PWMCON  | DCh     | 000*000          | No              |

| PWM Duty Data                                | PWM0D   | DEh     | 00000000         | No              |

| Accumulator                                  | ACC     | E0h     | 00000000         | Yes             |

| ADC Channel Input Enable High                | ADCSELH | E1h     | 11111111         | No              |

| ADC Channel Input Enable Low & Mux Selection | ADCSEL  | E2h     | 11111111         | No              |

| Alternative function Selection               | ALTSEL  | E3h     | 000000**         | No              |

| Port 0 Pull-up Control                       | POSEL   | E4h     | 00000000         | No              |

| Port 1 Pull-up Control                       | P1SEL   | E5h     | *****11          | No              |

| Port 2 Pull-up Control                       | P2SEL   | E6h     | *0000000         | No              |

| Extended Interrupt Enable                    | EIE     | E8h     | **00**00         | Yes             |

# MiDAS1.1 Family

| ADC Result High              | ADCR  | EEh | 00000000 | No  |

|------------------------------|-------|-----|----------|-----|

| ADC Control & ADC Result Low | ADCON | EFh | 00100000 | No  |

| B Register                   | В     | F0h | 00000000 | Yes |

| Port 0 Input/Output Control  | PODIR | F4h | 11111111 | No  |

| Port 1 Input/Output Control  | P1DIR | F5h | *****111 | No  |

| Port 2 Input/Output Control  | P2DIR | F6h | *1111111 | No  |

| Extended Interrupt Priority  | EIP   | F8h | **00**00 | Yes |

**Caution:** Don't touch \* bits. Updating these bits will cause the malfunctions. Especially following bits of SFR should not be updated.

# 6.1.3 Instruction Set Summary

The instruction set of the MiDAS1.1 family is compatible with that of the well-known 80C52. The MiDAS1.1 family has a special internal architecture and different timing to the standard 80C52. This means the relative duration of the individual instructions, i.e. the number of clock cycles per instructions, is different to that of 80C52.

Refer to Appendix A for more details about instruction set.

| Туре       | Instruction | Description             |

|------------|-------------|-------------------------|

|            | ADD         | Addition                |

|            | ADDC        | Addition with Carry     |

|            | SUBB        | Subtraction with Borrow |

| Arithmatic | INC         | Increment               |

| Arithmetic | DEC         | Decrement               |

|            | MUL         | Multiply                |

|            | DIV         | Divide                  |

|            | DA          | Decimal Adjust          |

| Logical    | ANL         | Logical AND             |

|            | ORL         | Logical OR              |

|            | XRL         | Logical Exclusive OR    |

|            | CLR         | Clear                   |

|            | CPL         | Complement              |

|            | RL          | Rotate Left             |

|            | RLC         | Rotate Left with Carry  |

|            | RR          | Rotate Right            |

# Table 6-3 Summary of Instruction Set

|               | RRC   | Rotate Right with Carry        |  |  |  |

|---------------|-------|--------------------------------|--|--|--|

|               | SWAP  | Swap Nibbles                   |  |  |  |

|               | MOV   | Move Data                      |  |  |  |

|               | MOVC  | Move Code                      |  |  |  |

| Data Transfor | PUSH  | Push                           |  |  |  |

| Data Transfer | POP   | Рор                            |  |  |  |

|               | ХСН   | Exchange                       |  |  |  |

|               | XCHD  | Exchange Lo-digit              |  |  |  |

|               | CLR   | Clear Bit                      |  |  |  |

|               | SETB  | Set Bit                        |  |  |  |

|               | CPL   | Complement Bt                  |  |  |  |

|               | ANL   | AND Bi                         |  |  |  |

|               | ORL   | OR Bit                         |  |  |  |

| Boolean       | MOV   | Move Bit                       |  |  |  |

|               | JC    | Jump if Carry is set           |  |  |  |

|               | JNC   | Jump if Carry is not set       |  |  |  |

|               | JB    | Jump if Bit is set             |  |  |  |

|               | JNB   | Jump if Bit is not set         |  |  |  |

|               | JBC   | Jump if Bit is set & Clear     |  |  |  |

|               | ACALL | Absolute Call                  |  |  |  |

|               | LCALL | Long Call                      |  |  |  |

|               | RET   | Return from Subroutine         |  |  |  |

|               | RETI  | Return from Interrupt          |  |  |  |

|               | AJMP  | Absolute Jump                  |  |  |  |

|               | LJMP  | Long Jump                      |  |  |  |

| Branch        | SJMP  | Short Jump                     |  |  |  |

|               | JMP   | Jump with DPTR                 |  |  |  |

|               | JZ    | Jump if ACC is zero            |  |  |  |

|               | JNZ   | Jump if ACC is not zero        |  |  |  |

|               | CJNE  | Compare and Jump if not equal  |  |  |  |

|               | DJNZ  | Decrement and Jump if not zero |  |  |  |

|               | NOP   | No Operation                   |  |  |  |

#### 6.1.3.1 Addressing Modes

The operands used in the instructions can be addressed in different modes. The MiDAS1.1 family uses six different addressing modes to this end:

- Immediate

- Direct

- Indirect

- Index

- Register

- Register-specific

#### 6.1.3.1.1 Immediate Addressing Mode

Immediate addressing mode means that constants can be loaded to registers. The constant is part of the instruction in program memory.

#### **Examples:**

| MOV R3, #0FFh       | R3 is loaded with constant value 0FFh        |

|---------------------|----------------------------------------------|

| ORL PSW, #00000101b | Logical OR operation with PSW and 0000 0101b |

| MOV DPTR, #1243h    | Load data pointer with constant value 1234h  |

# 6.1.3.1.2 Direct Addressing Mode

In direct addressing mode, the operand is specified by an 8-bit address field, which is part of the instruction.

**Note**: The SFRs can be accessed only in this mode. And the lower 128 bytes of the RAM can be addressed in this mode, too.

#### **Examples:**

| MOV A, TCON      | TCON is the 8-bit address of the SFR TCON.                      |  |  |

|------------------|-----------------------------------------------------------------|--|--|

| MOV R4, variable | Variable is the 8-bit address of a memory location in the lower |  |  |

|                  | part of the RAM.                                                |  |  |

#### 6.1.3.1.3 Indirect Addressing Mode

In indirect addressing mode, the operand is specified by an 8-bit that is stored in a register. And the content of either R0 or R1 (in the selected register bank) is used.

Note: The lower 128 bytes of the RAM can be addressed by using 8-bit addresses.

**Examples:**

| MOV A, @R0 | RAM is addressed by contents of R0 (8-bit address) |

|------------|----------------------------------------------------|

|------------|----------------------------------------------------|

#### 6.1.3.1.4 Index Addressing Mode

Only program memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in program memory. A 16-bit base register (either DPTR or the PC) points to the base of the table, and the accumulator is set up with the table entry number. The address of the table entry in program memory is formed by adding the accumulator data to the base pointer. Another type of indexed addressing is used in the "case jump" instruction. In this case, the destination address of a jump instruction is calculated as the sum of the base pointer and the accumulator data.

#### **Examples:**

| MOVC A, @A + DPTR | Address is the sum of DPTR and accumulator. |

|-------------------|---------------------------------------------|

| MOVC A, @A + PC   | Address is the sum of PC and accumulator    |

| JMP @A + DPTR     | Jump to sum of accumulator and DPTR         |

#### 6.1.3.1.5 Register Addressing Mode

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of the eight registers in the selected bank is accessed. One of four banks is selected at execution time by the two bank select bits (RS0 and RS1) in the PSW.

#### 6.1.3.1.6 Register-Specific Addressing Mode

Some instructions are specific to a certain register. For example, some instructions always operate on the accumulator, or data pointer, etc., so no address byte is needed to point to it.

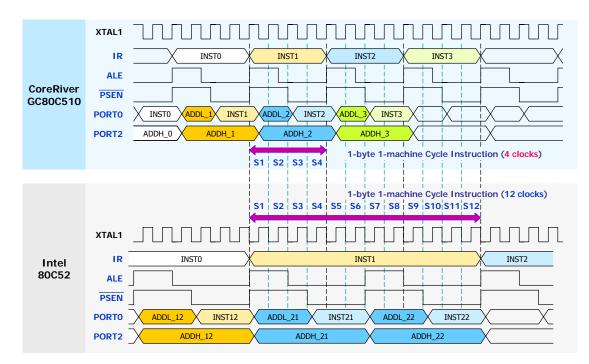

# 6.1.4 CPU Timing

The CPU timing for the MiDAS1.1 family is an important aspect, especially for those who wish to use software instructions to generate timing delays. Also, it provided the user with an insight into the timing differences between the MiDAS1.1 family and the standard 80C52 as shown in Figure 6-2.

In the MiDAS1.1 family, each machine cycle is four clock periods long. Each clock period is designated a state. Thus each machine cycle is made up of four states, S1, S2, S3 and S4 in that order. Due to the reduced time for each instruction execution, both the clock edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. Since the MiDAS1.1 family fetches one opcode per machine cycle, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction.

Figure 6-2 Comparative Timing of the MiDAS1.1 family and Intel 80C52

# 6.2 Peripheral Description

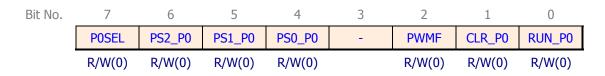

# 6.2.1 I/O Ports

The MiDAS1.1 Family has the port 0 (8 bits), port 1 (3 bits), and port 2 (7 bits). The port configuration is to control the registers: input/output direction control (PXDIR), output type control to determine the push-pull or open-drain output type (PXTYPE), and pull-up control (PXSEL).

The ADC (Analog-to-Digital Converter) is 12 channels and 10-bit resolution. The port 0 has 7-channel ADC input and port 2 has 5-channel ADC input.

The ADC configuration for port is to control the register: ADCSEL, ADCSELH, ADCON, and ADCR. After reset, the port 0 and port 2 are configured as general I/O ports which is input mode with pushpull output type and pull-up register is ON. And ADC input channels of port 0 and port 2 are disabled. The port 1 is configured as crystal input/output and reset signal input.

# 6.2.1.1 PORT 0

Port 0 has the following configuration modes in according to P0DIR, P0SEL, P0TYPE, ALTSEL, ADCOSEL, ADCON, and ADCSELH register.

- Input / Output mode controlled by P0DIR (Default = FFh, Input mode)

- Push-pull / Open-drain output type controlled by P0TYPE (Default = 00h, Push-pull output type)

- Pull-up ON / OFF controlled by P0SEL (Default = FFh, Pull-up ON)

- ADC input enable & digital input disable, or ADC input disable & digital input enable by ADCSEL and ADCSELH (Default = FFh is ADC input disable & digital input enable.)

- AV<sub>REF</sub> (ADC reference voltage) using P0[4] enabled by ADCON

After reset, port 0 is configured as input mode with push-pull output type and pull-up is turn-on. Also, ADC input channels are disabled. Note that the port 0[7:1] (= P0[7:1]) is configurable as an ADC input pins. The ADC0 ~ ADC6 input channels of the port 0 are selected by ADCSEL and ADCSELH register.

# [How to control the ADC input channel enable / disable for P0]

If an ADC input of port 0 is enabled, port 0 is automatically configured as ADC input channel without any effect of port 0 state. Namely, ADC input channel is valid by ADC selection registers (ADCSEL, ADCSELH) even if port 0 is operating on the output mode (bit value of P0DIR = 0). If ADC input channel is disabled, port configuration will be back to the state before entering the ADC input channel enable mode. To select the ADC channel input, set the bit of the ADCSEL or ADCSELH register to "0" (0 = ADC channel bit enable, 1 = disable (Default)). In more detail about ADC, refer to "6.2.7 ADC" part.

# [How to control the P0 input / output mode]

The initial value of P0DIR (Port 0 Input/Output Control) register is FFh. This means that the mode of P0 is input mode. To configure the bit of the P0 to output mode, set to the bit of the P0DIR register to "0" (0 = Output, 1 = Input (Default)).

## [How to control the P0 pull-up ON/OFF]

The initial value of POSEL (Port 0 Pull-up Control) register is 00h. This means that the pull-up of P0 is ON. To disable the pull-up resistor control, set to the bit of the POSEL register to "1" (0 = Pull-up ON (Default), 1=Pull-up OFF).

#### [How to control the P0 output type]

The initial value of P0TYPE (Port 0 Type Control) register is 00h. This means that the output type of P0 is push-pull output type. To configure the bit output type of the P0 to open-drain output, set the bit of the P0TYPE register to "1" (0 = Push-pull output (Default), 1 = Open-drain output).

# Figure 6-3 Configuration of PORT 0

Note: Read-Modify-Write instructions do not read port pin but SFR register.

Page 29 of 211

# [About the alternative pins and description]

In addition, all the pins have an alternative function listed below. Each of the functions is controlled by several other SFRs.

P0[6] Port 0 P0[7] P0[0] P0[6] P0[4] P0[3] P0[2] P0[1] ADC6 ADC5 ADC4 ADC3 ADC2 ADC1 ADC0 **INT0B** PWM TVO  $\mathsf{AV}_{\mathsf{REF}}$ INT3B INT2 INT1B TXD RXD PWM

| Alternative Pin   | Description                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC6 ~ ADC0       | ADC Analog Input 6 ~ 0                                                                                                                                                         |

| AV <sub>REF</sub> | ADC Voltage Reference Input.                                                                                                                                                   |

| PWM               | PWM Waveform Output. (Refer to ALTSEL register)                                                                                                                                |

| INT3B             | External Interrupt 3.<br>A falling edge on this pin will cause an external interrupt 3 if enabled.                                                                             |

| INT2              | External Interrupt 2.<br>A rising edge on this pin will cause an external interrupt 2 if enabled.                                                                              |

| INT1B             | External Interrupt 1.<br>A falling edge or low level on this pin will cause an external interrupt 1 if enabled.                                                                |

| INT0B             | External Interrupt 0.<br>A falling edge or low level on this pin will cause an external interrupt 0 if enabled.                                                                |

| TXD               | Serial Port Transmit.<br>This pin transmits the serial port data in serial port modes 1 and emits the<br>synchronizing clock in serial port mode 0. (Refer to ALTSEL register) |

| RXD               | Serial Port Receive.<br>This pin receives the serial port data in serial port modes 1 and is a bi-directional data transfer pin in serial port mode 0.                         |

| TVO               | Timer 0 Overflow Output. (Refer to ALTSEL register)                                                                                                                            |

# [How to control the TVO enable / disable]

If user wants to use the P0[0] bit is configured as TVO (Timer 0 overflow clock output to P0[0]), set the ALTSEL[3] to "1". Then TVO waveform will be output to P0[0].

# [How to control the PWM waveform output to P0[0] or P0[6] enable / disable]

If user wants to use the P0[0] bit as PWM waveform output to P0[0], set the PWM00 (ALTSEL[4]) to "1". Then PWM waveform will be output to P0[0].

If user wants to use the P0[6] bit as PWM waveform output to P0[6], set the P0SEL (PWMCON[0]) to "1". The PWM waveform will be output to P0[6].

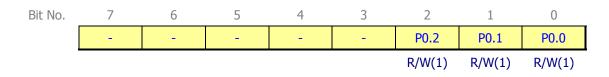

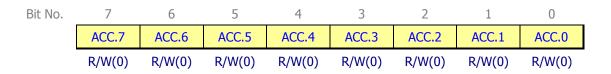

# 6.2.1.1.1 P0 (80h) : Port 0 Register

| Bit No. | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | P0.7   | P0.6   | P0.5   | P0.4   | P0.3   | P0.2   | P0.1   | P0.0   |

|         | R/W(1) |

This register functions as a general purpose I/O port. The initial value of P0 is FFh.

# 6.2.1.1.2 POTYPE (D4h) : Port 0 Type Control Register

| Bit No. | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|---------|----------|----------|----------|----------|----------|----------|----------|----------|

|         | POTYPE.7 | P0TYPE.6 | P0TYPE.5 | P0TYPE.4 | POTYPE.3 | P0TYPE.2 | P0TYPE.1 | POTYPE.0 |

|         | R/W(0)   |

This register configures the P0 output type to the push-pull or open-drain. The initial P0 output type is configured to push-pull output type.

0 = Push-pull output type. (Default)

1 = Open-drain output.

# 6.2.1.1.3 POSEL (E4h) : Port 0 Pull-up Control Register

| Bit No. | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|         | POSEL.7 | POSEL.6 | P0SEL.5 | P0SEL.4 | POSEL.3 | POSEL.2 | POSEL.1 | POSEL.0 |

|         | R/W(0)  |

This register is enables/disabled the internal pull-up in P0.

0 = Pull-up ON. The bit is configured to pull-up ON. (Default)

1 = Pull-up OFF. The bit is configured to pull-up OFF.

# 6.2.1.1.4 **PODIR** (F4h) : Port 0 Input/Output Control Register

| Bit No. | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

|         | P0DIR.7 | PODIR.6 | P0DIR.5 | P0DIR.4 | PODIR.3 | P0DIR.2 | P0DIR.1 | P0DIR.0 |

|         | R/W(1)  |

This register is configured the P0 to input mode or output mode. The initial P0 mode is configured to input mode.

0 = Output mode. The bit is configured to output.

1 = Input mode. The bit is configured to input. (Default)

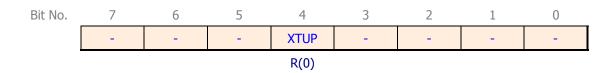

6.2.1.1.5 ALTSEL (E3h) : Alternative Function Selection Register

| Bit No. | 7      | 6       | 5      | 4      | 3      | 2      | 1 | 0 |

|---------|--------|---------|--------|--------|--------|--------|---|---|

|         | IOXEN  | IORSTEN | CLO    | PWM00  | TVO    | ТХ     | - | - |

|         | R/W(0) | R/W(0)  | R/W(0) | R/W(0) | R/W(0) | R/W(0) |   |   |

| Symbol | Description                                                                         |

|--------|-------------------------------------------------------------------------------------|

|        | PWM Waveform Output Enable to P0[0].                                                |

| PWM00  | 0 = Disable the PWM waveform output to P0[0]. (Default)                             |

|        | 1 = Enable the PWM waveform output to P0[0].                                        |

|        | Timer0 Overflow Output Enable to P0[0].                                             |

| TVO    | 0 = Disable the Timer0 overflow output to P0[0]. (Default)                          |

|        | 1 = Enable the Timer0 overflow output to P0[0].                                     |

|        | UART TX Data Output Enable to P0[2]. (TXD : TX Data)                                |

|        | 0 = Disable the TX data output to P0[2]. (Default)                                  |

| тх     | 1 = Enable the TX data output to P0[2].                                             |

|        | Note that the port directional mode (input/output) of P0[2] for TXD is don't care.  |

|        | But the directional mode (input/output) of P0[1] for RXD must set up to input mode, |

|        | When user is setting to UART communication.                                         |

| -      | Reserved                                                                            |

# 6.2.1.1.6 ADCSELH (E1h) ADC Channel Selection High Register

| Bit No. | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | ADC11B | ADC10B | ADC9B  | ADC8B  | ADC7B  | ADC6B  | ADC5B  | ADC4B  |

|         | R/W(1) |

| Symbol         | Description                                                                            |                                                                         |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

|                | ADC Channel Selection Low. These bits are configured to enable/disable the ADC channel |                                                                         |  |  |  |  |  |

|                | inputs (ADC[11:4]). P0[5] ~ P0[7] : ADC4 ~ ADC6 input.                                 |                                                                         |  |  |  |  |  |

|                | ADC Channel Result                                                                     |                                                                         |  |  |  |  |  |

|                | ADC4B                                                                                  | 1 = ADC4 input channel is disabled & digital input is enabled at P0[5]  |  |  |  |  |  |

| ADC4B          |                                                                                        | (Default)                                                               |  |  |  |  |  |

| ADC4B<br>ADC5B |                                                                                        | 0 = ADC4 input channel is enabled & digital input is disabled.          |  |  |  |  |  |

| ADC5B          | ADC5B                                                                                  | 1 = ADC5 input channel is disabled & digital input is enabled at P0[6]. |  |  |  |  |  |

| ADCOD          |                                                                                        | (Default)                                                               |  |  |  |  |  |

|                |                                                                                        | 0 = ADC5 input channel is enabled & digital input is disabled.          |  |  |  |  |  |

|                | ADC6B                                                                                  | 1 = ADC6 input channel is disabled & digital input is enabled at P0[7]. |  |  |  |  |  |

|                |                                                                                        | (Default)                                                               |  |  |  |  |  |

|                |                                                                                        | 0 = ADC6 input channel is enabled & digital input is disabled.          |  |  |  |  |  |

# 6.2.1.1.7 ADCSEL (E2h): ADC Channel Selection Low & MUX Selection Register

| Bit No. | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | ADC3B  | ADC2B  | ADC1B  | ADC0B  | CH3    | CH2    | CH1    | CH0    |

|         | R/W(1) |

\* R/W (1) means that user can read and writer this flag bit. The initial value of flag bit is "1".

| Symbol     | Description                                                                             |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

|            | ADC C                                                                                   | ADC Channel Selection Low. |                                                                |                                                                         |                                                              |  |  |  |  |  |

|            | The                                                                                     | se bits a                  | are conf                                                       | e configured to enable/disable the ADC channel inputs (ADC[3:0]). P0[1] |                                                              |  |  |  |  |  |

|            | ~ P0                                                                                    | [4] : AD                   | C0 ~ A[                                                        | ) ~ ADC3 input. (Default = 1)                                           |                                                              |  |  |  |  |  |

|            | ADC C                                                                                   | Channel                    |                                                                | Result                                                                  |                                                              |  |  |  |  |  |

| ADC0B      | AD                                                                                      | C0B                        | 1 = A                                                          | DC0 inp                                                                 | out channel is disabled & digital input is enabled at P0[1]. |  |  |  |  |  |

| ADC1B      |                                                                                         |                            | 0 = A                                                          | DC0 inp                                                                 | out channel is enabled & digital input is disabled.          |  |  |  |  |  |

| ADC2B      | ADC1B 1 = ADC1 input channel is disabled & digital input is enabled at P0[2].           |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

| ADC3B      |                                                                                         |                            | 0 = ADC1 input channel is enabled & digital input is disabled. |                                                                         |                                                              |  |  |  |  |  |

|            | AD                                                                                      | C2B                        | 1 = A                                                          | DC2 inp                                                                 | out channel is disabled & digital input is enabled at P0[3]. |  |  |  |  |  |

|            |                                                                                         |                            | 0 = A                                                          | 0 = ADC2 input channel is enabled & digital input is disabled.          |                                                              |  |  |  |  |  |

|            | AD                                                                                      | C3B                        | 1 = A                                                          | 1 = ADC3 input channel is disabled & digital input is enabled at P0[4]. |                                                              |  |  |  |  |  |

|            |                                                                                         |                            | 0 = A                                                          | 0 = ADC3 input channel is enabled & digital input is disabled.          |                                                              |  |  |  |  |  |

|            | ADC MUX Selection.                                                                      |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

|            | Theses bits is configured to select the ADC input. The initial value of CH[3:0] is 0xFh |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

|            | (4'b1111). Ch, Dh, Eh and Fh means that all ADC inputs are disabled.                    |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

| CLIO       | CH3                                                                                     | CH2                        | CH1                                                            | CH0                                                                     | Result                                                       |  |  |  |  |  |

| CH0<br>CH1 | 0                                                                                       | 0                          | 0                                                              | 0                                                                       | 0x0h : ADC0 is selected                                      |  |  |  |  |  |

| 0=         | 0                                                                                       | 0                          | 0                                                              | 1                                                                       | 0x1h : ADC1 is selected                                      |  |  |  |  |  |

| CH2<br>CH3 | 0                                                                                       | 0                          | 1                                                              | 0                                                                       | 0x2h : ADC2 is selected                                      |  |  |  |  |  |

| СПЗ        |                                                                                         |                            |                                                                |                                                                         |                                                              |  |  |  |  |  |

|            | 1                                                                                       | 0                          | 1                                                              | 0                                                                       | 0xAh : ADC10s selected                                       |  |  |  |  |  |

|            | 1                                                                                       | 0                          | 1                                                              | 1                                                                       | 0xBh : ADC11is selected                                      |  |  |  |  |  |

|            | 1100 (0xCh) ~ 1111 (0xFh)                                                               |                            |                                                                | (0xFh)                                                                  | No ADC channel is not selected (Default Value = $0xFh$ )     |  |  |  |  |  |

#### 6.2.1.2 PORT 1

Port 1 has the following configuration modes in according to P1DIR, P1SEL, P1TYPE, ALTSEL, and PMR register.

- Input / Output mode controlled by P1DIR (Default = \*\*\*\*\*11, Input mode)

- General I/O enable by ALTSEL[7] (IOXEN, Default (= 0) is not general I/O for P1[0] and P1[1]), ALTSEL[6] (IORSTEN, Default (=0) is not general I/O for P1[2]), and PMR[3] (XTOFF, Default (=0) does not disable the internal amplifier for external crystal).

- Push-pull / Open-drain output type of P1[0] and P1[1] controlled by P1TYPE

(Default = \*\*\*\*\*00, Push-pull output type). The P1[2] is only the open-drain output type.

- Pull-up ON / OFF controlled by P1SEL (Default = \*\*\*\*\*00, Pull-up OFF)

After reset, the port 1 configuration is that P1[0] and P1[1] is crystal input/output (XTAL1/XTAL2) and P1[2] is a chip reset signal input (RESETB). The pull-up of P[0] and P[1] is OFF and P[2] has no pull-up. In addition, Port 1 can be configured as the following modes using P1DIR, P1SEL, P1TYPE, ALTSEL register.

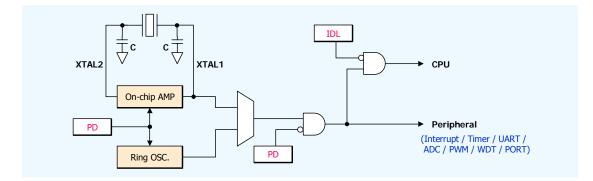

# [How to control the XTAL1 (P1[0]) and XTAL2 (P1[1]) as general I/O pins]

If you want to use XTAL1 (P1[0]) and XTAL2 (P1[1]) as general I/O pins, you should set ALTSEL[7] (IOXEN flag) to "1". Then, P1[0] and P1[1] are configured as general I/O pins. And you should set PMR[3] (XTOFF flag) to "1".

In other words, to use the general I/O pins, you should set P1[0] and P1[1] as general I/O pins and disable the internal amplifier for crystal between these two pins. Refer to the below figure.

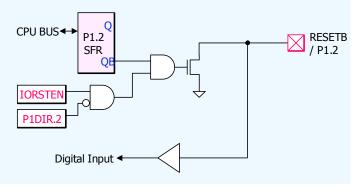

#### [How to control the RESETB (P1[2]) as I/O pin]

If you want to use RESETB as general I/O pin, you should set ALTSEL[6] (IORSTEN flag) to "1". Then, P1[2] is configured as general I/O pin. Note that retain "1" at P1[2] pin until this RESETB pin is configured as general I/O pin. If you do not that, MCU remains at reset mode.

#### [How to control the P1 input / output mode]

The initial value of P1DIR (Port 1 Input/Output Control) register is \*\*\*\*\*111. This means that the mode of P1[0], P1[1], and P1[2] is input mode. To configure the bit of the P1 to output mode, set to the bit of the P1DIR register to "0" (0 = Output, 1 = Input (Default)).

#### [How to control the P1 pull-up ON/OFF]

The initial value of POSEL (Port 1 Pull-up Control) register is \*\*\*\*\*11. This means that the pull-up of

P1[0] and P1[1] is OFF. To enable the pull-up resistor control, set to the bit of the P1SEL register to "0" (0 = Pull-up ON, 1=Pull-up OFF (Default)). Note that P1[2] has no pull-up.

# [How to control the P1 output type]

The initial value of P1TYPE (Port 1 Type Control) register is \*\*\*\*\*00h. This means that the output type of P1[0] and P1[1] is push-pull output type. To configure the bit output type of the P1[0] and P1[1] to open-drain output, set the bit of the P1TYPE register to "1" (0 = Push-pull output (Default), 1 = Open-drain output). Note that P1[2] is only open-drain output type. If user wants to use the P1[2] pin as output pin, this pin may need the external pull-up resistor.

# [About the alternative pins and description]

In addition, all the pins have an alternative function listed below. Each of the functions is controlled by several other SFRs

| Port 1 | - | - | - | - | - | P1[2]  | P1[1] | P1[0] |

|--------|---|---|---|---|---|--------|-------|-------|

|        |   |   |   |   |   | RESETB | XTAL2 | XTAL1 |

| Alternative Pin | Description                                           |

|-----------------|-------------------------------------------------------|

| XTAL1           | External Crystal Oscillator Input. (Refer to ALTSEL)  |

| XTAL2           | External Crystal Oscillator Output. (Refer to ALTSEL) |

| RESETB          | Inverted Reset Input. Active Low. (Refer to ALTSEL)   |

(a) P1.0 (XTAL1) and P1.1 (XTAL2)

(b) P1.2 (RESETB)

Figure 6-4 Configuration of PORT1

## 6.2.1.2.1 P1 (90h) : Port 1 Register

This register functions as a general purpose I/O port. The initial value of P0 is FFh.

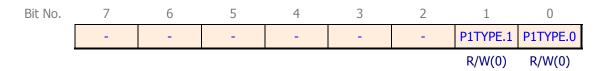

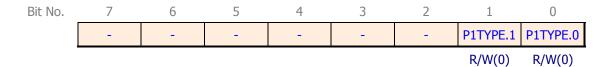

## 6.2.1.2.2 P1TYPE (D5h) : Port 1 Type Control Register

This register configures the P0 output type to the push-pull or open-drain. The initial P1 output type is configured to push-pull output type. Note that the P1[2] pin is only the open-drain output type.

0 = Push-pull output type. (Default)

1 = Open-drain output.

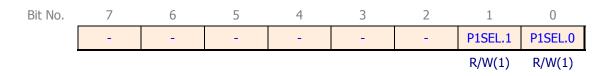

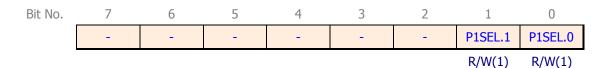

## 6.2.1.2.3 P1SEL (E5h) : Port 1 Pull-up Control Register

This register is enables/disabled the internal pull-up in P1. Note that the P1[2] has no pull-up.

0 = Pull-up ON. The bit is configured to pull-up ON.

1 = Pull-up OFF. The bit is configured to pull-up OFF. (Default)

## 6.2.1.2.4 P1DIR (F5h) : Port 1 Input/Output Control Register

This register is configured the P1 to input mode or output mode. The initial P1 mode is configured to input mode.

0 = Output mode. The bit is configured to output.

1 = Input mode. The bit is configured to input. (Default)

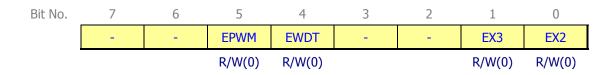

#### 6.2.1.2.5 ALTSEL (E3h) : Alternative Function Selection Register

| Bit No. | 7      | 6       | 5      | 4      | 3      | 2      | 1 | 0 |

|---------|--------|---------|--------|--------|--------|--------|---|---|

|         | IOXEN  | IORSTEN | CLO    | PWM00  | TVO    | ТΧ     | - | - |

|         | R/W(0) | R/W(0)  | R/W(0) | R/W(0) | R/W(0) | R/W(0) |   |   |

| Symbol  | Description                                                                             |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------|--|--|--|--|

|         | I/O bits from XTAL1/XTAL2 Enable. (XTAL1 : Input, XTAL2 : Output)                       |  |  |  |  |

| IOXEN   | 0 = The P1[1] and P1[0] bits are configured as XTAL Input/Output (Default)              |  |  |  |  |

| IOVEN   | 1 = The P1[1] and P1[0] bits are configured as general I/O pins.                        |  |  |  |  |

|         | Note that you must set XTOFF bit (PMR.3) to " $1''$ to turn off the internal amplifier. |  |  |  |  |

|         | I/O bits from RESETB Enable.                                                            |  |  |  |  |

| IORSTEN | 0 = The P1[2] bit is configured as RESETB input. (Default)                              |  |  |  |  |

|         | 1 = The P1[2] bit is configured as general I/O pin.                                     |  |  |  |  |

| -       | Reserved                                                                                |  |  |  |  |

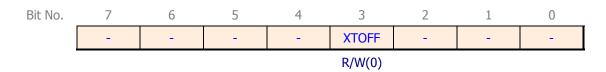

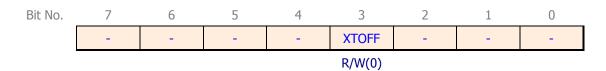

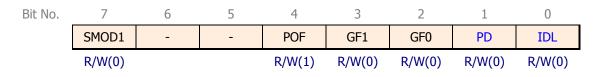

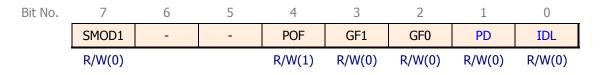

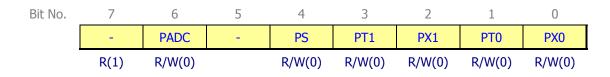

## 6.2.1.2.6 PMR (C4h) : Power Management Register

| Symbol | Description                                                                                  |  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|        | Internal Amplifier Disable for External Crystal Oscillator.                                  |  |  |  |  |  |  |

|        | This bit controls the enable/disable the internal amplifier for external crystal oscillator. |  |  |  |  |  |  |

|        | 0 = Internal amplifier is enabled. (Default)                                                 |  |  |  |  |  |  |

| XTOFF  | 1 = Internal amplifier is disabled.                                                          |  |  |  |  |  |  |

|        | Set the XTOFF bit to "1" when user wants to use $P1[0]$ and $P1[2]$ as general I/O pins.     |  |  |  |  |  |  |

|        | Don't set XTOFF bit to "1" when XT/RG bit (EXIF.3) is "1".                                   |  |  |  |  |  |  |

|        | (XT/RG = $1''$ : The external clock is selected as system clock. Refer to EXIF register.)    |  |  |  |  |  |  |

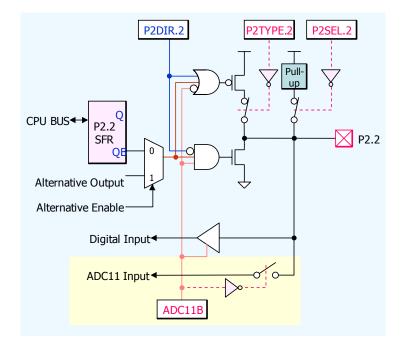

# Figure 6-5 Configuration of PORT2

Page 40 of 211

### 6.2.1.3 PORT 2

Port 2 has the following configuration modes in according to P2DIR, P2SEL, P2TYPE, ALTSEL, ADCON, ADCSEL, and ADCSELH register.

- Input / Output mode controlled by P2DIR (Default = \*1111111, Input mode)

- Push-pull / Open-drain output type controlled by P2TYPE (Default = \*0000000h, Push-pull output type)

- Pull-up ON / OFF controlled by P0SEL (Default = \*1111111h, Pull-up ON)

- ADC input enable & digital input disable, or ADC input disable & digital input enable by ADCSEL and ADCSELH (Default = FFh is ADC input disable & digital input enable.)

After reset, port 2 is configured as input mode with push-pull output type and pull-up is turn-on. Also, ADC input channels are disabled. Note that the port 2[6:2] (= P2[6:2]) is configurable as an ADC input pins. The ADC7 ~ ADC11 input channels of the port 2 are selected by ADCSEL and ADCLSELH register.

#### [How to control the ADC input channel enable / disable for P2]

If an ADC input of port 2 is enabled, port 2 is automatically configured as ADC input channel without any effect of port 2 state. Namely, ADC input channel is valid by ADC selection registers (ADCSEL, ADCSELH) even if port 2 is operating on the output mode (bit value of P2DIR = 0). If ADC input channel is disabled, port configuration will be back to the state before entering the ADC input channel enable mode. To select the ADC channel input, set the bit of the ADCSEL or ADCSELH register to "0" (0 = ADC channel bit enable, 1 = disable (Default)). In more detail about ADC, refer to "6.2.7 ADC" part.

#### [How to control the P2 input / output mode]

The initial value of P2DIR (Port 2 Input/Output Control) register is \*1111111. This means that the mode of P2 is input mode. To configure the bit of the P2 to output mode, set to the bit of the P2DIR register to "0" (0 = Output, 1 = Input (Default)).

#### [How to control the P2 pull-up ON/OFF]

The initial value of P2SEL (Port 2 Pull-up Control) register is \*0000000h. This means that the pull-up of P2 is ON. To disable the pull-up resistor control, set to the bit of the P2SEL register to "1" (0 = Pull-up ON (Default), 1=Pull-up OFF).

## [How to control the P2 output type]

The initial value of P2TYPE (Port 2 Type Control) register is \*0000000h. This means that the output type of P2 is push-pull output type. To configure the bit output type of the P2 to open-drain output, set the bit of the P2TYPE register to "1" (0 = Push-pull output (Default), 1 = Open-drain output).

## [How to control the Timer0 Counter from P2[0]]

If user wants to use the timer0 as counter from external input pin (P2[6]; T0 input pin), set the C/T bit (TMOD[2]) to "1". A "1" to "0" transition on this T0 input pin will increment the timer0 counter.

The default value of C/T bit (TMOD[2]) is "0", timer0 timer uses the system clock for timing. When the value of C/T bit is 1, timer0 counter uses the external T0 input transition for counter. In more detail, refer to TMOD register.

## [About the alternative pins and description]

In addition, all the pins have an alternative function listed below. Each of the functions is controlled by several other SFRs.

| Port 2 | - | P2[6] | P2[5] | P2[4] | P2[3] | P2[2] | P2[1] | P2[0] |

|--------|---|-------|-------|-------|-------|-------|-------|-------|

|        |   | ADC7  | ADC8  | ADC9  | ADC10 | ADC11 |       | Т0    |

|        |   | CLO   |       |       |       |       |       |       |

| Alternative Pin | Description                                                                                                                           |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADC11 ~ ADC7    | ADC Analog Input 11 ~ 7                                                                                                               |  |  |  |  |

| CLO             | CLO System Clock Output to P2[6]. (Refer to ALTSEL register)                                                                          |  |  |  |  |

| то              | Timer0 Input or T0 Input. (Refer to TMOD register)<br>A "1" to "0" transition on this T0 input pin will increment the timer0 counter. |  |  |  |  |

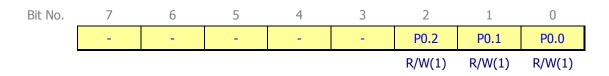

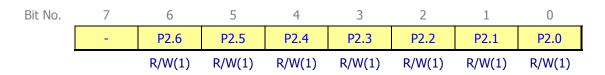

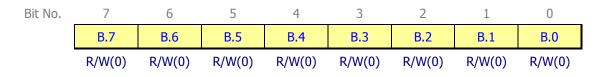

### 6.2.1.3.1 P2 (A0h) : Port 2 Register

| Bit No. | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|---|--------|--------|--------|--------|--------|--------|--------|

|         | - | P2.6   | P2.5   | P2.4   | P2.3   | P2.2   | P2.1   | P2.0   |

|         |   | R/W(1) |

This register functions as a general purpose I/O port. The initial value of P2 is \*1111111.

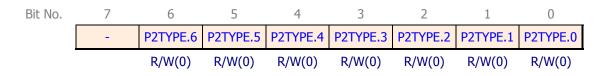

## 6.2.1.3.2 P2TYPE (D6h) : Port 2 Type Control Register

This register configures the P2 output type to the push-pull or open-drain. The initial P2 output type is configured to push-pull output type.

0 = Push-pull output type. (Default)

1 = Open-drain output.

## 6.2.1.3.3 P2SEL (E6h) : Port 2 Pull-up Control Register

| Bit No. | 7 | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---|---------|---------|---------|---------|---------|---------|---------|

|         | - | P2SEL.6 | P2SEL.5 | P2SEL.4 | P2SEL.3 | P2SEL.2 | P2SEL.1 | P2SEL.0 |

|         |   | R/W(0)  |

This register is enables/disabled the internal pull-up in P2.

0 = Pull-up ON. The bit is configured to pull-up ON. (Default)

1 = Pull-up OFF. The bit is configured to pull-up OFF.

## 6.2.1.3.4 **P2DIR** (F6h) : Port 2 Input/Output Control Register

| Bit No. | 7 | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------|---|---------|---------|---------|---------|---------|---------|---------|

|         | - | P2DIR.6 | P2DIR.5 | P2DIR.4 | P2DIR.3 | P2DIR.2 | P2DIR.1 | P2DIR.0 |

|         |   | R/W(1)  |

This register is configured the P2 to input mode or output mode. The initial P2 mode is configured to input mode.

0 = Output mode. The bit is configured to output.

1 = Input mode. The bit is configured to input. (Default)

## 6.2.1.3.5 ADCSELH (E1h) ADC Channel Selection High Register

| Bit No. | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | ADC11B | ADC10B | ADC9B  | ADC8B  | ADC7B  | ADC6B  | ADC5B  | ADC4B  |

|         | R/W(1) |

| Symbol |                | Description                                                               |

|--------|----------------|---------------------------------------------------------------------------|

|        | ADC Channel Se | election Low. These bits are configured to enable/disable the ADC channel |

|        | inputs (ADC[11 | :4]). P2[2] ~ P2[6] : ADC7 ~ ADC11 input.                                 |

|        | ADC Channel    | Result                                                                    |

|        | ADC7B          | 1 = ADC7 input channel is disabled & digital input is enabled at P2[6].   |

| ADC7B  |                | (Default)                                                                 |

| ADC8B  |                | 0 = ADC7 input channel is enabled & digital input is disabled.            |

| ADC9B  | ADC8B          | 1 = ADC8 input channel is disabled & digital input is enabled at P2[5].   |

| ADC10B |                | (Default)                                                                 |

| ADC11B |                | 0 = ADC8 input channel is enabled & digital input is disabled.            |

|        |                |                                                                           |

|        | ADC11B         | 1 = ADC11 input channel is disabled & digital input is enabled at P2[2].  |

|        |                | (Default)                                                                 |

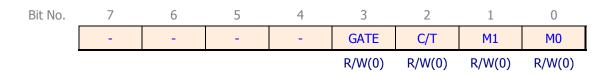

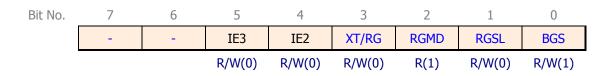

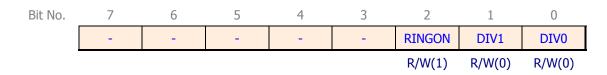

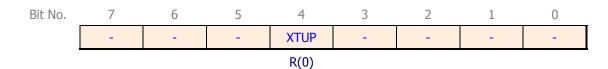

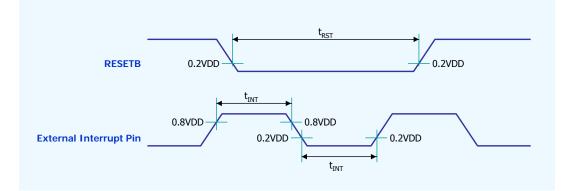

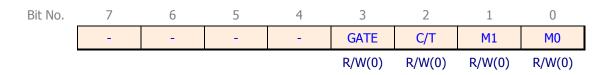

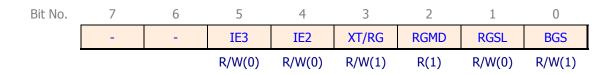

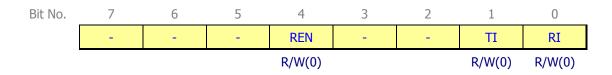

|        |                | 0 = ADC11 input channel is enabled & digital input is disabled.           |