# MC68Hc912D60A MC68HC912D60C MC68HC912D60P Technical Data

HC12 Microcontrollers

MC68HC912D60A/D Rev. 3.1 08/2005

freescale.com

# MC68HC912D60A MC68HC912D60C MC68HC912D60P

Technical Data — Rev. 3.1

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale was negligent regarding the design or manufacture of the part. Freescale, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Freescale, Inc., 2005

**Technical Data**

MC68HC912D60A — Rev. 3.1

**Technical Data**

# **List of Paragraphs**

| List of Paragraphs5                               |

|---------------------------------------------------|

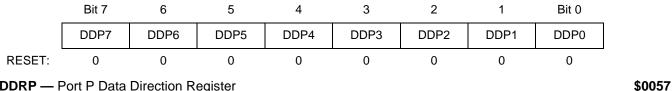

| Table of Contents                                 |

| List of Figures                                   |

| List of Tables                                    |

| Section 1. General Description23                  |

| Section 2. Central Processing Unit                |

| Section 3. Pinout and Signal Descriptions         |

| Section 4. Registers61                            |

| Section 5. Operating Modes and Resource Mapping71 |

| Section 6. Bus Control and Input/Output85         |

| Section 7. Flash Memory97                         |

| Section 8. EEPROM Memory105                       |

| Section 9. Resets and Interrupts                  |

| Section 10. I/O Ports with Key Wake-up            |

| Section 11. Clock Functions                       |

| Section 12. Oscillator                            |

| Section 13. Pulse Width Modulator                 |

| Section 14. Enhanced Capture Timer                |

| Section 15. Multiple Serial Interface             |

| Section 16. Freescale Interconnect Bus            |

| Section 17. MSCAN Controller                                           |

|------------------------------------------------------------------------|

| Section 18. Analog-to-Digital Converter                                |

| Section 19. Development Support                                        |

| Section 20. Electrical Specifications                                  |

| Section 21. Appendix: CGM Practical Aspects427                         |

| Section 22. Appendix: Changes from MC68HC912D60437                     |

| Section 23. Appendix: Information on MC68HC912D60A<br>Mask Set Changes |

| Glossary                                                               |

| Revision History                                                       |

**Technical Data**

List of Paragraphs

## **Table of Contents**

### **Technical Data** — List of Paragraphs

### **Technical Data** — Table of Contents

### **Technical Data** — List of Figures

### **Technical Data — List of Tables**

### **Section 1. General Description**

| 1.1 | Contents                         |

|-----|----------------------------------|

| 1.2 | Introduction                     |

| 1.3 | Devices Covered in this Document |

| 1.4 | Features                         |

| 1.5 | Ordering Information             |

| 1.6 | Block Diagrams                   |

### **Section 2. Central Processing Unit**

| 2.1 | Contents                 |

|-----|--------------------------|

| 2.2 | Introduction             |

| 2.3 | Programming Model        |

| 2.4 | Data Types               |

| 2.5 | Addressing Modes         |

| 2.6 | Indexed Addressing Modes |

| 2.7 | Opcodes and Operands     |

#### MC68HC912D60A — Rev. 3.1

#### **Section 3. Pinout and Signal Descriptions**

| 3.1                                             | Contents                                       |

|-------------------------------------------------|------------------------------------------------|

| 3.2                                             | MC68HC912D60A Pin Assignments in 112-pin QFP38 |

| 3.3                                             | MC68HC912D60A Pin Assignments in 80-pin QFP40  |

| 3.4                                             | Power Supply Pins                              |

| 3.5                                             | Signal Descriptions                            |

| 3.6                                             | Port Signals                                   |

|                                                 | Section 4. Registers                           |

| 4.1                                             | Contents                                       |

| 4.2                                             | Register Block                                 |

| Section 5. Operating Modes and Resource Mapping |                                                |

| 5.1                                             | Contents                                       |

| 5.2                                             | Introduction                                   |

| 5.3                                             | Operating Modes                                |

| 5.4                                             | Background Debug Mode                          |

| 5.5                                             | Internal Resource Mapping                      |

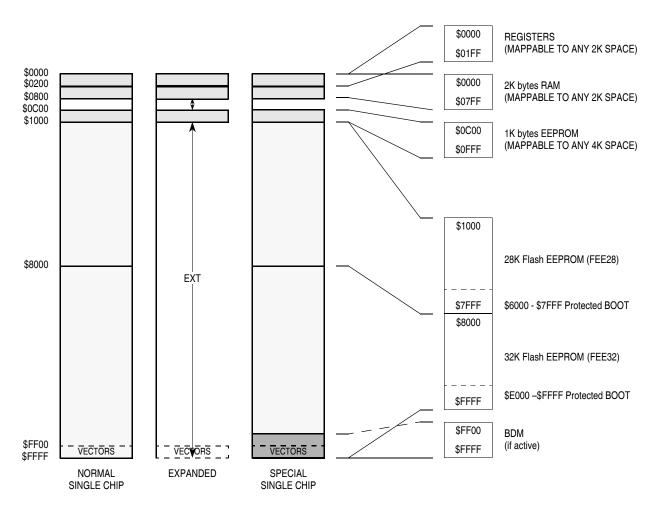

## Memory Maps......83

### Section 6. Bus Control and Input/Output

| 6.1 | Contents                                    | .85 |

|-----|---------------------------------------------|-----|

| 6.2 |                                             | .85 |

| 6.3 | Detecting Access Type from External Signals | .85 |

| 6.4 | Registers.                                  | .86 |

### Section 7. Flash Memory

| 7.1 | Contents |  |

|-----|----------|--|

|-----|----------|--|

#### **Technical Data**

8

5.6

| 7.2  | Introduction                 |

|------|------------------------------|

| 7.3  | Overview                     |

| 7.4  | Flash EEPROM Control Block   |

| 7.5  | Flash EEPROM Arrays98        |

| 7.6  | Flash EEPROM Registers       |

| 7.7  | Operation                    |

| 7.8  | Programming the Flash EEPROM |

| 7.9  | Erasing the Flash EEPROM     |

| 7.10 | Stop or Wait Mode            |

| 7.11 | Flash protection bit FPOPEN  |

### Section 8. EEPROM Memory

| 8.1 | Contents                                |

|-----|-----------------------------------------|

| 8.2 | Introduction                            |

| 8.3 | EEPROM Selective Write More Zeros       |

| 8.4 | EEPROM Programmer's Model               |

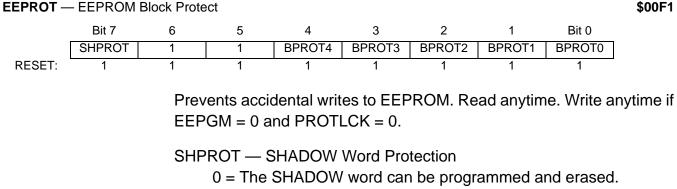

| 8.5 | EEPROM Control Registers                |

| 8.6 | Program/Erase Operation115              |

| 8.7 | Shadow Word Mapping115                  |

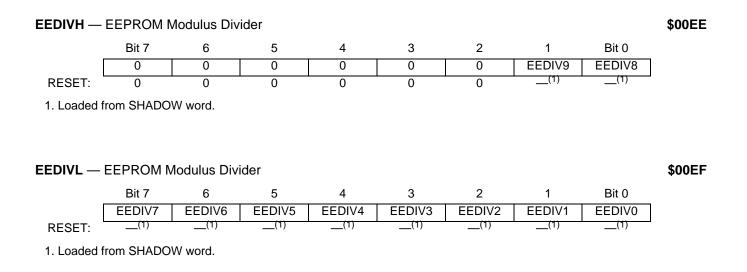

| 8.8 | Programming EEDIVH and EEDIVL Registers |

### Section 9. Resets and Interrupts

| 9.1 | Contents                                 |

|-----|------------------------------------------|

| 9.2 | Introduction                             |

| 9.3 | Maskable interrupts120                   |

| 9.4 | Latching of Interrupts121                |

| 9.5 | Interrupt Control and Priority Registers |

|     |                                          |

| 9.6   | Resets                                 |

|-------|----------------------------------------|

| 9.7   | Effects of Reset                       |

| 9.8   | Register Stacking                      |

| 9.9   | Customer Information                   |

|       | Section 10. I/O Ports with Key Wake-up |

| 10.1  | Contents                               |

| 10.2  | Introduction                           |

| 10.3  | Key Wake-up and Port Registers         |

| 10.4  | Key Wake-Up Input Filter               |

|       | Section 11. Clock Functions            |

| 11.1  | Contents                               |

| 11.2  | Introduction                           |

| 11.3  | Clock Sources                          |

| 11.4  | Phase-Locked Loop (PLL)                |

| 11.5  | Acquisition and Tracking Modes         |

| 11.6  | Limp-Home and Fast STOP Recovery modes |

| 11.7  | System Clock Frequency formulas        |

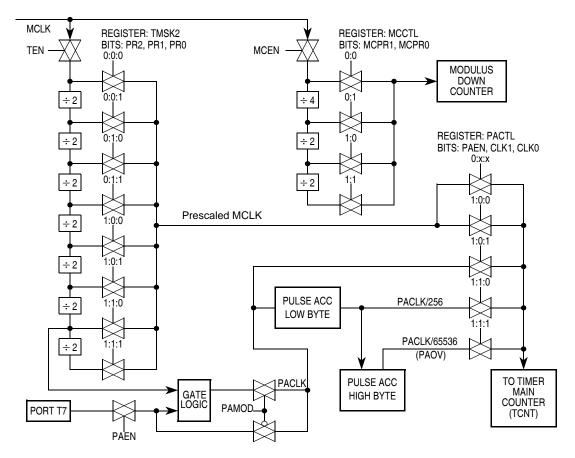

| 11.8  | Clock Divider Chains                   |

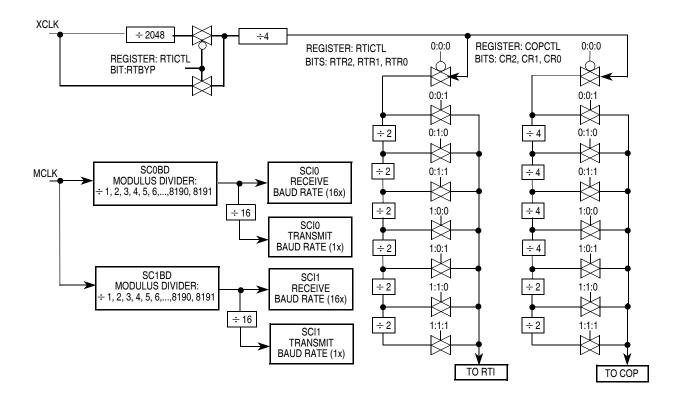

| 11.9  | Computer Operating Properly (COP)      |

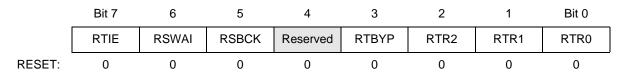

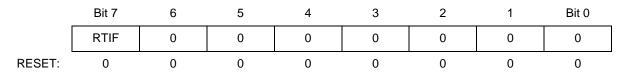

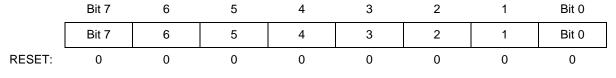

| 11.10 | Real-Time Interrupt                    |

| 11.11 | Clock Monitor                          |

| 11.12 | Clock Function Registers               |

|       |                                        |

### Section 12. Oscillator

| 12.1 | Contents. |  |  |  |  | 175 |

|------|-----------|--|--|--|--|-----|

|------|-----------|--|--|--|--|-----|

| Technical Data |

|----------------|

|----------------|

| 12.2 | Introduction                                               |

|------|------------------------------------------------------------|

| 12.3 | MC68HC912D60A Oscillator Specification                     |

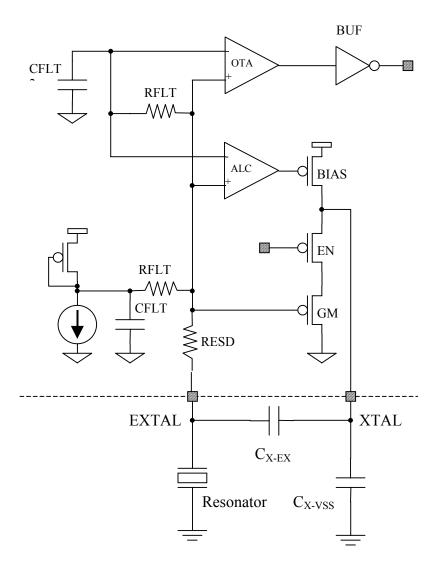

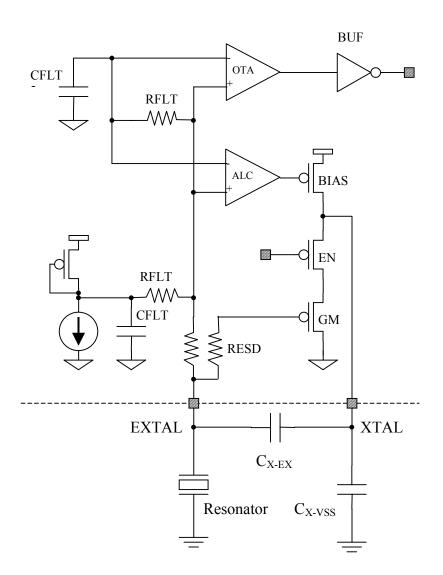

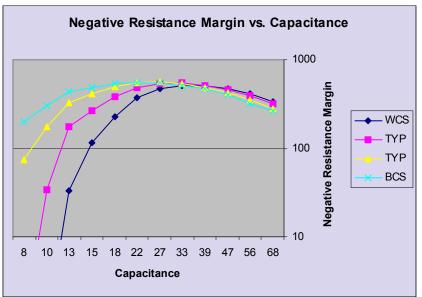

| 12.4 | MC68HC912D60C Colpitts Oscillator Specification 179        |

| 12.5 | MC68HC912D60P Pierce Oscillator Specification              |

|      | Section 13. Pulse Width Modulator                          |

| 13.1 | Contents                                                   |

| 13.2 | Introduction                                               |

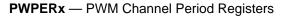

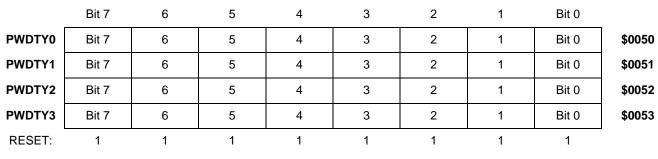

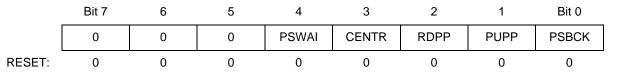

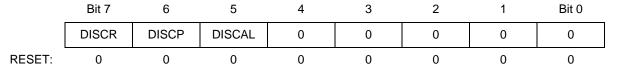

| 13.3 | PWM Register Description                                   |

| 13.4 | PWM Boundary Cases                                         |

|      | Section 14. Enhanced Capture Timer                         |

| 14.1 | Contents                                                   |

| 14.2 | Introduction                                               |

| 14.3 | Enhanced Capture Timer Modes of Operation                  |

| 14.4 | Timer Registers                                            |

| 14.5 | Timer and Modulus Counter Operation in Different Modes 261 |

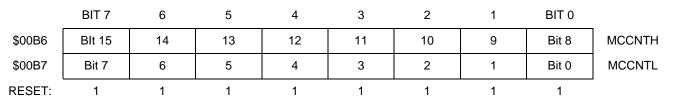

|      | Section 15. Multiple Serial Interface                      |

| 15.1 | Contents                                                   |

| 15.2 | Introduction                                               |

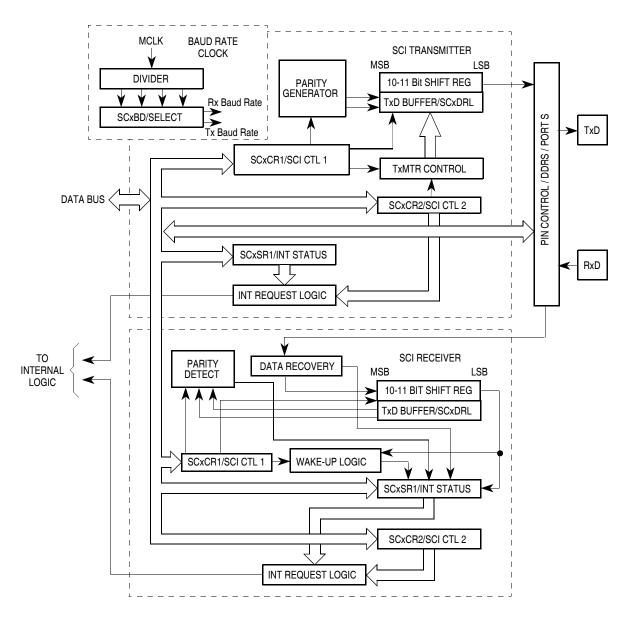

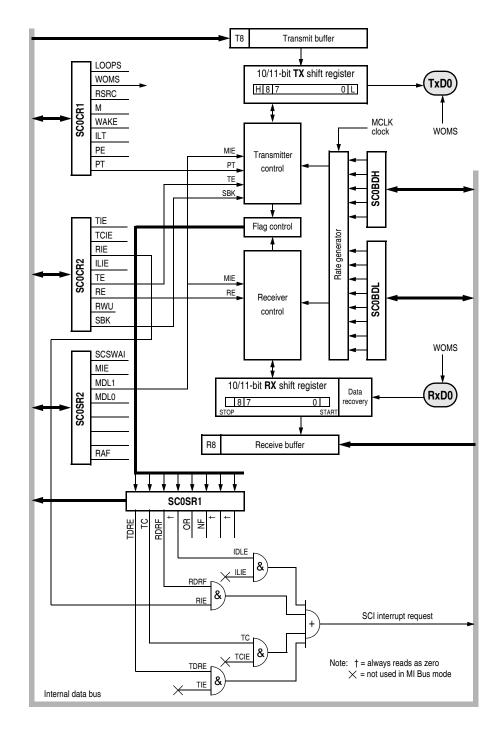

| 15.3 | Block diagram                                              |

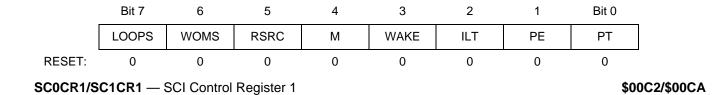

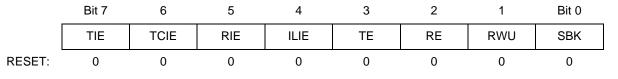

| 15.4 | Serial Communication Interface (SCI)                       |

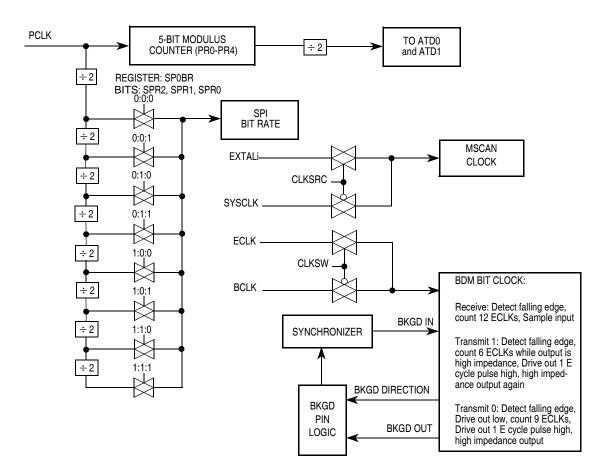

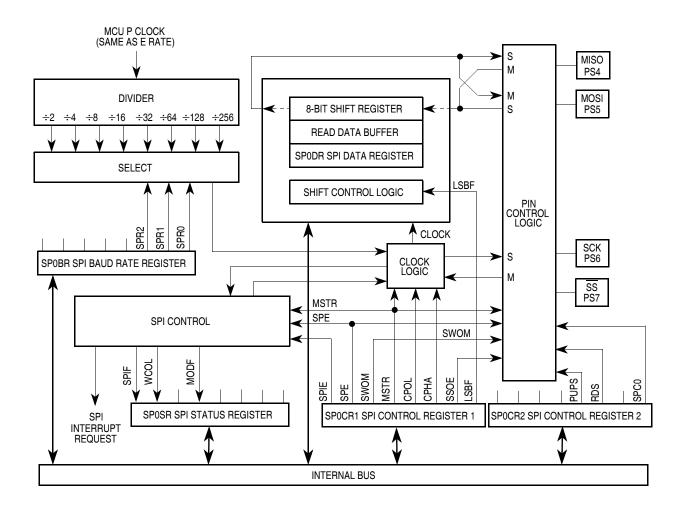

| 15.5 | Serial Peripheral Interface (SPI)276                       |

| 15.6 | Port S                                                     |

|      | Section 16. Freescale Interconnect Bus                     |

###

MC68HC912D60A — Rev. 3.1

### **Table of Contents**

| 16.2 | Introduction          |

|------|-----------------------|

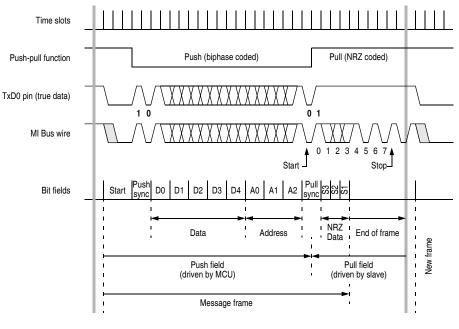

| 16.3 | Push-pull sequence    |

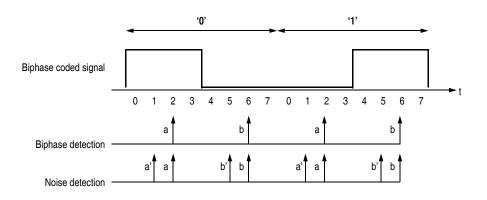

| 16.4 | Biphase coding        |

| 16.5 | Message validation    |

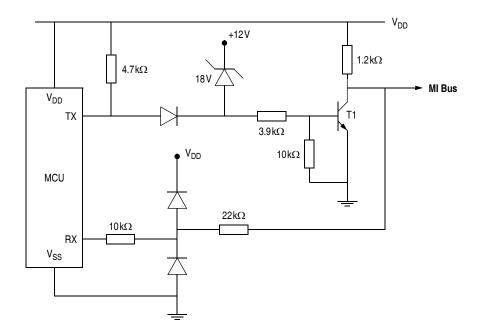

| 16.6 | Interfacing to MI Bus |

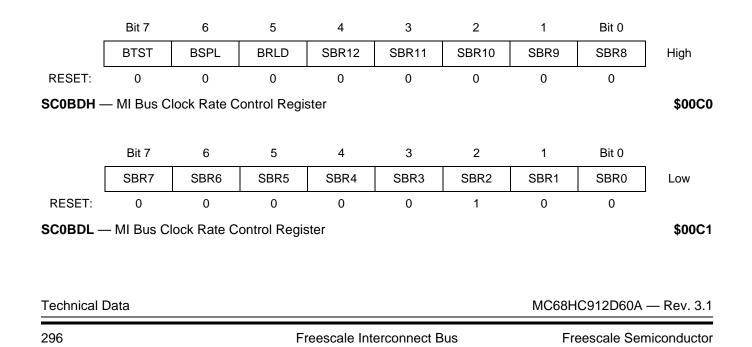

| 16.7 | MI Bus clock rate     |

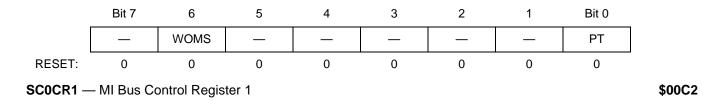

| 16.8 | SCI0/MI Bus registers |

### Section 17. MSCAN Controller

| 17.1  | Contents                                |

|-------|-----------------------------------------|

| 17.2  | Introduction                            |

| 17.3  | External Pins                           |

| 17.4  | Message Storage                         |

| 17.5  | Identifier Acceptance Filter            |

| 17.6  | Interrupts                              |

| 17.7  | Protocol Violation Protection           |

| 17.8  | Low Power Modes                         |

| 17.9  | Timer Link                              |

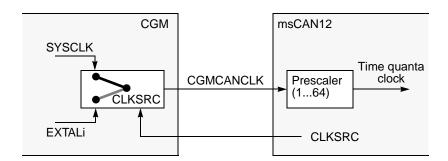

| 17.10 | Clock System                            |

| 17.11 | Memory Map                              |

| 17.12 | Programmer's Model of Message Storage   |

| 17.13 | Programmer's Model of Control Registers |

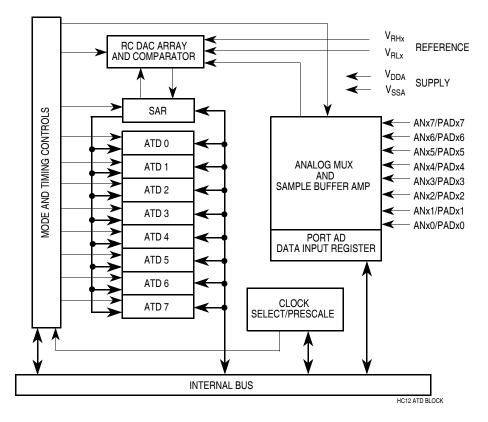

### Section 18. Analog-to-Digital Converter

| 18.1 | Contents           | 349 |

|------|--------------------|-----|

| 18.2 |                    | 349 |

| 18.3 | Modes of Operation | 351 |

**Technical Data**

12

| 18.4 | Functional Description                       |

|------|----------------------------------------------|

| 18.5 | ATD Operational Modes                        |

| 18.6 | ATD Operation In Different MCU Modes         |

| 18.7 | General Purpose Digital Input Port Operation |

| 18.8 | Application Considerations                   |

| 18.9 | ATD Registers                                |

### **Section 19. Development Support**

| 19.1 | Contents              |

|------|-----------------------|

| 19.2 | Introduction          |

| 19.3 | Instruction Queue     |

| 19.4 | Background Debug Mode |

| 19.5 | Breakpoints           |

| 19.6 | Instruction Tagging   |

### **Section 20. Electrical Specifications**

| 20.1 | Contents       | 405 |

|------|----------------|-----|

| 20.2 |                | 405 |

| 20.3 | Tables of Data | 406 |

### Section 21. Appendix: CGM Practical Aspects

| 21.1 | Contents                            |

|------|-------------------------------------|

| 21.2 | Introduction                        |

| 21.3 | Practical Aspects For The PLL Usage |

| 21.4 | Printed Circuit Board Guidelines    |

### Section 22. Appendix: Changes from MC68HC912D60

| 22.1  | Contents | 437 |

|-------|----------|-----|

| ZZ. I | Contents | t   |

Freescale Semiconductor

13

### **Table of Contents**

| 22.2 | Significant changes from the MC68HC912D60<br>(non-suffix device)    |

|------|---------------------------------------------------------------------|

| Sec  | tion 23. Appendix: Information on MC68HC912D60A<br>Mask Set Changes |

| 23.1 | Contents                                                            |

| 23.2 | Introduction                                                        |

| 23.3 | Flash Protection Feature443                                         |

| 23.4 | Clock Circuitry                                                     |

| 23.5 | Pseudo Stop Mode                                                    |

| 23.6 | Oscillator                                                          |

| 23.7 | PLL                                                                 |

|      |                                                                     |

### **Technical Data — Glossary**

### **Technical Data — Revision History**

| 23.8  | Contents                              | 457 |

|-------|---------------------------------------|-----|

| 23.9  | Changes from Rev 2.0 to Rev 3.0       | 457 |

| 23.10 | Major Changes From Rev 1.0 to Rev 2.0 | 457 |

| 23.11 | Major Changes From Rev 0.0 to Rev 1.0 | 458 |

# List of Figures

| Figur | e Title                                                | Page |

|-------|--------------------------------------------------------|------|

| 1-1   | MC68HC912D60A 112-pin QFP Block Diagram                | 29   |

| 1-2   | MC68HC912D60A 80-pin QFP Block Diagram                 | 30   |

| 2-1   | Programming Model                                      | 32   |

| 3-1   | Pin Assignments in 112-pin TQFP for MC68HC912D60A      |      |

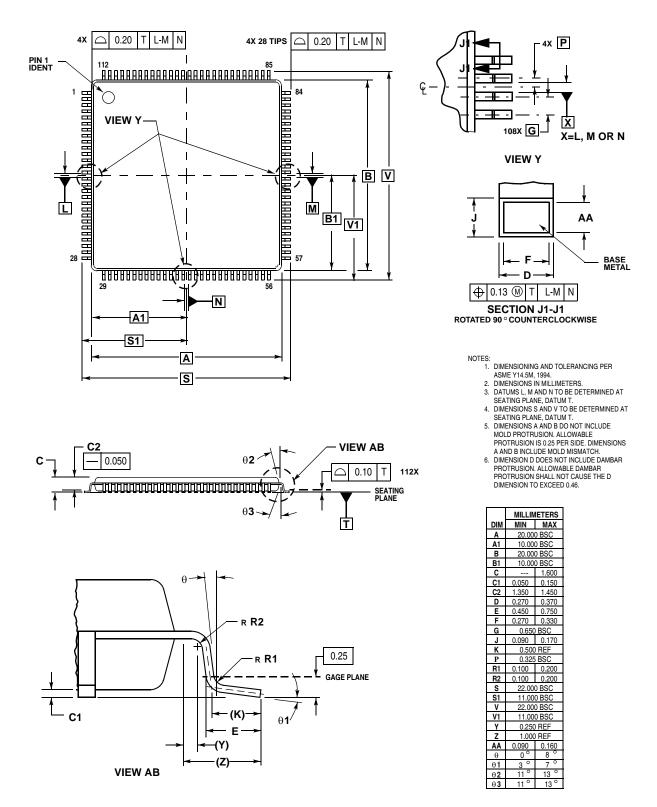

| 3-2   | 112-pin TQFP Mechanical Dimensions (case no987)        | 39   |

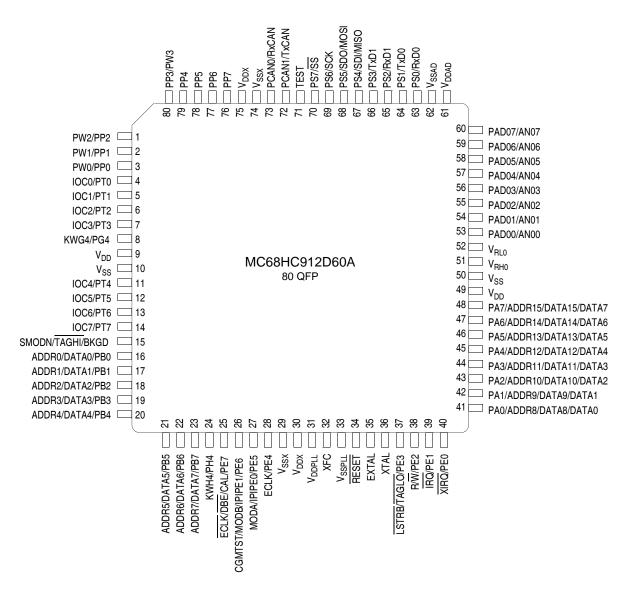

| 3-3   | Pin Assignments in 80-pin QFP for MC68HC912D60A.       | 40   |

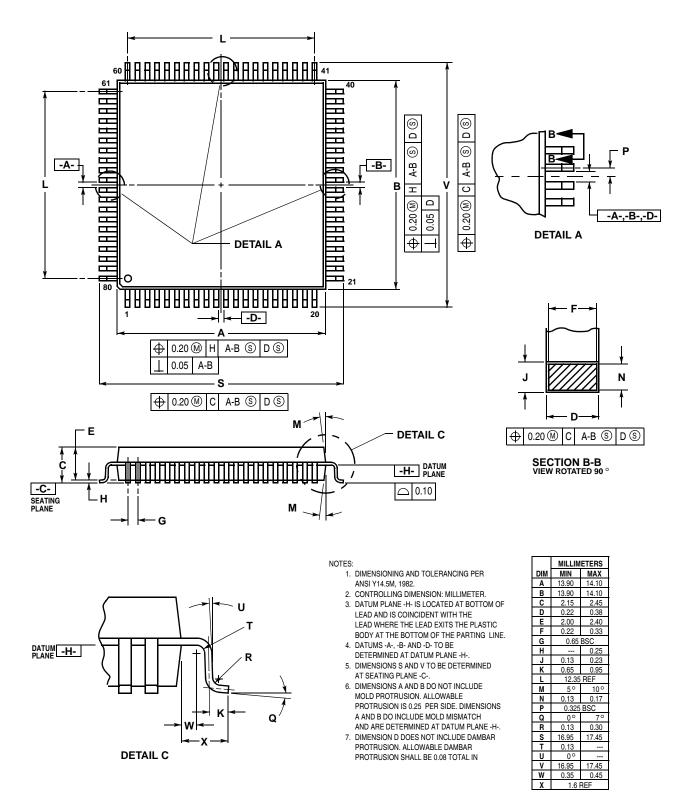

| 3-4   | 80-pin QFP Mechanical Dimensions (case no841B)         | 41   |

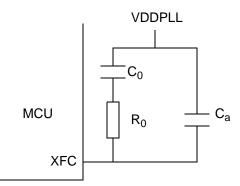

| 3-5   | PLL Loop Filter Connections                            | 43   |

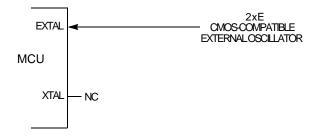

| 3-6   | External Oscillator Connections                        | 45   |

| 5-1   | MC68HC912D60A Memory Map                               |      |

| 6-1   | Access Type vsBus Control Pins                         | 86   |

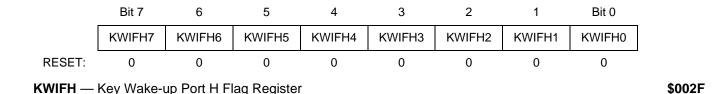

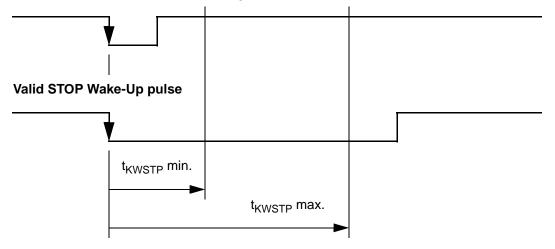

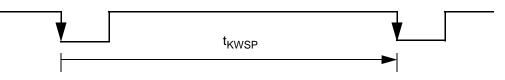

| 10-1  | STOP Key Wake-up Filter (falling edge trigger) timing. |      |

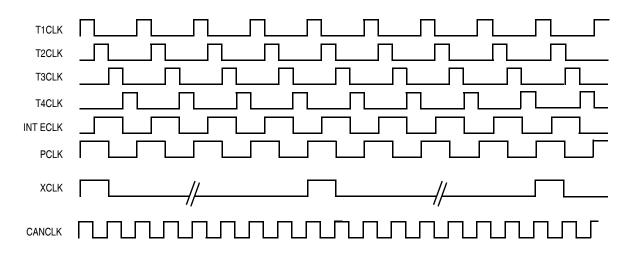

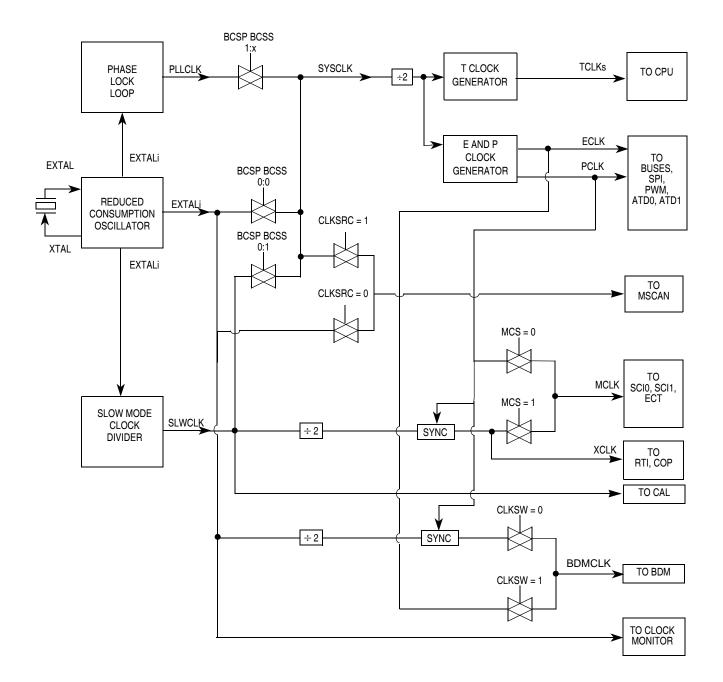

| 11-1  | Internal Clock Relationships                           | 139  |

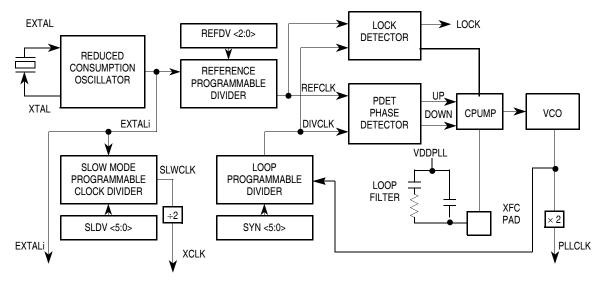

| 11-2  | PLL Functional Diagram                                 |      |

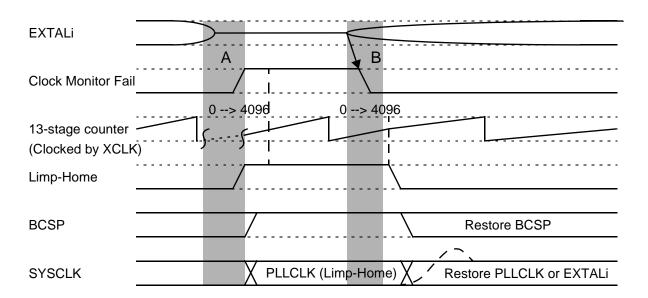

| 11-3  | Clock Loss during Normal Operation                     |      |

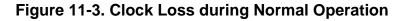

| 11-4  | No Clock at Power-On Reset                             |      |

| 11-5  | STOP Exit and Fast STOP Recovery                       |      |

| 11-6  | Clock Generation Chain                                 |      |

| 11-7  | Clock Chain for SCI0, SCI1, RTI, COP.                  |      |

| 11-8  | Clock Chain for ECT                                    |      |

| 11-9  | Clock Chain for MSCAN, SPI, ATD0, ATD1 and BDM         |      |

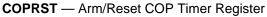

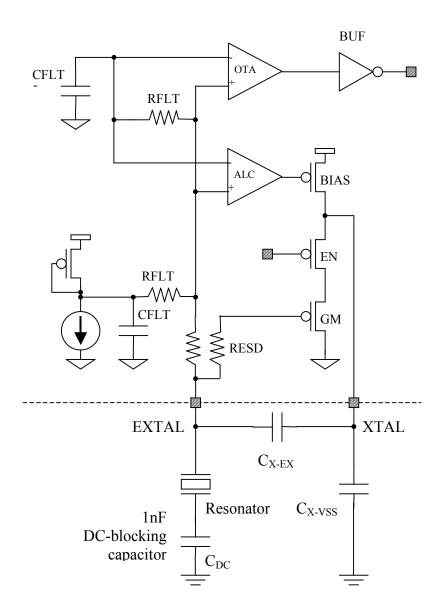

| 12-1  | MC68HC912D60A Colpitts Oscillator Architecture         |      |

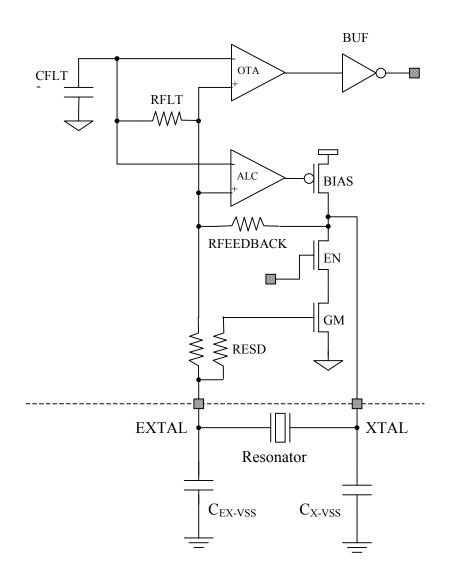

| 12-2  | MC68HC912D60C Colpitts Oscillator Architecture         |      |

| 12-3  | MC68HC912D60C Crystal with DC Blocking Capacitor.      |      |

| 12-4  | MC68HC912D60P Pierce Oscillator Architecture.          |      |

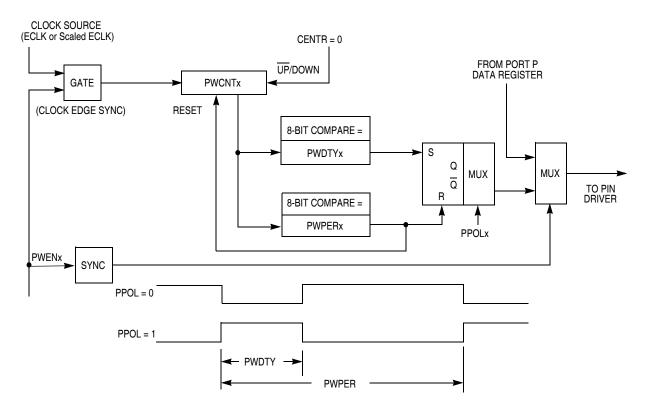

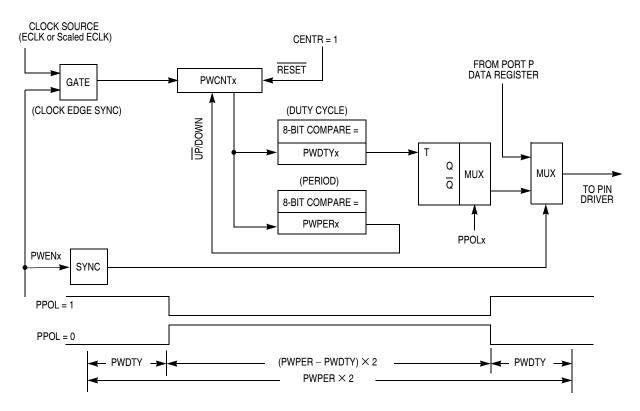

| 13-1  | Block Diagram of PWM Left-Aligned Output Channel       |      |

| 13-2  | Block Diagram of PWM Center-Aligned Output Channel     |      |

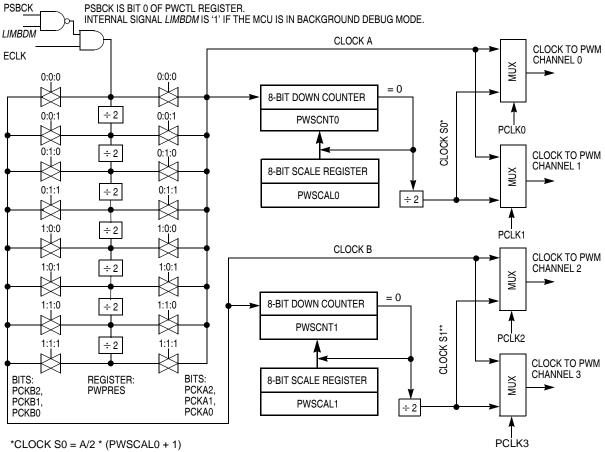

| 13-3  | PWM Clock Sources.                                     |      |

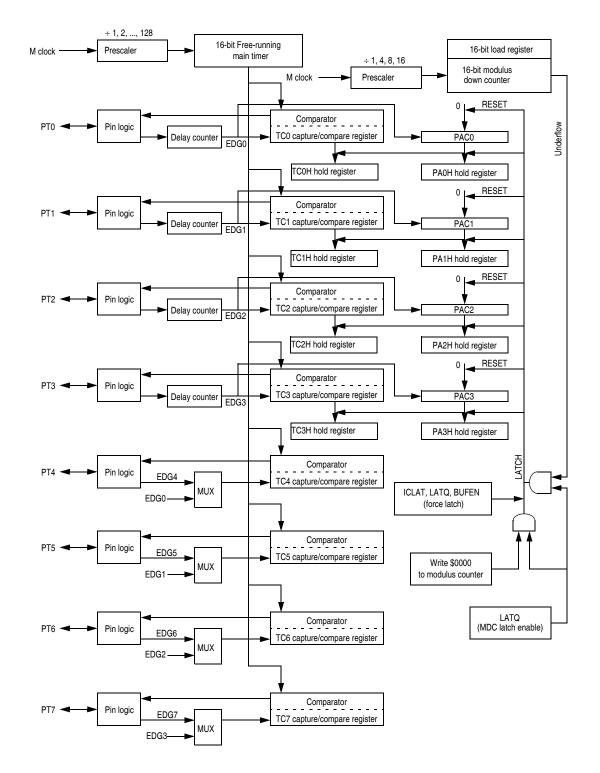

| 14-1  | Timer Block Diagram in Latch Mode.                     |      |

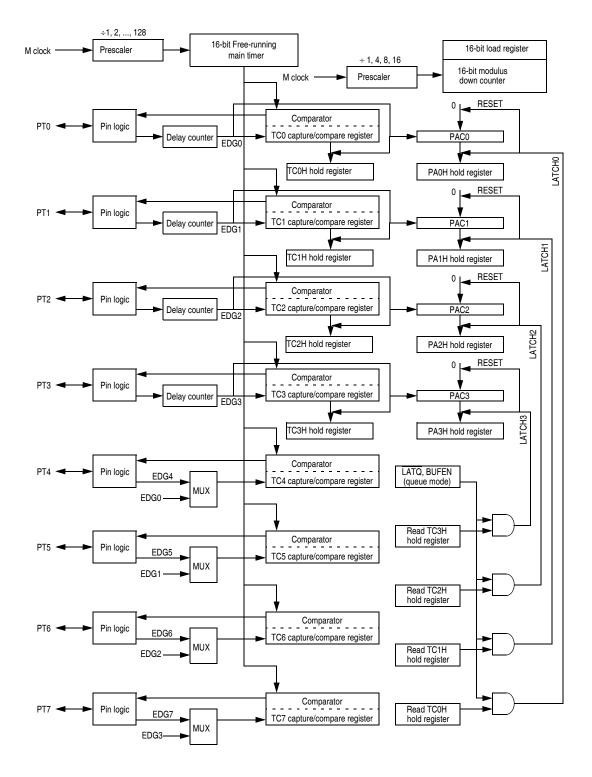

| 14-2  | Timer Block Diagram in Queue Mode.                     | 226  |

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

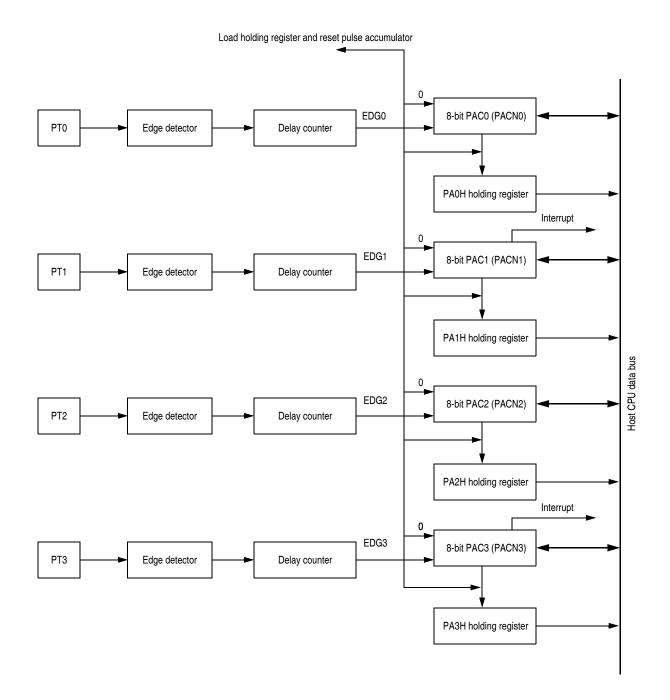

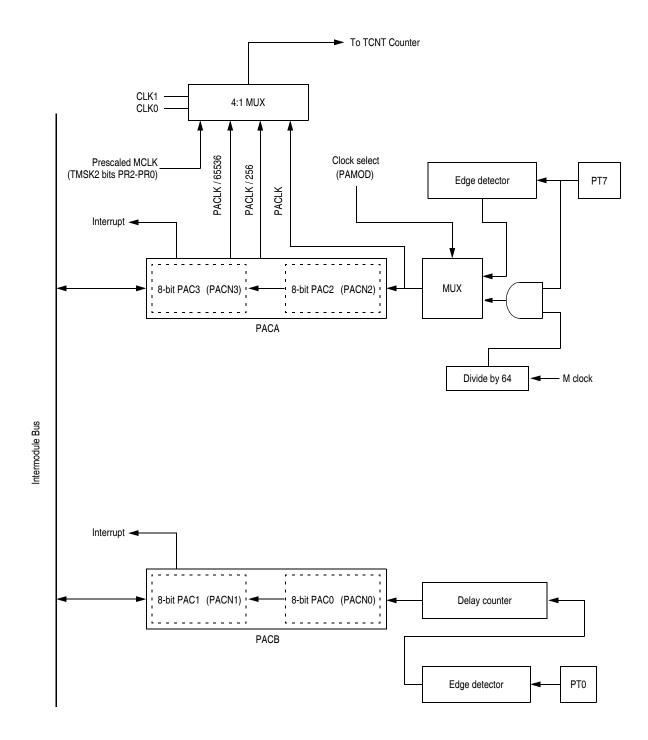

| 14-3  | 8-Bit Pulse Accumulators Block Diagram         | 227 |

|-------|------------------------------------------------|-----|

| 14-4  | 16-Bit Pulse Accumulators Block Diagram        | 228 |

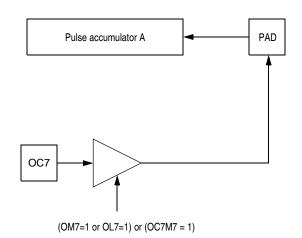

| 14-5  | Block Diagram for Port7 with Output compare /  |     |

|       | Pulse Accumulator A                            | 229 |

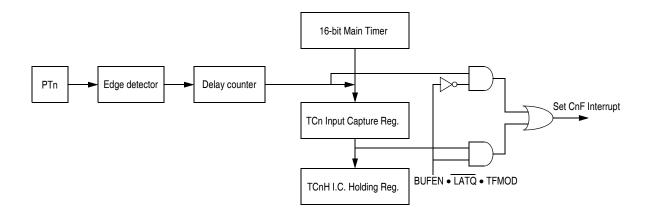

| 14-6  | C3F-C0F Interrupt Flag Setting                 | 229 |

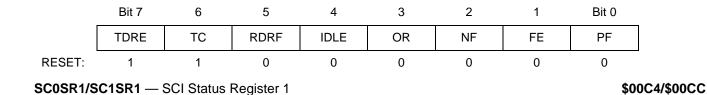

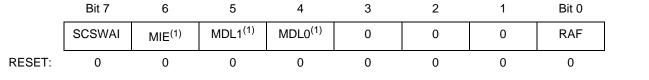

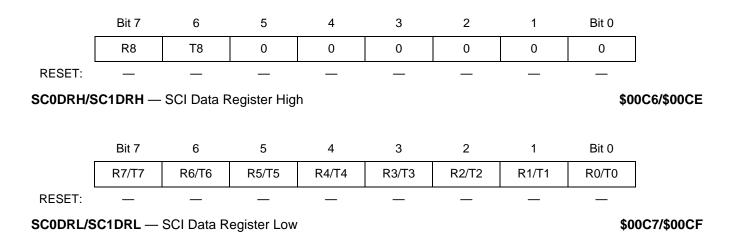

| 15-1  | Multiple Serial Interface Block Diagram        | 264 |

| 15-2  | Serial Communications Interface Block Diagram  | 265 |

| 15-3  | Serial Peripheral Interface Block Diagram      | 277 |

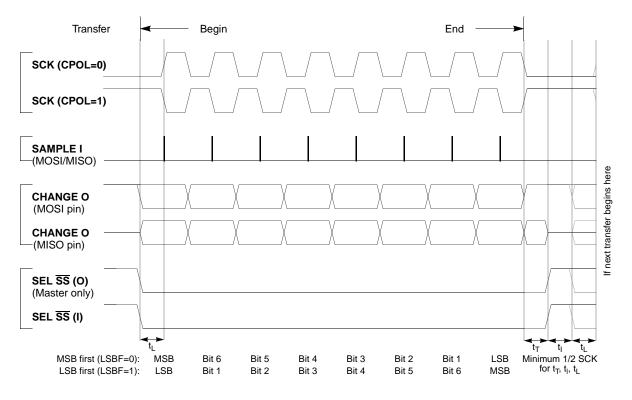

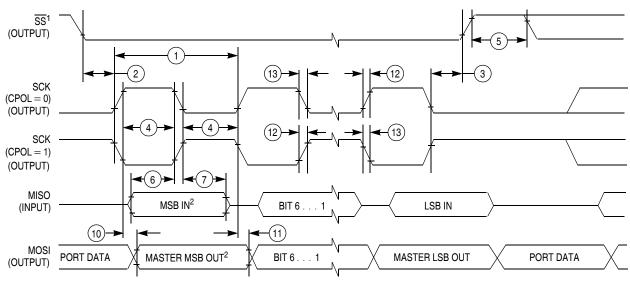

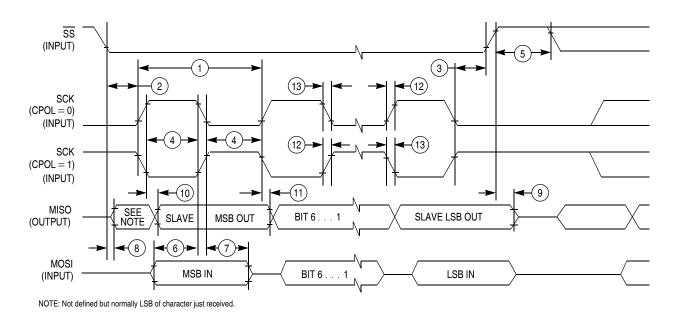

| 15-4  | SPI Clock Format 0 (CPHA = 0)                  | 278 |

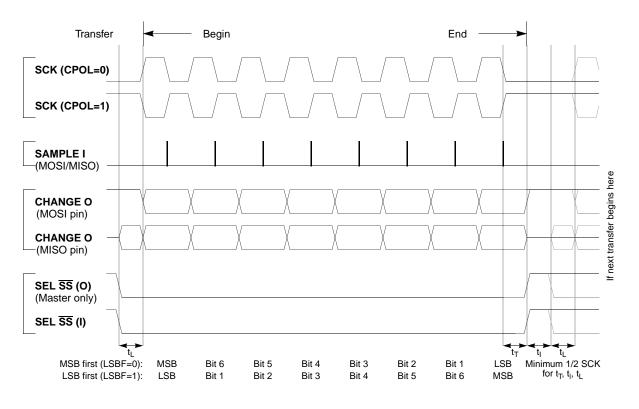

| 15-5  | SPI Clock Format 1 (CPHA = 1)                  | 279 |

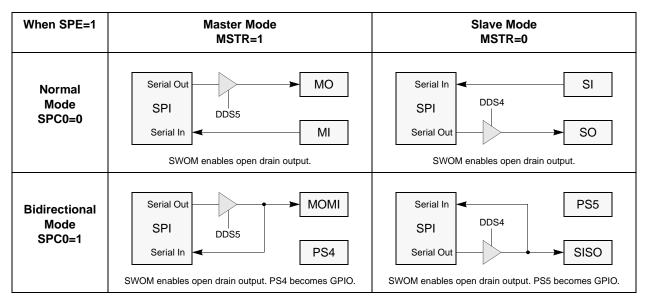

| 15-6  | Normal Mode and Bidirectional Mode             | 280 |

| 16-1  | MI Bus timing                                  | 290 |

| 16-2  | Biphase coding and error detection             | 292 |

| 16-3  | MI BUS Block Diagram                           | 293 |

| 16-4  | A typical MI Bus interface                     | 295 |

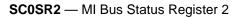

| 17-1  | The CAN System                                 |     |

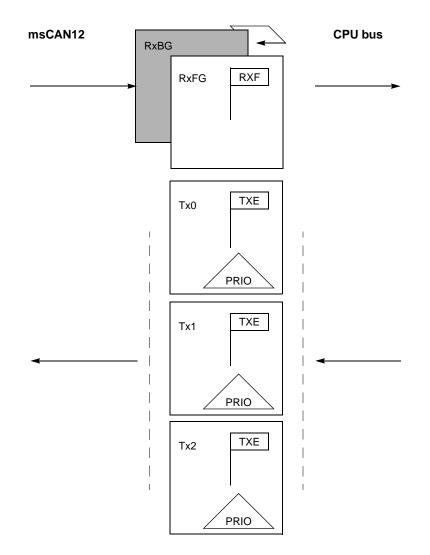

| 17-2  | User Model for Message Buffer Organization.    | 308 |

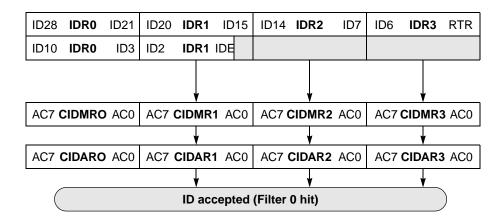

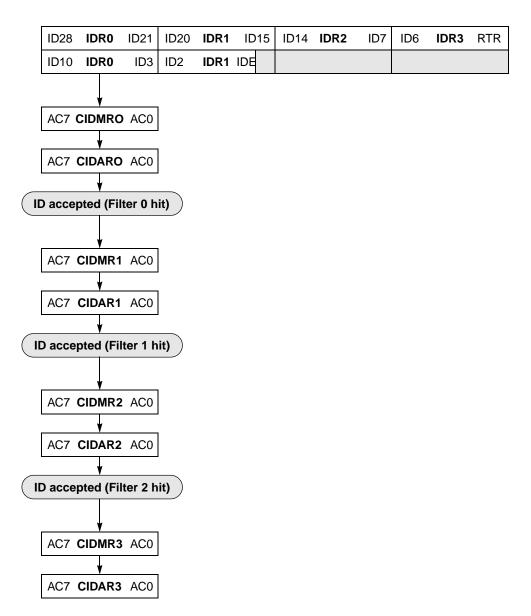

| 17-3  | 32-bit Maskable Identifier Acceptance Filters  | 312 |

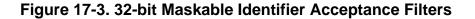

| 17-4  | 16-bit Maskable Acceptance Filters             |     |

| 17-5  | 8-bit Maskable Acceptance Filters              |     |

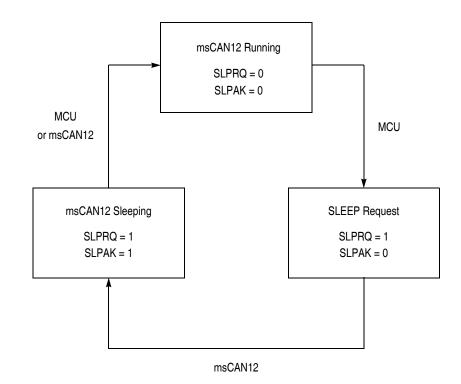

| 17-6  | SLEEP Request / Acknowledge Cycle              |     |

| 17-7  | Clocking Scheme                                |     |

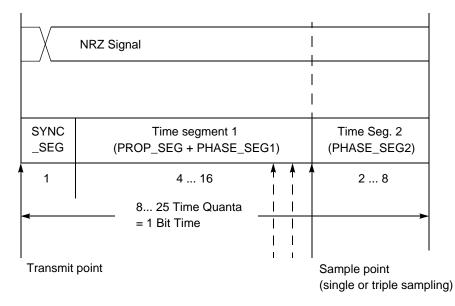

| 17-8  | Segments within the Bit Time                   |     |

| 17-9  | msCAN12 Memory Map                             |     |

| 17-10 | Message Buffer Organization                    |     |

| 17-11 |                                                |     |

| 17-12 |                                                |     |

| 18-1  | Analog-to-Digital Converter Block Diagram      |     |

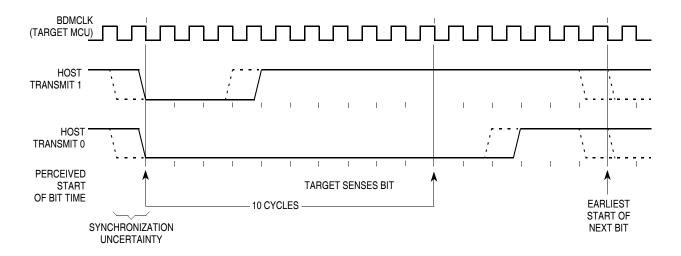

| 19-1  | BDM Host to Target Serial Bit Timing           |     |

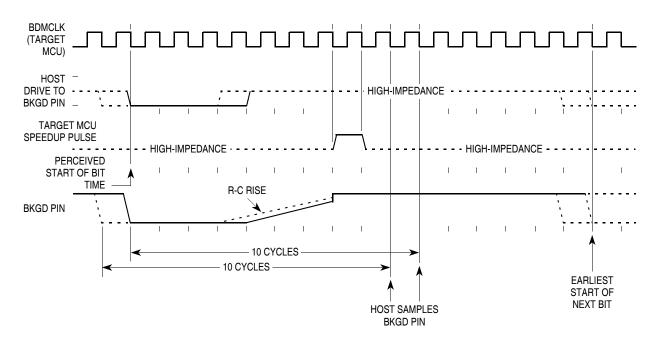

| 19-2  | BDM Target to Host Serial Bit Timing (Logic 1) |     |

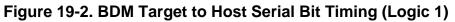

| 19-3  | BDM Target to Host Serial Bit Timing (Logic 0) |     |

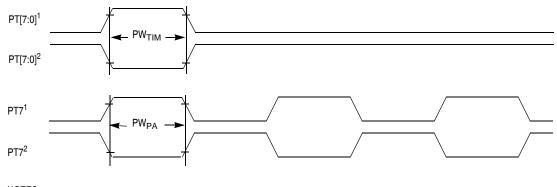

| 20-1  | Timer Inputs                                   |     |

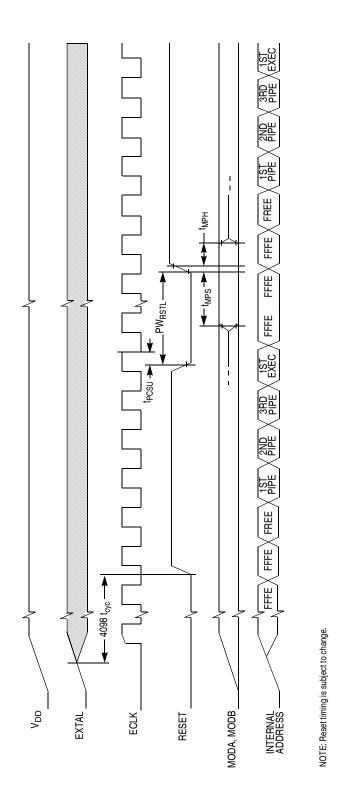

| 20-2  | POR and External Reset Timing Diagram          |     |

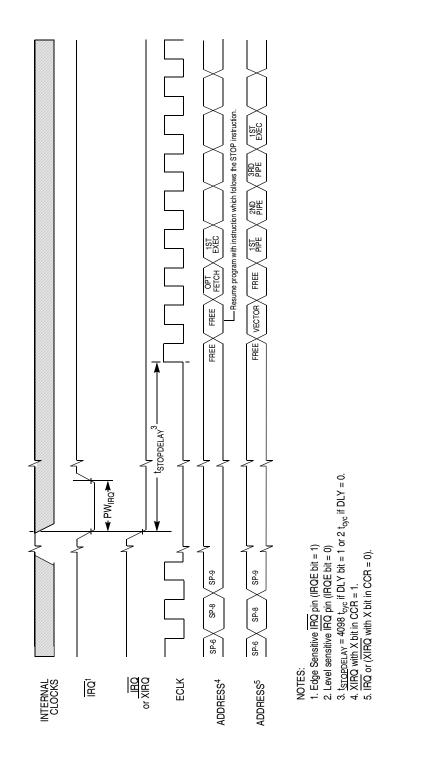

| 20-3  | STOP Recovery Timing Diagram                   | 416 |

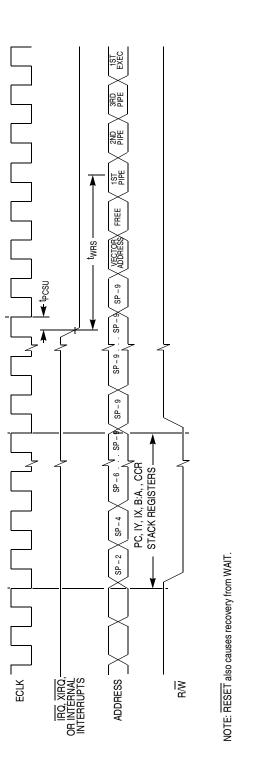

| 20-4  | WAIT Recovery Timing Diagram                   | 417 |

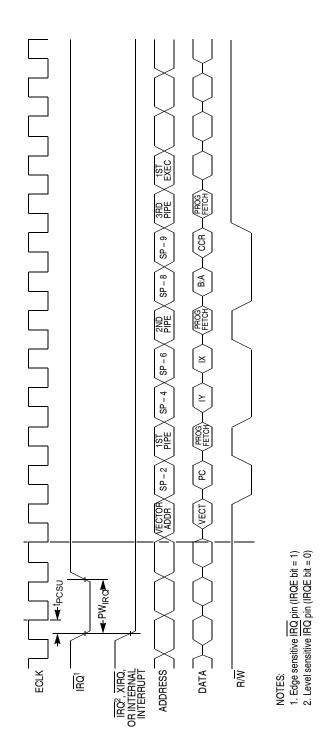

| 20-5  | Interrupt Timing Diagram                       |     |

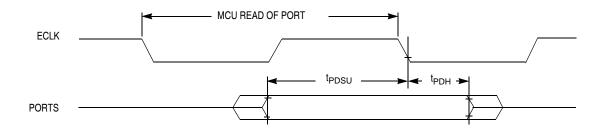

| 20-6  | Port Read Timing Diagram                       | 419 |

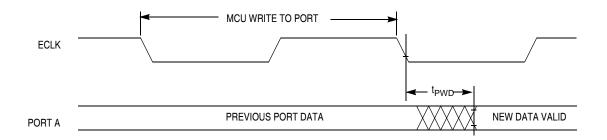

| 20-7  | Port Write Timing Diagram                      | 419 |

|       |                                                |     |

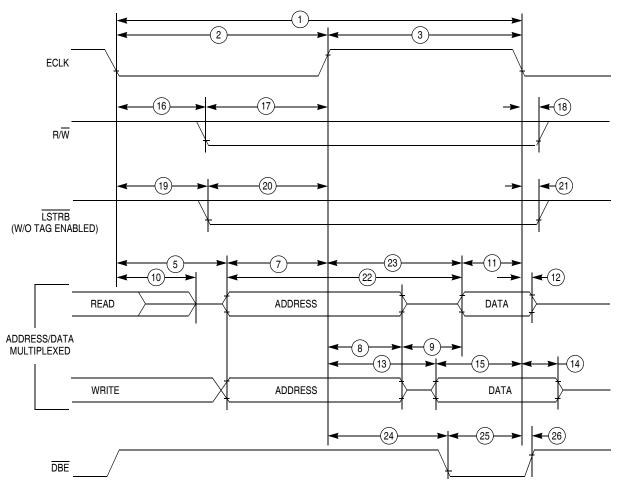

| 20-8  | Multiplexed Expansion Bus Timing Diagram4 | 21 |

|-------|-------------------------------------------|----|

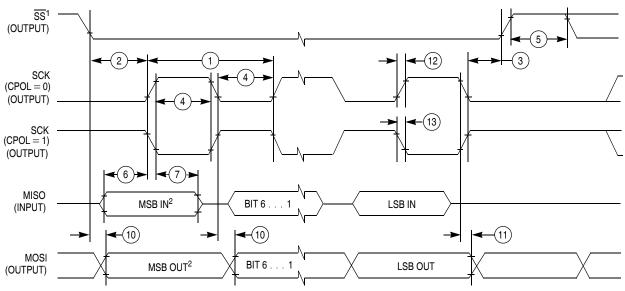

| 20-9  | SPI Timing Diagram (1 of 2)4              | 23 |

| 20-10 | SPI Timing Diagram (2 of 2)4              | 24 |

17

**Technical Data**

List of Figures

MC68HC912D60A — Rev. 3.1

## **List of Tables**

| Table | Title                                             | Page |

|-------|---------------------------------------------------|------|

| 1-1   | Device Ordering Information                       | 27   |

| 1-2   | Development Tools Ordering Information            | 28   |

| 2-1   | M68HC12 Addressing Mode Summary                   | 34   |

| 2-2   | Summary of Indexed Operations                     | 35   |

| 3-1   | MC68HC912D60A Power and Ground Connection Summar  | y.44 |

| 3-2   | MC68HC912D60A Signal Description Summary          | 50   |

| 3-3   | MC68HC912D60A Port Description Summary            | 59   |

| 3-4   | Port Pull-Up, Pull-Down and Reduced Drive Summary | 60   |

| 4-1   | MC68HC912D60A Register Map                        | 62   |

| 5-1   | Mode Selection                                    | 72   |

| 5-2   | Mapping Precedence                                | 78   |

| 5-3   | RFSTR Stretch Bit Definition                      | 82   |

| 5-4   | EXSTR Stretch Bit Definition                      | 82   |

| 8-1   | EEDIV Selection                                   | .109 |

| 8-2   | 1K byte EEPROM Block Protection                   | .112 |

| 8-3   | Erase Selection.                                  | .113 |

| 8-4   | Shadow word mapping                               | .115 |

| 9-1   | Interrupt Vector Map                              | .122 |

| 9-2   | Stacking Order on Entry to Interrupts             | .128 |

| 11-1  | Summary of STOP Mode Exit Conditions              | .155 |

| 11-2  | Summary of Pseudo STOP Mode Exit Conditions       | .155 |

| 11-3  | Clock Monitor Time-Outs                           | .167 |

| 11-4  | Real Time Interrupt Rates.                        | .169 |

| 11-5  | COP Watchdog Rates                                | .172 |

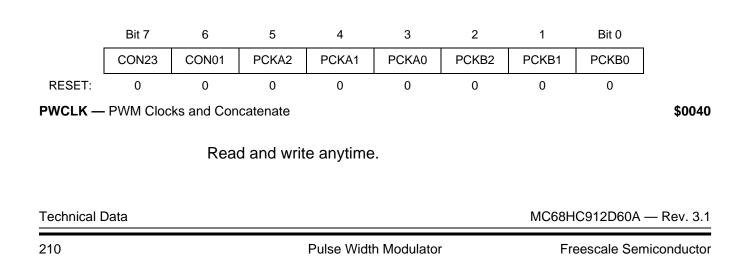

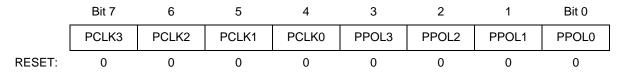

| 13-1  | Clock A and Clock B Prescaler                     | .212 |

| 13-2  | PWM Left-Aligned Boundary Conditions              | .222 |

| 13-3  | PWM Center-Aligned Boundary Conditions            | .222 |

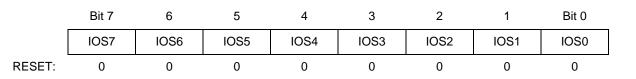

| 14-1  | Compare Result Output Action                      | .238 |

| 14-2  | Edge Detector Circuit Configuration               | .238 |

Freescale Semiconductor

List of Tables

| 14-3  | Prescaler Selection                                    | .240  |

|-------|--------------------------------------------------------|-------|

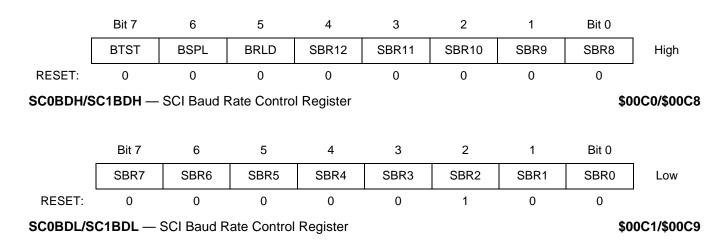

| 15-1  | Baud Rate Generation                                   | .266  |

| 15-2  | Loop Mode Functions                                    | .269  |

| 15-3  | SS Output Selection                                    | .279  |

| 15-4  | SPI Clock Rate Selection                               | .283  |

| 16-1  | MI Bus Delay                                           | .301  |

| 17-1  | msCAN12 Interrupt Vectors                              | .315  |

| 17-2  | msCAN12 vsCPU operating modes                          | .317  |

| 17-3  | CAN Standard Compliant Bit Time Segment Settings       | . 323 |

| 17-4  | Data length codes                                      | . 328 |

| 17-5  | Synchronization jump width                             | . 333 |

| 17-6  | Baud rate prescaler                                    | .333  |

| 17-7  | Time segment syntax                                    | . 334 |

| 17-8  | Time segment values                                    | . 335 |

| 17-9  | Identifier Acceptance Mode Settings                    | .341  |

| 17-10 | Identifier Acceptance Hit Indication                   | .342  |

| 18-1  | Result Data Formats Available                          | .361  |

| 18-2  | Left Justified ATD Output Codes                        | .362  |

| 18-3  | ATD Response to Background Debug Enable                | . 364 |

| 18-4  | Final Sample Time Selection                            | .365  |

| 18-5  | Clock Prescaler Values.                                | . 366 |

| 18-6  | Conversion Sequence Length Coding                      | . 367 |

| 18-7  | Result Register Assignment for Different Conversion    |       |

|       | Sequences                                              | .367  |

| 18-8  | Special Channel Conversion Select Coding               | . 368 |

| 18-9  | Analog Input Channel Select Coding                     | . 369 |

| 18-10 | Multichannel Mode Result Register Assignment (MULT=1). | .370  |

| 19-1  | IPIPE Decoding                                         | .378  |

| 19-2  | Hardware Commands                                      | . 384 |

| 19-3  | BDM Firmware Commands                                  | . 385 |

| 19-4  | BDM registers                                          | .387  |

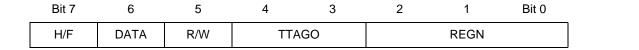

| 19-5  | TTAGO Decoding                                         | . 392 |

| 19-6  | TTAGO Value                                            | .392  |

| 19-7  | Instruction                                            | . 392 |

| 19-8  | REGN Decoding                                          | . 392 |

| 19-9  | Breakpoint Mode Control                                | . 398 |

| 19-10 | Breakpoint Address Range Control                       | . 399 |

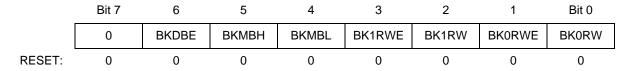

|       | Breakpoint Read/Write Control                          |       |

|       |                                                        |       |

**Technical Data**

| 19-12 | Tag Pin Function.                            | .403 |

|-------|----------------------------------------------|------|

| 20-1  | Maximum Ratings                              | .406 |

| 20-2  | Thermal Characteristics                      | .407 |

| 20-3  | DC Electrical Characteristics                | .408 |

| 20-4  | Supply Current                               | .409 |

| 20-5  | ATD DC Electrical Characteristics            | .409 |

| 20-6  | Analog Converter Characteristics (Operating) | .410 |

| 20-7  | ATD AC Characteristics (Operating)           | .410 |

| 20-8  | ATD Maximum Ratings                          | .411 |

| 20-9  | EEPROM Characteristics                       | .411 |

| 20-10 | Flash EEPROM Characteristics                 | .412 |

| 20-11 | Pulse Width Modulator Characteristics        | .412 |

| 20-12 | Control Timing                               | .413 |

| 20-13 | Peripheral Port Timing                       | .419 |

| 20-14 | Multiplexed Expansion Bus Timing.            | .420 |

| 20-15 | SPI Timing                                   | .422 |

| 20-16 | CGM Characteristics.                         | .425 |

|       | Oscillator Characteristics                   |      |

| 20-18 | Key Wake-up                                  | .426 |

| 20-19 | msCAN12 Wake-up Time from Sleep Mode         | .426 |

| 21-1  | Suggested 8MHz Synthesis PLL Filter Elements |      |

|       | (Tracking Mode)                              | .431 |

| 21-2  | Suggested 8MHz Synthesis PLL Filter Elements |      |

|       | (Acquisition Mode)                           | .432 |

|       |                                              |      |

21

### List of Tables

**Technical Data**

List of Tables

## **Section 1. General Description**

### 1.1 Contents

| 1.2 | Introduction                      | .23  |

|-----|-----------------------------------|------|

| 1.3 | Devices Covered in this Document. | .24  |

| 1.4 | Features                          | .24  |

| 1.5 | Ordering Information              | . 27 |

| 1.6 | Block Diagrams.                   | . 29 |

### **1.2 Introduction**

The MC68HC912D60A microcontroller unit (MCU) is a 16-bit device available in two package options, 80-pin QFP and 112-pin TQFP. Onchip peripherals include a 16-bit central processing unit (CPU12), 60K bytes of flash EEPROM, 2K bytes of RAM, 1K bytes of EEPROM, two asynchronous serial communication interfaces (SCI), a serial peripheral interface (SPI), an enhanced capture timer (ECT), two (one on 80QFP) 8-channel,10-bit analog-to-digital converters (ATD), a four-channel pulse-width modulator (PWM), and a CAN 2.0 A, B software compatible module (MSCAN12). System resource mapping, clock generation, interrupt control and bus interfacing are managed by the lite integration module (LIM). The MC68HC912D60A has full 16-bit data paths throughout, however, the external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements. In addition to the I/O ports available in each module, 16 (2 on 80QFP) I/O port pins are available with Key-Wake-Up capability from STOP or WAIT mode.

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

**General Description**

#### **1.3 Devices Covered in this Document**

The MC68HC912D60C and MC68HC912D60P are devices similar to the MC68HC912D60A, but with different oscillator configurations. Refer to Section 12. Oscillator for more details.

The generic term MC68HC912D60A is used throughout this document to mean all derivatives mentioned above, except in Section 12. Oscillator, where it refers only to the MC68HC912D60A device.

### **1.4 Features**

- 16-bit CPU12

- Upward compatible with M68HC11 instruction set

- Interrupt stacking and programmer's model identical to M68HC11

- 20-bit ALU

- Instruction queue

- Enhanced indexed addressing

- Multiplexed bus

- Single chip or expanded

- 16 address/16 data wide or 16 address/8 data narrow mode

- Two 8-bit ports with key wake-up interrupt (2 pins only are available on 80QFP) and one I<sup>2</sup>C start bit detector (112TQFP only)

- Memory

- 60K byte flash EEPROM, made of a 28K module and a 32K module with 8K bytes protected BOOT section in each module (MC68HC912D60A)

- 1K byte EEPROM

- 2K byte RAM

- Analog-to-digital converters

- 2 x 8-channels, 10-bit resolution in 112TQFP

- 1 x 8-channels, 8-bit resolution in 80QFP

- 1M bit per second, CAN 2.0 A, B software compatible module

- Two receive and three transmit buffers

- Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit or 8 x 8 bit

- Four separate interrupt channels for Rx, Tx, error and wake-up

- Low-pass filter wake-up function

- In 80QFP, only TxCAN and RxCAN pins are available

- Loop-back for self test operation

- Programmable link to a timer input capture channel, for timestamping and network synchronization.

- Enhanced capture timer (ECT)

- 16-bit main counter with 7-bit prescaler

- 8 programmable input capture or output compare channels; 4 of the 8 input captures with buffer

- Input capture filters and buffers, three successive captures on four channels, or two captures on four channels with a capture/compare selectable on the remaining four

- Four 8-bit or two 16-bit pulse accumulators

- 16-bit modulus down-counter with 4-bit prescaler

- Four user-selectable delay counters for signal filtering

- 4 PWM channels with programmable period and duty cycle

- 8-bit 4-channel or 16-bit 2-channel

- Separate control for each pulse width and duty cycle

- Center- or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

#### MC68HC912D60A — Rev. 3.1

#### **General Description**

- Serial interfaces

- Two asynchronous serial communications interfaces (SCI)

- MI-Bus implemented on final devices

- Synchronous serial peripheral interface (SPI)

- LIM (light integration module)

- WCR (windowed COP watchdog, real time interrupt, clock monitor)

- ROC (reset and clocks)

- MEBI (multiplexed external bus interface)

- MBI (internal bus interface and map)

- INT (interrupt control)

- Clock generation

- Phase-locked loop clock frequency multiplier

- Limp home mode in absence of external clock

- Slow mode divider

- Low power 0.5 to 16 MHz crystal oscillator reference clock

- Option of a Pierce or Colpitts oscillator

- 112-Pin TQFP package or 80-pin QFP package

- Up to 68 general-purpose I/O lines, plus up to 18 input-only lines in 112TQFP

- or

Up to 48 general-purpose I/O lines, plus up to 10 input-only lines in 80QFP

- 8MHz operation at 5V

- Development support

- Single-wire background debug<sup>™</sup> mode (BDM)

- On-chip hardware breakpoints

### 1.5 Ordering Information

| Baakaga                    | Ambient Temperature |            | Order Number  |

|----------------------------|---------------------|------------|---------------|

| Package                    | Range               | Designator |               |

| 112-Pin TQFP               | –40 to +85°C        | С          | MC912D60ACPV8 |

| Single Tray                | –40 to +105°C       | V          | MC912D60AVPV8 |

| 60 Pcs                     | –40 to +125°C       | M*         | MC912D60AMPV8 |

| 80-Pin TQFP                | –40 to +85°C        | С          | MC912D60ACFU8 |

| Single Tray                | –40 to +105°C       | V          | MC912D60AVFU8 |

| 84 Pcs                     | –40 to +125°C       | M*         | MC912D60AMFU8 |

| 112-Pin TQFP               | –40 to +85°C        | С          | MC912D60CCPV8 |

| Single Tray                | –40 to +105°C       | V          | MC912D60CVPV8 |

| 60 Pcs                     | –40 to +125°C       | M*         | MC912D60CMPV8 |

| 80-Pin TQFP<br>Single Tray | –40 to +85°C        | С          | MC912D60CCFU8 |

|                            | –40 to +105°C       | V          | MC912D60CVFU8 |

| 84 Pcs                     | –40 to +125°C       | M*         | MC912D60CMFU8 |

| 112-Pin TQFP               | –40 to +85°C        | С          | MC912D60PCPV8 |

| Single Tray                | –40 to +105°C       | V          | MC912D60PVPV8 |

| 60 Pcs                     | –40 to +125°C       | M*         | MC912D60PMPV8 |

| 80-Pin TQFP                | –40 to +85°C        | С          | MC912D60PCFU8 |

| Single Tray                | –40 to +105°C       | V          | MC912D60PVFU8 |

| 84 Pcs                     | –40 to +125°C       | M*         | MC912D60PMFU8 |

#### Table 1-1. Device Ordering Information

\* Important: M temperature operation is available only for single chip modes

| Description            | Name | Order Number                                           |

|------------------------|------|--------------------------------------------------------|

| MCUez                  |      | Free from World Wide Web                               |

| Serial Debug Interface | SDI  | M68SDIL (3–5V), M68DIL12 (SDIL + MCUez +<br>SDBUG12)   |

| Evaluation board       | EVB  | M68EVB912D60 (EVB only)<br>M68KIT912D60 (EVB + SDIL12) |

| Table 1-2. Development 7 | <b>Fools Ordering Information</b> |

|--------------------------|-----------------------------------|

|--------------------------|-----------------------------------|

**NOTE:** SDBUG12 is a P & E Micro Product. It can be obtained from P & E from their web site (http://www.pemicro.com) for approximately \$100.

Third party tools: http://www.mcu.motsps.com/dev\_tools/3rd/index.html

Technical Data

### 1.6 Block Diagrams

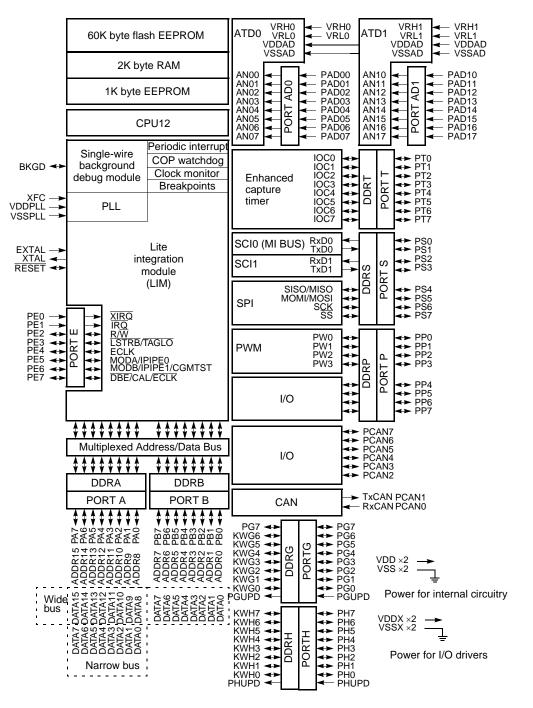

Figure 1-1. MC68HC912D60A 112-pin QFP Block Diagram

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

**General Description**

#### **General Description**

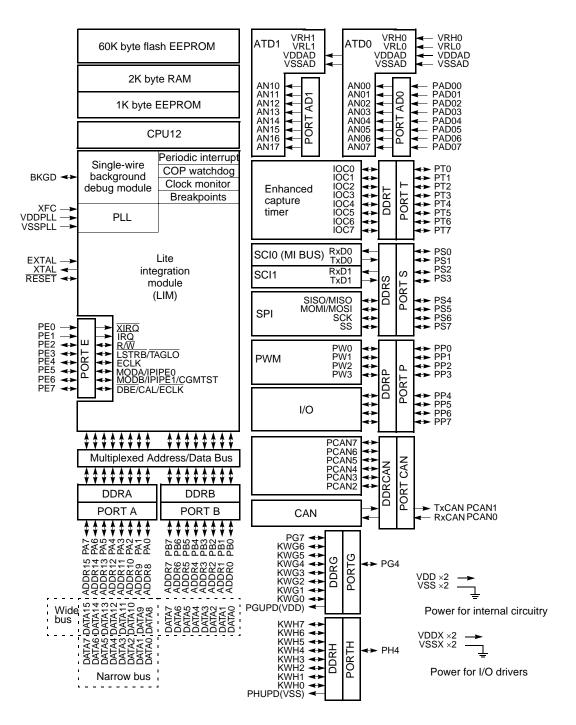

**Note:** Several I/O on ports G, H and CAN are unavailable externally on the 80-pin QFP package. These internal pins should either be defined as outputs or have their pull-ups/downs enabled.

#### Figure 1-2. MC68HC912D60A 80-pin QFP Block Diagram

**Technical Data**

MC68HC912D60A — Rev. 3.1

**General Description**

## **Section 2. Central Processing Unit**

#### 2.1 Contents

| 2.2 | Introduction             |

|-----|--------------------------|

| 2.3 | Programming Model        |

| 2.4 | Data Types               |

| 2.5 | Addressing Modes         |

| 2.6 | Indexed Addressing Modes |

| 2.7 | Opcodes and Operands     |

### 2.2 Introduction

The CPU12 is a high-speed, 16-bit processing unit. It has full 16-bit data paths and wider internal registers (up to 20 bits) for high-speed extended math instructions. The instruction set is a proper superset of the M68HC11instruction set. The CPU12 allows instructions with odd byte counts, including many single-byte instructions. This provides efficient use of ROM space. An instruction queue buffers program information so the CPU always has immediate access to at least three bytes of machine code at the start of every instruction. The CPU12 also offers an extensive set of indexed addressing capabilities.

### 2.3 Programming Model

CPU12 registers are an integral part of the CPU and are not addressed as if they were memory locations.

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

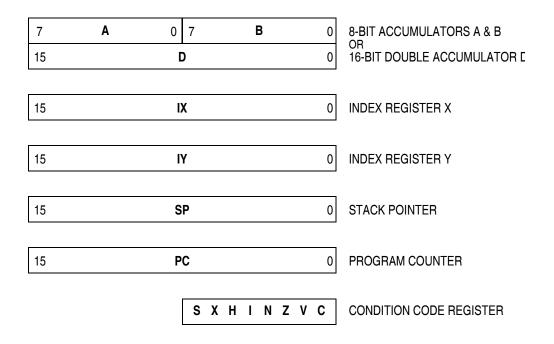

Figure 2-1. Programming Model

Accumulators A and B are general-purpose 8-bit accumulators used to hold operands and results of arithmetic calculations or data manipulations. Some instructions treat the combination of these two 8bit accumulators as a 16-bit double accumulator (accumulator D).

**Index registers** X and Y are used for indexed addressing mode. In the indexed addressing mode, the contents of a 16-bit index register are added to 5-bit, 9-bit, or 16-bit constants or the content of an accumulator to form the effective address of the operand to be used in the instruction.

**Stack pointer** (SP) points to the last stack location used. The CPU12 supports an automatic program stack that is used to save system context during subroutine calls and interrupts, and can also be used for temporary storage of data. The stack pointer can also be used in all indexed addressing modes.

**Program counter** is a 16-bit register that holds the address of the next instruction to be executed. The program counter can be used in all indexed addressing modes except autoincrement/decrement.

Technical Data

**Condition Code Register** (CCR) contains five status indicators, two interrupt masking bits, and a STOP disable bit. The five flags are half carry (H), negative (N), zero (Z), overflow (V), and carry/borrow (C). The half-carry flag is used only for BCD arithmetic operations. The N, Z, V, and C status bits allow for branching based on the results of a previous operation.

After a reset, the CPU fetches a vector from the appropriate address and begins executing instructions. The X and I interrupt mask bits are set to mask any interrupt requests. The S bit is also set to inhibit the STOP instruction.

#### 2.4 Data Types

The CPU12 supports the following data types:

- Bit data

- 8-bit and 16-bit signed and unsigned integers

- 16-bit unsigned fractions

- 16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A word is composed of two consecutive bytes with the most significant byte at the lower value address. There are no special requirements for alignment of instructions or operands.

#### 2.5 Addressing Modes

Addressing modes determine how the CPU accesses memory locations to be operated upon. The CPU12 includes all of the addressing modes of the M68HC11 CPU as well as several new forms of indexed addressing. Table 2-1 is a summary of the available addressing modes.

MC68HC912D60A — Rev. 3.1

| Addressing Mode                            | Source Format                                | Abbreviation | Description                                                                                                             |

|--------------------------------------------|----------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Inherent                                   | INST<br>(no externally<br>supplied operands) | INH          | Operands (if any) are in CPU registers                                                                                  |

| Immediate                                  | INST #opr8i<br>or<br>INST #opr16i            | IMM          | Operand is included in instruction stream<br>8- or 16-bit size implied by context                                       |

| Direct                                     | INST opr8a                                   | DIR          | Operand is the lower 8-bits of an address in the range \$0000 – \$00FF                                                  |

| Extended                                   | INST opr16a                                  | EXT          | Operand is a 16-bit address                                                                                             |

| Relative                                   | INST rel8<br>or<br>INST rel16                | REL          | An 8-bit or 16-bit relative offset from the current pc is supplied in the instruction                                   |

| Indexed<br>(5-bit offset)                  | INST oprx5,xysp                              | IDX          | 5-bit signed constant offset from x, y, sp, or pc                                                                       |

| Indexed<br>(auto pre-decrement)            | INST oprx3,–xys                              | IDX          | Auto pre-decrement x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(auto pre-increment)            | INST oprx3,+xys                              | IDX          | Auto pre-increment x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(auto post-decrement)           | INST oprx3,xys–                              | IDX          | Auto post-decrement x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(auto post-increment)           | INST oprx3,xys+                              | IDX          | Auto post-increment x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(accumulator offset)            | INST abd,xysp                                | IDX          | Indexed with 8-bit (A or B) or 16-bit (D)<br>accumulator offset from x, y, sp, or pc                                    |

| Indexed<br>(9-bit offset)                  | INST oprx9,xysp                              | IDX1         | 9-bit signed constant offset from x, y, sp, or<br>pc<br>(lower 8-bits of offset in one extension byte)                  |

| Indexed<br>(16-bit offset)                 | INST oprx16,xysp                             | IDX2         | 16-bit constant offset from x, y, sp, or pc<br>(16-bit offset in two extension bytes)                                   |

| Indexed-Indirect<br>(16-bit offset)        | INST [oprx16,xysp]                           | [IDX2]       | Pointer to operand is found at<br>16-bit constant offset from x, y, sp, or pc<br>(16-bit offset in two extension bytes) |

| Indexed-Indirect<br>(D accumulator offset) | INST [D,xysp]                                | [D,IDX]      | Pointer to operand is found at<br>x, y, sp, or pc plus the value in D                                                   |

#### 2.6 Indexed Addressing Modes

The CPU12 indexed modes reduce execution time and eliminate code size penalties for using the Y index register. CPU12 indexed addressing uses a postbyte plus zero, one, or two extension bytes after the instruction opcode. The postbyte and extensions do the following tasks:

- Specify which index register is used.

- Determine whether a value in an accumulator is used as an offset.

- Enable automatic pre- or post-increment or decrement

- Specify use of 5-bit, 9-bit, or 16-bit signed offsets.

| Postbyte<br>Code (xb) | Source<br>Code<br>Syntax | Comments                                                                                                                                                                                            |  |

|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rr0nnnn               | ,r<br>n,r<br>—n,r        | 5-bit constant offset n = -16 to +15<br>rr can specify X, Y, SP, or PC                                                                                                                              |  |

| 111rr0zs n,r<br>_n,r  |                          | Constant offset (9- or 16-bit signed)<br>z-0 = 9-bit with sign in LSB of postbyte(s)<br>1 = 16-bit<br>if $z = s = 1$ , 16-bit offset indexed-indirect (see below)<br>rr can specify X, Y, SP, or PC |  |

| 111rr011              | [n,r]                    | <b>16-bit offset indexed-indirect</b><br>rr can specify X, Y, SP, or PC                                                                                                                             |  |

| rr1pnnnn              | n,—r n,+r<br>n,r— n,r+   | Auto pre-decrement/increment or Auto post-<br>decrement/increment;<br>p = pre-(0) or post-(1), n = -8 to -1, +1 to +8<br>rr can specify X, Y, or SP (PC not a valid choice)                         |  |

| 111rr1aa              | A,r<br>B,r<br>D,r        | Accumulator offset (unsigned 8-bit or 16-bit)<br>aa-00 = A<br>01 = B<br>10 = D (16-bit)<br>11 = see accumulator D offset indexed-indirect<br>rr can specify X, Y, SP, or PC                         |  |

| 111rr111              | [D,r]                    | Accumulator D offset indexed-indirect<br>rr can specify X, Y, SP, or PC                                                                                                                             |  |

Table 2-2. Summary of Indexed Operations

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

**Central Processing Unit**

#### 2.7 Opcodes and Operands

The CPU12 uses 8-bit opcodes. Each opcode identifies a particular instruction and associated addressing mode to the CPU. Several opcodes are required to provide each instruction with a range of addressing capabilities.

Only 256 opcodes would be available if the range of values were restricted to the number that can be represented by 8-bit binary numbers. To expand the number of opcodes, a second page is added to the opcode map. Opcodes on the second page are preceded by an additional byte with the value \$18.

To provide additional addressing flexibility, opcodes can also be followed by a postbyte or extension bytes. Postbytes implement certain forms of indexed addressing, transfers, exchanges, and loop primitives. Extension bytes contain additional program information such as addresses, offsets, and immediate data.

Technical Data

**Central Processing Unit**

# **Section 3. Pinout and Signal Descriptions**

# 3.1 Contents

| 3.2 | MC68HC912D60A Pin Assignments in 112-pin QFP38 |

|-----|------------------------------------------------|

| 3.3 | MC68HC912D60A Pin Assignments in 80-pin QFP40  |

| 3.4 | Power Supply Pins                              |

| 3.5 | Signal Descriptions44                          |

| 3.6 | Port Signals                                   |

MC68HC912D60A — Rev. 3.1

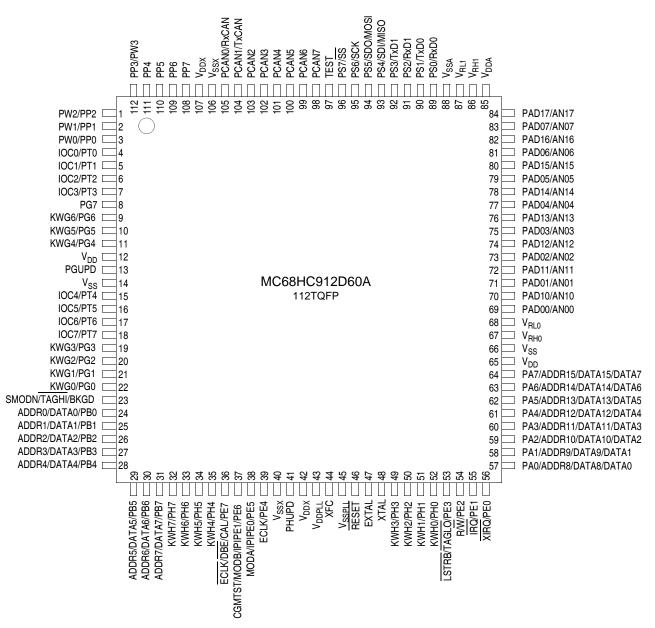

# 3.2 MC68HC912D60A Pin Assignments in 112-pin QFP

Note: TEST = This pin is used for factory test purposes. It is recommended that this pin is not connected in the application, but it may be bonded to 5.5 V max without issue. Never apply voltage higher than 5.5 V to this pin.

#### Figure 3-1. Pin Assignments in 112-pin TQFP for MC68HC912D60A

**Technical Data**

MC68HC912D60A — Rev. 3.1

Figure 3-2. 112-pin TQFP Mechanical Dimensions (case no. 987)

MC68HC912D60A — Rev. 3.1

# **Pinout and Signal Descriptions**

# 3.3 MC68HC912D60A Pin Assignments in 80-pin QFP

Note: TEST = This pin is used for factory test purposes. It is recommended that this pin is not connected in the application, but it may be bonded to 5.5 V max without issue. Never apply voltage higher than 5.5 V to this pin.

#### Figure 3-3. Pin Assignments in 80-pin QFP for MC68HC912D60A

Figure 3-4. 80-pin QFP Mechanical Dimensions (case no. 841B)

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

# 3.4 Power Supply Pins

MC68HC912D60A power and ground pins are described below and summarized in Table 3-1.

All power supply pins must be connected to appropriate supplies. On no account must any pins be left floating.

# 3.4.1 Internal Power ( $V_{DD}$ ) and Ground ( $V_{SS}$ )

Power is supplied to the MCU through  $V_{DD}$  and  $V_{SS}$ . Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

#### 3.4.2 External Power (V<sub>DDX</sub>) and Ground (V<sub>SSX</sub>)

External power and ground for I/O drivers. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

# 3.4.3 V<sub>DDA</sub>, V<sub>SSA</sub>

Provides operating voltage and ground for the analog-to-digital converter. This allows the supply voltage to the ATD to be bypassed independently. Connecting  $V_{DDA}$  to  $V_{DD}$  if the ATD modules are not used will not result in an increase of power consumption.

#### 3.4.4 Analog to Digital Reference Voltages (V<sub>RH</sub>, V<sub>RL</sub>)

$V_{RH0}$ ,  $V_{RL0}$ : reference voltage high and low for ATD converter 0.  $V_{RH1}$ ,  $V_{RL1}$ : reference voltage high and low for ATD converter 1.

If the ATD modules are not used, leaving  $V_{RH}$  connected to  $V_{DD}$  will not result in an increase of power consumption.

Technical Data

MC68HC912D60A — Rev. 3.1

# 3.4.5 V<sub>DDPLL</sub>, V<sub>SSPLL</sub>

Provides operating voltage and ground for the Phased-Locked Loop. This allows the supply voltage to the PLL to be bypassed independently.

**NOTE:** The VSSPLL pin should always be grounded even if the PLL is not used. The VDDPLL pin should not be left floating. It is recommended to connect the VDDPLL pin to ground if the PLL is not used.

#### 3.4.6 XFC

PLL loop filter. Please see Appendix: CGM Practical Aspects for information on how to calculate PLL loop filter elements. Any current leakage on this pin must be avoided.

Figure 3-5. PLL Loop Filter Connections

If VDDPLL is connected to VSS (this is normal case), then the XFC pin should either be left floating or connected to VSS (**never** to VDD). If VDDPLL is tied to VDD but the PLL is switched off (PLLON bit cleared), then the XFC pin should be connected preferably to VDDPLL (i.e. ready for VCO minimum frequency).

|                    | Pin Number    |                |                                                                                  |  |

|--------------------|---------------|----------------|----------------------------------------------------------------------------------|--|

| Mnemonic           | 80-pin<br>QFP | 112-pin<br>QFP | Description                                                                      |  |

| V <sub>DD</sub>    | 9, 49         | 12, 65         | Internal power and ground.                                                       |  |

| V <sub>SS</sub>    | 10, 50        | 14, 66         |                                                                                  |  |

| V <sub>DDX</sub>   | 30, 75        | 42, 107        | External power and ground, supply to pip drivere                                 |  |

| V <sub>SSX</sub>   | 29, 74        | 40, 106        | External power and ground, supply to pin drivers.                                |  |

| V <sub>DDA</sub>   | 61            | 85             | Operating voltage and ground for the analog-to-digital                           |  |

| V <sub>SSA</sub>   | 62            | 88             | converter, allows the supply voltage to the A/D to be<br>bypassed independently. |  |

| V <sub>RH1</sub>   | _             | 86             | Petersnes veltages for the appleg to digital convertor 1                         |  |

| V <sub>RL1</sub>   | _             | 87             | Reference voltages for the analog-to-digital converter 1                         |  |

| V <sub>RH0</sub>   | 51            | 67             | Deference veltages for the enclose to divital convertor 0                        |  |

| V <sub>RL0</sub>   | 52            | 68             | Reference voltages for the analog-to-digital converter 0.                        |  |

| V <sub>DDPLL</sub> | 31            | 43             | Provides operating voltage and ground for the Phased-Locked                      |  |

| V <sub>SSPLL</sub> | 33            | 45             | Loop. This allows the supply voltage to the PLL to be bypassed independently.    |  |

Table 3-1. MC68HC912D60A Power and Ground Connection Summary

# 3.5 Signal Descriptions

#### 3.5.1 Crystal Driver and External Clock Input (XTAL, EXTAL)

These pins provide the interface for either a crystal or a CMOS compatible clock to control the internal clock generator circuitry. Out of reset the frequency applied to EXTAL is twice the desired E–clock rate. All the device clocks are derived from the EXTAL input frequency.

#### 3.5.1.1 Crystal Connections

Refer to Section 12. Oscillator for details of crystal connections.

# **NOTE:** When selecting a crystal, it is recommended to use one with the lowest possible frequency in order to minimise EMC emissions.

#### 3.5.1.2 External Oscillator Connections

XTAL is the crystal output. The XTAL pin must be left unterminated when an external CMOS compatible clock input is connected to the EXTAL pin. The XTAL output is normally intended to drive only a crystal. The XTAL output can be buffered with a high-impedance buffer to drive the EXTAL input of another device.

Figure 3-6. External Oscillator Connections

#### 3.5.2 E-Clock Output (ECLK)

ECLK is the output connection for the internal bus clock and is used to demultiplex the address and data and is used as a timing reference. ECLK frequency is equal to 1/2 the crystal frequency out of reset. The ECLK output is turned off in single chip user mode to reduce the effects of RFI. It can be turned on if necessary. In single-chip special mode, the ECLK is turned ON at reset and can be turned OFF. In special peripheral mode the ECLK is an input to the MCU. All clocks, including the ECLK, are halted when the MCU is in STOP mode. It is possible to configure the MCU to interface to slow external memory. ECLK can be stretched for such accesses.

# 3.5.3 Reset (RESET)

An active low bidirectional control signal, RESET, acts as an input to initialize the MCU to a known start-up state. It also acts as an open-drain

| MC68HC912D60A — Rev. 3.1 | Technical Data |

|--------------------------|----------------|

|                          |                |

output to indicate that an internal failure has been detected in either the clock monitor or COP watchdog circuit. The MCU goes into reset asynchronously and comes out of reset synchronously. This allows the part to reach a proper reset state even if the clocks have failed, while allowing synchronized operation when starting out of reset.

It is important to use an external low-voltage reset circuit (such as MC34064 or MC34164) to prevent corruption of RAM or EEPROM due to power transitions.

The reset sequence is initiated by any of the following events:

- Power-on-reset (POR)

- COP watchdog enabled and watchdog timer times out

- Clock monitor enabled and Clock monitor detects slow or stopped clock

- User applies a low level to the reset pin

External circuitry connected to the reset pin should not include a large capacitance that would interfere with the ability of this signal to rise to a valid logic one within nine bus cycles after the low drive is released. Upon detection of any reset, an internal circuit drives the reset pin low and a clocked reset sequence controls when the MCU can begin normal processing. In the case of POR or a clock monitor error, a 4096 cycle oscillator startup delay is imposed before the reset recovery sequence starts (reset is driven low throughout this 4096 cycle delay). The internal reset recovery sequence then drives reset low for 16 to 17 cycles and releases the drive to allow reset to rise. Nine cycles later this circuit samples the reset pin to see if it has risen to a logic one level. If reset is low at this point, the reset is assumed to be coming from an external request and the internally latched states of the COP timeout and clock monitor failure are cleared so the normal reset vector (\$FFFE:FFFF) is taken when reset is finally released. If reset is high after this nine cycle delay, the reset source is tentatively assumed to be either a COP failure or a clock monitor fail. If the internally latched state of the clock monitor fail circuit is true, processing begins by fetching the clock monitor vector (\$FFFC:FFFD). If no clock monitor failure is indicated, and the latched state of the COP timeout is true, processing begins by fetching the COP

vector (\$FFFA:FFFB). If neither clock monitor fail nor COP timeout are pending, processing begins by fetching the normal reset vector (\$FFFE:FFFF).

#### 3.5.4 Maskable Interrupt Request (IRQ)

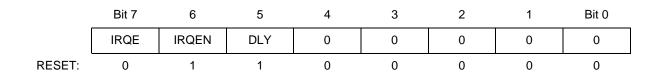

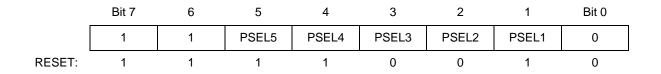

The IRQ input provides a means of applying asynchronous interrupt requests to the MCU. Either falling edge-sensitive triggering or level-sensitive triggering is program selectable (INTCR register). IRQ is always enabled and configured to level-sensitive triggering at reset. It can be disabled by clearing the IRQEN bit (INTCR register). When the MCU is reset the IRQ function is masked in the condition code register.

This pin is always an input and can always be read. There is an active pull-up on this pin while in reset and immediately out of reset. The pull-up can be turned off by clearing PUPE in the PUCR register.

#### 3.5.5 Nonmaskable Interrupt (XIRQ)

The  $\overline{XIRQ}$  input provides a means of requesting a nonmaskable interrupt after reset initialization. During reset, the X bit in the condition code register (CCR) is set and any interrupt is masked until MCU software enables it. Because the  $\overline{XIRQ}$  input is level sensitive, it can be connected to a multiple-source wired-OR network. This pin is always an input and can always be read. There is an active pull-up on this pin while in reset and immediately out of reset. The pull-up can be turned off by clearing PUPE in the PUCR register.  $\overline{XIRQ}$  is often used as a power loss detect interrupt.

Whenever XIRQ or IRQ are used with multiple interrupt sources (IRQ must be configured for level-sensitive operation if there is more than one source of IRQ interrupt), each source must drive the interrupt input with an open-drain type of driver to avoid contention between outputs. There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If the interrupt line is held low, the MCU will recognize another interrupt as soon as the interrupt mask bit in the MCU is cleared (normally upon return from an interrupt).

MC68HC912D60A — Rev. 3.1

Freescale Semiconductor

#### 3.5.6 Mode Select (SMODN, MODA, and MODB)

The state of these pins during reset determine the MCU operating mode. After reset, MODA and MODB can be configured as instruction queue tracking signals IPIPE0 and IPIPE1. MODA and MODB have active pulldowns during reset.

The SMODN pin has an active pull-up when configured as input. This pin can be used as BKGD or  $\overline{TAGHI}$  after reset.

#### 3.5.7 Single-Wire Background Mode Pin (BKGD)

The BKGD pin receives and transmits serial background debugging commands. A special self-timing protocol is used. The BKGD pin has an active pull-up when configured as input; BKGD has no pull-up control. Refer to Development Support.

#### 3.5.8 External Address and Data Buses (ADDR[15:0] and DATA[15:0])

External bus pins share function with general-purpose I/O ports A and B. In single-chip operating modes, the pins can be used for I/O; in expanded modes, the pins are used for the external buses.

In expanded wide mode, ports A and B are used for multiplexed 16-bit data and address buses. PA[7:0] correspond to ADDR[15:8]/DATA[15:8]; PB[7:0] correspond to ADDR[7:0]/DATA[7:0].

In expanded narrow mode, ports A and B are used for the16-bit address bus, and an 8-bit data bus is multiplexed with the most significant half of the address bus on port A. In this mode, 16-bit data is handled as two back-to-back bus cycles, one for the high byte followed by one for the low byte. PA[7:0] correspond to ADDR[15:8] and to DATA[15:8] or DATA[7:0], depending on the bus cycle. The state of the address pin should be latched at the rising edge of E. To allow for maximum address setup time at external devices, a transparent latch should be used.

#### 3.5.9 Read/Write $(R/\overline{W})$

In all modes this pin can be used as general-purpose I/O and is an input with an active pull-up out of reset. If the read/write function is required it should be enabled by setting the RDWE bit in the PEAR register. External writes will not be possible until enabled.

#### 3.5.10 Low-Byte Strobe (LSTRB)

In all modes this pin can be used as general-purpose I/O and is an input with an active pull-up out of reset. If the strobe function is required, it should be enabled by setting the LSTRE bit in the PEAR register. This signal is used in write operations and so external low byte writes will not be possible until this function is enabled. This pin is also used as TAGLO in Special Expanded modes and is multiplexed with the LSTRB function.

#### 3.5.11 Instruction Queue Tracking Signals (IPIPE1 and IPIPE0)

These signals are used to track the state of the internal instruction execution queue. Execution state is time-multiplexed on the two signals. Refer to Development Support.

# 3.5.12 Data Bus Enable (DBE)

The DBE pin (PE7) is an active low signal that will be asserted low during ECLK high time. DBE provides separation between output of a multiplexed address and the input of data. When an external address is stretched, DBE is asserted during what would be the last quarter cycle of the last ECLK cycle of stretch. In expanded modes this pin is used to enable the drive control of external buses during external reads. Use of the DBE is controlled by the NDBE bit in the PEAR register.DBE is enabled out of reset in expanded modes. This pin has an active pull-up during and after reset in single chip modes.

MC68HC912D60A — Rev. 3.1

#### 3.5.13 Inverted ECLK (ECLK)

The ECLK pin (PE7) can be used to latch the address for demultiplexing. It has the same behavior as the ECLK, except is inverted. In expanded modes this pin is used to enable the drive control of external buses during external reads. Use of the ECLK is controlled by the NDBE and DBENE bits in the PEAR register.

#### 3.5.14 Calibration reference (CAL)

The CAL pin (PE7) is the output of the Slow Mode programmable clock divider, SLWCLK, and is used as a calibration reference. The SLWCLK frequency is equal to the crystal frequency out of reset and always has a 50% duty. If the DBE function is enabled it will override the enabled CAL output. The CAL pin output is disabled by clearing CALE bit in the PEAR register.

#### 3.5.15 Clock generation module test (CGMTST)

The CGMTST pin (PE6) is the output of the clocks tested when CGMTE bit is set in PEAR register. The PIPOE bit must be cleared for the clocks to be tested.

#### 3.5.16 TEST

This pin is used for factory test purposes. It is recommended that this pin is not connected in the application, but it may be bonded to 5.5 V max without issue. Never apply voltage higher than 5.5 V to this pin.

| Pin Name    | Pin Number |         | Description                                                                                                                                                                 |  |  |  |  |

|-------------|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| FIII Naille | 80-pin     | 112-pin | Description                                                                                                                                                                 |  |  |  |  |

| EXTAL       | 35         | 47      | Crystal driver and external clock input pins.                                                                                                                               |  |  |  |  |

| XTAL        | 36         | 48      | Crystal driver and external clock input pins.                                                                                                                               |  |  |  |  |

| RESET       | 34         | 46      | An active low bidirectional control signal, RESET acts as an input to initialize the MCU to a known start-up state, and an output when COP or clock monitor causes a reset. |  |  |  |  |

#### Table 3-2. MC68HC912D60A Signal Description Summary

**Technical Data**

MC68HC912D60A — Rev. 3.1

| Pin NameInternational systemDescriptionADDR[7:0]23-1631-24External bus pins share function with general-purpose I/O ports A and B.<br>In single chip modes, the pins can be used for I/O. In expanded modes,<br>the pins are used for the external buses.ADDR[15:8]48-4164-57External buse during external reads.DBE2536Data bus control and, in expanded mode, enables the drive control of<br>external buses during external reads.ECLK2536Inverted ECLK used to latch the address.CAL2536Color generation reference for functions such as time of day. It<br>is overridden when DBE function is enabled. It always has a 50% duty<br>cycle.CGMTST2637Clock generation module test output.MODB/<br>IPIPE026, 2737, 38State of mode select pins during reset determine the initial operating mode<br>of the MCU. After reset, MODB and MODA can be configured as<br>instruction queue tracking signals IPIPE1 and IPIPE0 or as general-<br>purpose I/O pins.ECLK2839E Clock is the output connection for the external bus clock. ECLK is used<br>as a timing reference and for address demultiplexing.ITAGE/03753External signal inflictates the size 168 access.) Pin<br>function TAGEO used in instruction queues<br>asynchronous interrupt requests to the MCU. Either falling edge-<br>asynchronous interrupt requests input provides a means of applying<br>asynchronous interrupt requests the sepanded modes.MODB/<br>IPIPE01523Single-wire background interface pin is dedicated to the background<br>debug function. During reset, this pin determines special or normal<br>operating mode. <th></th> <th>Din</th> <th>lumber</th> <th></th>                                                                                                                     |                  | Din        | lumber   |                                                                                                                                                                              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADDR[7:0]<br>DATA[7:0]23-1631-24External bus pins share function with general-purpose I/O ports A and B.<br>In single chip modes, the pins can be used for I/O. In expanded modes,<br>the pins are used for the external buses.ADDR[15:8]<br>DATA[15:8]48-4164-57External bus control and, in expanded mode, enables the drive control of<br>external buses during external reads.DBE2536Inverted ECLK used to latch the address.CAL2536Inverted ECLK used to latch the address.CAL2536CAL is the output of the Slow Mode programmable clock divider, SLWCLK,<br>is overridden when DBE function is enabled. It always has a 50% duty<br>cycle.CGMTST2637Clock generation module test output.MODB/<br>IPIPE026, 2737, 38State of mode select pins during reset determine the initial operating mode<br>of the MCU. After reset, MODB and MODA can be configured as<br>instruction queue tracking signals IPIPE1 and IPIPE0 or as general-<br>purpose I/O pins.IECLK2839E Clock is the output connection for the external bus clock. ECLK is used<br>as a timing reference and for address demultiplexing.LSTRE/<br>TAGLO3753Indicates direction of data on expansion bus. Shares function with general-<br>purpose I/O. Read/write in expanded modes.R/W3854Indicates direction of data on expansion bus. Shares function with general-<br>purpose I/O. Read/write in expanded modes.IRQ4056Provides a means of requesting asynchronous nonmaskable interrupt<br>requests after reset initializationXIRQ4056Provides a means of requesting asynchron                                                                                                                                                                                                                       | Pin Name         | Pin Number |          | Description                                                                                                                                                                  |  |  |  |  |

| DATA[7:0]25-1631-24External bus pins share function with general-purpose I/O ports A and B.<br>In single chip modes, the pins can be used for I/O. In expanded modes,<br>the pins are used for the external buses.DBE2536Data bus control and, in expanded mode, enables the drive control of<br>external buses during external reads.DE2536Inverted ECLK used to latch the address.CAL2536Inverted ECLK used to latch the address.CAL2536CAL is the output of the Slow Mode programmable clock divider, SLWCLK,<br>and is used as a calibration reference for functions such as time of day. It<br>is overridden when DBE function is enabled. It always has a 50% duty<br>cycle.CGMTST2637Clock generation module test output.MODB/<br>IPIPE1,<br>IPIPE026, 2737, 38State of mode select pins during reset determine the initial operating mode<br>of the MCU. After reset, MODB and MODA can be configured as<br>instruction queue tracking signals IPIPE1 and IPIPE0 or as general-<br>purpose I/O pins.ECLK2839E Clock is the output connection for the external bus clock. ECLK is used<br>as a timing reference and for address demultiplexing.ICSTRB/<br>TAGLO3753Low byte strobe (0 - low byte valid), in all modes this pin can be used as<br>28 signal. (The SZ8 internal signal indicates the size 16/8 access.) Pin<br>function TAGLO used in instruction tagging. See Development Support.R/W3854Indicates direction of data on expansion bus. Shares function with general-<br>purpose I/O. Read/write in expanded modes.IRQ4056Provides a means of requesting asynchronous nonmas                                                                                                                                                                          |                  | 80-pin     | 112-pin  |                                                                                                                                                                              |  |  |  |  |

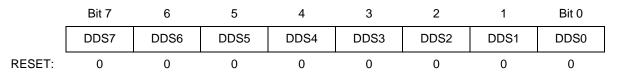

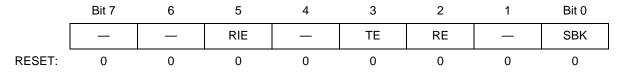

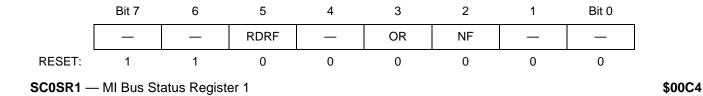

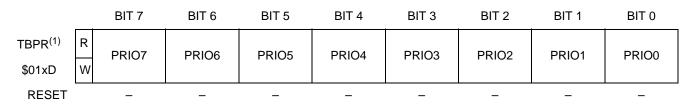

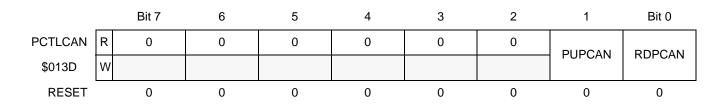

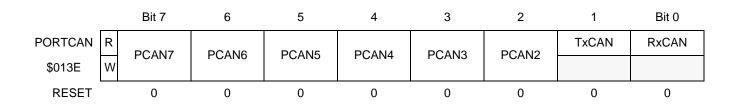

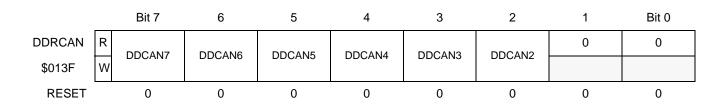

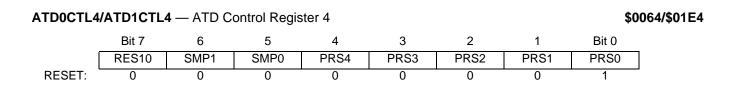

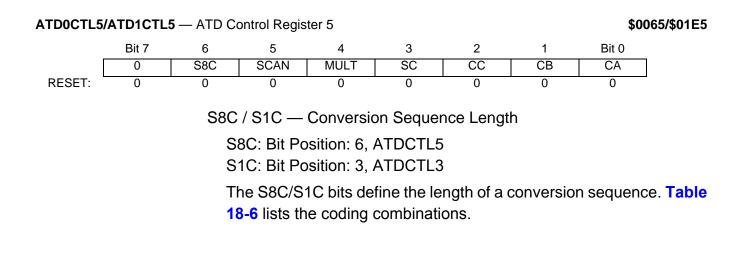

| ADDR[15:8]<br>DATA[15:8]48-4164-57the pins are used for the external buses.DBE2536Data bus control and, in expanded mode, enables the drive control of<br>external buses during external reads.ECLK2536Inverted ECLK used to latch the address.CAL2536Inverted ECLK used to latch the address.CAL2536CAL is the output of the Slow Mode programmable clock divider, SLWCLK,<br>is overridden when DBE function reference for functions such as time of day, it<br>is overridden when DBE function is enabled. It always has a 50% duty<br>cycle.CGMTST2637Clock generation module test output.MODB/<br>IPIPE1,<br>IPIPE026, 2737, 38State of mode select pins during reset determine the initial operating mode<br>of the MCU. After reset, MODB and MODA can be configured as<br>instruction queue tracking signals IPIPE1 and IPIPE0 or as general-<br>purpose I/O pins.ECLK2839E Clock is the output connection for the external bus clock. ECLK is used<br>as a timing reference and for address demultiplexing.LSTRE/<br>TAGLO3753Low byte strobe (0 = low byte valid), in all modes this pin can be used as<br>VO. The low strobe function is the exclusive-NOR of A0 and the internal<br>SZ8 signal. (The SZ8 internal signal indicates the size 16/8 access.) Pin<br>function TAGLO used in instruction tagging. See Development Support.R/W3854Indicates direction of data on expansion bus. Shares function with general-<br>purpose I/O. Read/write in expanded modes.IRQ4056Provides a means of requesting asynchronous nonmaskable interrupt<br>requests after reset initialization                                                                                                                                                                           |                  | 23–16      | 31–24    |                                                                                                                                                                              |  |  |  |  |