# **Cypress Semiconductor**

# CY8C9520, CY8C9540, and CY8C9560

**Preliminary Data Sheet**

# 20-, 40-, and 60-Bit I/O Expander with EEPROM

# Features

- I2C<sup>™</sup> interface logic electrically compatible with SMBus.

- Up to 20 (CY8C9520), 40 (CY8C9540) or 60 (CY8C9560)

I/O data pins independently configurable as inputs, outputs, bi-directional input/outputs or PWM outputs.

- 4/8/16 PWM sources with 8-bit resolution.

- Extendable Soft Addressing<sup>™</sup> algorithm allowing flexible I2C-address configuration.

- Internal 3-/11-/27-Kbyte EEPROM.

- Storage of user defaults and I/O port settings in the internal EEPROM.

- Optional EEPROM Write Disable (WD) input.

- Interrupt output indicates input pin level changes and pulse width modulator (PWM) state changes.

- Internal power-on reset (POR).

August 17, 2005

# Overview

The CY8C95xx is a multi-port I/O expander with on-board useravailable EEPROM and several PWM outputs. All devices in this family operate identically but differ in I/O pins, number of PWMs, and internal EEPROM size.

The CY8C95xx operates as two I2C slave devices. The first device is a multi-port I/O expander (single I2C address to access all ports via registers). The second device is a serial EEPROM. Dedicated configuration registers can be used to disable the EEPROM. The EEPROM utilizes 2-byte addressing to support the 28-Kbyte EEPROM address space. The selected device is defined by the most significant bits of the I2C address or by specific register addressing.

The I/O expander's data pins can be independently assigned as inputs, outputs, quasi-bidirectional input/outputs or PWM ouputs. The individual data pins can be configured as open drain/collector, strong drive (10 mA source, 25 mA sink), resistively pulled-up/-down, or high-impedance. The factory default configuration is pulled-up internally.

The system master writes to the I/O configuration registers via the I2C bus. Configuration and output register settings can be stored as user defaults in a dedicated section of the EEPROM. If user defaults have been stored in EEPROM, they are restored to the ports at power-up. While this device can share the bus with SMBus devices, it can only communicate with I2C-masters.

There is one dedicated pin that is configured as an interrupt output (INT) and can be connected to the interrupt logic of the system master. This signal can inform the system master that there is incoming data on its ports or that the PWM output state was changed.

The EEPROM is byte-readable and supports byte-by-byte writing. A pin can be configured as an EEPROM Write Disable (WD) input that blocks write operations when set high. The configuration registers can also disable EEPROM operations.

The CY8C95xx has one fixed address pin (A0) and up to six additional pins (A1-A6) which allow up to 128 devices to share a common two-wire I2C data bus. The Extendable Soft Addressing algorithm provides the option to choose the number of pins needed to assign the desired address. Pins not used for address bits are available as GPIO pins. There are 4 (CY8C9520), 8 (CY8C9540) or 16 (CY8C9560) independently configurable 8-bit PWMs. These PWMs are denoted as PWM0-PWM15. Each PWM can be clocked by one of six available clock sources.

# Architecture

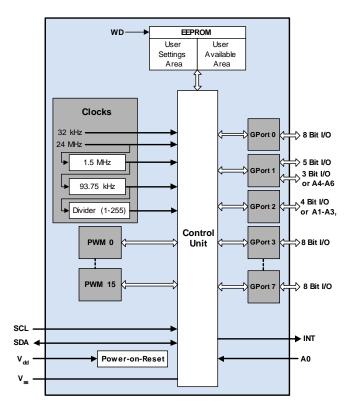

The figure titled "Top Level Block Diagram" on page 1 illustrates the device block diagram. The main blocks include the control unit, PWMs, EEPROM and I/O ports. The control unit executes commands received from the I2C bus and transfers data between other bus devices and the master device.

The on-chip EEPROM can be separated conventionally into two regions. The first region is designed to store data and is available for byte-wide read/writes via the I2C bus. It is possible to prevent write operations by setting the WD pin to high. All EEPROM operations can be blocked by configuration register settings. The second region allows the user to store the port and PWM default settings using special commands. These defaults will be automatically reloaded and processed after device power-on.

The number of I/O lines and PWM sources is presented in the following table.

| Port    | CY8C9520 | CY8C9540 | CY8C9560 |

|---------|----------|----------|----------|

| GPort 0 | 8 bit    | 8 bit    | 8 bit    |

| GPort 1 | 5-8 bit* | 5-8* bit | 5-8 bit* |

| GPort 2 | 0-4 bit* | 0-4* bit | 0-4 bit* |

| GPort 3 | -        | 8 bit    | 8 bit    |

| GPort 4 | -        | 8 bit    | 8 bit    |

| GPort 5 | -        | 4 bit    | 8 bit    |

| GPort 6 | -        | -        | 8 bit    |

| GPort 7 | -        | -        | 8 bit    |

| PWMs    | 4        | 8        | 16       |

Table 1-1. GPIO Availability

\* This port contains configuration-dependant GPIO lines or A1-A6 and WD lines.

There are four pins on GPort 2 and three on GPort 1 that can be used as general purpose I/O or EEPROM Write Disable (WD) and I2C-address input (A1-A6), depending on configuration settings.

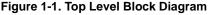

The figure titled "Logical Structure of the I/O Port" shows the single port logical structure. The Port Drive Mode register gives the option to select one of seven available modes for each pin separately: pulled-up/-down, open drain high/low, strong drive fast/slow, or high-impedance. By default these configuration registers store values setting I/O pins to pulled-up. The Invert register allows for inversion of the logic of the Input registers separately for each pin. The Select PWM register allows pins to be assigned as PWM outputs. All of these configuration registers are read/writable using corresponding commands in the multi-port device.

#### Figure 1-2. Logical Structure of the I/O Port

The Port Input and Output registers are separated. When the Output register is written, the data is sent to the external pins. When the Input register is read, the external pin logic levels are captured and transferred. As a result, the read data can be different from written Output register data. This allows for implementation of a quasi-bidirectional input-output mode, when the corresponding binary digit is configured as pulled-up/down output.

Each GPort has an Interrupt Mask register and an Interrupt Status register. Each high bit in the Interrupt Status register signals that there has been a change in the corresponding input line since the last read of that Interrupt Status register. The Interrupt Status register is cleared after each read. The Interrupt Mask register enables/disables activation of the INT line when input levels are changed. Each high in the Interrupt Mask register masks (disables) an interrupt generated from the corresponding input line.

# Applications

Each GPIO pin can be used to monitor and control various board-level devices, including LEDs and system intrusion detection devices.

The on-board EEPROM can be used to store information such as error codes or board manufacturing data for read-back by application software for diagnostic purposes.

# **Device Access Addressing**

Following a start condition, the I2C master device sends a byte to address an I2C slave. This address selects the device to be accessed in the CY8C95xx. By default there are two possible address formats in binary representation: 01000A0X and 10100A0X. The first is used to access the multi-port device and the second to access the EEPROM. If additional address lines (A1-A6) are used then the Device Addressing Table 1-2 defines the device addresses. This addressing method uses a technique called Extendable Soft Addressing<sup>™</sup>, described later in this document.

#### Table 1-2. Device Addressing

|       |       | Mu    | lti-Po | ort D | evice          | e              |     |       |       | EE    | PRO   | M De  | vice           |                |     |

|-------|-------|-------|--------|-------|----------------|----------------|-----|-------|-------|-------|-------|-------|----------------|----------------|-----|

| 01    |       | 0     | 0      | 0     | 0              | A <sub>0</sub> | R/W | 1     | 0     | 1     | 0     | 0     | 0              | $A_0$          | R/W |

| 0     | 1     | 0     | 0      | 0     | A <sub>1</sub> | A <sub>0</sub> | R/W | 1     | 0     | 1     | 0     | 0     | A <sub>1</sub> | $A_0$          | R/W |

| 0     | 1     | 0     | 0      | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W | 1     | 0     | 1     | 0     | $A_2$ | A <sub>1</sub> | $A_0$          | R/W |

| 0     | 1     | 0     | $A_3$  | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W | 1     | 0     | 1     | $A_3$ | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W |

| 0     | 1     | $A_4$ | $A_3$  | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W | 1     | 0     | $A_4$ | $A_3$ | $A_2$ | A <sub>1</sub> | $A_0$          | R/W |

| 0     | $A_5$ | $A_4$ | $A_3$  | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W | 1     | $A_5$ | $A_4$ | $A_3$ | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W |

| $A_6$ | $A_5$ | $A_4$ | $A_3$  | $A_2$ | A <sub>1</sub> | A <sub>0</sub> | R/W | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | A <sub>1</sub> | $A_0$          | R/W |

When all address lines A1-A6 are used, the device being accessed is defined by the first byte following the address in the write transaction. If the most significant bit (MSb) of this byte is '0', this byte is treated as a command (register address) byte of the multi-port device. If the MSb is '1', this byte is the first of a 2-byte EEPROM address. In this case, the device will mask the MSb to determine the EEPROM address.

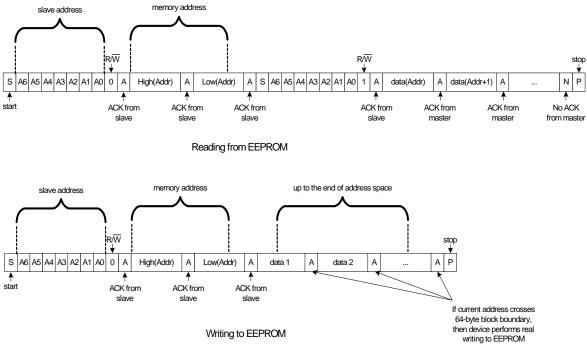

### Serial EEPROM Device

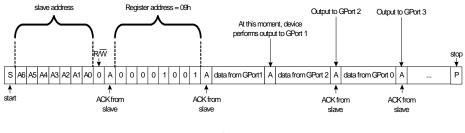

EEPROM reading and writing operations require 2 bytes, AHI and ALO, which indicate which memory address to use.

To read one or more bytes, the master device addresses the unit with a write cycle (= 0) to send AHI followed by ALO, readdresses the unit with a read cycle (= 1), and reads one or more data bytes. Each data byte read will increment the internal address counter by one up to the end of the EEPROM address space. A read or write beyond the end of the EEPROM address space should result in a NAK response by the Port Expander.

To write data to the EEPROM, the master device performs one write cycle, with the first two bytes being AHI followed by ALO. This is followed by one or more data bytes. In the case of block writing it is advisable to set the starting address on the beginning of the 64-byte boundary, for example 01C0h or 0080h, but this is not mandatory. When a 64-byte boundary is crossed in the EEPROM, the I2C clock is stretched while the device performs an EEPROM write sequence. If the end of available EEPROM space is reached, then further writes will be responded to with a NAK.

Refer to Figure 2-2, "Memory Reading and Writing," on page 10, which illustrates memory reading and writing procedures for the EEPROM device.

### Multi-Port I/O Device

This device allows the user to set various configurations and I/O operations through internal registers.

Each data transfer is preceded by the command byte. This byte is used as a pointer to a register that will receive or transmit data. Available registers are listed in Table 3-1, "The Device Register Address Map," on page 11.

# **Document Conventions**

#### Acronyms

The following table lists the acronyms that are used in this document.

| Acronym | Description                                                           |

|---------|-----------------------------------------------------------------------|

| AC      | alternating current                                                   |

| DC      | direct current                                                        |

| EEPROM  | electrically erasable programmable read-only memory (E <sup>2</sup> ) |

| GPIO    | general purpose IO                                                    |

| I/O     | input/output                                                          |

| MSb     | most-significant bit                                                  |

| POR     | power on reset                                                        |

| PWM     | pulse width modulator                                                 |

### Units of Measure

A units of measure table is located in the Electrical Specifications section. Table 4-1, "Units of Measure," on page 16 lists all the abbreviations used in Section 4.

# Numeric Naming

Hexidecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexidecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (e.g., 01010100b' or '01000011b'). Numbers not indicated by an 'h', 'b', or 0x are decimal.

# **Table of Contents**

The following is a table of contents for the remainder of this data sheet.

| 2. | <b>Pino</b><br>2.1 |                | Pin Descriptions                                                                |    |

|----|--------------------|----------------|---------------------------------------------------------------------------------|----|

|    |                    | 2.1.1          | 28-Pin Part Pinout                                                              |    |

|    |                    | 2.1.2          | 48-Pin Part Pinout                                                              |    |

|    |                    | 2.1.3          | 100-Pin Part Pinout                                                             | 7  |

|    | 2.2                | PIN De         | scriptions                                                                      |    |

|    |                    | 2.2.1          | Extendable Soft Addressing <sup>™</sup>                                         | 9  |

|    |                    | 2.2.2          | Interrupt Pin (INT)                                                             | 9  |

|    |                    | 2.2.3          | Write Disable Pin (WD)                                                          |    |

|    |                    | 2.2.4          | External Reset Pin (XRES)                                                       | 9  |

|    |                    | 2.2.5          | Working with PWMs                                                               |    |

| 3. |                    |                | erence                                                                          |    |

|    | 3.1                |                | er Mapping Table                                                                |    |

|    | 3.2                | Registe        | er Descriptions                                                                 |    |

|    |                    | 3.2.1          | Input Port Registers (00h - 07h)                                                |    |

|    |                    | 3.2.2          | Output Port Registers (08h - 0Fh)                                               | 12 |

|    |                    | 3.2.3          | Int. Status Port Registers (10h - 17h)                                          | 12 |

|    |                    | 3.2.4          | Port Select Register (18h)                                                      | 12 |

|    |                    | 3.2.5<br>3.2.6 | Interrupt Mask Port Register (19h)<br>Select PWM Register (1Ah)                 | 12 |

|    |                    | 3.2.0          | Inversion Register (1Bh)                                                        |    |

|    |                    | 3.2.8          | Port Direction Register (1Ch)                                                   |    |

|    |                    | 3.2.9          | Drive Mode Registers (1Dh-23h)                                                  | 13 |

|    |                    | 3.2.10         | PWM Select Register (28h)                                                       |    |

|    |                    | 3.2.11         | Config (29h)                                                                    | 13 |

|    |                    | 3.2.12         | Period Register (2Ah)                                                           | 13 |

|    |                    | 3.2.13         | Pulse Width Register (2Bh)                                                      |    |

|    |                    | 3.2.14         | Divider Register (2Ch)                                                          |    |

|    |                    | 3.2.15         | Enable Register (2Dh)                                                           | 13 |

|    |                    | 3.2.16         | Device ID/Status Register (2Eh)                                                 | 14 |

|    | 2.2                | 3.2.17         | Command Register (30h)                                                          |    |

|    | 3.3                |                | ands Description                                                                |    |

|    |                    | 3.3.1<br>3.3.2 | Store Config to E2 POR Defaults Cmd (01h)<br>Restore Factory Defaults Cmd (02h) |    |

|    |                    | 3.3.2          | Write E2 POR Defaults Cmd (03h)                                                 |    |

|    |                    | 3.3.4          | Read E2 POR Defaults Cmd (04h)                                                  | 15 |

|    |                    | 3.3.5          | Write Device Config Cmd (05h)                                                   |    |

|    |                    | 3.3.6          | Read Device Config Cmd (06h)                                                    | 15 |

|    |                    | 3.3.7          | Reconfigure Device Cmd (07h)                                                    | 15 |

| 4. | Elec               | trical Sp      | ecifications                                                                    |    |

|    | 4.1                |                | e Maximum Ratings                                                               |    |

|    | 4.2                |                | ng Temperature                                                                  |    |

|    | 4.3                |                | ctrical Characteristics                                                         |    |

|    |                    | 4.3.1          | DC Chip-Level Specifications                                                    |    |

|    |                    | 4.3.2          | DC Programming Specifications                                                   |    |

|    |                    | 4.3.3          | DC General Purpose I/O Specifications                                           | 18 |

|    | 4.4                | AC Ele         | ctrical Characteristics                                                         | 19 |

|    |                    | 4.4.1          | AC General Purpose I/O Specifications                                           | 19 |

|    |                    | 4.4.2          | AC PWM Output Jitter Specifications                                             |    |

|    |                    | 4.4.3          | AC I2C Specifications                                                           | 20 |

| 5. | Pack               |                | formation                                                                       |    |

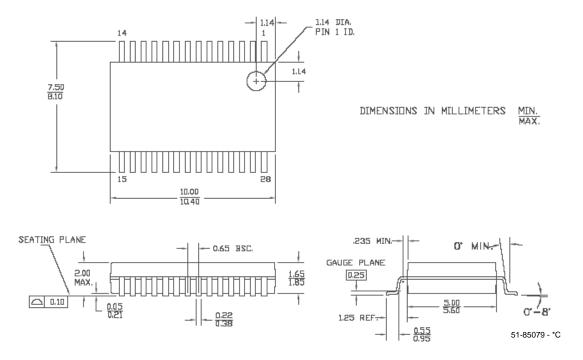

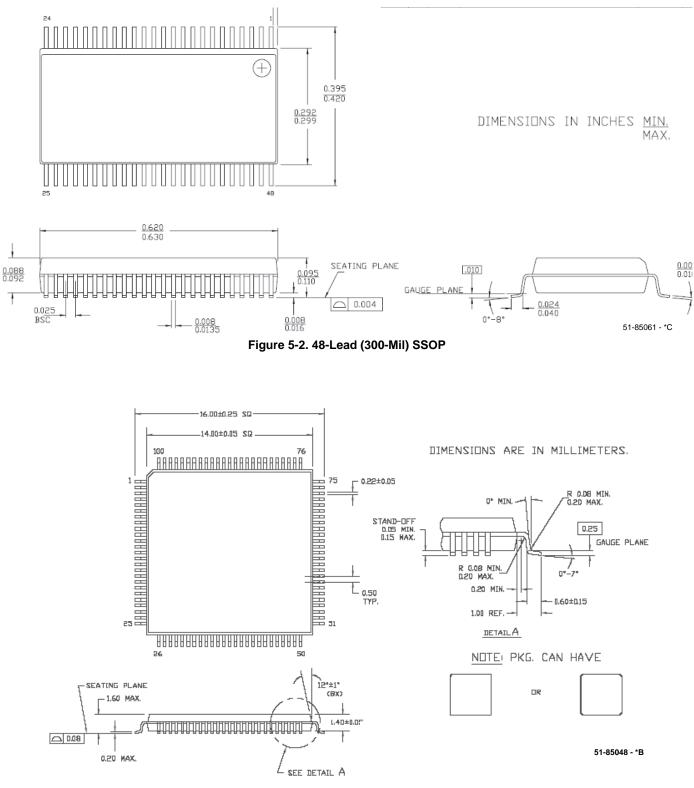

|    | 5.1                | Packag         | ing Dimensions                                                                  | 21 |

|    | 5.2                | Therma         | al Impedances                                                                   | 23 |

|    | 5.3                |                | Reflow Peak Temperature                                                         |    |

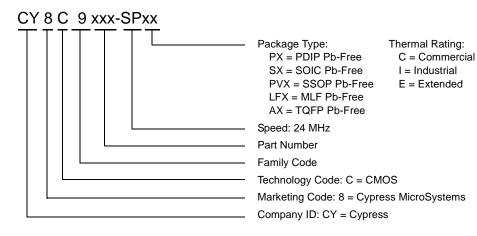

| 6. | Orde               |                | ormation                                                                        |    |

|    | 6.1                |                | q Code Definitions                                                              |    |

| 7. | -                  |                | ervice Information                                                              |    |

|    | 7.1                |                | n History                                                                       |    |

|    | 7.1                |                | phts and Code Protection                                                        |    |

|    | 1.4                | CODVIL         |                                                                                 | ∠J |

This chapter describes, lists, and illustrates the CY8C95xx device pins and pinout configurations, along with application examples.

# 2.1 Pinouts

The CY8C95xx device is available in a variety of packages, which are listed and illustrated in the following tables.

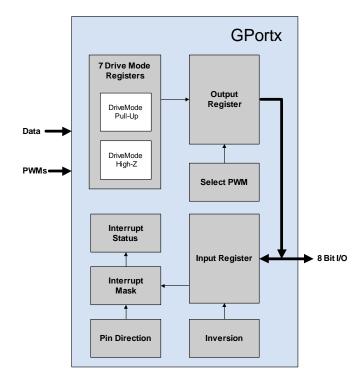

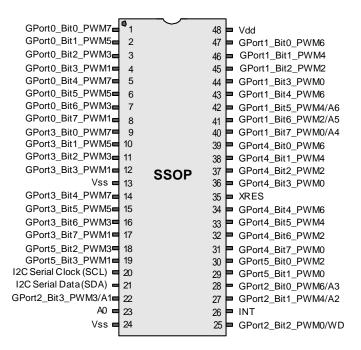

#### 2.1.1 28-Pin Part Pinout

#### Table 2-1. 28-Pin Part Pinout (SSOP)

| Pin<br>No. | Pin Name                            | Description                                            |

|------------|-------------------------------------|--------------------------------------------------------|

| 1          | GPort0_Bit0_PWM3                    | Port 0, Bit 0, PWM 3.                                  |

| 2          | GPort0_Bit1_PWM1                    | Port 0, Bit 1, PWM 1.                                  |

| 3          | GPort0_Bit2_PWM3                    | Port 0, Bit 2, PWM 3.                                  |

| 4          | GPort0_Bit3_PWM1                    | Port 0, Bit 3, PWM 1.                                  |

| 5          | GPort0_Bit4_PWM3                    | Port 0, Bit 4, PWM 3.                                  |

| 6          | GPort0_Bit5_PWM1                    | Port 0, Bit 5, PWM 1.                                  |

| 7          | GPort0_Bit6_PWM3                    | Port 0, Bit 6, PWM 3.                                  |

| 8          | GPort0_Bit7_PWM1                    | Port 0, Bit 7, PWM 1.                                  |

| 9          | V <sub>SS</sub>                     | Ground connection.                                     |

| 10         | I <sup>2</sup> C Serial Clock (SCL) | I <sup>2</sup> C Clock.                                |

| 11         | I <sup>2</sup> C Serial Data (SDA)  | I <sup>2</sup> C Data.                                 |

| 12         | GPort2_Bit3_PWM3/A1                 | Port 2, Bit 3, PWM 3, Address 1.                       |

| 13         | A0                                  | Address 0.                                             |

| 14         | V <sub>SS</sub>                     | Ground connection.                                     |

| 15         | GPort2_Bit2_PWM0/WD                 | Port 2, Bit 2, PWM 0, E <sup>2</sup> Write Disable.    |

| 16         | INT                                 |                                                        |

| 17         | GPort2_Bit1_PWM0/A2                 | Port 2, Bit 1, PWM 0, Address 2.                       |

| 18         | GPort2_Bit0_PWM2/A3                 | Port 2, Bit 0, PWM 2, Address 3.                       |

| 19         | XRES                                | Active high external reset with internal pull<br>down. |

| 20         | GPort1_Bit7_PWM0/A4                 | Port 1, Bit 7, PWM 0, Address 4.                       |

| 21         | GPort1_Bit6_PWM2/A5                 | Port 1, Bit 6, PWM 2, Address 5.                       |

| 22         | GPort1_Bit5_PWM0/A6                 | Port 1, Bit 5, PWM 0, Address 6.                       |

| 23         | GPort1_Bit4_PWM2                    | Port 1, Bit 4, PWM 2.                                  |

| 24         | GPort1_Bit3_PWM0                    | Port 1, Bit 3, PWM 0.                                  |

| 25         | GPort1_Bit2_PWM2                    | Port 1, Bit 2, PWM 2.                                  |

| 26         | GPort1_Bit1_PWM0                    | Port 1, Bit 1, PWM 0.                                  |

| 27         | GPort1_Bit0_PWM2                    | Port 1, Bit 0, PWM 2.                                  |

| 28         | V <sub>dd</sub>                     | Supply voltage.                                        |

#### CY8C9520 28-Pin Device

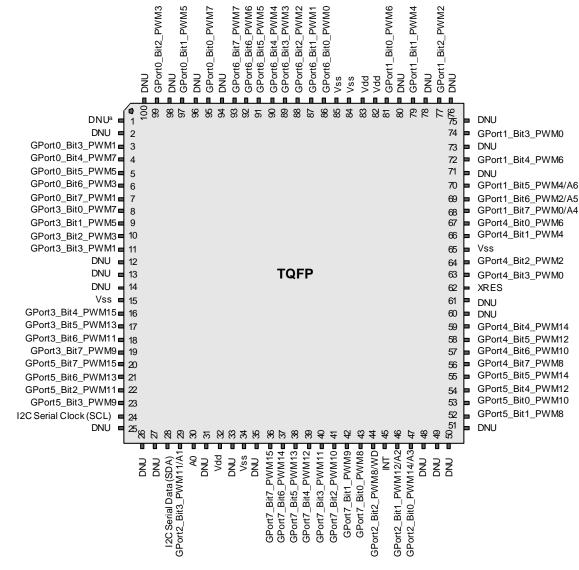

#### 2.1.2 48-Pin Part Pinout

#### Table 2-2. 48-Pin Part Pinout (SSOP)

| Pin<br>No. | Pin Name                            | Description                                         |

|------------|-------------------------------------|-----------------------------------------------------|

| 1          | GPort0_Bit0_PWM7                    | Port 0, Bit 0, PWM 7.                               |

| 2          | GPort0_Bit1_PWM5                    | Port 0, Bit 1, PWM 5.                               |

| 3          | GPort0_Bit2_PWM3                    | Port 0, Bit 2, PWM 3.                               |

| 4          | GPort0_Bit3_PWM1                    | Port 0, Bit 3, PWM 1.                               |

| 5          | GPort0_Bit4_PWM7                    | Port 0, Bit 4, PWM 7.                               |

| 6          | GPort0_Bit5_PWM5                    | Port 0, Bit 5, PWM 5.                               |

| 7          | GPort0_Bit6_PWM3                    | Port 0, Bit 6, PWM 3.                               |

| 8          | GPort0_Bit7_PWM1                    | Port 0, Bit 7, PWM 1.                               |

| 9          | GPort3_Bit0_PWM7                    | Port 3, Bit 0, PWM 7.                               |

| 10         | GPort3_Bit1_PWM5                    | Port 3, Bit 1, PWM 5.                               |

| 11         | GPort3_Bit2_PWM3                    | Port 3, Bit 2, PWM 3.                               |

| 12         | GPort3_Bit3_PWM1                    | Port 3, Bit 3, PWM 1.                               |

| 13         | V <sub>SS</sub>                     | Ground connection.                                  |

| 14         | GPort3_Bit4_PWM7                    | Port 3, Bit 4, PWM 7.                               |

| 15         | GPort3_Bit5_PWM5                    | Port 3, Bit 5, PWM 5.                               |

| 16         | GPort3_Bit6_PWM3                    | Port 3, Bit 6, PWM 3.                               |

| 17         | GPort3_Bit7_PWM1                    | Port 3, Bit 7, PWM 1.                               |

| 18         | GPort5_Bit2_PWM3                    | Port 5, Bit 2, PWM 3.                               |

| 19         | GPort5_Bit3_PWM1                    | Port 5, Bit 3, PWM 1.                               |

| 20         | I <sup>2</sup> C Serial Clock (SCL) | I <sup>2</sup> C Clock.                             |

| 21         | I <sup>2</sup> C Serial Data (SDA)  | I <sup>2</sup> C Data.                              |

| 22         | GPort2_Bit3_PWM3/A1                 | Port 2, Bit 3, PWM 3, Address 1.                    |

| 23         | A0                                  | Address 0.                                          |

| 24         | V <sub>SS</sub>                     | Ground connection.                                  |

| 25         | GPort2_Bit2_PWM0/WD                 | Port 2, Bit 2, PWM 0, E <sup>2</sup> Write Disable. |

| 26         | INT                                 |                                                     |

| 27         | GPort2_Bit1_PWM4/A2                 | Port 2, Bit 1, PWM 4, Address 2.                    |

| 28         | GPort2_Bit0_PWM6/A3                 | Port 2, Bit 0, PWM 6, Address 3.                    |

| 29         | GPort5_Bit1_PWM0                    | Port 5, Bit 1, PWM 0.                               |

| 30         | GPort5_Bit0_PWM2                    | Port 5, Bit 0, PWM 2.                               |

| 31         | GPort4_Bit7_PWM0                    | Port 4, Bit 7, PWM 0.                               |

| 32         | GPort4_Bit6_PWM2                    | Port 4, Bit 6, PWM 2.                               |

| 33         | GPort4_Bit5_PWM4                    | Port 4, Bit 5, PWM 4.                               |

| 34         | GPort4_Bit4_PWM6                    | Port 4, Bit 4, PWM 6.                               |

| 35         | XRES                                | Active high external reset with internal pull down. |

| 36         | GPort4_Bit3_PWM0                    | Port 4, Bit 3, PWM 0.                               |

| 37         | GPort4_Bit2_PWM2                    | Port 4, Bit 2, PWM 2.                               |

| 38         | GPort4_Bit1_PWM4                    | Port 4, Bit 1, PWM 4.                               |

| 39         | GPort4_Bit0_PWM6                    | Port 4, Bit 0, PWM 6.                               |

| 40         | GPort1_Bit7_PWM0/A4                 | Port 1, Bit 7, PWM 0, Address 4.                    |

| 41         | GPort1_Bit6_PWM2/A5                 | Port 1, Bit 6, PWM 2, Address 5.                    |

| 42         | GPort1_Bit5_PWM4/A6                 | Port 1, Bit 5, PWM 4, Address 6.                    |

| 43         | GPort1_Bit4_PWM6                    | Port 1, Bit 4, PWM 6.                               |

| 44         | GPort1_Bit3_PWM0                    | Port 1, Bit 3, PWM 0.                               |

| 45         | GPort1_Bit2_PWM2                    | Port 1, Bit 2, PWM 2.                               |

| 46         | GPort1_Bit1_PWM4                    | Port 1, Bit 1, PWM 4.                               |

| 47         | GPort1_Bit0_PWM6                    | Port 1, Bit 0, PWM 6.                               |

| 48         | V <sub>dd</sub>                     | Supply voltage.                                     |

#### CY8C9540 48-Pin Device

# 2.1.3 100-Pin Part Pinout

#### Table 2-3. 100-Pin Part Pinout (TQFP)

| Pin<br>No. | Name                                | Description                                         | Pin<br>No. | Name                | Description                                         |

|------------|-------------------------------------|-----------------------------------------------------|------------|---------------------|-----------------------------------------------------|

| 1          | DNU                                 | DNU = Do Not Use; leave floating.                   | 51         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 2          | DNU                                 | DNU = Do Not Use; leave floating.                   | 52         | GPort5_Bit1_PWM8    | Port 5, Bit 1, PWM 8.                               |

| 3          | GPort0_Bit3_PWM1                    | Port 0, Bit 3, PWM 1.                               | 53         | GPort5_Bit0_PWM10   | Port 5, Bit 0, PWM 10.                              |

| 4          | GPort0_Bit4_PWM7                    | Port 0, Bit 4, PWM 7.                               | 54         | GPort5_Bit4_PWM12   | Port 5, Bit 4, PWM 12.                              |

| 5          | GPort0_Bit5_PWM5                    | Port 0, Bit 5, PWM 5.                               | 55         | GPort5_Bit5_PWM14   | Port 5, Bit 5, PWM 14.                              |

| 6          | GPort0_Bit6_PWM3                    | Port 0, Bit 6, PWM 3.                               | 56         | GPort4_Bit7_PWM8    | Port 4, Bit 7, PWM 8.                               |

| 7          | GPort0_Bit7_PWM1                    | Port 0, Bit 7, PWM 1.                               | 57         | GPort4_Bit6_PWM10   | Port 4, Bit 6, PWM 10.                              |

| 8          | GPort3_Bit0_PWM7                    | Port 3, Bit 0, PWM 7.                               | 58         | GPort4_Bit5_PWM12   | Port 4, Bit 5, PWM 12.                              |

| 9          | GPort3_Bit1_PWM5                    | Port 3, Bit 1, PWM 5.                               | 59         | GPort4_Bit4_PWM14   | Port 4, Bit 4, PWM 14.                              |

| 10         | GPort3_Bit2_PWM3                    | Port 3, Bit 2, PWM 3.                               | 60         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 11         | GPort3_Bit3_PWM1                    | Port 3, Bit 3, PWM 1.                               | 61         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 12         | DNU                                 | DNU = Do Not Use; leave floating.                   | 62         | XRES                | Active high external reset with internal pull down. |

| 13         | DNU                                 | DNU = Do Not Use; leave floating.                   | 63         | GPort4_Bit3_PWM0    | Port 4, Bit 3, PWM 0.                               |

| 14         | DNU                                 | DNU = Do Not Use; leave floating.                   | 64         | GPort4_Bit2_PWM2    | Port 4, Bit 2, PWM 2.                               |

| 15         | V <sub>SS</sub>                     | Ground connection.                                  | 65         | V <sub>SS</sub>     | Ground connection.                                  |

| 16         | GPort3_Bit4_PWM15                   | Port 3, Bit 4, PWM 157.                             | 66         | GPort4_Bit1_PWM4    | Port 4, Bit 1, PWM 4.                               |

| 17         | GPort3_Bit5_PWM13                   | Port 3, Bit 5, PWM 13.                              | 67         | GPort4_Bit0_PWM6    | Port 4, Bit 0, PWM 6.                               |

| 18         | GPort3_Bit6_PWM11                   | Port 3, Bit 6, PWM 11.                              | 68         | GPort1_Bit7_PWM0/A4 | Port 1, Bit 7, PWM 0, Address 4.                    |

| 19         | GPort3_Bit7_PWM9                    | Port 3, Bit 7, PWM 9.                               | 69         | GPort1_Bit6_PWM2/A5 | Port 1, Bit 6, PWM 2, Address 5.                    |

| 20         | GPort5_Bit7_PWM15                   | Port 5, Bit 7, PWM 15.                              | 70         | GPort1_Bit5_PWM4/A6 | Port 1, Bit 5, PWM 4, Address 6.                    |

| 21         | GPort5_Bit6_PWM13                   | Port 5, Bit 6, PWM 13.                              | 71         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 22         | GPort5_Bit2_PWM11                   | Port 5, Bit 2, PWM 11.                              | 72         | GPort1_Bit4_PWM6    | Port 1, Bit 4, PWM 6.                               |

| 23         | GPort5_Bit3_PWM9                    | Port 5, Bit 3, PWM 9.                               | 73         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 24         | I <sup>2</sup> C Serial Clock (SCL) | I <sup>2</sup> C Clock.                             | 74         | GPort1_Bit3_PWM0    | Port 1, Bit 3, PWM 0.                               |

| 25         | DNU                                 | DNU = Do Not Use; leave floating.                   | 75         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 26         | DNU                                 | DNU = Do Not Use; leave floating.                   | 76         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 27         | DNU                                 | DNU = Do Not Use; leave floating.                   | 77         | GPort1_Bit2_PWM2    | Port 1, Bit 2, PWM 2.                               |

| 28         | I <sup>2</sup> C Serial Data (SDA)  | I <sup>2</sup> C Data.                              | 78         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 29         | GPort2_Bit3_PWM11/A1                | Port 2, Bit 3, PWM 11, Address 1.                   | 79         | GPort1_Bit1_PWM4    | Port 1, Bit 1, PWM 4.                               |

| 30         | AO                                  | Address 0.                                          | 80         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 31         | DNU                                 | DNU = Do Not Use; leave floating.                   | 81         | GPort1_Bit0_PWM6    | Port 1, Bit 0, PWM 6.                               |

| 32         | V <sub>dd</sub>                     | Supply voltage.                                     | 82         | V <sub>dd</sub>     | Supply voltage.                                     |

| 33         | DNU                                 | DNU = Do Not Use; leave floating.                   | 83         | V <sub>dd</sub>     | Supply voltage.                                     |

| 34         | V <sub>SS</sub>                     | Ground connection.                                  | 84         |                     | Ground connection.                                  |

|            |                                     |                                                     |            | V <sub>SS</sub>     |                                                     |

| 35         | DNU                                 | DNU = Do Not Use; leave floating.                   | 85         | V <sub>SS</sub>     | Ground connection.                                  |

| 36         | GPort7_Bit7_PWM15                   | Port 7, Bit 7, PWM 15.                              | 86         | GPort6_Bit0_PWM0    | Port 6, Bit 0, PWM 0.                               |

| 37         | GPort7_Bit6_PWM14                   | Port 7, Bit 6, PWM 14.                              | 87         | GPort6_Bit1_PWM1    | Port 6, Bit 1, PWM 1.                               |

| 38         | GPort7_Bit5_PWM13                   | Port 7, Bit 5, PWM 13.                              | 88         | GPort6_Bit2_PWM2    | Port 6, Bit 2, PWM 2.                               |

| 39         | GPort7_Bit4_PWM12                   | Port 7, Bit 4, PWM 12.                              | 89         | GPort6_Bit3_PWM3    | Port 6, Bit 3, PWM 3.                               |

| 40         | GPort7_Bit3_PWM11                   | Port 7, Bit 3, PWM 11.                              | 90         | GPort6_Bit4_PWM4    | Port 6, Bit 4, PWM 4.                               |

| 41         | GPort7_Bit2_PWM10                   | Port 7, Bit 2, PWM 10.                              | 91         | GPort6_Bit5_PWM5    | Port 6, Bit 5, PWM 5.                               |

| 42         | GPort7_Bit1_PWM9                    | Port 7, Bit 1, PWM 9.                               | 92         | GPort6_Bit6_PWM6    | Port 6, Bit 6, PWM 6.                               |

| 43         | GPort7_Bit0_PWM8                    | Port 7, Bit 0, PWM 8.                               | 93         | GPort6_Bit7_PWM7    | Port 6, Bit 7, PWM 7.                               |

| 44         | GPort2_Bit2_PWM8/WD                 | Port 2, Bit 2, PWM 8, E <sup>2</sup> Write Disable. | 94         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 45         | INT                                 |                                                     | 95         | GPort0_Bit0_PWM7    | Port 0, Bit 0, PWM 7.                               |

| 46         | GPort2_Bit1_PWM12/A2                | Port 7, Bit 7, PWM 0, Address 4.                    | 96         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 47         | GPort2_Bit0_PWM14/A3                | Port 7, Bit 6, PWM 2, Address 5.                    | 97         | GPort0_Bit1_PWM5    | Port 0, Bit 1, PWM 5.                               |

| 48         | DNU                                 | DNU = Do Not Use; leave floating.                   | 98         | DNU                 | DNU = Do Not Use; leave floating.                   |

| 49         | DNU                                 | DNU = Do Not Use; leave floating.                   | 99         | GPort0_Bit2_PWM3    | Port 0, Bit 2, PWM 3.                               |

| 50         | DNU                                 | DNU = Do Not Use; leave floating.                   | 100        | DNU                 | DNU = Do Not Use; leave floating.                   |

CY8C9560 100-Pin Device

a.) DNU = Do Not Use; leave floating.

# 2.2 PIN Descriptions

### 2.2.1 Extendable Soft Addressing™

The A0 line is always used to define the corresponding bit of the I2C address. This pin should be pulled up or down. If A0 is a strong pull-up or a strong pull-down (wired through 330 or less resistor to Vdd or Vss), then that is the only address line being specified and the A1-A6 lines are used as GPIO. If A0 is a weak pull-up or a weak pull-down (connected to Vdd or Vss through 75K- 200K-ohm resistor), then A0 is not the only externally defined address bit. There is a pin assigned to be A1 if it is needed. This pin can be pulled-up or pulled-down strong or weak with a resistor. As with A0, the type of pull determines whether the address bit is the last externally defined address bit. Differently from A0, A1 is not dedicated as an address pin. It is only used if A0 is not the only address bit externally defined. There are also predefined pins for A2, A3, A4, A5 and A6 that will only be used for addressing if needed. The last address bit in the chain is pulled strong. That way, only the number of pins needed to assign the address desired for the part are allocated as address pins, any pins not used for address bits are available to be used as GPIO pins. The Table , "Device Addressing," on page 3 defines the resulting device I2C address.

# 2.2.2 Interrupt Pin (INT)

The interrupt output (if enabled) is activated if one of the following events occurs:

- One of the GPIO port pins changes state and the corresponding bit in the Interrupt Mask register is set low.

- When a PWM driven by the slowest clock source (367.6 Hz) and assigned to a pin changes state and the pin's corresponding bit in the Interrupt Mask register is set low.

The interrupt line is deactivated when the master device performs a read from the corresponding Interrupt Status register.

### 2.2.3 Write Disable Pin (WD)

If this feature is enabled, '0' allows writes to the EEPROM and '1' blocks any memory writes. This pin is checked immediately before performing any write to memory. If the EEE bit in the Enable register is not set (EEPROM disabled) or bit EERO is set (EEPROM is read-only) then WD line level is ignored.

Note that '1' on this line blocks all commands which perform operations with EEPROM (see Table 3-9, "Available Commands," on page 14).

This line may be enabled/disabled by bit 1 of the Enable register (2Dh): '1' enables WD function, '0' disables.

### 2.2.4 External Reset Pin (XRES)

A full device reset is caused by pulling the XRES pin high. The XRES pin has an always-on pull-down resistor, so it does not require an external pull down for operation. It can be tied directly to ground or left open. Behavior after XRES is similar to POR.

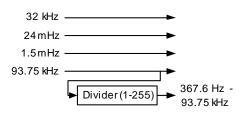

### 2.2.5 Working with PWMs

There are four independent PWMs in the CY8C9520, eight in the CY8C9540 and sixteen in the CY8C9560. Each I/O pin can be configured as a PWM output by writing '1' to the corresponding bit of the Select PWM register (see Table 3-2, "Output and Select PWM Registers Logic," on page 127).

The next step of PWM configuration is clock source selection using the Config PWM registers. There are six available clock sources: 32 kHz (default), 24 MHz, 1.5 MHz, 93.75 kHz, 367.6 Hz or previous PWM output. (see Figure 2-1).

#### Figure 2-1. Clock Sources

By default, 32 kHz is selected as the PWM clock.

PWM Period registers are used to set the output period:

$$t_{OUT} = Period \times t_{CLK}$$

Equation 1

Allowed values are between 1 and FFh.

The PWM Pulse Width register sets the duration of the PWM output pulse. Allowed values are between zero and the (Period-1) value. The duty cycle ratio can be computed using the following equation:

$$DutyCycle = \frac{PulseWidth}{Period}$$

Equation 2

Р

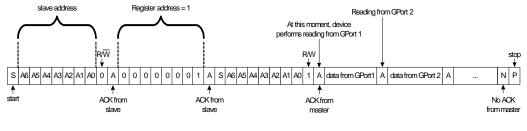

Figure 2-2. Memory Reading and Writing

Reading from GPort 1

Writing from GPort 1

Figure 2-3. Port Reading and Writing in Multi-Port Device

# 3. Register Reference

This chapter lists and describes the registers of the CY8C95xx device, starting with a register map and then detailed descriptions of register types.

# 3.1 Register Mapping Table

The register address is auto-incrementing. If the master device writes or reads data to or from one register and then continues data transfer in the same I2C transaction, sequential bytes will be written or read to or from the following registers. For example, if the first byte is sent to the Output Port 1 register, then the next bytes will be written to Output Port 2, Output Port 3, Output Port 4 etc. The first byte of each write transaction is treated as the register address.

To read data from a seires of registers, the master device should write the starting register address byte then perform a start and series of read transactions. If no address was sent, reads start from address 0.

To read a specific register address, the master device should write the register address byte, then perform a start and read transaction.

See Figure 1-3, "Port Reading and Writing in Multi-Port Device," on page 11.

The device's register mapping is listed in Table 3-1.

#### Table 3-1. The Device Register Address Map

| Address | Register                | Default Register<br>Value |

|---------|-------------------------|---------------------------|

| 00h     | Input Port 0            | None                      |

| 01h     | Input Port 1            | None                      |

| 02h     | Input Port 2            | None                      |

| 03h     | Input Port 3            | None                      |

| 04h     | Input Port 4            | None                      |

| 05h     | Input Port 5            | None                      |

| 06h     | Input Port 6            | None                      |

| 07h     | Input Port 7            | None                      |

| 08h     | Output Port 0           | FFh                       |

| 09h     | Output Port 1           | FFh                       |

| 0Ah     | Output Port 2           | FFh                       |

| 0Bh     | Output Port 3           | FFh                       |

| 0Ch     | Output Port 4           | FFh                       |

| 0Dh     | Output Port 5           | FFh                       |

| 0Eh     | Output Port 6           | FFh                       |

| 0Fh     | Output Port 7           | FFh                       |

| 10h     | Interrupt Status Port 0 | 00h                       |

| 11h     | Interrupt Status Port 1 | 00h                       |

| 12h     | Interrupt Status Port 2 | 00h                       |

#### Table 3-1. The Device Register Address Map (continued)

| Address | Register                     | Default Register<br>Value |

|---------|------------------------------|---------------------------|

| 13h     | Interrupt Status Port 3      | 00h                       |

| 14h     | Interrupt Status Port 4      | 00h                       |

| 15h     | Interrupt Status Port 5      | 00h                       |

| 16h     | Interrupt Status Port 6      | 00h                       |

| 17h     | Interrupt Status Port 7      | 00h                       |

| 18h     | Port Select                  | 00h                       |

| 19h     | Interrupt Mask               | FFh                       |

| 1Ah     | Select PWM for Port Output   | 00h                       |

| 1Bh     | Inversion                    | 00h                       |

| 1Ch     | Pin Direction - Input/Output | 00h                       |

| 1Dh     | Drive Mode - Pull Up         | FFh                       |

| 1Eh     | Drive Mode - Pull Down       | 00h                       |

| 1Fh     | Drive Mode - Open Drain High | 00h                       |

| 20h     | Drive Mode - Open Drain Low  | 00h                       |

| 21h     | Drive Mode - Strong          | 00h                       |

| 22h     | Drive Mode - Slow Strong     | 00h                       |

| 23h     | Drive Mode - High-Z          | 00h                       |

| 24h     | Reserved                     | None                      |

| 25h     | Reserved                     | None                      |

| 26h     | Reserved                     | None                      |

| 27h     | Reserved                     | None                      |

| 28h     | PWM Select                   | 00h                       |

| 29h     | Config PWM                   | 00h                       |

| 2Ah     | Period PWM                   | FFh                       |

| 2Bh     | Pulse Width PWM              | 80h                       |

| 2Ch     | Programmable Divider         | FFh                       |

| 2Dh     | Enable WDE, EEE, EERO        | 00h                       |

| 2Eh     | Device ID/Status             | 20h/40h/60h               |

| 2Fh     | Reserved                     | None                      |

| 30h     | Command                      | 00h                       |

# 3.2 Register Descriptions

The registers for the CY8C95xx are described in the sections that follow. Note that the PWM registers are located at addresses 28h to 2Bh.

#### 3.2.1 Input Port Registers (00h - 07h)

These registers represent actual logical levels on the pins and are used for I/O port reading operations. They are read-only.

The Inversion registers will change the state of reads to these ports.

### 3.2.2 Output Port Registers (08h - 0Fh)

These registers are used for writing data to GPIO ports. By default, all ports are in the pull-up mode allowing quasi-bidirectional I/O. To allow input operations without reconfiguration, these registers have to store '1's.

Output register data also affects pin states when PWMs are enabled. See Table 3-2. Output and Select PWM Registers Logic for details.

Figure 2-3 on page 10 illustrates port read/write procedures.

The Inversion registers have no effect on these ports.

#### 3.2.3 Int. Status Port Registers (10h - 17h)

Each '1' bit in these registers signals that there has been a change in the corresponding input line since the last read of that Interrupt Status register. Each Interrupt (Int.) Status register is cleared only after a read of that register.

If a PWM is assigned to a pin, then all state changes of the PWM will set the corresponding bit in the Interrupt Status register. If the pin's interrupt mask is cleared and the PWM is set to the slowest possible rate allowed (driven by the programmable clock source with divide register 2Dh set to FFh), then the INT line will also be driven on the PWM state change.

### 3.2.4 Port Select Register (18h)

This register is used to select the GPort to be configured. Write a value of 0-7 to this register to select the port to program with the following registers, 19h-23h.

### 3.2.5 Interrupt Mask Port Register (19h)

The Interrupt Mask register enables/disables activation of the INT line when GPIO input levels are changed. Each '1' in the Interrupt Mask register masks (disables) interrupts generated from the corresponding input line of the GPort selected by the Port Select register (18h).

### 3.2.6 Select PWM Register (1Ah)

This register is used to allow each port to act as a PWM output. By default, all ports are configured as GPIO lines. Each '1' in this register connects the corresponding pin of the GPort selected by the Port Select register (18h) to the PWM output. Output register data also affects the pin state when a PWM is enabled. See Table 3-2.

Note that a pin used as PWM output should be configured to the appropriate drive mode. See Table 3-4 on page 13 for more information.

Table 3-2 describes the logic of the Output and Select PWM registers.

| Table 3-2. | Output and | Select PWM | <b>Registers Logic</b> |

|------------|------------|------------|------------------------|

|------------|------------|------------|------------------------|

| Output | Select PWM | Pin State   |

|--------|------------|-------------|

| 0      | 0          | 0           |

| 1      | 0          | 1           |

| 0      | 1          | 0           |

| 1      | 1          | Current PWM |

### 3.2.7 Inversion Register (1Bh)

This register can invert the logic of the input ports. Each '1' written to this register inverts the logic of the corresponding bit in the Input register of the GPort selected by the Port Select register (18h).

The Input registers' logic is presented in Table 3-3.

These registers have no effect on outputs or PWMs.

#### Table 3-3. Inversion Register Logic

| Pin State | Invert | Input |

|-----------|--------|-------|

| 0         | 0      | 0     |

| 1         | 0      | 1     |

| 0         | 1      | 1     |

| 1         | 1      | 0     |

### 3.2.8 Port Direction Register (1Ch)

Each bit in a port can be configured as either an input or an output. To perform this configuration, the Port Direction register (1Ch) is used for the GPort selected by the Port Select register (18h). If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output.

### 3.2.9 Drive Mode Registers (1Dh-23h)

Each port's data pins can be set separately to one of seven available modes: pull-up/-down, open drain high/low, strong drive fast/slow, or high-impedance input. To perform this configuration, the seven drive mode registers are used for the GPort selected by the Port Select register (18h). Each '1' written to this register changes the corresponding line drive mode. Registers 1Dh through 23h have last-register priority meaning that the bit set to high in which the last register was written will override those that came before. Reading these registers reflects the actual setting, not what was originally written.

#### Table 3-4. Drive Mode Register Settings

| Register | Pin State           | Description                               |

|----------|---------------------|-------------------------------------------|

| 1Dh      | Resistive pull up   | Resistive high, strong low (default)      |

| 1Eh      | Resistive pull down | Strong high, resistive low                |

| 1Fh      | Open drain high     | Slow strong high, High-Z low              |

| 20h      | Open drain low      | Slow strong low, High-Z high              |

| 21h      | Strong drive        | Strong high, strong low, fast output mode |

| 22h      | Slow strong drive   | Strong high, strong low, slow output mode |

| 23h      | HIgh impedance      | High-Z                                    |

### 3.2.10 PWM Select Register (28h)

This register is used to select the PWM to be configured. Write a value of 00h-0Fh to this register to select the PWM to program with the following registers, 29h-2Bh.

### 3.2.11 Config (29h)

This register is used to choose the clock source for the PWM selected by the PWM Select register (28h) and interrupt logic.

There are six available clock sources: 32 kHz (default), 24 MHz, 1.5 MHz, 93.75 kHz, 367.6 Hz, or previous PWM output. The 367.6 Hz clock is user programmable. It divides the 93.75 kHz clock source by the divisor stored in the Divider register (2Ch). The default divide ratio is 255. (see Table 3-5 for details). By default, all PWMs are clocked from 32 kHz.

#### Table 3-5. PWM Clock Sources

| Config PWM | PWM Clock Source        |

|------------|-------------------------|

| xxxxx000b  | 32 kHz (default)        |

| xxxxx001b  | 24 MHz                  |

| xxxxx010b  | 1.5 MHz                 |

| xxxxx011b  | 93.75 kHz               |

| xxxxx100b  | 367.6 Hz (programmable) |

| xxxxx101b  | Previous PWM            |

Each PWM can generate an interrupt at the rising or falling edge of the output pulse. There is a limitation on the clock source for a PWM to generate an interrupt. Only the slowest speed source (programmed to 367.6 Hz) with the divider equal to 255 allows interrupt generation. Consequently, to create a PWM interrupt, it is necessary to choose the programmable divider output as the clock source (write xxxxx100b to Config register (29h)), write 255 to the Divide register (2Ch), and select PWM for pin output (1Ah).

Interrupt status is reflected in the Interrupt Status registers (10h-17h) and can cause INT line activation if enabled by the corresponding mask bit in the Interrupt Mask register:

### 3.2.12 Period Register (2Ah)

#### Table 3-6. Period Register

| Config PWM | PWM Interrupt on             |  |  |  |  |

|------------|------------------------------|--|--|--|--|

| xxxx0xxxb  | Falling pulse edge (default) |  |  |  |  |

| xxxx1xxxb  | Rising pulse edge            |  |  |  |  |

This register sets the period of the PWM counter. Allowed values are between 1 and FFh. The effective output waveform period of the PWM is:

$$t_{OUT} = Period \cdot t_{CLK}$$

### 3.2.13 Pulse Width Register (2Bh)

This register sets the pulse width of the PWM output. Allowed values are between zero and the (Period - 1) value. The duty cycle ratio can be computed using the following equation:

$$DutyCycle = \frac{PulseWidth}{Period}.$$

### 3.2.14 Divider Register (2Ch)

This register sets the frequency on the output of the programmable divider:

$$Frequency = \frac{93.75 \ kHz}{Divider}.$$

Allowed values are between 1 and 255.

#### 3.2.15 Enable Register (2Dh)

The WDE bit configures the write disable pin to operate either as a GPIO or as WD. It also enables/disables EEPROM operations (EEE bit) or makes the EEPROM read-only (EERO bit). Bit assignments are shown in Table 3-7 on page 14. Each '1' enables the corresponding feature, '0' disables.

#### Table 3-7. Enable Register

| Bit      | 7        | 6 | 5        | 4    | 3   | 2   | 1 | 0 |

|----------|----------|---|----------|------|-----|-----|---|---|

| Function |          | F | Reserved | EERO | EEE | WDE |   |   |

| Default  | Reserved |   |          |      |     | 0   | 0 | 0 |

Writes to this register differ from other registers. The write sequence to modify the Enable register is as follows:

- 1. Send device I2C address with bit 0.

- 2. Send register address 2Dh.

- **3.** Send unlock key the sequence of three bytes: 43h, 4Dh, 53h; ('C', 'M', 'S' in ASCII bytes).

- 4. Send new Enable register value.

This write sequence secures the register from accidental changes. The register can be read without the use of the unlock key.

By default, EERO and EEPROM (EEE bit) are disabled and WD line (WDE bit) is set to GPIO (WD disabled).

When performing a burst write operation that crosses this register, the data written to this register will be ignored and the address will increment to 2Eh.

#### 3.2.16 Device ID/Status Register (2Eh)

This register stores device identifiers (2xh/4xh/6xh) and reflects which settings were loaded during startup, either factory defaults (FD) or user defaults (UD). By default during startup, the device will attempt to load the user default block. If it seems to be corrupted then factory defaults are loaded and the low nibble of this register is set high to inform which set is active. The high nibble is always equal to 2 for CY8C9520, 4 for CY8C9540, and 6 for CY8C9560.

This register is read-only.

#### Table 3-8. Device ID Status Register

| Bit      | 7   | 8       | 5          | 4     | 3 | 2        | 1 | 0 |  |  |

|----------|-----|---------|------------|-------|---|----------|---|---|--|--|

| Function | Dev | ice Fam | ily (2, 4, | or 6) | F | Reserved |   |   |  |  |

### 3.2.17 Command Register (30h)

This register sends commands to the device, including current configuration as new POR defaults, restore factory defaults, define POR defaults, read POR defaults, write device configuration, read device configuration, and reconfigure device with stored POR defaults. The command set is presented in Table 3-9.

Note that registers are not restored in parallel. Do not assume any particular order to the restoration process.

#### Table 3-9. Available Commands

| Command | Description                                       |

|---------|---------------------------------------------------|

| 01h     | Store device configuration to EEPROM POR defaults |

| 02h     | Restore Factory Defaults                          |

| 03h     | Write EEPROM POR defaults                         |

| 04h     | Read EEPROM POR defaults                          |

| 05h     | Write device configuration                        |

| 06h     | Read device configuration                         |

| 07h     | Reconfigure device with stored POR defaults       |

# 3.3 Commands Description

## 3.3.1 Store Config to E<sup>2</sup> POR Defaults Cmd (01h)

The current ports settings (drive modes and output data) and other configuration registers are saved in the EEPROM by using the store configuration command (Cmd). These settings will be automatically loaded after the next device power-up or if the 07h command is issued.

### 3.3.2 Restore Factory Defaults Cmd (02h)

This command replaces the saved user configuration with the factory default configuration. Current settings are unaffected by this command. New settings will be loaded after the next device power-up or if the 07h command is issued.

# 3.3.3 Write E<sup>2</sup> POR Defaults Cmd (03h)

This command is used to send new power-up defaults to the CY8C95xx without changing current settings unless the 07h command is issued afterwards. This command is followed by 147 data bytes according to Table 3-10. The CRC is calculated as the XOR of the 146 data bytes (00h-91h). If the CRC check fails or an incomplete block is sent, then the slave will respond with a NAK and the data will not be saved to EEPROM.

To define new POR defaults the user must:

- Write command 03h;

- Write 146 data bytes with new values of registers;

- Write 1 CRC byte calculated as XOR of previous 146 data bytes.

Content of the data block is described in Table 3-10.

Table 3-10. POR Defaults Data Structure

| Offset    | Value                                 |

|-----------|---------------------------------------|

| 00h – 07h | Output Port 0-7                       |

| 08h – 0Fh | Interrupt mask Port 0-7               |

| 10h – 17h | Select PWM Port 0-7                   |

| 18h – 1Fh | Inversion Port 0-7                    |

| 20h – 27h | Pin Direction Port 0-7                |

| 28h       | Resistive pull up Drive Mode Port 0   |

| 29h       | Resistive pull down Drive Mode Port 0 |

| 2Ah       | Open drain high Drive Mode Port 0     |

| 2Bh       | Open drain low Drive Mode Port 0      |

| 2Ch       | Strong drive Drive Mode Port 0        |

| 2Dh       | Slow strong drive Drive Mode Port 0   |

| 2Eh       | High impedance Drive Mode Port 0      |

| 2Fh – 35h | Drive Modes Port 1                    |

| 36h – 3Ch | Drive Modes Port 2                    |

| 3Dh – 43h | Drive Modes Port 3                    |

| 44h – 4Ah | Drive Modes Port 4                    |

| 4Bh – 51h | Drive Modes Port 5                    |

| 52h – 58h | Drive Modes Port 6                    |

| 59h – 5Fh | Drive Modes Port 7                    |

| 60h       | Config setting PWM0                   |

| 61h       | Period setting PWM0                   |

| 62h       | Pulse Width setting PWM0              |

| 63h – 65h | PWM1 settings                         |

|           |                                       |

| 8Dh – 8Fh | PWM15 settings                        |

| 90h       | Divider                               |

| 91h       | Enable                                |

| 92h       | CRC                                   |

### 3.3.4 Read E2 POR Defaults Cmd (04h)

This command is used to read the POR settings stored in the EEPROM.

To read POR defaults the user must:

- Write command 04h;

- Read 146 data bytes (see Table 3-10).

- Read 1 CRC byte.

## 3.3.5 Write Device Config Cmd (05h)

This command is used to send a new device configuration to the CY8C95xx. It is followed by 146 data bytes according to Table 3-10. The CRC is calculated as the XOR of the 146 data bytes (00h-91h). If the CRC check fails or an incomplete block is sent, then the slave will respond with a NAK and the device will not use the data. This gives the user 'flat-address-space' access to all device settings.

To set the current device configuration the user must:

- Write command 05h;

- Write 146 data bytes with new values of registers;

- Write 1 CRC byte calculated as XOR of previous 146 data bytes.

If the CRC check passes, then the device will use the new settings immediately.

Content of the data block is described in Table 3-10.

### 3.3.6 Read Device Config Cmd (06h)

This command is used to read the current device configuration. It gives the user 'flat-address-space' access to all device settings.

To read device configuration the user must:

- Write command 06h;

- Read 146 data bytes (see Table 3-10).

- Read 1 CRC byte.

### 3.3.7 Reconfigure Device Cmd (07h)

This command is used to immediately reconfigure the device with actual POR defaults from EEPROM. It has the same effect on the registers as a POR.

This chapter presents the DC and AC electrical specifications of the CY8C95xx device. For the most up to date electrical specifications, confirm that you have the most recent data sheet by going to the web at http://www.cypress.com/psoc.

Specifications are valid for  $-40^oC \leq T_A \leq 85^oC$  and  $T_J \leq 100^oC,$  except where noted.

The following table lists the units of measure that are used in this chapter.

#### Table 4-1: Units of Measure

| Symbol | Unit of Measure             | Symbol | Unit of Measure |

|--------|-----------------------------|--------|-----------------|

| °C     | degree Celsius              | mA     | milli-ampere    |

| kHz    | kilohertz                   | nA     | nanoampere      |

| MHz    | megahertz                   | ns     | nanosecond      |

| μs     | microsecond                 | pF     | picofarad       |

| μV     | microvolts                  | V      | volts           |

| μVrms  | microvolts root-mean-square |        |                 |

# 4.1 Absolute Maximum Ratings

#### Table 4-2: Absolute Maximum Ratings

| Symbol           | Description                            | Min       | Тур | Max       | Units | Notes                                                        |

|------------------|----------------------------------------|-----------|-----|-----------|-------|--------------------------------------------------------------|

| T <sub>STG</sub> | Storage Temperature                    | -45       | -   | +100      | °C    | Higher storage temperatures will reduce data retention time. |

| T <sub>A</sub>   | Ambient Temperature with Power Applied | -40       | -   | +85       | °C    |                                                              |

| Vdd              | Supply Voltage on Vdd Relative to Vss  | -0.5      | -   | +6.0      | V     |                                                              |

| V <sub>IO</sub>  | DC Input Voltage                       | Vss - 0.5 | -   | Vdd + 0.5 | V     |                                                              |

| V <sub>IOZ</sub> | DC Voltage Applied to Tri-state        | Vss - 0.5 | -   | Vdd + 0.5 | V     |                                                              |

| I <sub>MIO</sub> | Maximum Current into any Port Pin      | -25       | -   | +50       | mA    |                                                              |

| ESD              | Electro Static Discharge Voltage       | 2000      | -   | -         | V     | Human Body Model ESD.                                        |

| LU               | Latch-up Current                       | -         | -   | 200       | mA    |                                                              |

# 4.2 Operating Temperature

#### Table 4-3: Operating Temperature

| Symbol         | Description          | Min | Тур | Max  | Units | Notes                                                                                                                                                                              |

|----------------|----------------------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient Temperature  | -40 | -   | +85  | °C    |                                                                                                                                                                                    |

| TJ             | Junction Temperature | -40 | -   | +100 | °C    | The temperature rise from ambient to junction is package specific. See "Thermal Impedances" on page 23. The user must limit the power consumption to comply with this requirement. |

# 4.3 DC Electrical Characteristics

#### 4.3.1 DC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, or 3.0V to 3.6V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and are for design guidance only.

#### Table 4-4: CY8C9520 DC Chip-Level Specifications

| Symbol           | Description             | Min  | Тур | Max  | Units | Notes                                                       |

|------------------|-------------------------|------|-----|------|-------|-------------------------------------------------------------|

| Vdd              | Supply Voltage          | 3.00 | -   | 5.25 | V     |                                                             |

| I <sub>DD</sub>  | Supply Current Vdd 5V   | -    | 3.8 | 5    | mA    | Conditions are 5.0V, $T_A = 25 ^{\circ}\text{C}$ , IOH = 0. |

| I <sub>DD3</sub> | Supply Current Vdd 3.3V | -    | 2.3 | 3    | mA    | Conditions are 3.3V, $T_A = 25 \ ^{o}C$ , IOH = 0.          |

#### Table 4-5: CY8C9540 DC Chip-Level Specifications

| Symbol           | Description             | Min  | Тур | Max  | Units | Notes                                              |

|------------------|-------------------------|------|-----|------|-------|----------------------------------------------------|

| Vdd              | Supply Voltage          | 3.00 | -   | 5.25 | V     |                                                    |

| I <sub>DD</sub>  | Supply Current Vdd 5V   | -    | 6   | 9    | mA    | Conditions are 5.0V, $T_A = 25 \ ^{o}C$ , IOH = 0. |

| I <sub>DD3</sub> | Supply Current Vdd 3.3V | -    | 3.3 | 6    | mA    | Conditions are 3.3V, $T_A = 25 \ ^{o}C$ , IOH = 0. |

#### Table 4-6: CY8C9560 DC Chip-Level Specifications

| Symbol           | Description                | Min | Тур | Max  | Units | Notes                                              |

|------------------|----------------------------|-----|-----|------|-------|----------------------------------------------------|

| Vdd              | Supply Voltage 3.00 -      |     | -   | 5.25 | V     |                                                    |

| I <sub>DD</sub>  | Supply Current Vdd 5V – 11 |     | 15  | 25   | mA    | Conditions are 5.0V, $T_A = 25 ^{o}C$ , IOH = 0.   |

| I <sub>DD3</sub> | Supply Current Vdd 3.3V    | -   | 5   | 9    | mA    | Conditions are 3.3V, $T_A = 25 \ ^{o}C$ , IOH = 0. |

### 4.3.2 DC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, or 3.0V to 3.6V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and are for design guidance only.

#### Table 4-7. DC Programming Specifications

| Symbol                | Description                          | Min       | Тур | Max | Units | Notes                         |

|-----------------------|--------------------------------------|-----------|-----|-----|-------|-------------------------------|

| Flash <sub>ENPB</sub> | Flash (EEPROM) Endurance (per block) | 50,000    | -   | -   | -     | Erase/write cycles per block. |

| Flash <sub>ENT</sub>  | Flash Endurance (total) <sup>1</sup> | 1,800,000 | -   | -   | -     | Erase/write cycles.           |

| Flash <sub>DR</sub>   | Flash Data Retention                 | 10        | -   | -   | Years |                               |

1. A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36x2 blocks of 25,000 maximum cycles each, or 36x4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36x50,000 and that no single block ever sees more than 50,000 cycles).

# 4.3.3 DC General Purpose I/O Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, or 3.0V to 3.6V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and are for design guidance only.

#### Table 4-8: DC GPIO Specifications

| Symbol           | Description                       | Min       | Тур | Max  | Units | Notes                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------|-----------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>  | High Output Level                 | Vdd - 1.0 | _   | _    | V     | IOH = 10 mA for any one pin, Vdd = 4.75 to<br>5.25V.<br>40 mA maximum combined IOH for GPort0;<br>GPort2_Bit3; GPort3; GPort5_Bit2, 3, 6, 7;<br>GPort6.<br>40 mA maximum combined IOH for GPort1;<br>GPort2_Bit0, 1, 2; GPort4; GPort5_Bit0, 1, 4, 5;<br>GPort7.<br>80 mA maximum combined IOH.    |

| V <sub>OL</sub>  | Low Output Level – – –            |           | _   | 0.75 | V     | IOL = 25 mA for any one pin, Vdd = 4.75 to<br>5.25V.<br>100 mA maximum combined IOL for GPort0;<br>GPort2_Bit3; GPort3; GPort5_Bit2, 3, 6, 7;<br>GPort6.<br>100 mA maximum combined IOL for GPort1;<br>GPort2_Bit0, 1, 2; GPort4; GPort5_Bit0, 1, 4, 5;<br>GPort7.<br>200 mA maximum combined IOL. |

| V <sub>IL</sub>  | Input Low Level                   | -         | -   | 0.8  | V     | Vdd = 3.0 to 5.5.                                                                                                                                                                                                                                                                                  |

| V <sub>IH</sub>  | Input High Level                  | 2.1       | -   |      | V     | Vdd = 3.0 to 5.5.                                                                                                                                                                                                                                                                                  |

| IIL              | Input Leakage (Absolute Value)    | -         | 1   | -    | nA    | Gross tested to 1 µA.                                                                                                                                                                                                                                                                              |

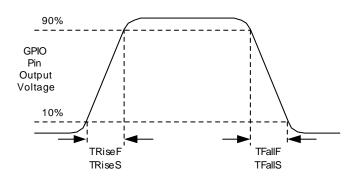

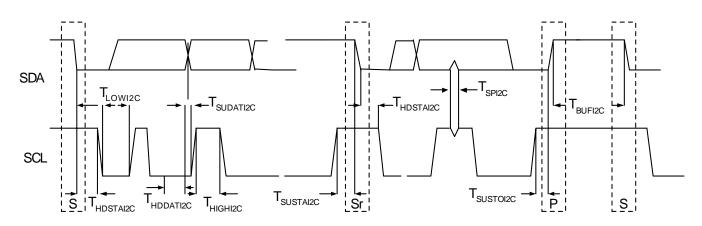

| C <sub>IN</sub>  | Capacitive Load on Pins as Input  | -         | 3.5 | 10   | pF    | Package and pin dependent. Temp = 25°C.                                                                                                                                                                                                                                                            |