# **DSP56000**

# 24-BIT DIGITAL SIGNAL PROCESSOR FAMILY MANUAL

Motorola, Inc. Semiconductor Products Sector DSP Division 6501 William Cannon Drive, West Austin, Texas 78735-8598

For More Information On This Product, Go to: www.freescale.com

Order this document by DSP56KFAMUM/AD

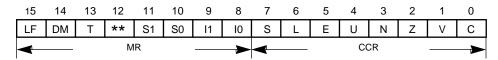

## MOTOROLA SEMICONDUCTOR TECHNICAL DATA

# **DSP56K Family**

# Addendum to 24-bit Digital Signal Processor Family Manual

This document, containing changes, additional features, further explanations, and clarifications, is a supplement to the original document:

#### DSP56KFAMUM/AD

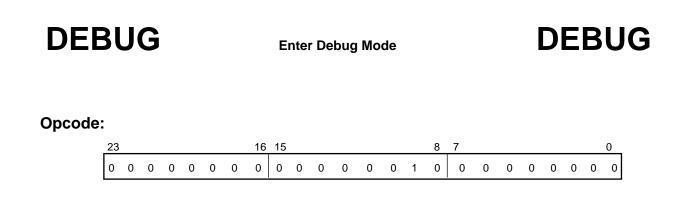

#### Family Manual

#### DSP56K Family 24-bit Digital Signal Processors

Change the following:

Page 11-4, Section 11.2.1 - Delete "4. NeXT<sup>TM</sup> under Mach".

Page A-83, third line - Replace "1;leN;le24" with "1≤N≤24"

Page A-104, Under the "Operation:" heading - Replace "D -1  $\Rightarrow$  D" with "D+1  $\Rightarrow$  D".

Page A-104, Second sentence after "Description:" heading - Replace "One is added from the LSB of D." with "One is added to the LSB of D; i.e. bit 0 of A0 or B0."

Page A-130, First symbolic description under the "Operation:" heading - Replace "If S[n]=0" with "If S[n]=1".

Page A-218, Timing description - Replace "**Timing:** 2+mvp oscillator clock cycles" with "**Timing:** 6 + ea + ap oscillator clock cycles".

Page A-219, Timing description - Replace "**Timing:** 2+mvp oscillator clock cycles" with "**Timing:** 6 + ea + ap oscillator clock cycles".

Page A-225, Timing description - Replace "**Timing:** 4+mvp oscillator clock cycles" with "**Timing:** 2+mvp oscillator clock cycles".

Page A-261, Timing description - Replace "**Timing:** 4 oscillator clock cycles" with "**Timing:** 2+mvp oscillator clock cycles".

Page A-261, Memory description - Replace "**Memory:** 1 program words" with "**Memory:** 1+ mv program words".

Page B-11, An inch below the middle of the page - Replace the "cir" instruction with "clr".

Page B-16, 7<sup>th</sup> instruction from bottom - Replace "Isl A,n0" with "Isl B A,n0".

© MOTOROLA INC., 1995

For More Information On This Product, Go to: www.freescale.com

# **TABLE OF CONTENTS**

| Paragraph |       | Page   |

|-----------|-------|--------|

| Number    | Title | Number |

|           |       |        |

#### SECTION 1 DSP56K FAMILY INTRODUCTION

| 1.1 |                                     | 1-3   |

|-----|-------------------------------------|-------|

| 1.2 | ORIGIN OF DIGITAL SIGNAL PROCESSING | 1-3   |

| 1.3 | SUMMARY OF DSP56K FAMILY FEATURES   | 1-9   |

| 1.4 | MANUAL ORGANIZATION                 | .1-11 |

#### SECTION 2 DSP56K CENTRAL ARCHITECTURE OVERVIEW

| 2.1 | DSP56K CENTRAL ARCHITECTURE OVERVIEW   | 2-3 |

|-----|----------------------------------------|-----|

| 2.2 | DATA BUSES                             | 2-3 |

| 2.3 | ADDRESS BUSES                          | 2-4 |

| 2.4 | DATA ALU                               | 2-5 |

| 2.5 | ADDRESS GENERATION UNIT                | 2-5 |

| 2.6 | PROGRAM CONTROL UNIT                   | 2-5 |

| 2.7 | MEMORY EXPANSION PORT (PORT A)         | 2-6 |

| 2.8 | ON-CHIP EMULATOR (OnCE)                | 2-6 |

| 2.9 | PHASE-LOCKED LOOP (PLL) BASED CLOCKING | 2-6 |

#### SECTION 3 DATA ARITHMETIC LOGIC UNIT

| 3.1 | DATA ARITHMETIC LOGIC UNIT         | 3-3 |

|-----|------------------------------------|-----|

| 3.2 | OVERVIEW AND DATA ALU ARCHITECTURE | 3-3 |

| 3.3 | DATA REPRESENTATION AND ROUNDING   | -10 |

| 3.4 | DOUBLE PRECISION MULTIPLY MODE     | -16 |

|     | - | -  |    | -      |            |

|-----|---|----|----|--------|------------|

| •   |   | ΓО | D, | $\sim$ | ι <b>Λ</b> |

| 1\/ |   |    | R  |        |            |

|     |   |    |    |        |            |

TABLE OF CONTENTS For More Information On This Product, Go to: www.freescale.com

#### **Table of Contents (Continued)**

####

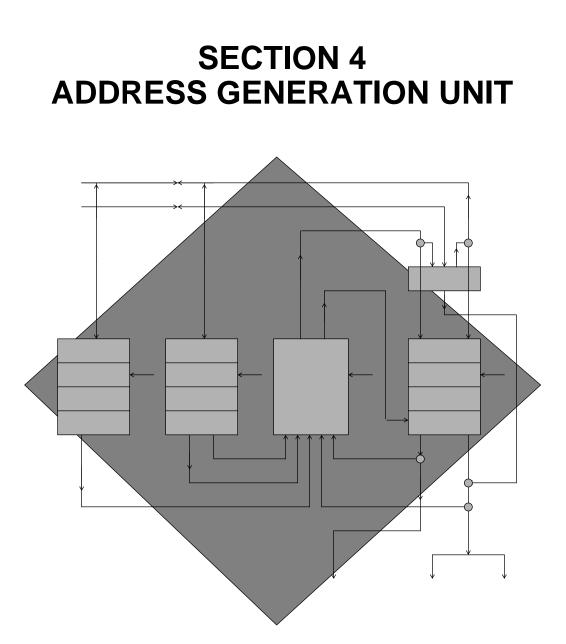

#### SECTION 4 ADDRESS GENERATION UNIT

| 4.1 | ADDRESS GENERATION UNIT AND ADDRESSING MODES | 4-3 |

|-----|----------------------------------------------|-----|

| 4.2 | AGU ARCHITECTURE                             | 4-3 |

| 4.3 | PROGRAMMING MODEL                            | 4-6 |

| 4.4 | ADDRESSING                                   | 4-8 |

#### SECTION 5 PROGRAM CONTROL UNIT

| 5.1 | PROGRAM CONTROL UNIT                    | .5-3 |

|-----|-----------------------------------------|------|

| 5.2 | OVERVIEW                                | .5-3 |

| 5.3 | PROGRAM CONTROL UNIT (PCU) ARCHITECTURE | .5-5 |

| 5.4 | PROGRAMMING MODEL                       | .5-8 |

#### SECTION 6 INSTRUCTION SET INTRODUCTION

| 6.1 | INSTRUCTION SET INTRODUCTION | 6-3  |

|-----|------------------------------|------|

| 6.2 | SYNTAX                       | 6-3  |

| 6.3 | INSTRUCTION FORMATS          | 6-3  |

| 6.4 | INSTRUCTION GROUPS           | 6-20 |

#### SECTION 7 PROCESSING STATES

| 7.1 | PROCESSING STATES                                   | 7-3  |

|-----|-----------------------------------------------------|------|

| 7.2 | NORMAL PROCESSING STATE                             | 7-3  |

| 7.3 | EXCEPTION PROCESSING STATE (INTERRUPT PROCESSING) . | 7-10 |

|  | ١ | J |

|--|---|---|

|  |   | 1 |

| TABLE OF CONTENTS<br>For More Information On This Product, |

|------------------------------------------------------------|

| Go to: www.freescale.com                                   |

MOTOROLA

#### Downloaded from Elcodis.com electronic components distributor

#### **Table of Contents (Continued)**

| Paragraph |  |

|-----------|--|

| Number    |  |

Semiconductor, Inc.

Freescale

| Number Title |                        | Number |

|--------------|------------------------|--------|

| 7.4          | RESET PROCESSING STATE | 7-33   |

| 7.5          | WAIT PROCESSING STATE  | 7-36   |

| 7.6          | STOP PROCESSING STATE  | 7-37   |

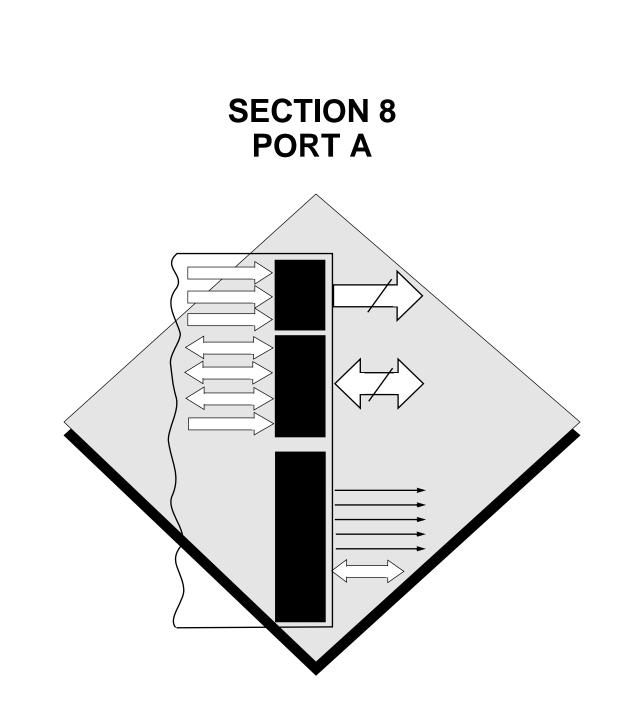

## SECTION 8 PORT A

| 8.1 | PORT A OVERVIEW  |  |

|-----|------------------|--|

| 8.2 | PORT A INTERFACE |  |

### SECTION 9 PLL CLOCK OSCILLATOR

| 9.1 | PLL CLOCK OSCILLATOR INTRODUCTION | 9-3   |

|-----|-----------------------------------|-------|

| 9.2 | PLL COMPONENTS                    | 9-3   |

| 9.3 | PLL PINS                          | 9-9   |

| 9.4 | PLL OPERATION CONSIDERATIONS      | .9-11 |

#### SECTION 10 ON-CHIP EMULATION (OnCE)

| 10.1  | ON-CHIP EMULATION INTRODUCTION                       | -3 |

|-------|------------------------------------------------------|----|

| 10.2  | ON-CHIP EMULATION (OnCE) PINS                        | -3 |

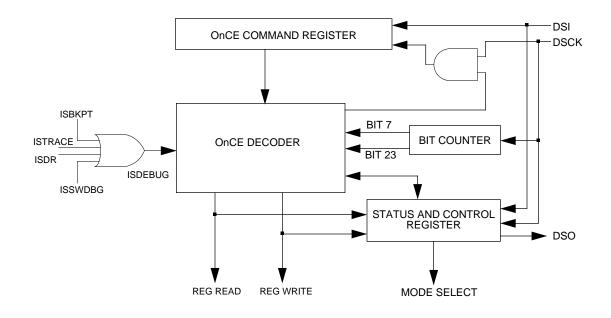

| 10.3  | OnCE CONTROLLER AND SERIAL INTERFACE                 | -6 |

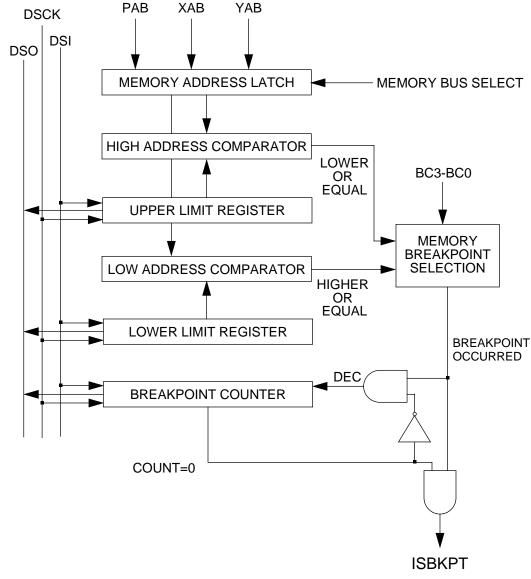

| 10.4  | OnCE MEMORY BREAKPOINT LOGIC10-                      | 11 |

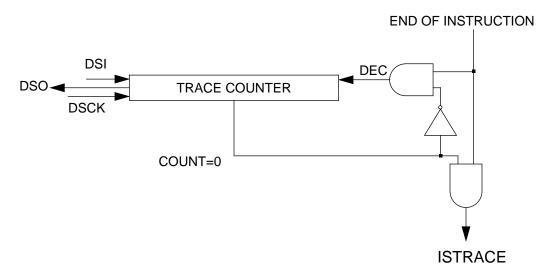

|       | OnCE TRACE LOGIC                                     |    |

| 10.6  | METHODS OF ENTERING THE DEBUG MODE                   | 14 |

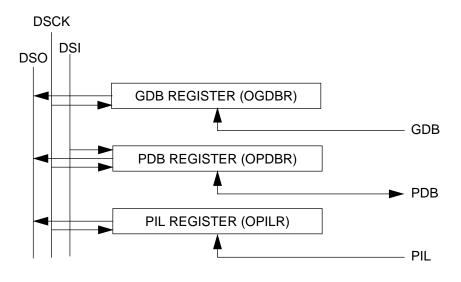

| 10.7  | PIPELINE INFORMATION AND GLOBAL DATA BUS REGISTER10- | 16 |

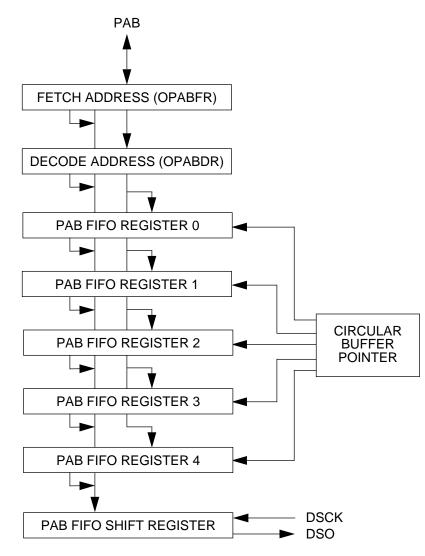

| 10.8  | PROGRAM ADDRESS BUS HISTORY BUFFER10-                | 18 |

| 10.9  | SERIAL PROTOCOL DESCRIPTION10-                       | 19 |

| 10.10 | DSP56K TARGET SITE DEBUG SYSTEM REQUIREMENTS10-      | 19 |

| 10.11 | USING THE OnCE                                       | 20 |

TABLE OF CONTENTS For More Information On This Product,

Go to: www.freescale.com

Page

Table of Contents (Continued)

#### Paragraph Number

Title

Page Number

MOTOROLA

#### SECTION 11 ADDITIONAL SUPPORT

| 11.1  | USER SUPPORT                                                                            | .11-3                                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.2  | MOTOROLA DSP PRODUCT SUPPORT                                                            | .11-4                                                                                                                                                                                                            |

| 11.3  | DSP56KADSx APPLICATION DEVELOPMENT SYSTEM                                               | .11-6                                                                                                                                                                                                            |

| 11.4  | Dr. BuB ELECTRONIC BULLETIN BOARD                                                       | .11-7                                                                                                                                                                                                            |

| 11.5  | MOTOROLA DSP NEWS1                                                                      | 1-16                                                                                                                                                                                                             |

| 11.6  | MOTOROLA FIELD APPLICATION ENGINEERS1                                                   | 1-16                                                                                                                                                                                                             |

| 11.7  | DESIGN HOTLINE- 1-800-521-62741                                                         | 1-16                                                                                                                                                                                                             |

| 11.8  | DSP HELP LINE – (512) 891-3230                                                          | 1-16                                                                                                                                                                                                             |

| 11.9  | MARKETING INFORMATION- (512) 891-2030                                                   | 1-16                                                                                                                                                                                                             |

| 11.10 | THIRD-PARTY SUPPORT INFORMATION - (512) 891-30981                                       | 1-16                                                                                                                                                                                                             |

| 11.11 | UNIVERSITY SUPPORT – (512) 891-30981                                                    | 1-16                                                                                                                                                                                                             |

| 11.12 | TRAINING COURSES - (602) 897-3665 or (800) 521-62741                                    | 1-17                                                                                                                                                                                                             |

| 11.13 | REFERENCE BOOKS AND MANUALS                                                             | 1-17                                                                                                                                                                                                             |

|       | 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8<br>11.9<br>11.10<br>11.11<br>11.12 | 11.2MOTOROLA DSP PRODUCT SUPPORT11.3DSP56KADSx APPLICATION DEVELOPMENT SYSTEM11.4Dr. BuB ELECTRONIC BULLETIN BOARD11.5MOTOROLA DSP NEWS11.6MOTOROLA FIELD APPLICATION ENGINEERS11.7DESIGN HOTLINE-1-800-521-6274 |

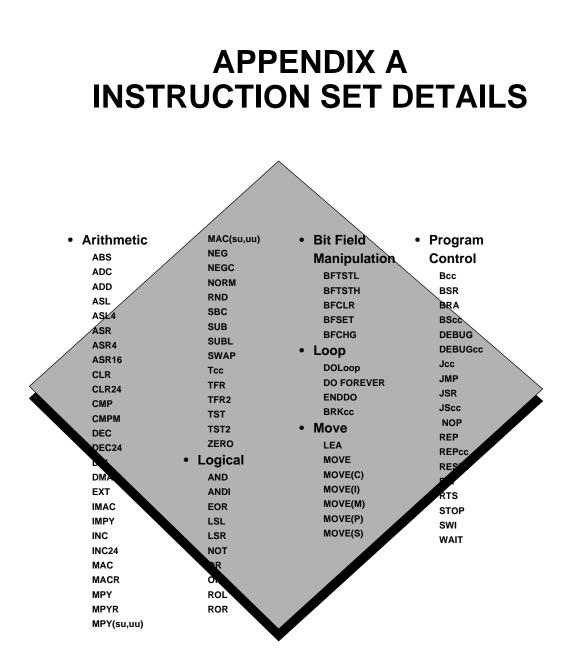

#### APPENDIX A INSTRUCTION SET DETAILS

| A.1  | APPENDIX A INTRODUCTION A-3             |

|------|-----------------------------------------|

| A.2  | INSTRUCTION GUIDE A-3                   |

|      | NOTATION                                |

| A.4  | ADDRESSING MODES A-10                   |

| A.5  | CONDITION CODE COMPUTATION A-15         |

| A.6  | PARALLEL MOVE DESCRIPTIONS A-20         |

| A.7  | INSTRUCTION DESCRIPTIONS A-21           |

| A.8  | INSTRUCTION TIMING A-294                |

| A.9  | INSTRUCTION SEQUENCE RESTRICTIONS A-305 |

| A.10 | INSTRUCTION ENCODING A-311              |

#### APPENDIX B BENCHMARK PROGRAMS

| B.1 |                    | B-3 |

|-----|--------------------|-----|

| B.2 | BENCHMARK PROGRAMS | B-3 |

TABLE OF CONTENTS For More Information On This Product,

Go to: www.freescale.com

Downloaded from Elcodis.com electronic components distributor

vi

# LIST of FIGURES

| Figur                                                                                                     | 'e                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Numb                                                                                                      | er Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Number                                                                                                                                                                        |

| 1-1<br>1-2<br>1-3                                                                                         | Analog Signal Processing<br>Digital Signal Processing<br>DSP Hardware Origins                                                                                                                                                                                                                                                                                                                                                                                             | 1-5                                                                                                                                                                           |

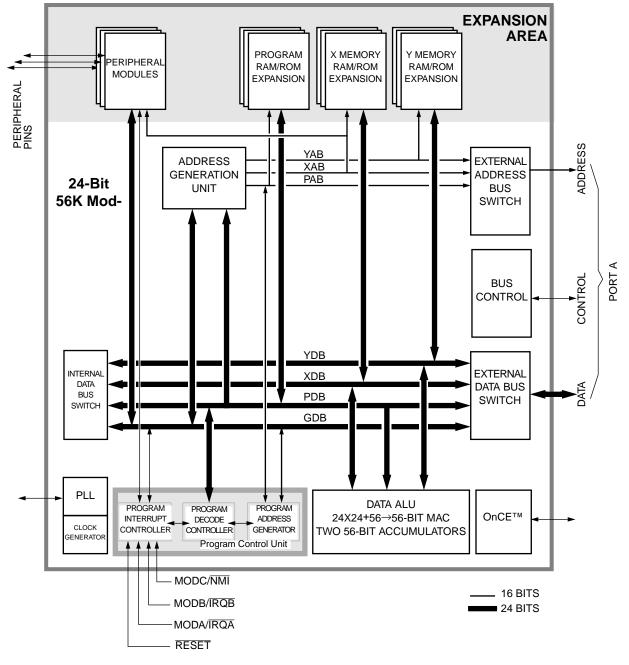

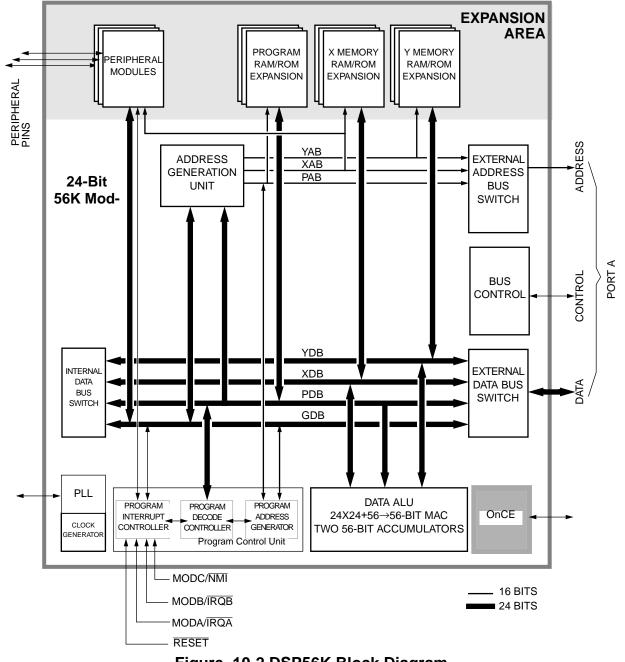

| 2-1                                                                                                       | DSP56K Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-4                                                                                                                                                                           |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14       | DSP56K Block Diagram<br>Data ALU<br>MAC Unit<br>DATA ALU Accumulator Registers<br>Saturation Arithmetic<br>Integer-to-Fractional Data Conversion<br>Bit Weighting and Alignment of Operands<br>Integer/Fractional Number Comparison<br>Integer/Fractional Multiplication Comparison<br>Convergent Rounding<br>Full Double Precision Multiply Algorithm<br>Single X Double Multiply Algorithm<br>Single X Double Multiply-Accumulate Algorithm<br>DSP56K Programming Model | 3-5          3-7          3-10          3-11          3-12          3-13          3-13          3-14          3-15          3-16          3-17          3-18                  |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13 | DSP56K Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li> 4-5</li> <li> 4-7</li> <li> 4-10</li> <li> 4-11</li> <li> 4-12</li> <li> 4-13</li> <li> 4-14</li> <li> 4-15</li> <li> 4-16</li> <li> 4-19</li> <li> 4-20</li> </ul> |

## List of Figures (Continued)

| Figur<br>Numb                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page<br>Number                                                                                                                     |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

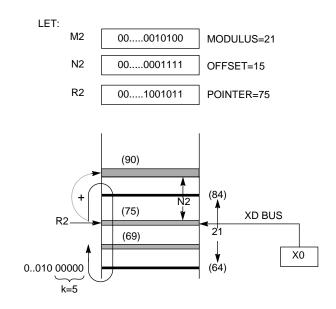

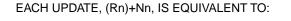

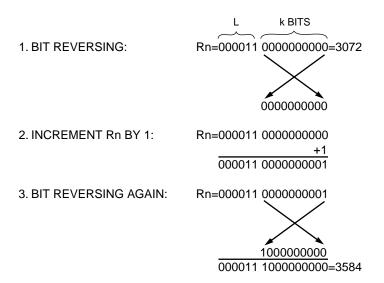

| 4-14<br>4-15                                                                        | Bit-Reverse Address Calculation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                    |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9                         | Program Address Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-4<br>5-7<br>5-8<br>5-9<br>5-14<br>5-15<br>5-15                                                                                   |

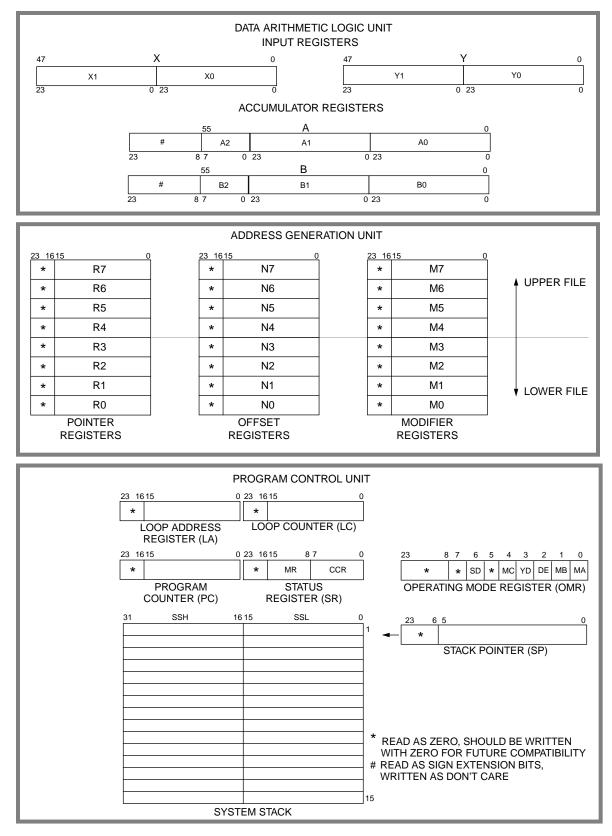

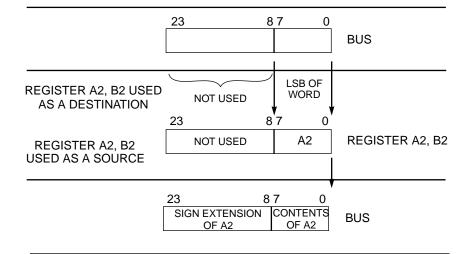

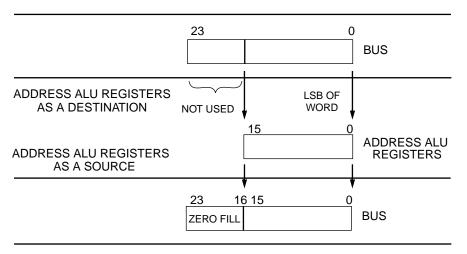

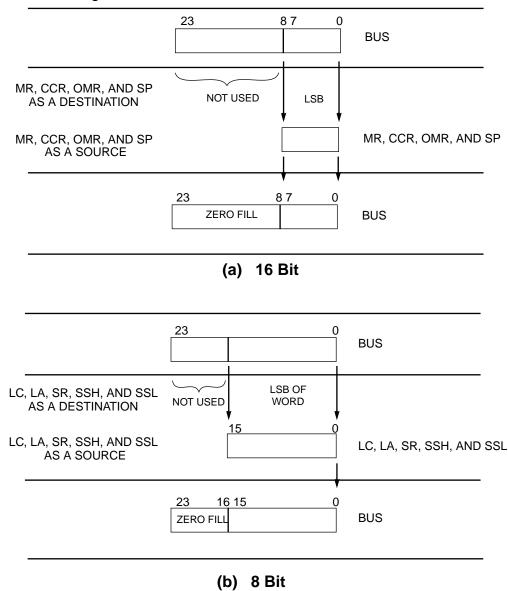

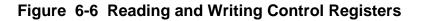

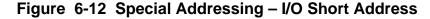

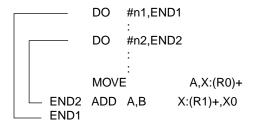

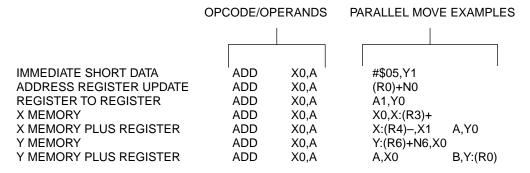

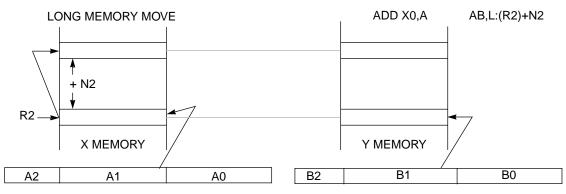

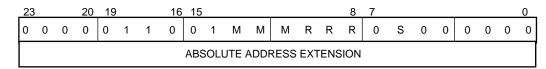

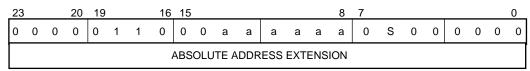

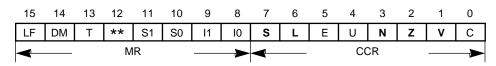

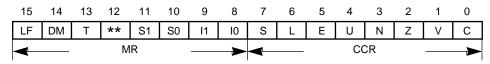

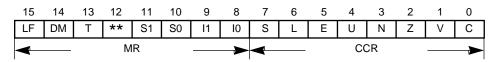

|                                                                                     | DSP56K Central Processing Module Programming Model<br>General Format of an Instruction Operation Word<br>Operand Sizes<br>Reading and Writing the ALU Extension Registers<br>Reading and Writing the Address ALU Registers<br>Reading and Writing Control Registers<br>Special Addressing – Immediate Data<br>Special Addressing – Absolute Addressing<br>Special Addressing – Immediate Short Data<br>Special Addressing – Short Jump Address<br>Special Addressing – Absolute Short Address<br>Special Addressing – I/O Short Address<br>Special Addressing – I/O Short Address<br>Hardware DO Loop<br>Classifications of Parallel Data Moves | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                               |

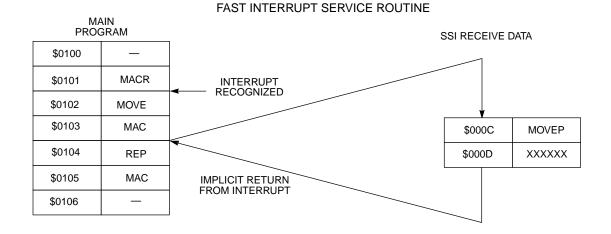

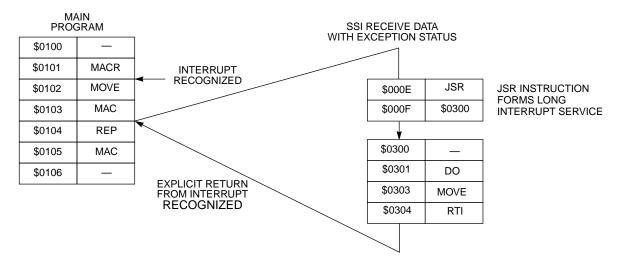

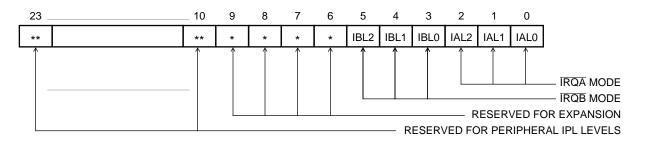

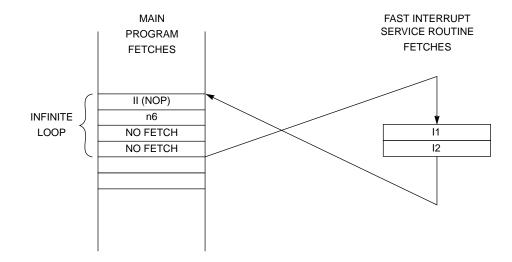

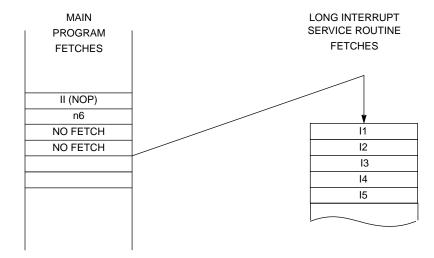

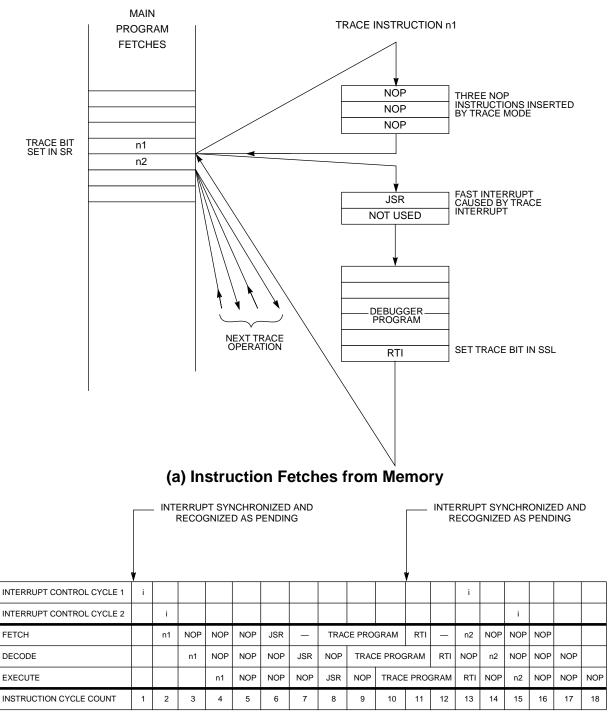

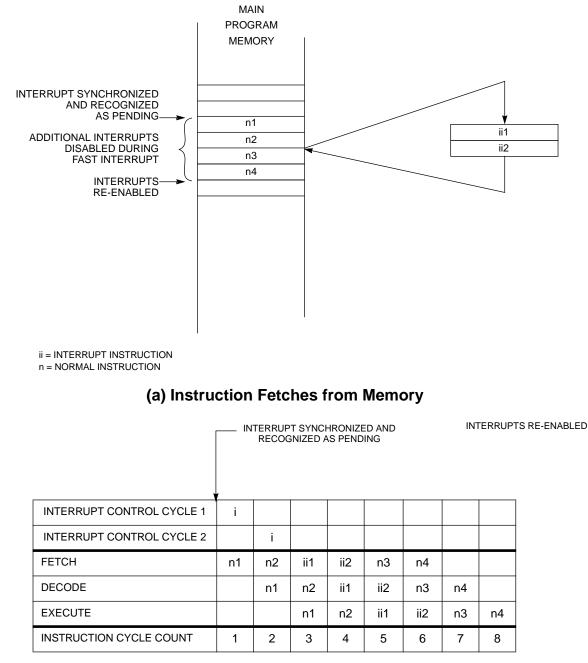

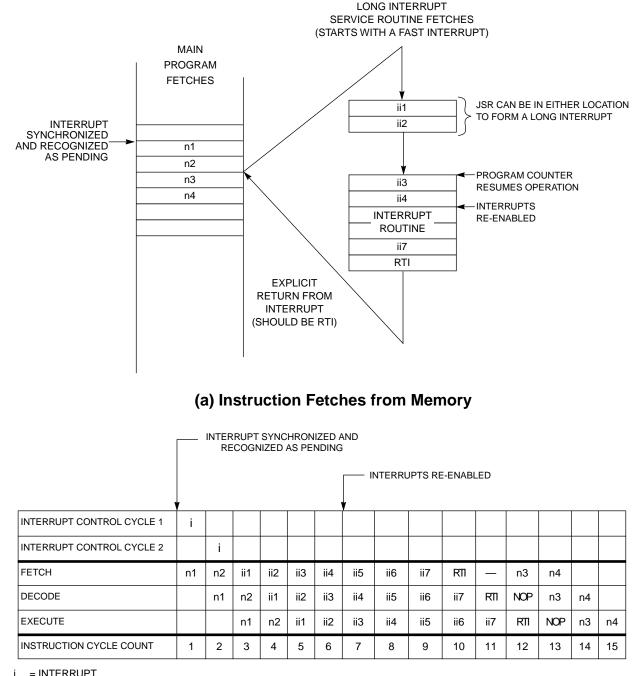

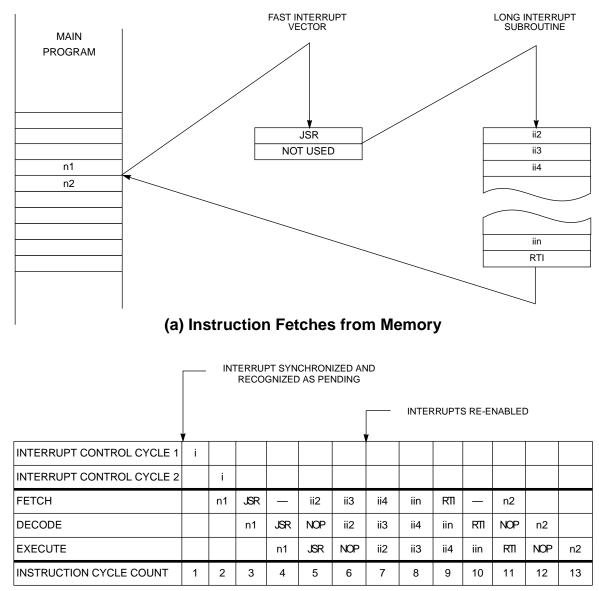

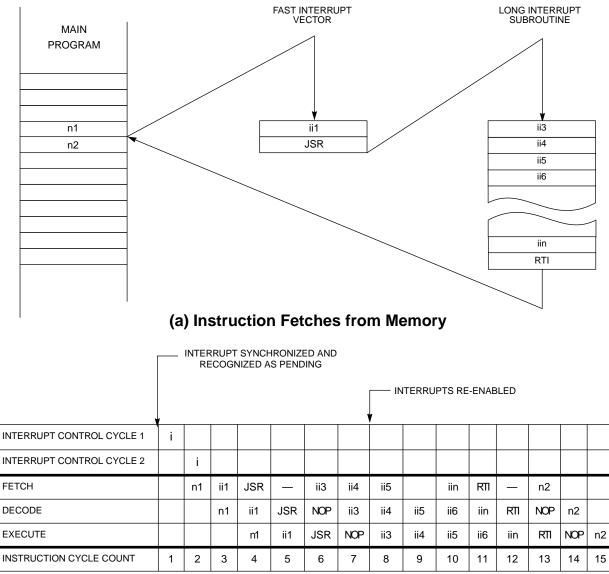

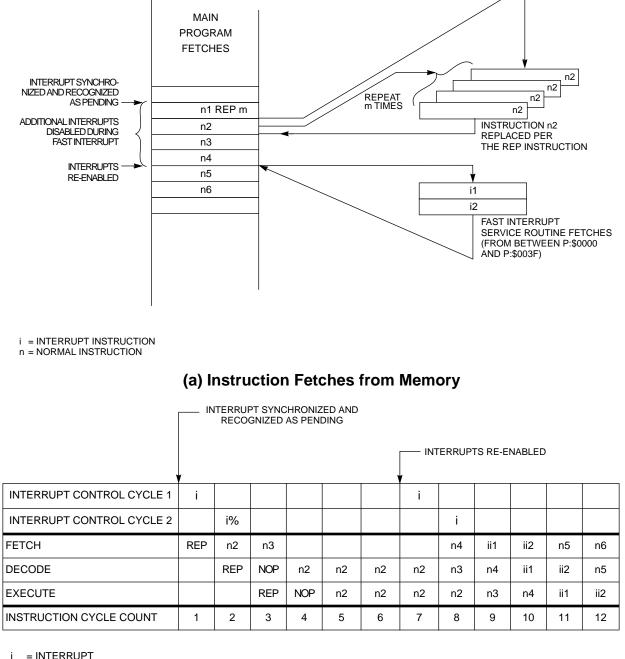

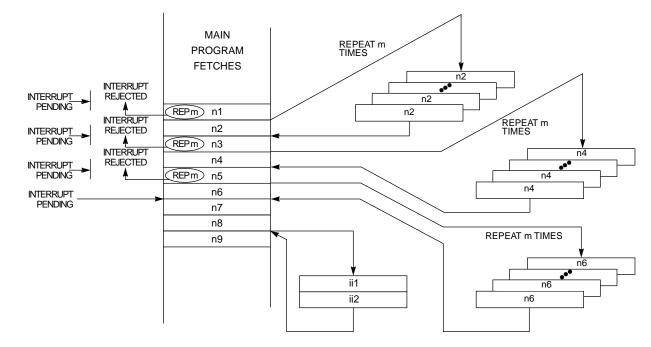

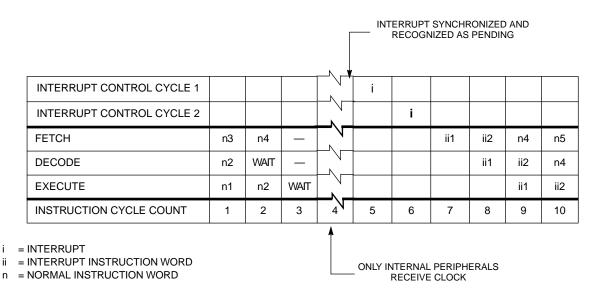

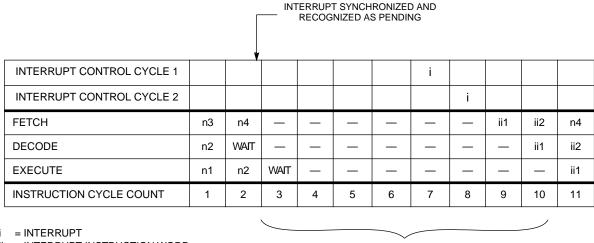

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8<br>7-9<br>7-10<br>7-11<br>7-12 | Fast and Long Interrupt ExamplesInterrupt Priority Register (Addr X:\$FFFF)Interrupting an SWIIllegal Instruction Interrupt Serviced by a Fast InterruptIllegal Instruction Interrupt Serviced by a Long InterruptRepeated Illegal InstructionTrace ExceptionFast Interrupt Service RoutineTwo Consecutive Fast InterruptsLong Interrupt Service RoutineJSR First Instruction of a Fast InterruptJSR Second Instruction of a Fast Interrupt                                                                                                                                                                                                     | 7-14          7-18          7-19          7-20          7-21          7-23          7-27          7-28          7-30          7-31 |

viii

LIST of FIGURES For More Information On This Product, Go to: www.freescale.com MOTOROLA

#### do to: www.irees

## List of Figures (Continued)

| Figure                                                               |                                                                                                                                                                                                                                                                                          | Page                                                    |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <u>Numb</u>                                                          | er Title                                                                                                                                                                                                                                                                                 | Number                                                  |

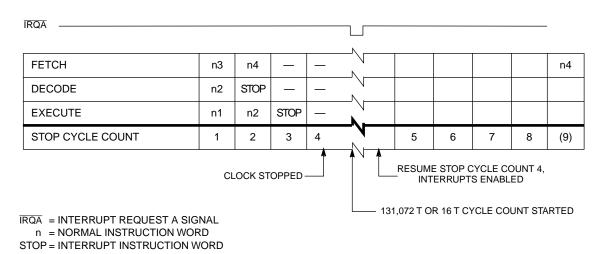

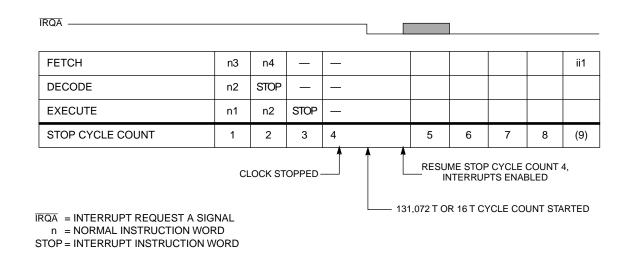

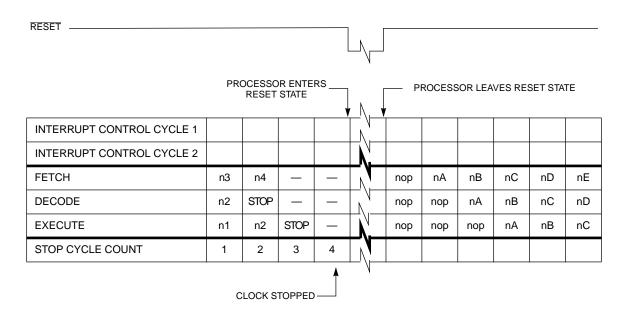

| 7-14<br>7-15<br>7-16<br>7-17                                         | STOP Instruction Sequence                                                                                                                                                                                                                                                                | 7-35<br>7-36<br>7-37<br>7-38<br>7-39                    |

| 8-1                                                                  | Port A Signals                                                                                                                                                                                                                                                                           | 8-4                                                     |

| 9-1<br>9-2<br>9-3                                                    | PLL Block DiagramDSP56K Block DiagramPLL Control Register (PCTL)                                                                                                                                                                                                                         | 9-4                                                     |

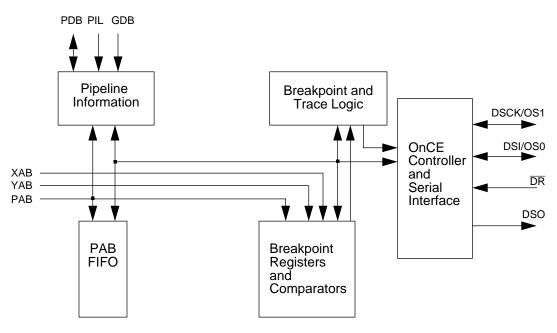

| 10-1<br>10-2<br>10-3<br>10-4<br>10-5<br>10-6<br>10-7<br>10-8<br>10-9 | OnCE Block Diagram<br>DSP56K Block Diagram<br>OnCE Controller and Serial Interface<br>OnCE Command Register<br>OnCE Status and Control Register (OSCR)<br>OnCE Memory Breakpoint Logic<br>OnCE Trace Logic Block Diagram<br>OnCE Pipeline Information and GDB Registers<br>OnCE PAB FIFO | 10-4<br>10-6<br>10-7<br>10-9<br>10-12<br>10-14<br>10-16 |

| B-1<br>B-2<br>B-3<br>B-4<br>B-5                                      | 20-Tap FIR Filter ExampleRadix 2, In-Place, Decimation-In-Time FFT.8-Pole 4-Multiply Cascaded Canonic IIR FilterLMS FIR Adaptive FilterReal Input FFT Based on Glenn Bergland Algorithm.                                                                                                 | B-7<br>B-9<br>B-11                                      |

# LIST of TABLES

| Table<br>Numb                                               |                                                                                                                                                                                                                                                                                                                  | Page<br>Number                                          |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 1-1                                                         | Benchmark Summary in Instruction Cycles                                                                                                                                                                                                                                                                          | 1-6                                                     |

| 3-1                                                         | Limited Data Values                                                                                                                                                                                                                                                                                              | 3-11                                                    |

| 4-1<br>4-2<br>4-3                                           | Address Register Indirect SummaryAddress Modifier SummaryBit-Reverse Addressing Sequence Example                                                                                                                                                                                                                 | 4-17                                                    |

| 6-1                                                         | Addressing Modes Summary                                                                                                                                                                                                                                                                                         | 6-21                                                    |

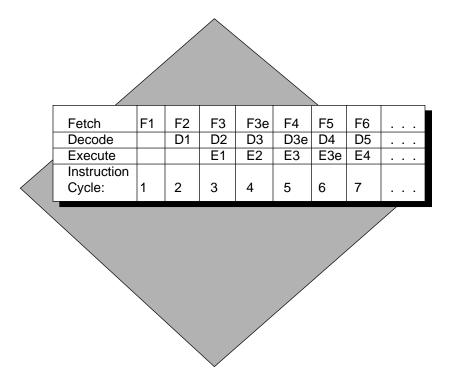

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6                      | Instruction Pipelining<br>Status Register Interrupt Mask Bits<br>Interrupt Priority Level Bits<br>External Interrupt<br>Central Processor Interrupt Priorities Within an IPL<br>Interrupt Sources                                                                                                                | 7-14<br>7-15<br>7-15<br>7-15                            |

| 9-1<br>9-2<br>9-3<br>9-4                                    | Multiplication Factor Bits MF0-MF11Division Factor Bits DF0-DF3PSTP and PEN RelationshipClock Output Disable Bits COD0-COD1                                                                                                                                                                                      | 9-7<br>9-8                                              |

| 10-1<br>10-2<br>10-3                                        | Chip Status Information<br>OnCE Register Addressing<br>Memory Breakpoint Control Table                                                                                                                                                                                                                           | 10-7                                                    |

| A-1<br>A-2<br>A-3<br>A-4<br>A-5<br>A-6<br>A-7<br>A-8<br>A-9 | Instruction Description Notation<br>DSP56K Addressing Modes<br>DSP56K Addressing Mode Encoding<br>Addressing Mode Modifier Summary<br>Condition Code Computations for Instructions (No Parallel Move)<br>Instruction Timing Summary<br>Parallel Data Move Timing<br>MOVEC Timing Summary<br>MOVEP Timing Summary | A-11<br>A-12<br>A-14<br>A-19<br>A-301<br>A-302<br>A-302 |

LIST of TABLES For More Information On This Product, Go to: www.freescale.com

MOTOROLA

Х

|      | List of Tables (Continued)                                   |        |

|------|--------------------------------------------------------------|--------|

| Tabl | 8                                                            | Page   |

| Numb | er Title                                                     | Number |

| A-10 | Bit Manipulation Timing Summary                              | A-303  |

| A-11 | Jump Instruction Timing Summary.                             |        |

| A-12 | RTI/RTS Timing Summary                                       |        |

| A-13 | Addressing Mode Timing Summary                               |        |

| A-14 | Memory Access Timing Summary                                 |        |

| A-15 | Single-Bit Register Encodings                                |        |

| A-16 | Single-Bit Special Register Encodings                        | A-312  |

| A-17 | Double-Bit Register Encodings                                | A-312  |

| A-18 | Triple-Bit Register Encodings.                               | A-313  |

| A-19 | (a) Four-Bit Register Encodings for 12 Registers in Data ALU | A-313  |

| A-19 | (b) Four-Bit Register Encodings for 16 Condition Codes       | A-313  |

| A-20 | Five-Bit Register Encodings for 28 Registers in              |        |

|      | Data ALU and Address ALU                                     |        |

| A-21 | Six-Bit Register Encodings for 43 Registers On-Chip          | A-314  |

| A-22 | Write Control Encoding                                       |        |

| A-23 | Memory Space Bit Encoding                                    |        |

| A-24 | Program Controller Register Encoding                         |        |

| A-25 | Condition Code and Address Encoding                          |        |

| A-26 | Effective Addressing Mode Encoding                           |        |

| A-27 | Operation Code K0-2 Decode                                   |        |

| A-28 | Operation Code QQQ Decode                                    |        |

| A-29 | Nonmultiply Instruction Encoding                             |        |

| A-30 | Special Case #1                                              |        |

| A-31 | Special Case #2                                              | A-334  |

|      |                                                              |        |

## List of Tables (Continued)

B-1 27-MHz Benchmark Results for the DSP56001R27 ..... B-4

|        | Freescale Semiconductor, in |                |

|--------|-----------------------------|----------------|

|        | List of Tables (Continued)  |                |

| Table  |                             | Page           |

| Number | Title                       | Page<br>Number |

MOTOROLA

Downloaded from **Elcodis.com** electronic components distributor

xii

# **SECTION CONTENTS**

| SECTION 1.1 INTRODUCTION                        | . 3  |

|-------------------------------------------------|------|

| SECTION 1.2 ORIGIN OF DIGITAL SIGNAL PROCESSING | . 3  |

| SECTION 1.2 SUMMARY OF DSP56K FAMILY FEATURES   | . 9  |

| SECTION 1.3 MANUAL ORGANIZATION                 | . 11 |

1 - 2

#### 1.1 INTRODUCTION

The DSP56K Family is Motorola's series of 24-bit general purpose Digital Signal Processors (DSPs<sup>\*</sup>). The family architecture features a central processing module that is common to the various family members, such as the DSP56002 and the DSP56004.

**Note:** The DSP56000 and the DSP56001 are not based on the central processing module architecture and should not be used with this manual. They will continue to be described in the DSP56000/DSP56001 User's Manual (DSP56000UM/AD Rev. 2).

This manual describes the DSP56K Family's central processor and instruction set. It is intended to be used with a family member's User's Manual, such as the DSP56002 User's Manual.

The User's Manual presents the device's specifics, including pin descriptions, operating modes, and peripherals. Packaging and timing information can be found in the device's Technical Data Sheet.

This chapter introduces general DSP theory and discusses the features and benefits of the Motorola DSP56K family of 24-bit processors. It also presents a brief description of each of the sections of the manual.

#### 1.2 ORIGIN OF DIGITAL SIGNAL PROCESSING

DSP is the arithmetic processing of real-time signals sampled at regular intervals and digitized. Examples of DSP processing include the following:

- Filtering of signals

- Convolution, which is the mixing of two signals

- Correlation, which is a comparison of two signals

- Rectification, amplification, and/or transformation of a signal

All of these functions have traditionally been performed using analog circuits. Only recently has semiconductor technology provided the processing power necessary to digitally perform these and other functions using DSPs.

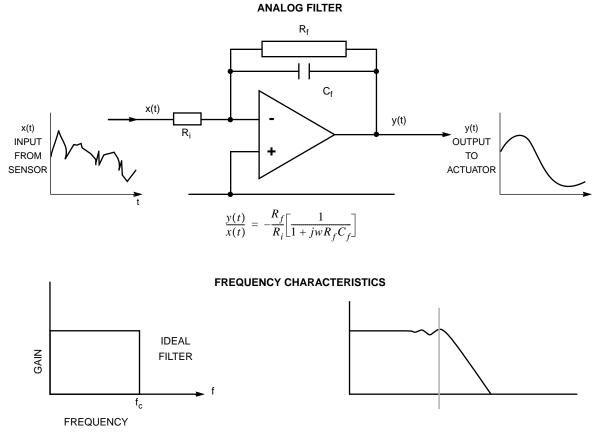

Figure 1-1 shows a description of analog signal processing. The circuit in the illustration filters a signal from a sensor using an operational amplifier, and controls an actuator with the result. Since the ideal filter is impossible to design, the engineer must design the filter for acceptable response, considering variations in temperature, component aging, power supply variation, and component accuracy. The resulting circuit typically has low noise immunity, requires adjustments, and is difficult to modify.

<sup>\*</sup>This manual uses the acronym DSP for Digital Signal Processing or Digital Signal Processor, depending on the context.

Figure 1-1 Analog Signal Processing

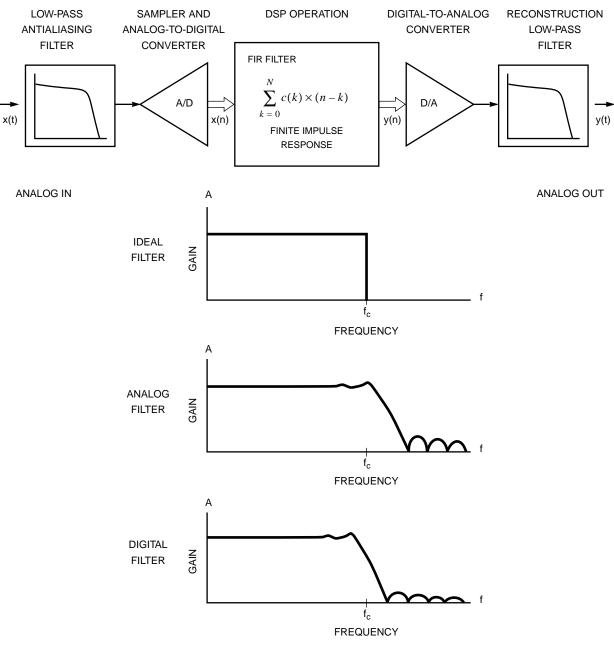

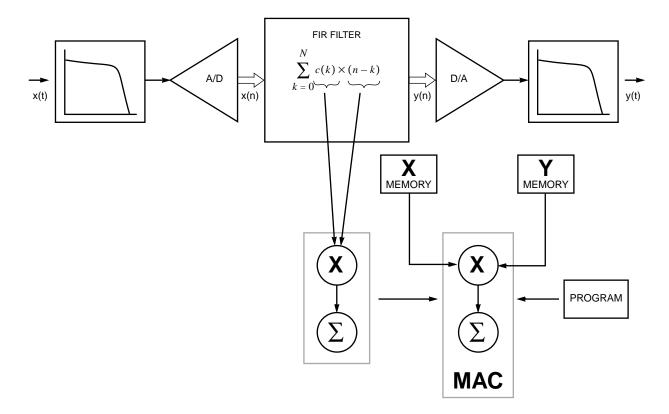

The equivalent circuit using a DSP is shown in Figure 1-2. This application requires an analog-to-digital (A/D) converter and digital-to-analog (D/A) converter in addition to the DSP. Even with these additional parts, the component count can be lower using a DSP due to the high integration available with current components.

Processing in this circuit begins by band-limiting the input with an anti-alias filter, eliminating out-of-band signals that can be aliased back into the pass band due to the sampling process. The signal is then sampled, digitized with an A/D converter, and sent to the DSP.

The filter implemented by the DSP is strictly a matter of software. The DSP can directly implement any filter that can also be implemented using analog techniques. Also, adaptive filters can be easily implemented using DSP, whereas these filters are extremely difficult to implement using analog techniques.

The DSP output is processed by a D/A converter and is low-pass filtered to remove the effects of digitizing. In summary, the advantages of using the DSP include the following:

1-4

- Fewer components

- Stable, deterministic performance

- Wide range of applications

- High noise immunity and power-supply rejection

- Self-test can be built in

- No filter adjustments

- Filters with much closer tolerances

- · Adaptive filters easily implemented

MOTOROLA

DSP56K FAMILY INTRODUCTION For More Information On This Product, Go to: www.freescale.com The DSP56K family is not designed for a particular application but is designed to execute commonly used DSP benchmarks in a minimum time for a single-multiplier architecture. For example, a cascaded, 2nd-order, four-coefficient infinite impulse response (IIR) biquad section has four multiplies for each section. For that algorithm, the theoretical minimum number of operations for a single-multiplier architecture is four per section. Table 1-1 shows a list of benchmarks with the number of instruction cycles a DSP56K chip uses compared to the number of multiplies the algorithm requires.

| Benchmark                                  | Number of Cycles | Number of<br>Algorithm<br>Multiplies |

|--------------------------------------------|------------------|--------------------------------------|

| Real Multiply                              | 3                | 1                                    |

| N Real Multiplies                          | 2N               | Ν                                    |

| Real Update                                | 4                | 1                                    |

| N Real Updates                             | 2N               | Ν                                    |

| N Term Real Convolution (FIR)              | N                | N                                    |

| N Term Real * Complex Convolution          | 2N               | N                                    |

| Complex Multiply                           | 6                | 4                                    |

| N Complex Multiplies                       | 4N               | N                                    |

| Complex Update                             | 7                | 4                                    |

| N Complex Updates                          | 4N               | 4N                                   |

| N Term Complex Convolution (FIR)           | 4N               | 4N                                   |

| N <sup>th</sup> - Order Power Series       | 2N               | 2N                                   |

| 2 <sup>nd</sup> - Order Real Biquad Filter | 7                | 4                                    |

| N Cascaded 2 <sup>nd</sup> - Order Biquads | 4N               | 4N                                   |

| N Radix Two FFT Butterflies                | 6N               | 4N                                   |

| Table 1-1 | Benchmark Summa | ary in Instruction | <b>Cycles</b> |

|-----------|-----------------|--------------------|---------------|

|-----------|-----------------|--------------------|---------------|

These benchmarks and others are used independently or in combination to implement functions whose characteristics are controlled by the coefficients of the benchmarks being executed. Useful functions using these and other benchmarks include the following:

1-6

#### **Freescale Semiconductor, Inc.** ORIGIN OF DIGITAL SIGNAL PROCESSING

#### **Digital Filtering**

Finite Impulse Response (FIR) Infinite Impulse Response (IIR) Matched Filters (Correlators) Hilbert Transforms Windowing Adaptive Filters/Equalizers

#### **Signal Processing**

Compression (e.g., Linear Predictive Coding of Speech Signals) Expansion Averaging Energy Calculations Homomorphic Processing Mu-law/A-law to/from Linear Data Conversion

#### **Data Processing**

Encryption/Scrambling Encoding (e.g., Trellis Coding) Decoding (e.g., Viterbi Decoding)

#### **Numeric Processing**

Scaler, Vector, and Matrix Arithmetic Transcendental Function Computation (e.g., Sin(X), Exp(X)) Other Nonlinear Functions Pseudo-Random-Number Generation

#### Modulation

Amplitude Frequency Phase

#### **Spectral Analysis**

Fast Fourier Transform (FFT) Discrete Fourier Transform (DFT) Sine/Cosine Transforms Moving Average (MA) Modeling Autoregressive (AR) Modeling ARMA Modeling

Useful applications are based on combining these and other functions. DSP applications affect almost every area in electronics because any application for analog electronic circuitry can be duplicated using DSP. The advantages in doing so are becoming more compelling as DSPs become faster and more cost effective. Some typical applications for DSPs are presented in the following list:

#### Telecommunication

Tone Generation Dual-Tone Multifrequency (DTMF) Subscriber Line Interface Full-Duplex Speakerphone Teleconferencing Voice Mail Adaptive Differential Pulse Code Modulation (ADPCM) Transcoder Medium-Rate Vocoders Noise Cancelation Repeaters Integrated Services Digital Network (ISDN) Transceivers Secure Telephones

#### **Data Communication**

High-Speed Modems Multiple Bit-Rate Modems High-Speed Facsimile

#### **Radio Communication**

Secure Communications Point-to-Point Communications Broadcast Communications Cellular Mobile Telephone

#### Computer

Array Processors Work Stations Personal Computers Graphics Accelerators

DSP56K FAMILY INTRODUCTION For More Information On This Product Go to: www.freescale.com

#### Freescale Semiconductor, Inc. ORIGIN OF DIGITAL SIGNAL PROCESSING

#### **Image Processing**

Pattern Recognition Optical Character Recognition Image Restoration Image Compression Image Enhancement Robot Vision

#### Graphics

3-D Rendering Computer-Aided Engineering (CAE) Desktop Publishing Animation

#### Instrumentation

Spectral Analysis Waveform Generation Transient Analysis Data Acquisition

#### **Speech Processing**

Speech Synthesizer Speech Recognizer Voice Mail Vocoder Speaker Authentication Speaker Verification

#### **Audio Signal Processing**

Digital AM/FM Radio Digital Hi-Fi Preamplifier Noise Cancelation Music Synthesis Music Processing Acoustic Equalizer

#### **High-Speed Control**

Laser-Printer Servo Hard-Disk Servo Robotics Motor Controller Position and Rate Controller

#### Vibration Analysis

Electric Motors Jet Engines Turbines

#### **Medical Electronics**

Cat Scanners Sonographs X-Ray Analysis Electrocardiogram Electroencephalogram Nuclear Magnetic Resonance Analysis

#### **Digital Video**

Digital Television High-Resolution Monitors

#### **Radar and Sonar Processing**

Navigation Oceanography Automatic Vehicle Location Search and Tracking

#### Seismic Processing

Oil Exploration Geological Exploration

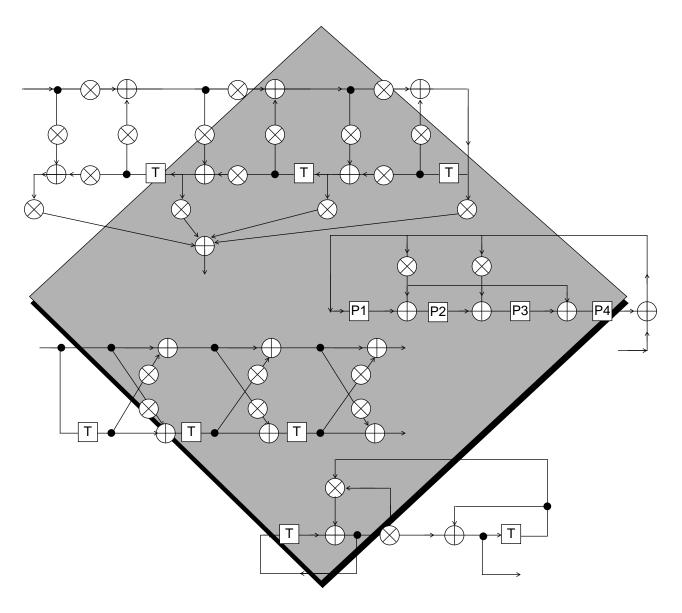

As shown in Figure 1-3, the keys to DSP are as follows:

- The Multiply/Accumulate (MAC) operation

- Fetching operands for the MAC

- Program control to provide versatile operation

- Input/Output to move data in and out of the DSP

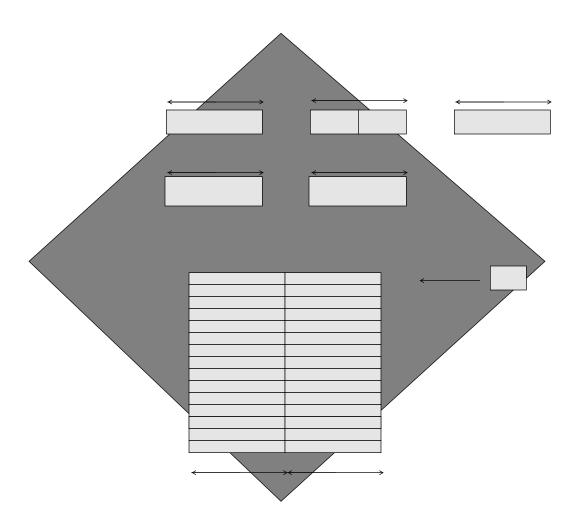

MAC is the basic operation used in DSP. The DSP56K family of processors has a dual Harvard architecture optimized for MAC operations. Figure 1-3 shows how the DSP56K

1- 8

DSP56K FAMILY INTRODUCTION For More Information On This Product Go to: www.freescale.com

architecture matches the shape of the MAC operation. The two operands, C() and X(), are directed to a multiply operation, and the result is summed. This process is built into the chip by using two separate memories (X and Y) to feed a single-cycle MAC. The entire process must occur under program control to direct the correct operands to the multiplier and save the accumulator as needed. Since the two memories and the MAC are independent, the DSP can perform two moves, a multiply and an accumulate, in a single operation. As a result, many of the benchmarks shown in Table 1-1 can be executed at or near the theoretical maximum speed for a single-multiplier architecture.

#### 1.3 SUMMARY OF DSP56K FAMILY FEATURES

The high throughput of the DSP56K family of processors makes them well suited for communication, high-speed control, numeric processing and computer and audio applications. The main features that contribute to this high throughput include:

• **Speed** — Speeds high enough to easily address applications traditionally served by low-end floating point DSPs.

Figure 1-3 DSP Hardware Origins

Downloaded from Elcodis.com electronic components distributor

#### **Freescale Semiconductor, Inc.** SUMMARY OF DSP56K FAMILY FEATURES

- **Precision** The data paths are 24 bits wide, providing 144 dB of dynamic range; intermediate results held in the 56-bit accumulators can range over 336 dB.

- Parallelism Each on-chip execution unit (AGU, program control unit, data ALU), memory, and peripheral operates independently and in parallel with the other units through a sophisticated bus system. The data ALU, AGU, and program control unit operate in parallel so that an instruction prefetch, a 24-bit x 24-bit multiplication, a 56-bit addition, two data moves, and two address-pointer updates using one of three types of arithmetic (linear, modulo, or reverse-carry) can be executed in a single instruction cycle. This parallelism allows a four-coefficient IIR filter section to be executed in only four cycles, the theoretical minimum for single-multiplier architecture. At the same time, the two serial controllers can send and receive full-duplex data, and the host port can send/receive simplex data.

- Flexibility While many other DSPs need external communications circuitry to interface with peripheral circuits (such as A/D converters, D/A converters, or host processors), the DSP56K family provides on-chip serial and parallel interfaces which can support various configurations of memory and peripheral modules

- **Sophisticated Debugging** Motorola's on-chip emulation technology (OnCE) allows simple, inexpensive, and speed independent access to the internal registers for debugging. OnCE tells application programmers exactly what the status is within the registers, memory locations, buses, and even the last five instructions that were executed.

- Phase-locked Loop (PLL) Based Clocking PLL allows the chip to use almost any available external system clock for full-speed operation while also supplying an output clock synchronized to a synthesized internal core clock. It improves the synchronous timing of the processors' external memory port, eliminating the timing skew common on other processors.

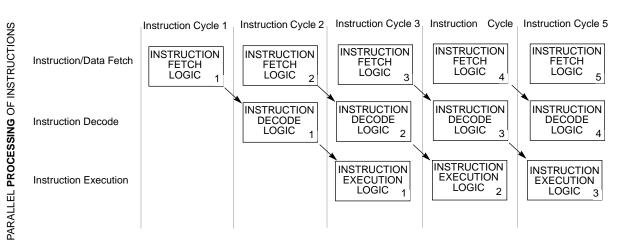

- **Invisible Pipeline** The three-stage instruction pipeline is essentially invisible to the programmer, allowing straightforward program development in either assembly language or a high-level language such as a full Kernighan and Ritchie C.

- Instruction Set The instruction mnemonics are MCU-like, making the transition from programming microprocessors to programming the chip as easy as possible. The orthogonal syntax controls the parallel execution units. The hardware DO loop instruction and the repeat (REP) instruction make writing straight-line code obsolete.

1- 10

- **DSP56001 Compatibility** All members of the DSP56K family are downward compatible with the DSP56001, and also have added flexibility, speed, and functionality.

- Low Power As a CMOS part, the DSP56000/DSP56001 is inherently very low power and the STOP and WAIT instructions further reduce power requirements.

#### 1.4 MANUAL ORGANIZATION

This manual describes the central processing module of the DSP56K family in detail and provides practical information to help the user:

- Understand the operation of the DSP56K family

- Design parallel communication links

- Design serial communication links

- Code DSP algorithms

- Code communication routines

- Code data manipulation algorithms

- Locate additional support

The following list describes the contents of each section and each appendix:

#### Section 2 – DSP56K Central Architecture Overview

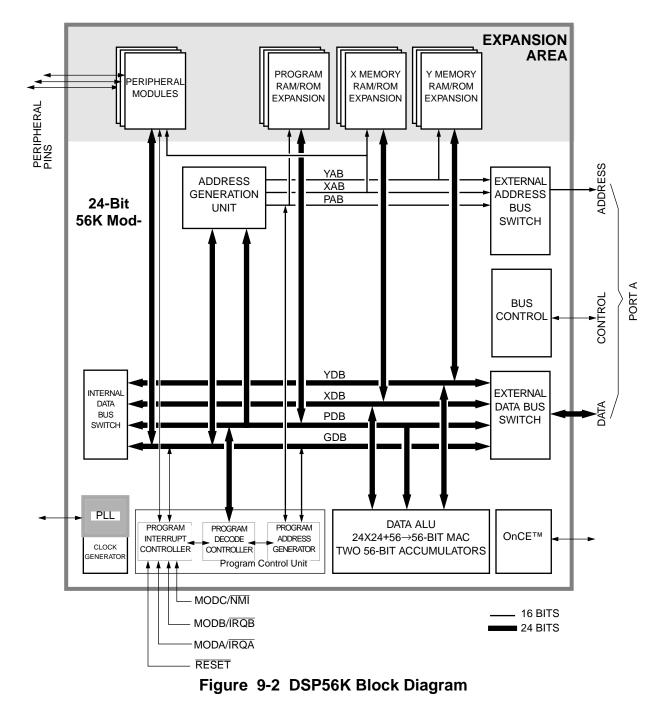

The DSP56K central architecture consists of the data arithmetic logic unit (ALU), address generation unit (AGU), program control unit, On-Chip Emulation (OnCE) circuitry, the phase locked loop (PLL) based clock oscillator, and an external memory port (Port A). This section describes each subsystem and the buses interconnecting the major components in the DSP56K central processing module.

#### Section 3 – Data Arithmetic Logic Unit

This section describes in detail the data ALU and its programming model.

#### Section 4 – Address Generation Unit

This section specifically describes the AGU, its programming model, address indirect modes, and address modifiers.

#### Section 5 – Program Control Unit

This section describes in detail the program control unit and its programming model.

#### Section 6 – Instruction Set Introduction

This section presents a brief description of the syntax, instruction formats, operand/memory references, data organization, addressing modes, and instruction set. A detailed description of each instruction is given in APPENDIX A - INSTRUCTION SET DETAILS.

#### Section 7 - Processing States

This section describes the five processing states (normal, exception, reset, wait, and stop).

#### Section 8 – Port A

This section describes the external memory port, its control register, and control signals.

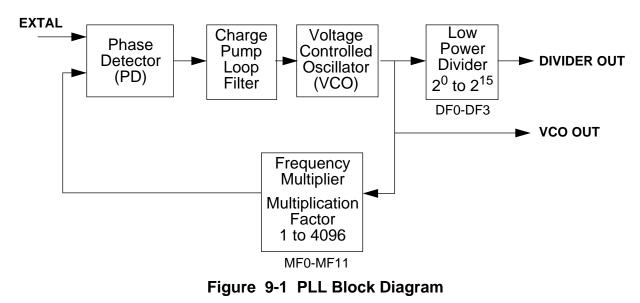

Section 9 - PLL Clock Oscillator

This section describes the PLL and its functions

Section 10 – On-Chip Emulator (OnCE)

This section describes the OnCE circuitry and its functions.

#### Section 11 – Additional Support

This section presents a brief description of current support products and services and information on where to obtain them.

#### Appendix A – Instruction Set Details

A detailed description of each DSP56K family instruction, its use, and its affect on the processor are presented.

#### Appendix B – Benchmarks

DSP5K family benchmark results are listed in this appendix.

1- 12

DSP56K CENTRAL ARCHITECTURE OVERVIEW For More Information On This Product,

Go to: www.freescale.com

# **SECTION CONTENTS**

| SECTION 2.1 DSP56K CENTRAL ARCHITECTURE OVERVIEW   | 3 |

|----------------------------------------------------|---|

| SECTION 2.2 DATA BUSES                             | 3 |

| SECTION 2.3 ADDRESS BUSES                          | 4 |

| SECTION 2.4 DATA ALU                               | 5 |

| SECTION 2.5 ADDRESS GENERATION UNIT                | 5 |

| SECTION 2.6 PROGRAM CONTROL UNIT                   | 5 |

| SECTION 2.7 MEMORY EXPANSION PORT (PORT A)         | 6 |

| SECTION 2.8 ON-CHIP EMULATOR (OnCE)                | 6 |

| SECTION 2.9 PHASE-LOCKED LOOP (PLL) BASED CLOCKING | 6 |

2 - 2

DSP56K CENTRAL ARCHITECTURE OVERVIEW For More Information On This Product, Go to: www.freescale.com

#### 2.1 DSP56K CENTRAL ARCHITECTURE OVERVIEW

The DSP56K family of processors is built on a standard central processing module. In the expansion area around the central processing module, the chip can support various configurations of memory and peripheral modules which may change from family member to family member. This section introduces the architecture and the major components of the central processing module.

The central components are:

- Data Buses

- Address Buses

- Data Arithmetic Logic Unit (data ALU)

- Address Generation Unit (AGU)

- Program Control Unit (PCU)

- Memory Expansion (Port A)

- On-Chip Emulator (OnCE<sup>™</sup>) circuitry

- Phase-locked Loop (PLL) based clock circuitry

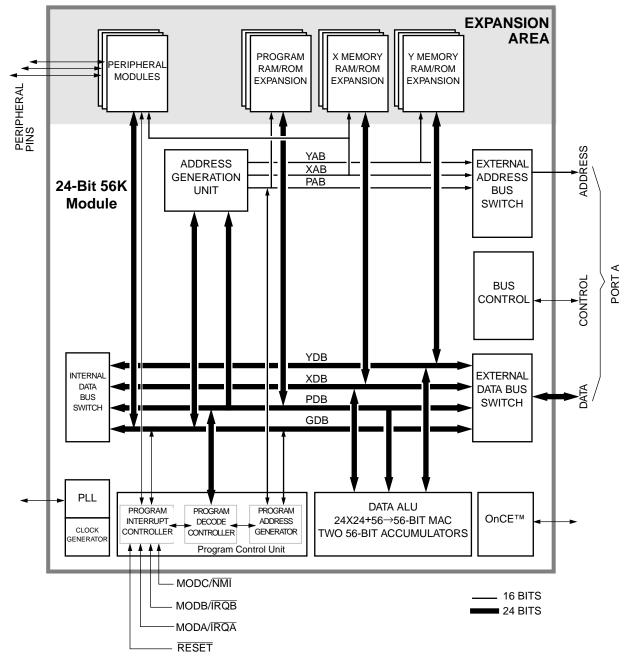

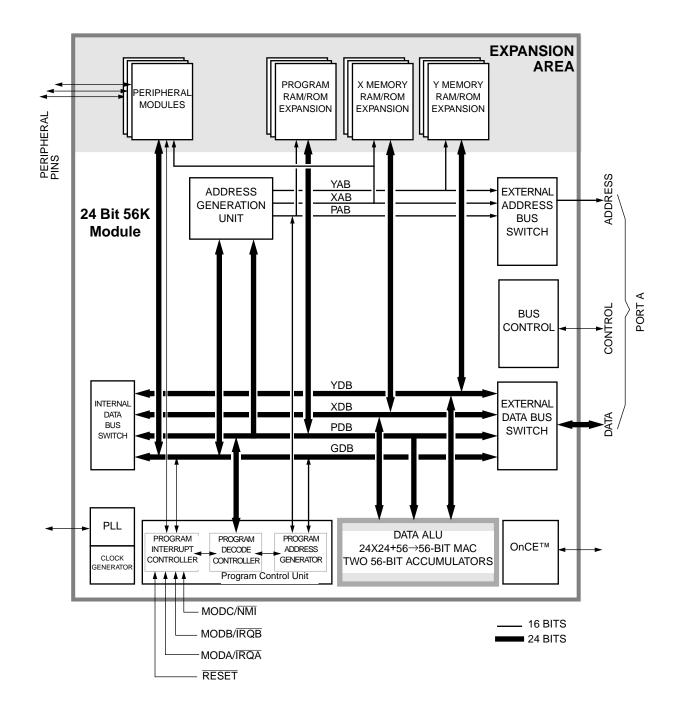

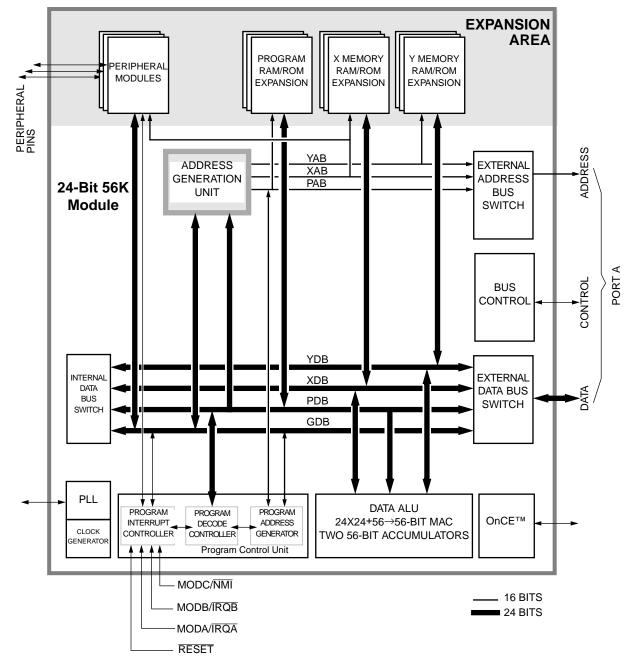

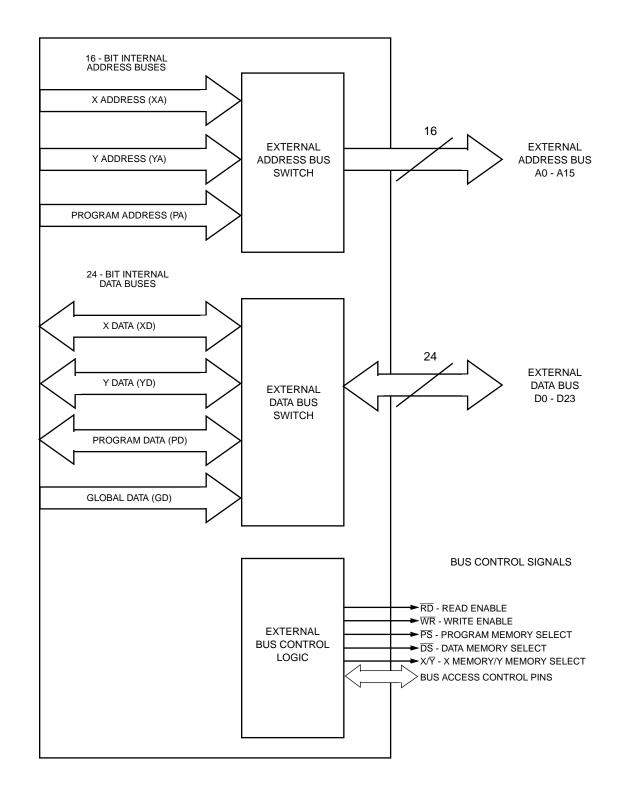

Figure 2-1 shows a block diagram of a typical DSP56K family processor, including the central processing module and a nonspecific expansion area for memory and peripherals. The following paragraphs give brief descriptions of each of the central components. Each of the components is explained in detail in subsequent chapters.

#### 2.2 DATA BUSES

The DSP56K central processing module is organized around the registers of three independent execution units: the PCU, the AGU, and the data ALU. Data movement between the execution units occurs over four bidirectional 24-bit buses: the X data bus (XDB), the Y data bus (YDB), the program data bus (PDB), and the global data bus (GDB). (Certain instructions treat the X and Y data buses as one 48-bit data bus by concatenating them.) Data transfers between the data ALU and the X data memory or Y data memory occur over XDB and YDB, respectively. XDB and YDB are kept local on the chip to maximize speed and minimize power dissipation. All other data transfers, such as I/O transfers with peripherals, occur over the GDB. Instruction word prefetches occur in parallel over the PDB.

The bus structure supports general register-to-register, register-to-memory, and memoryto-register data movement. It can transfer up to two 24-bit words and one 56-bit word in the same instruction cycle. Transfers between buses occur in the internal bus switch.

#### Freescale Semiconductor, Inc. ADDRESS BUSES

Figure 2-1 DSP56K Block Diagram

#### 2.3 ADDRESS BUSES

Addresses are specified for internal X data memory and Y data memory on two unidirectional 16-bit buses — X address bus (XAB) and Y address bus (YAB). Program memory addresses are specified on the bidirectional program address bus (PAB). External mem-

2-4

DSP56K CENTRAL ARCHITECTURE OVERVIEW For More Information On This Product, Go to: www.freescale.com ory spaces are addressed over a single 16-bit unidirectional address bus driven by a three-input multiplexer that can select the XAB, the YAB, or the PAB. Only one external memory access can be made in an instruction cycle. There is no speed penalty if only one external memory space is accessed in an instruction cycle. However, if two or three external memory spaces are accessed in a single instruction, there will be a one or two instruction cycle execution delay, respectively.

A bus arbitrator controls external access.

#### 2.3.1 Internal Bus Switch

Transfers between buses occur in the internal bus switch. The internal bus switch, which is similar to a switch matrix, can connect any two internal buses without adding any pipeline delays. This flexibility simplifies programming.

#### 2.3.2 Bit Manipulation Unit

The bit manipulation unit is physically located in the internal bus switch block because the internal data bus switch can access each memory space. The bit manipulation unit performs bit manipulation operations on memory locations, address registers, control registers, and data registers over the XDB, YDB, and GDB.

#### 2.4 DATA ALU

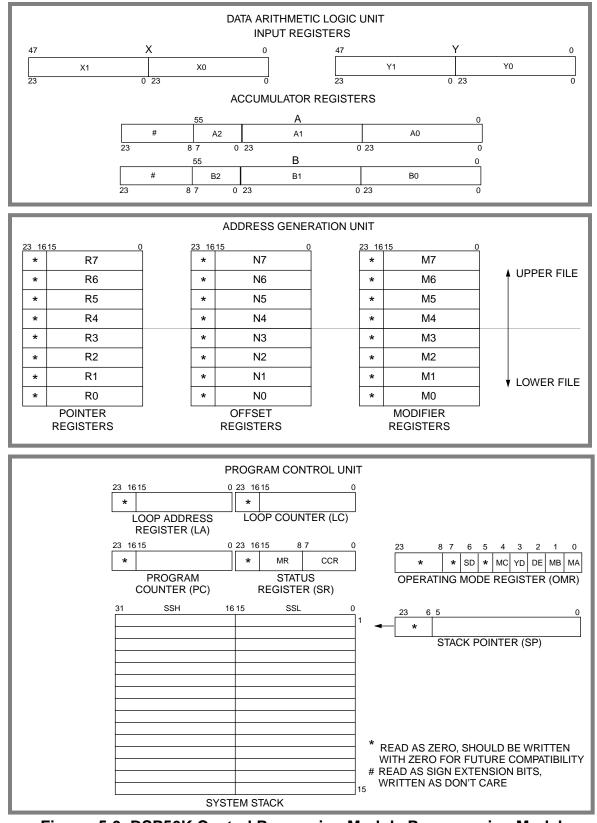

The data ALU performs all of the arithmetic and logical operations on data operands. It consists of four 24-bit input registers, two 48-bit accumulator registers, two 8-bit accumulator extension registers, an accumulator shifter, two data bus shifter/limiter circuits, and a parallel, single-cycle, nonpipelined Multiply-Accumulator (MAC) unit.

#### 2.5 ADDRESS GENERATION UNIT

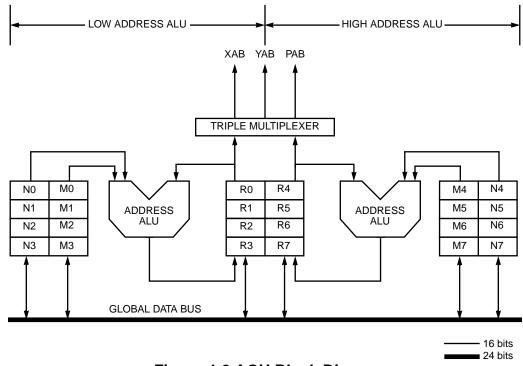

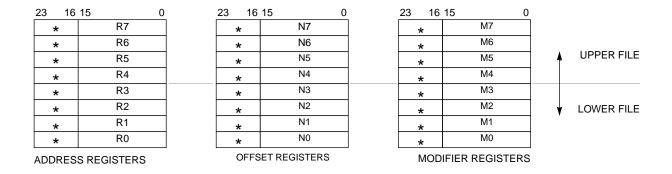

The AGU performs all of the address storage and address calculations necessary to indirectly address data operands in memory. It operates in parallel with other chip resources to minimize address generation overhead. The AGU has two identical address arithmetic units that can generate two 16-bit addresses every instruction cycle. Each of the arithmetic units can perform three types of arithmetic: linear, modulo, and reverse-carry.

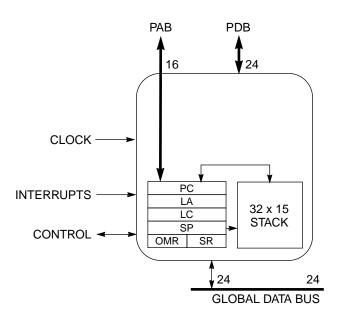

#### 2.6 PROGRAM CONTROL UNIT

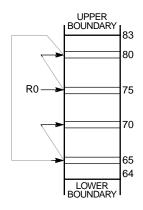

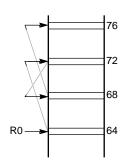

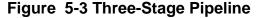

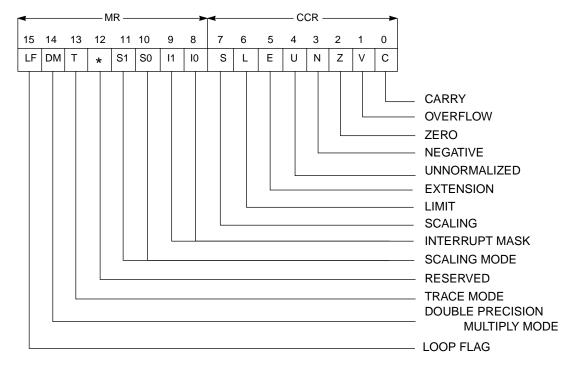

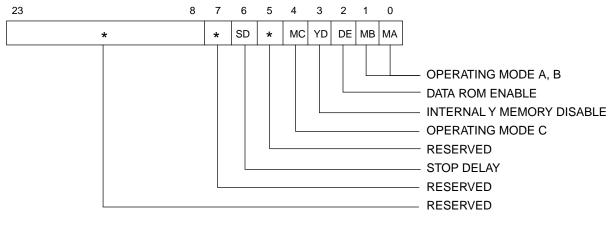

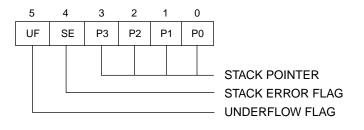

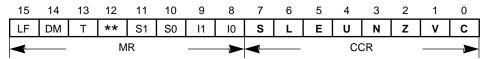

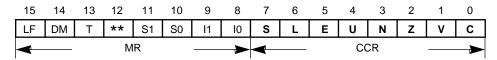

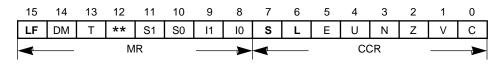

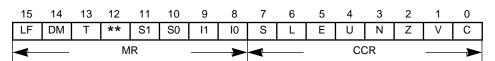

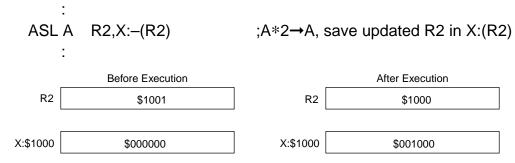

The program control unit performs instruction prefetch, instruction decoding, hardware DO loop control, and interrupt (or exception) processing. It consists of three components: the program address generator, the program decode controller, and the program interrupt controller. It contains a 15-level by 32-bit system stack memory and the following six di-

rectly addressable registers: the program counter (PC), loop address (LA), loop counter (LC), status register (SR), operating mode register (OMR), and stack pointer (SP). The 16-bit PC can address 65,536 locations in program memory space.

There are four mode and interrupt control pins that provide input to the program interrupt controller. The Mode Select A/External Interrupt Request A(MODA/IRQA) and Mode Select B/External Interrupt Request B (MODB/IRQB) pins select the chip operating mode and receive interrupt requests from external sources.

The Mode Select C/Non-Maskable Interrupt (MODC/NMI) pin provides further operating mode options and non-maskable interrupt input.

The RESET pin resets the chip. When it is asserted, it initializes the chip and places it in the reset state. When it is deasserted, the chip assumes the operating mode indicated by the MODA, MODB, and MODC pins.

#### 2.7 MEMORY EXPANSION PORT (PORT A)

Port A synchronously interfaces with a wide variety of memory and peripheral devices over a common 24-bit data bus. These devices include high-speed static RAMs, slower memory devices, and other DSPs and MPUs in master/slave configurations. This variety is possible because the expansion bus timing is programmable and can be tailored to match the speed requirements of the different memory spaces. Not all DSP56K family members feature a memory expansion port. See the individual device's User's Manual to determine if a particular chip includes this feature.

### 2.8 ON-CHIP EMULATOR (OnCE)

DSP56K on-chip emulation (OnCE) circuitry allows the user to interact with the DSP56K and its peripherals non-intrusively to examine registers, memory, or on-chip peripherals. It provides simple, inexpensive, and speed independent access to the internal registers for sophisticated debugging and economical system development.

Dedicated OnCE pins allow the user to insert the DSP into its target system and retain debug control without sacrificing other user accessible on-chip resources. The design eliminates the costly cabling and the access to processor pins required by traditional emulator systems.

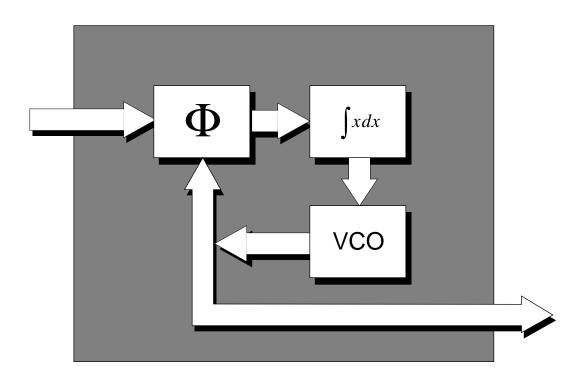

### 2.9 PHASE-LOCKED LOOP (PLL) BASED CLOCKING

The PLL allows the DSP to use almost any available external system clock for full-speed operation, while also supplying an output clock synchronized to a synthesized internal clock. The PLL performs frequency multiplication, skew elimination, and low-power division.

DSP56K CENTRAL ARCHITECTURE OVERVIEW For More Information On This Product, Go to: www.freescale.com

MOTOROLA

#### Downloaded from $\underline{Elcodis.com}$ electronic components distributor

**Freescale Semiconductor, Inc.**

# **SECTION CONTENTS**

| SECTION 3.1 DATA ARITHMETIC LOGIC UNIT                                      | 3  |

|-----------------------------------------------------------------------------|----|

| SECTION 3.2 OVERVIEW AND DATA ALU ARCHITECTURE                              |    |

| 3.2.1 Data ALU Input Registers (X1, X0, Y1, Y0)<br>3.2.2 MAC and Logic Unit |    |

| 3.2.3 Data ALU A and B Accumulators                                         | 7  |

| 3.2.4 Accumulator Shifter<br>3.2.5 Data Shifter/Limiter                     |    |

| 3.2.5.1 Limiting (Saturation Arithmetic)<br>3.2.5.2 Scaling                 |    |

| SECTION 3.3 DATA REPRESENTATION AND ROUNDING                                | 10 |

| SECTION 3.4 DOUBLE PRECISION MULTIPLY MODE                                  | 16 |

| SECTION 3.5 DATA ALU PROGRAMMING MODEL                                      | 19 |

| SECTION 3.6 DATA ALU SUMMARY                                                | 19 |

#### 3.1 DATA ARITHMETIC LOGIC UNIT

This section describes the operation of the Data ALU registers and hardware. It discusses data representation, rounding, and saturation arithmetic used within the Data ALU, and concludes with a discussion of the programming model.

#### 3.2 OVERVIEW AND DATA ALU ARCHITECTURE

As described in Section 2, The DSP56K family central processing module is composed of three execution units that operate in parallel. They are the Data ALU, address generation unit (AGU), and the program control unit (PCU) (see Figure 3-1). These three units are register oriented rather than bus oriented and interface over the system buses with memory and memory-mapped I/O devices.

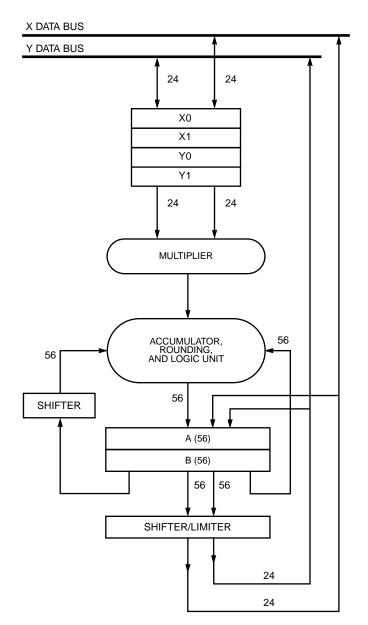

The Data ALU (see Figure 3-2) is the first of these execution units to be presented. It balances speed with the capability to process signals that have a wide dynamic range and performs all arithmetic and logical operations on data operands.

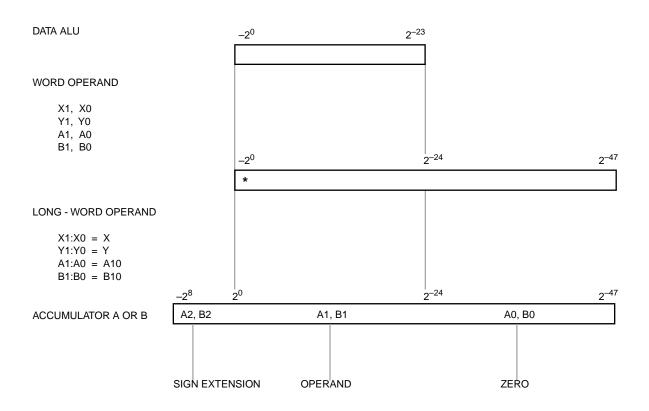

The Data ALU registers may be read or written over the XDB and the YDB as 24- or 48bit operands. The source operands for the Data ALU, which may be 24, 48, or 56 bits, always originate from Data ALU registers. The results of all Data ALU operations are stored in an accumulator.

The 24-bit data words provide 144 dB of dynamic range. This range is sufficient for most real-world applications since the majority of data converters are 16 bits or less – and certainly not greater than 24 bits. The 56-bit accumulator inside the Data ALU provides 336 dB of internal dynamic range so that no loss of precision will occur due to intermediate processing. Special circuitry handles data overflows and roundoff errors.

The Data ALU can perform any of the following operations in a single instruction cycle: multiplication, multiply-accumulate with positive or negative accumulation, convergent rounding, multiply-accumulate with positive or negative accumulation and convergent rounding, addition, subtraction, a divide iteration, a normalization iteration, shifting, and logical operations.

The components of the Data ALU are:

- Four 24-bit input registers

- A parallel, single-cycle, nonpipelined multiply-accumulator/logic unit (MAC)

- Two 48-bit accumulator registers

- Two 8-bit accumulator extension registers

- An accumulator shifter

- Two data bus shifter/limiter circuits

MOTOROLA

DATA ARITHMETIC LOGIC UNIT For More Information On This Product Go to: www.freescale.com

#### **Freescale Semiconductor, Inc.** OVERVIEW AND DATA ALU ARCHITECTURE

#### Figure 3-1 DSP56K Block Diagram

The following paragraphs describe each of these components and provide a description of data representation, rounding, and saturation arithmetic.

DATA ARITHMETIC LOGIC UNIT For More Information On This Product,

Go to: www.freescale.com

**MOTOROLA**

3 - 4

Semiconductor, Inc.

Freescale

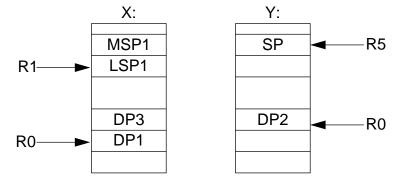

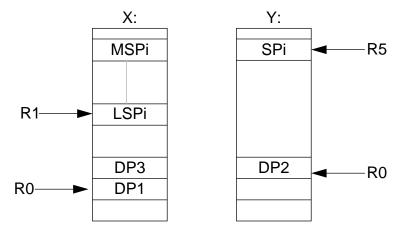

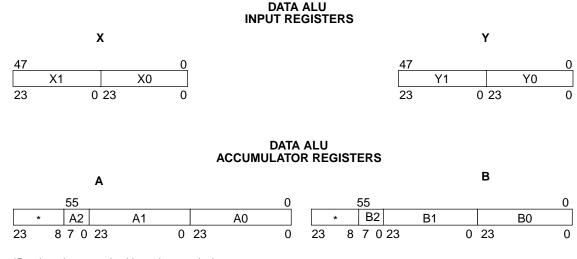

#### 3.2.1 Data ALU Input Registers (X1, X0, Y1, Y0)

X1, X0, Y1, and Y0 are four 24-bit, general-purpose data registers. They can be treated as four independent, 24-bit registers or as two 48-bit registers called X and Y, developed by concatenating X1:X0 and Y1:Y0, respectively. X1 is the most significant word in X and Y1 is the most significant word in Y. The registers serve as input buffer registers between the XDB or YDB and the MAC unit. They act as Data ALU source operands and allow new operands to be loaded for the next instruction while the current instruction uses the

Figure 3-2 Data ALU

```

MOTOROLA

```

DATA ARITHMETIC LOGIC UNIT For More Information On This Product, Go to: www.freescale.com register contents. The registers may also be read back out to the appropriate data bus to implement memory-delay operations and save/restore operations for interrupt service routines.

#### 3.2.2 MAC and Logic Unit

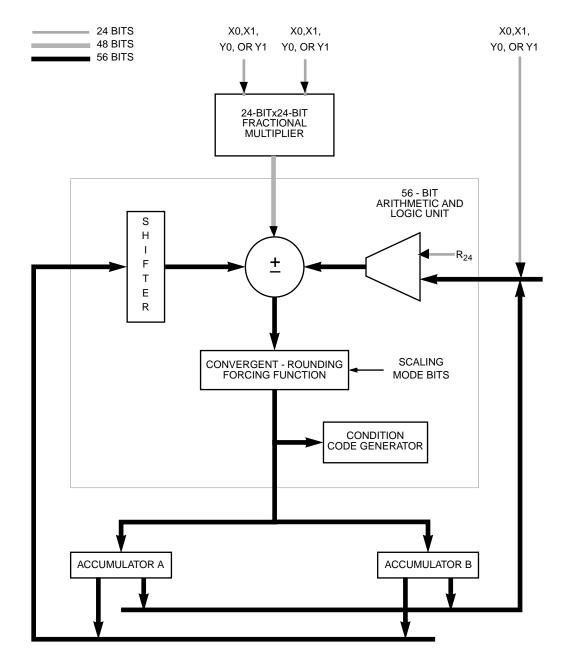

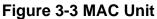

The MAC and logic unit shown in Figure 3-3 conduct the main arithmetic processing and perform all calculations on data operands in the DSP.

For arithmetic instructions, the unit accepts up to three input operands and outputs one 56-bit result in the following form: extension:most significant product:least significant product (EXT:MSP:LSP). The operation of the MAC unit occurs independently and in parallel with XDB and YDB activity, and its registers facilitate buffering for Data ALU inputs and outputs. Latches on the MAC unit input permit writing an input register which is the source for a Data ALU operation in the same instruction.

The arithmetic unit contains a multiplier and two accumulators. The input to the multiplier can only come from the X or Y registers (X1, X0, Y1, Y0). The multiplier executes 24-bit x 24-bit, parallel, twos-complement fractional multiplies. The 48-bit product is right justified and added to the 56-bit contents of either the A or B accumulator. The 56-bit sum is stored back in the same accumulator (see Figure 3-3). An 8-bit adder, which acts as an extension accumulator for the MAC array, accommodates overflow of up to 256 and allows the two 56-bit accumulators to be added to and subtracted from each other. The extension adder output is the EXT portion of the MAC unit output. This multiply/accumulate operation is not pipelined, but is a single-cycle operation. If the instruction specifies a multiply without accumulation (MPY), the MAC clears the accumulator and then adds the contents to the product.

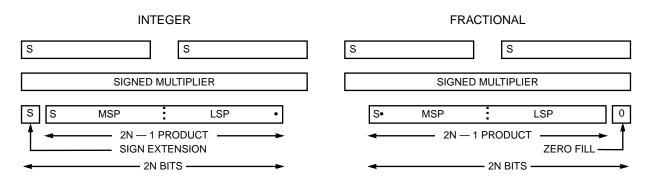

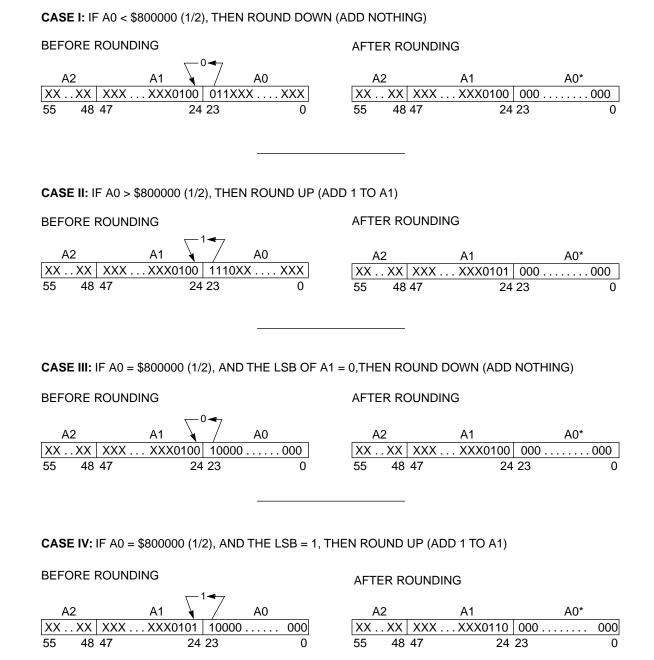

In summary, the results of all arithmetic instructions are valid (sign-extended and zerofilled) 56-bit operands in the form of EXT:MSP:LSP (A2:A1:A0 or B2:B1:B0). When a 56bit result is to be stored as a 24-bit operand, the LSP can be simply truncated, or it can be rounded (using convergent rounding) into the MSP.

Convergent rounding (round-to-nearest) is performed when the instruction (for example, the signed multiply-accumulate and round (MACR) instruction) specifies adding the multiplier's product to the contents of the accumulator. The scaling mode bits in the status register specify which bit in the accumulator shall be rounded.

The logic unit performs the logical operations AND, OR, EOR, and NOT on Data ALU registers. It is 24 bits wide and operates on data in the MSP portion of the accumulator. The LSP and EXT portions of the accumulator are not affected.

3 - 6

### **Freescale Semiconductor, Inc.** OVERVIEW AND DATA ALU ARCHITECTURE

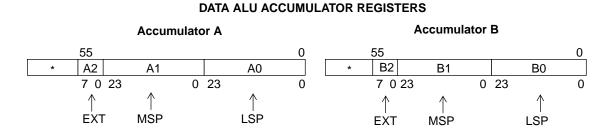

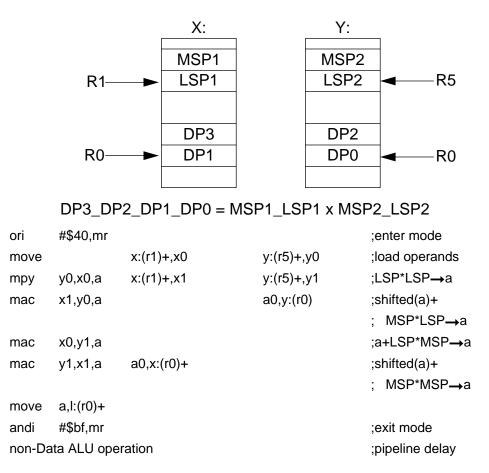

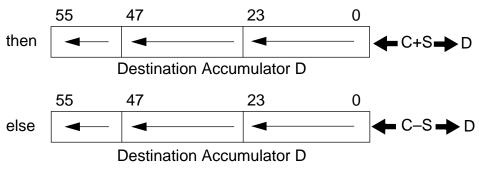

### 3.2.3 Data ALU A and B Accumulators

The Data ALU features two general-purpose, 56-bit accumulators, A and B. Each consists of three concatenated registers (A2:A1:A0 and B2:B1:B0, respectively). The 8-bit sign extension (EXT) is stored in A2 or B2 and is used when more than 48-bit accuracy is needed; the 24-bit most significant product (MSP) is stored in A1 or B1; the 24-bit least

MOTOROLA

Freescale Semiconductor, Inc.

#### DATA ARITHMETIC LOGIC UNIT For More Information On This Product, Go to: www.freescale.com

\*Read as sign extension bits, written as don't care.

### Figure 3-4 DATA ALU Accumulator Registers

significant product (LSP) is stored in A0 or B0 as shown in Figure 3-4.

Overflow occurs when a source operand requires more bits for accurate representation than are available in the destination. The 8-bit extension registers offer protection against overflow. In the DSP56K chip family, the extreme values that a word operand can assume are - 1 and + 0.9999998. If the sum of two numbers is less than - 1 or greater than + 0.9999998, the result (which cannot be represented in a 24 bit word operand) has underflowed or overflowed. The 8-bit extension registers can accurately represent the result of 255 overflows or 255 underflows. Whenever the accumulator extension registers are in use, the V bit in the status register is set.

Automatic sign extension occurs when the 56-bit accumulator is written with a smaller operand of 48 or 24 bits. A 24-bit operand is written to the MSP (A1 or B1) portion of the accumulator, the LSP (A0 or B0) portion is zero filled, and the EXT (A2 or B2) portion is sign extended from MSP. A 48-bit operand is written into the MSP:LSP portion (A1:A0 or B1:B0) of the accumulator, and the EXT portion is sign extended from MSP. No sign extension occurs if an individual 24-bit register is written (A1, A0, B1, or B0). When either A or B is read, it may be optionally scaled one bit left or one bit right for block floating-point arithmetic. Sign extension can also occur when writing A or B from the XDB and/or YDB or with the results of certain Data ALU operations (such as the transfer conditionally (Tcc) or transfer Data ALU register (TFR) instructions).

Overflow protection occurs when the contents of A or B are transferred over the XDB and YDB by substituting a limiting constant for the data. Limiting does not affect the content of A or B – only the value transferred over the XDB or YDB is limited. This overflow protection occurs after the contents of the accumulator has been shifted according to the scaling mode. Shifting and limiting occur only when the entire 56-bit A or B accumulator is specified as the source for a parallel data move over the XDB or YDB. When individual registers A0, A1, A2, B0, B1, or B2 are specified as the source for a parallel data move,

shifting and limiting are not performed.

### 3.2.4 Accumulator Shifter

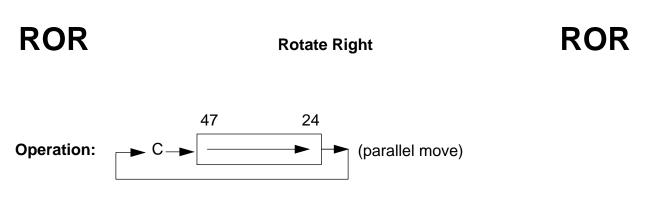

The accumulator shifter (see Figure 3-3) is an asynchronous parallel shifter with a 56-bit input and a 56-bit output that is implemented immediately before the MAC accumulator input. The source accumulator shifting operations are as follows:

- No Shift (Unmodified)

- 1-Bit Left Shift (Arithmetic or Logical) ASL, LSL, ROL

- 1-Bit Right Shift (Arithmetic or Logical) ASR, LSR, ROR

- Force to zero

# 3.2.5 Data Shifter/Limiter

The data shifter/limiter circuits (see Figure 3-3) provide special post-processing on data read from the Data ALU A and B accumulators out to the XDB or YDB. There are two independent shifter/limiter circuits (one for XDB and one for the YDB); each consists of a shifter followed by a limiting circuit.

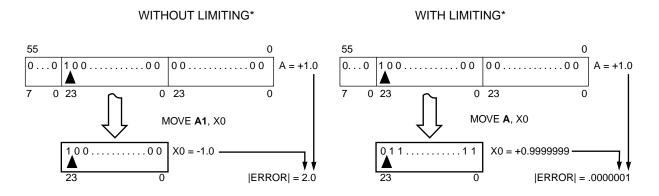

# 3.2.5.1 Limiting (Saturation Arithmetic)

The A and B accumulators serve as buffer registers between the MAC unit and the XDB and/or YDB. They act both as Data ALU source and destination operands. Test logic exists in each accumulator register to support the operation of the data shifter/limiter circuits. This test logic detects overflows out of the data shifter so that the limiter can substitute one of several constants to minimize errors due to the overflow. This process is called saturation arithmetic

The Data ALU A and B accumulators have eight extension bits. Limiting occurs when the extension bits are in use and either A or B is the source being read over XDB or YDB. If the contents of the selected source accumulator can be represented without overflow in the destination operand size (i.e., accumulator extension register not in use), the data limiter is disabled, and the operand is not modified. If contents of the selected source accumulator cannot be represented without overflow in the destination operand size, the data limiter will substitute a limited data value with maximum magnitude (saturated) and with the same sign as the source accumulator contents: \$7FFFF for 24-bit or \$7FFFFF FFFF for 48-bit positive numbers, \$800000 for 24-bit or \$800000 000000 for 48-bit negative numbers. This process is called saturation arithmetic. The value in the accumulator register is not shifted and can be reused within the Data ALU. When limiting does occur, a flag is set and latched in the status register. Two limiters allow two-word operands to be limited independently in the same instruction cycle. The two data limiters can also be com-

\* Limiting automatically occurs when the 56 - bit operands A or B (not A2, A1, A0, B2, B1, or B0) are read. The contents of A or B are **NOT** changed.

### **Figure 3-5 Saturation Arithmetic**

bined to form one 48-bit data limiter for long-word operands.

For example, if the source operand were 01.100 (+ 1.5 decimal) and the destination register were only four bits, the destination register would contain 1.100 (- 1.5 decimal) after the transfer, assuming signed fractional arithmetic. This is clearly in error as overflow has occurred. To minimize the error due to overflow, it is preferable to write the maximum ("limited") value the destination can assume. In the example, the limited value would be 0.111 (+ 0.875 decimal), which is clearly closer to + 1.5 than - 1.5 and therefore introduces less error.

Figure 3-5 shows the effects of saturation arithmetic on a move from register A1 to register X0. The instruction "MOVE A1,X0" causes a move without limiting, and the instruction "MOVE A,X0" causes a move of the same 24 bits with limiting. The error without limiting is 2.0; whereas, it is 0.0000001 with limiting. Table 3-1 shows a more complete set of limiting situations.

### 3.2.5.2 Scaling

The data shifters can shift data one bit to the left or one bit to the right, or pass the data unshifted. Each data shifter has a 24-bit output with overflow indication and is controlled by the scaling mode bits in the status register. These shifters permit dynamic scaling of fixed-point data without modifying the program code. For example, this permits block floating-point algorithms such as fast Fourier transforms to be implemented in a regular fashion.

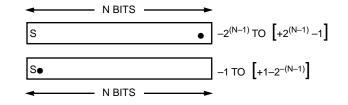

### 3.3 DATA REPRESENTATION AND ROUNDING

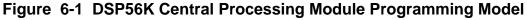

The DSP56K uses a fractional data representation for all Data ALU operations. Figure 3-

3 - 10

| Destination      | Source  | Accumulator | Limited Value | Type of |            |  |

|------------------|---------|-------------|---------------|---------|------------|--|

| Memory Reference | Operand | Sign        | XDB           | YDB     | Access     |  |

| X                | X:A     | +           | 7FFFFF        |         | One 24 bit |  |

| ^                | X:B     | -           | 800000        | —       | One 24 bit |  |

| Y                | Y:A     | +           | _             | 7FFFF   | 00411      |  |

| T T              | Y:B     | -           | —             | 800000  | One 24 bit |  |

|                  | X:A Y:A | +           | 7FFFF         | 7FFFF   |            |  |

|                  | X:A Y:B | -           | 800000        | 800000  |            |  |

| X and Y          | X:BY:A  | +           | 7FFFFF        | 7FFFF   | Two 24 bit |  |

|                  | X:BY:B  | -           | 800000        | 800000  | 100 24 01  |  |

|                  | L:AB    | +           | 7FFFFF        | 7FFFF   |            |  |

|                  | L:BA    | -           | 800000        | 800000  |            |  |

|                  | L:A     | +           | 7FFFF         | FFFFF   | One 19 hit |  |

| L (X:Y)          | L:B     | -           | 800000        | 000000  | One 48 bit |  |

### Table 3-1 Limited Data Values

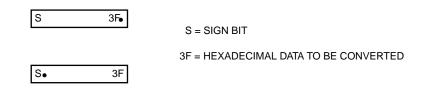

7 shows the bit weighting of words, long words, and accumulator operands for this representation. The decimal points are all aligned and are left justified.

Data must be converted to a fractional number by scaling before being used by the DSP or the user will have to be very careful in how the DSP manipulates the data. Moving \$3F to a 24-bit Data ALU register does not result in the contents being \$00003F as might be expected. Assuming numbers are fractional, the DSP left justifies rather than right justifies. As a result, storing \$3F in a 24-bit register results in the contents being \$3F0000. The simplest example of scaling is to convert all integer numbers to fractional numbers by shifting the decimal 24 places to the left (see Figure 3-6). Thus, the data has not changed; only the position of the decimal has moved.

# Figure 3-6 Integer-to-Fractional Data Conversion

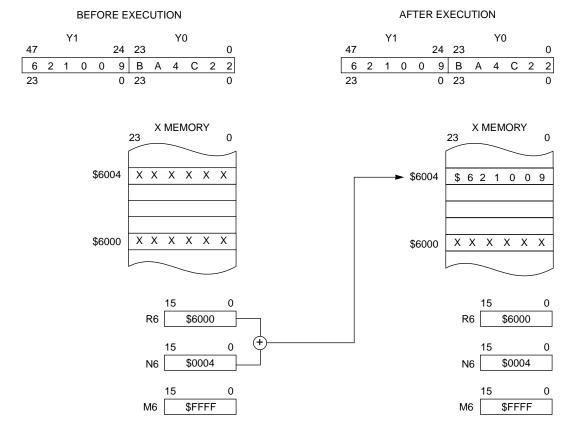

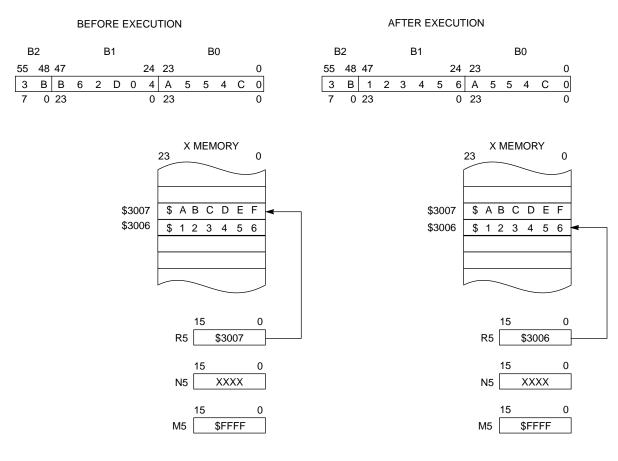

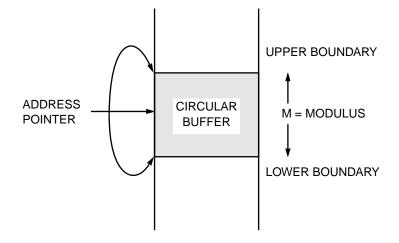

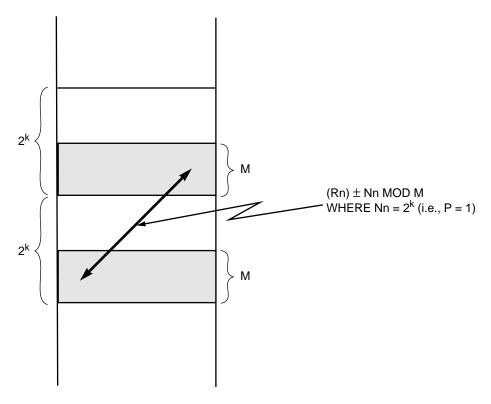

MOTOROLA