# 10-Bit Current-Output D/A Converter

**DAC-100**

### **FEATURES**

- Fast Settling ...... 225nsec (8 Bits), 375nsec (10 Bits)

- Stable . . . . . . . . . . . Tempcos to ±15ppm/° C Max

- Commercial, Industrial and Military Models Available

- TTL Compatible Logic Inputs

- Wide Supply Range ..... ±6V to ±18V

- Available in Die Form

The small size, wide operating temperature range, and high reliability construction make the DAC-100 ideal for aerospace applications. Other applications include use in servo-positioning systems, X-Y plotters, CRT displays, programmable power supplies, analog meter movement drivers, waveform generators and high speed analog-to-digital converters.

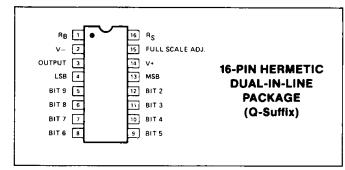

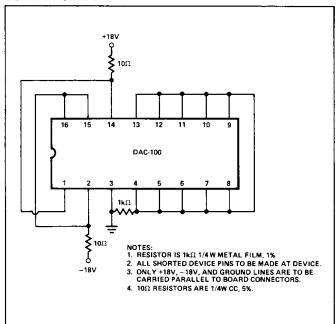

### **PIN CONNECTIONS**

### **GENERAL DESCRIPTION**

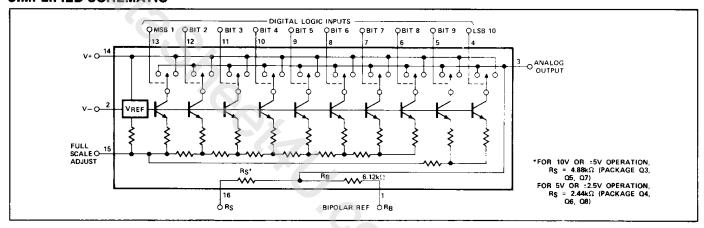

The DAC-100 is a complete 10-bit resolution digital-to-analog converter constructed on two monolithic chips in a single 16-pin DIP. Featuring excellent linearity vs. temperature performance, the DAC-100 includes a low tempco voltage reference, ten current source/switches and a high stability thin-film R-2R ladder network. Maximum application flexibility is provided by the fast current output, matched bipolar offset and feedback resistors. Resistors are included for use with an external op amp for voltage output applications.

Although all units have 10-bit resolution, a wide choice of linearity and temperature coefficient options are provided to allow price/performance optimization.

### ORDERING INFORMATION 1

| N.L.*<br>%FS | TEMPCO* | MILITARY TEMPERATURE |                                     | INDUSTRIAL T       | TEMPERATURE           | COMMERCIAL TEMPERATUR |                       |  |

|--------------|---------|----------------------|-------------------------------------|--------------------|-----------------------|-----------------------|-----------------------|--|

| MAX          | MAX     | $V_0 = \pm 5V/10V$   | $V_0 = \pm 2.5 \text{V}/5 \text{V}$ | $V_0 = \pm 5V/10V$ | $V_0 = \pm 2.5 V/5 V$ | $V_0 = \pm 5V/10V$    | $V_0 = \pm 2.5 V/5 V$ |  |

| ±0.05        | ±60     | DAC100ACQ5/883       | DAC100ACQ6/883                      | DAC100ACQ7         | DAC100ACQ8            | DAC100ACQ3            | DAC100ACQ4            |  |

| ±0.10        | ±30     | _                    | _                                   | DAC100BBQ7         | DAC100BBQ8            | _                     | _                     |  |

| ±0.10        | ±60     | DAC100BCQ5/883       |                                     | -                  | _                     | DAC100BCQ3            | DAC100BCQ4            |  |

| ±0.20        | ±60     | DAC100CCQ5/883       | DAC100CCQ6/883                      | DAC100CCQ7         | _                     | DAC100CCQ3            | DAC100CCQ4            |  |

| ±0.30        | ±120    | _                    | _                                   | _                  | _                     | DAC100DDQ3            | -                     |  |

Part number construction: The 1st letter following DAC-100 (A-D) refers to the nonlinearity specification; the 2nd letter (A-D) refers to the full-scale tempco; the letter Q refers to the package; and the end numeral indicates the output voltage and temperature.

### SIMPLIFIED SCHEMATIC

<sup>†</sup> Burn-in is available on commercial and industrial temperature range parts in CerDIP, plastic DIP, and TO-can packages.

# **DAC-100**

### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| V+ Supply to V- Supply             | 0 to +36V       |

|------------------------------------|-----------------|

| V+ Supply to Output                | 0 to +18V       |

| V- Supply to Output                | 0 to -18V       |

| Logic Inputs to Output             | 1V to +6V       |

| Operating Temperature Range Q3, Q4 | 0°C to +70°C    |

| Q5, Q6, Q7, Q8                     | -55°C to +125°C |

| Junction Temperature               | -25°C to +150°C |

| Storage Temperature Ra  | 65°C                     | to +150°C       |        |

|-------------------------|--------------------------|-----------------|--------|

| Lead Temperature (Solo  | dering, 60 sec)          |                 | +300°C |

| PACKAGE TYPE            | ⊖ <sub>jA</sub> (Note 2) | Θ <sub>jC</sub> | UNITS  |

| 16-Pin Hermetic DIP (Q) | 94                       | 12              | °C/W   |

| NOTES:                  |                          |                 |        |

<sup>1.</sup> Ratings apply to DICE and packaged parts, unless otherise noted.

**ELECTRICAL CHARACTERISTICS** at  $V_S = \pm 15V$ ,  $-25^{\circ}$  C  $\leq T_A \leq +85^{\circ}$  C for Q7 and Q8 devices;  $0^{\circ}$  C  $\leq T_A \leq +70^{\circ}$  C for Q3 and Q4;  $-55^{\circ}$  C  $\leq T_A \leq +125^{\circ}$  C for Q5 and Q6 devices, unless otherwise noted.

| PARAMETER                           | SYMBOL           | CONDITIONS                             | DAC-100        | MIN | TYP | MAX   | UNITS      |

|-------------------------------------|------------------|----------------------------------------|----------------|-----|-----|-------|------------|

| Resolution                          |                  |                                        |                | 10  | _   | _     | Bits       |

| Nonlinearity                        |                  | (±1/2LSB — 10 bits)                    | A              | _   | _   | ±0.05 |            |

| (For nonlinearity/tempco            | NL               | (±1/2LSB — 9 bits)                     | В—             | -   | _   | ±0.1  | %FS        |

| combinations, see Ordering          | .42              | (±1/2LSB — 8 bits)                     | C—             | _   | _   | ±0.2  | /01 3      |

| Information)                        |                  | (±3/4LSB — 8 bits)                     | D—             |     | _   | ±0.3  |            |

| Full-Scale Tempco                   |                  |                                        | <b></b> B      | _   | _   | ±30   | ppm/°C     |

| (See Full-Scale Test Circuit)       | T <sub>C</sub>   |                                        | -c             | _   | _   | ±60   | FF         |

|                                     |                  |                                        | D              |     |     | ± 120 |            |

|                                     |                  | to ±0.05% FS                           | ALL            | _   |     | 375   |            |

|                                     |                  | to ±0.1% FS                            | ALL            | -   | _   | 300   |            |

| Settling Time T <sub>A</sub> = 25°C | ts               | to ±0.2% FS                            | ALL            | -   | _   | 225   | ns         |

|                                     |                  | to ±0.4% FS                            | ALL            | _   | _   | 150   |            |

|                                     |                  | to ±0.8% FS                            | ALL            |     |     | 100   |            |

| Full-Range Output Voltage           |                  | Connect FS Adjust to V-                |                |     |     |       |            |

| (Limits guarantee adjustability     |                  | 10V Models (Q3, Q5, Q7)                |                | 10  | _   | 11.1  |            |

| to exact 10.0 (5.0)V with a         | V <sub>FR</sub>  | (See Full-Scale Test Circuit)          |                |     |     |       | v          |

| 200Ω Trimpot® between               | тн               | 5V Models (Q4, Q6, Q8)                 |                |     |     |       | •          |

| Adjust and V-)                      |                  | $V_{iN} = 0.7V$                        |                | 5   | _   | 5.55  |            |

| ··- <b>/</b>                        |                  | (See Basic Unipolar Voltage Output     | Circuit:       |     |     |       |            |

| Zero-Scale Output Voltage           | V <sub>ZS</sub>  | V <sub>IN</sub> = 2.1V                 | ALL            | _   |     | 0.013 | %FS        |

| Logic Inputs: High                  | V <sub>INH</sub> | Measured with respect to<br>output pin | ALL            | 2.1 | _   | _     | v          |

| Logic Inputs: Low                   | V <sub>INL</sub> | Measured with respect to output pin    | ALL            | _   | _   | 0.7   | V          |

| Logic Input Current, Each Input     | I <sub>IN</sub>  | V <sub>IN</sub> = 0 to +6V             | ALL            | _   |     | 5     | μА         |

| Logic Input Resistance              | R <sub>IN</sub>  | V <sub>IN</sub> = 0 to +6V             | ALL            | _   | 3   |       | mΩ         |

| Logic Input Capacitance             | C <sub>IN</sub>  |                                        | ALL            |     | 2   | -     | pF         |

| Output Resistance                   | Ro               |                                        | ALL            | _   | 500 |       | kΩ         |

| Output Capacitance                  | co               |                                        | ALL            | -   | 13  |       | pF         |

| Applied Power Supplies: V+          | 7.00             |                                        | ALL            | +6  |     | +18   | V          |

| Applied Power Supplies: V-          |                  |                                        | ALL            | -6  | _   | -18   | V          |

| Power Supply Sensitivity            | P <sub>SS</sub>  | $V_S = \pm 6V \text{ to } \pm 18V$     | ALL            | _   |     | ±0.10 | % per Volt |

|                                     |                  | V <sub>S</sub> = ±15V                  | Q3, Q4         | _   | 200 | 300   |            |

| Power Consumption                   | $P_{D}$          | $V_S = \pm 6V$                         | Q3, Q4         | _   | 80  | _     | mW         |

|                                     | _                | $V_S = \pm 15V$                        | Q5, Q6, Q7, Q8 | _   | 200 | 250   |            |

|                                     |                  | V <sub>S</sub> = +15V                  | Q3, Q4         |     |     | 10    |            |

| Positive Supply Current             | 1+               | V <sub>S</sub> = +15V                  | Q5, Q6, Q7, Q8 | _   | _   | 8.33  | mA         |

|                                     |                  | V <sub>S</sub> = -15V                  | Q3, Q4         |     |     | -10   |            |

| Negative Supply Current             | ł-               | $V_S = -15V$<br>$V_S = -15V$           | Q5, Q6, Q7, Q8 | _   | _   | -8.33 | mA         |

### NOTE:

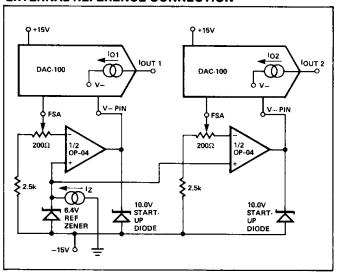

For applications where long-term stability is critical, an external voltage reference is recommended (see PMI REF-01/02).

Θ<sub>IA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>IA</sub> is specified for device in socket for CerDIP package.

### **DICE CHARACTERISTICS**

# DAR-01 RC R1 R2 R3 R4 R5 R6 R7 R8 15 16 13000 3 1977 © 2000 1 2 6 8

DIE SIZE  $.090 \times .064$  inch, 5760 sq. mils (2.286  $\times$  1.701 mm, 3.888 sq. mm)

- 1. R<sub>B</sub>

- 2. V-

- 3. OUTPUT

- 15. FULL-SCALE ADJ

- 16. R<sub>8</sub>

- R Pads are connected to similarly marked pads on DAI-01

Note: Pads 4 — 14, See DAI-01

**DAI-01**

DIE SIZE 0.080 x 0.067 inch, 5,360 sq. mils (2.032 x 1.702 mm, 3.458 sq. mm)

14. V+

- 2. V- 10. BIT 4

3. OUTPUT 11. BIT 3

4. BIT 10 (LSB) 12. BIT 2

5. BIT 9 13. BIT 1 (MSB)

- 6. BIT 8 7. BIT 7

- 8. BIT 6 9. BIT 5

- R Pads are connected to similarly marked pads on DAR-01

Note: Pads 1, 2, 15, 16, See DAR-01

These die versions are available on special order; contact your PMI sales office.

**WAFER TEST LIMITS** at  $T_A = 25^{\circ}$ C for the R-2R Ladder Network comprised of R1—R8, R12, R23, R34, R45 and R56 when connected to an ideal DAI-01, unless otherwise noted.

|              |            |     | DAR-01-N |        |     | DAR-01-G |       |       |

|--------------|------------|-----|----------|--------|-----|----------|-------|-------|

| PARAMETER    | CONDITIONS | MIN | TYP      | MAX    | MIN | TYP      | MAX   | UNITS |

| Nonlinearity | VR1 = 3.2V | _   | _        | ±0.035 | _   | _        | ±0.05 | %     |

### **WAFER TEST LIMITS** at $T_A = 25$ °C, VR1 = 3.2V, unless otherwise noted.

|                 |                      |      | DAR-0 | 1    |       |

|-----------------|----------------------|------|-------|------|-------|

| PARAMETER       | CONDITIONS           | MIN  | TYP   | MAX  | UNITS |

| Resistance R1   | Absolute Measurement | 2.56 |       | 3.84 | kΩ    |

| Ratio RC1 to R1 | Ideal = 1.00503 to 1 | -1   | _     | +1   | %     |

| Ratio R1 to RS1 | Ideal = 1.29959 to 1 | -1   | _     | +1   | %     |

| Ratio R1 to RS2 | Ideal = 1.29959 to 1 | -1   | _     | +1   | %     |

| Ratio RB to R1  | Ideal = 1.92211 to 1 |      |       | +1   | %     |

### NOTE:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

### TYPICAL ELECTRICAL CHARACTERISTICS in common to all grades.

|                                  | DAR-01                           |     |      |     |        |  |  |

|----------------------------------|----------------------------------|-----|------|-----|--------|--|--|

| PARAMETER                        | CONDITIONS                       | MIN | TYP  | MAX | UNITS  |  |  |

| Absolute Temperature Coefficient | All Resistors                    |     | ±180 |     | ppm/°C |  |  |

| Tracking Temperature Coefficient | All Resistors with Respect to R1 |     | 3    |     | ppm/°C |  |  |

### WAFER TEST LIMITS at T<sub>A</sub> = 25°C when connected to an ideal DAR-01, unless otherwise noted.

|                               |                  |                        |     | D   |       |     |     |       |       |

|-------------------------------|------------------|------------------------|-----|-----|-------|-----|-----|-------|-------|

| PARAMETER                     | SYMBOL           | CONDITIONS             | MIN | TYP | MAX   | MIN | TYP | MAX   | UNITS |

| Nonlinearity                  | NL               | V <sub>S</sub> = ± 15V |     | _   | ±0.05 |     | _   | ±0.1  | %     |

| internal Reference<br>Voltage | V <sub>MCR</sub> | $V_S = \pm 15V$        | 6.6 | _   | 6.900 | 6.6 | _   | 6.900 | V     |

### WAFER TEST LIMITS at $V_S = \pm 15V$ , $T_A = 25^{\circ}$ C when connected to an ideal DAR-01, unless otherwise noted.

|                           |                                          |              | DAI-01 |        |                     |

|---------------------------|------------------------------------------|--------------|--------|--------|---------------------|

| PARAMETER                 | CONDITIONS                               | MIN          | TYP    | MAX    | UNITS               |

| Resolution                |                                          | 10           | _      | 10     | Bits                |

| Analog Output Current     | All Bits Low, V- Connected to FS Adjust  | 1840         | _      | 2274   | μΑ                  |

| Zero-Scale Output Current | All Bits High, V- Connected to FS Adjust |              | _      | ±0.011 | %I <sub>FS</sub>    |

| Logic Input "0"           | Measured with Respect to Output          | <del>-</del> | _      | 0.7    | v                   |

| Logic Input "1"           | Measured with Respect to Output          | 2.1          | _      |        | ٧                   |

| Supply Current            | All Bits High, V- Connected to FS Adjust |              | -      | 8.33   | mA                  |

| Power Supply Rejection    | $V_S = \pm 6V \text{ to } \pm 18V$       | _            | _      | 0.1    | %I <sub>FS</sub> /V |

### NOTE:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

# TYPICAL ELECTRICAL CHARACTERISTICS at $V_S = \pm 15V$ , and when connected to an ideal DAR-01, unless otherwise noted.

|                                           |            | DAI-01-N |     | DAI-01-G |     |     |     |        |

|-------------------------------------------|------------|----------|-----|----------|-----|-----|-----|--------|

| PARAMETER                                 | CONDITIONS | MIN      | TYP | MAX      | MIN | TYP | MAX | UNITS  |

| Full-Scale Temperature Coefficient (Note) |            | _        | ±60 | _        | _   | ±60 | _   | ppm/°C |

### NOTE:

Full-Scale Temperature Coefficient is defined as the change in output voltage measured in the basic unipolar voltage output test circuit shown on the DAC-100 data sheet and is expressed in ppm between 25°C and either temperature extreme divided by the corresponding temperature change.

### **BASIC CONNECTIONS**

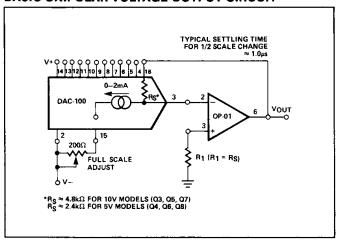

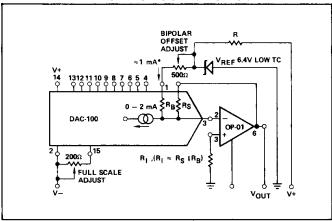

### **BASIC UNIPOLAR VOLTAGE OUTPUT CIRCUIT**

### **BASIC BIPOLAR VOLTAGE OUTPUT CIRCUIT**

### **APPLICATIONS INFORMATION**

FULL RANGE OUTPUT ADJUSTMENT — The output current of the DAC-100 may be reduced to produce an exact 10.000 (5.000) volt output by connecting a 200 $\Omega$  adjustable resistance between the full-scale adjust pin and V-. Adjustment should be made with an input of all "zeroes."

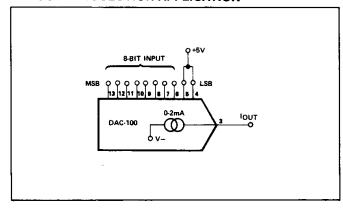

LOWER RESOLUTION APPLICATIONS — The DAC-100 may be used in applications requiring less than 10 bits of resolution. All unused logic inputs must be tied to logic high for proper operation. "Floating" logic inputs can cause improper operation.

### REDUCED RESOLUTION APPLICATION

LOGIC CODING — The DAC-100 uses complementary or inverted binary logic coding, i.e., an all "zeroes" input produces a full range output, while an all "ones" input produces a zero-scale output. Each lesser significant bit's weight is one-half the previous more significant bit's value. High logic input turns the bit "OFF," low logic input level turns the bit "ON".

**LOGIC COMPATIBILITY** — The input logic levels are directly compatible with TTL logic and may also be used with CMOS logic powered from a single +5 volt supply.

**NONLINEARITY (NL)** — The maximum deviation from an ideal straight line drawn between the end points, expressed as a percent of full-scale range (FSR) or given in terms of LSB value. The end points are zero-scale output to full-scale output for unipolar operation and minus full-scale to positive full-scale for bipolar operation.

**BIPOLAR OPERATION** — The DAC-100 may be converted to bipolar operation by injecting a half-scale current into the output; this is accomplished by connecting the internal bipolar resistor to a +6.4 volt reference. Trimming of the zero output may be facilitated by placing a  $500\Omega$  adjustable resistance in series with the +6.4 volts.

**VOLTAGE AT OUTPUT PIN** — The DAC-100 is designed to be operated with the voltage at the output pin held very close to zero volts. Input logic threshold levels are directly affected by output pin voltage changes; voltage swings at the output may cause loss of linearity due to improper switching of bits. Large voltage swings may cause permanent damage and should be avoided. Proper operation can be obtained with output voltages held within  $\pm 0.7$  volts; a pair of back-to-back silicon diodes tied from the output to ground is a convenient way of clamping the output to this limit.

## **DAC-100**

### **TYPICAL APPLICATIONS**

### **EXTERNAL REFERENCE CONNECTION**

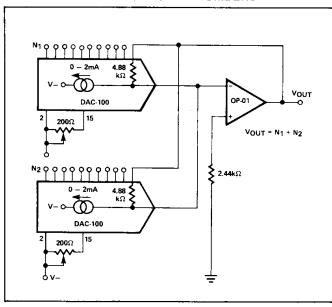

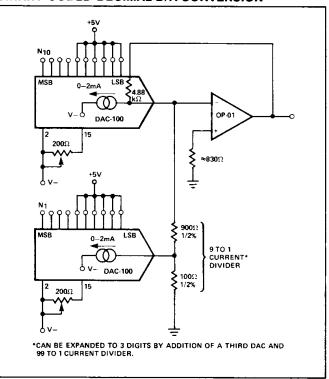

### **ANALOG SUM OF TWO DIGITAL NUMBERS**

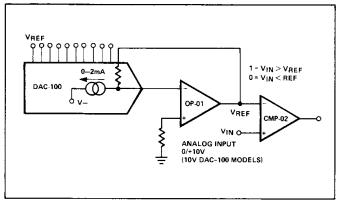

### **DIGITALLY PROGRAMMED LEVEL DETECTOR**

### **BINARY-CODED-DECIMAL D/A CONVERSION**

### INTERFACING WITH CMOS LOGIC

The DAC-100 requires only about  $1\mu A$  of input current into each logic stage. This enables use with CMOS inputs as long as one rule is observed; logic input voltages should not exceed 6.5 volts or V+, whichever is smaller. To provide an understanding of this rule, it is necessary to discuss the logic input stage design.

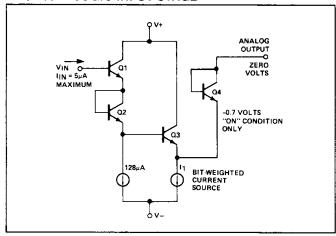

### **LOGIC INPUT STAGE DESIGN**

For simplicity, only one of the ten identical input circuits is shown below. The DAC-100 uses a fast current-steering technique that switches a bit-weighted current between the positive supply (V+) and the analog output, which is usually constrained to be at zero volts (virtual ground) by an external summing amplifier.

### **DAC-100 — LOGIC INPUT STAGE**

Switching is accomplished by forward biasing Q4, diodeconnected transistor, for the bit "ON" condition and back biasing Q4 in the "OFF" condition. For the "ON" condition  $(V_{IN} \leq 0.7 \text{ volts}), Q3$  is "OFF" — all of the bit-weighted current,  $I_1$ , flows from the analog output through Q4 and ultimately to V–. In the "OFF" condition  $(V_{IN} \geq 2.1 \text{ volts}), Q3$  is "ON", Q4 is back biased, and the bit-weighted current is sourced from the positive power supply instead of the analog output.

If  $V_{IN}$  is too high, Q4's emitter-base junction will experience reverse breakdown and a fault condition will occur. Equation 1 describes this condition:

1)

$$BV_{IH} = V_{BE1} + V_{BE2} + V_{BE3} + BV_{EB4} \approx 7.7 \text{ volts}$$

Using this relationship, it can be seen that a conservative input voltage limit would be around 6.5 volts. When the 6.5V input limit is observed, DAC-100 operation with CMOS inputs is easily achieved.

### ±6 VOLT POWER SUPPLY OPERATION

This is the most convenient method of interfacing the DAC-100 with CMOS logic. At  $\pm 6$  volts the DAC-100 power dissipation is only 80mW, which is very small considering the inclusion of a complete internal reference. No interfacing components are required with  $\pm 5\%$  power supplies, and the CMOS logic and DAC-100 can use the same +6 volt power supply. In this application the device is directly CMOS compatible.

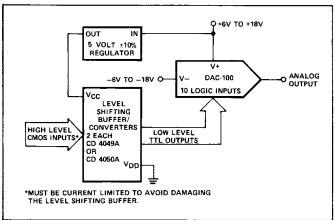

### **BLOCK DIAGRAM — CMOS TO DAC-100 INTERFACE**

### HIGH LEVEL CMOS INTERFACING

The block diagram below illustrates a convenient method for interfacing CMOS input levels between 6.5 volts and 15 volts with the DAC-100. Inexpensive and readily available CMOS hex buffer/converters step down the high-level inputs to TTL levels that cannot exceed 5 volts — clearly satisfying the input stage voltage rule.

In addition to level shifting, buffer/converters provide input coding flexibility since they are available as inverting (CD4049A) or non-inverting (CD4050A) devices. This gives the user a choice between negative-true and positive-true binary coding and allows the same basic DAC-100 to CMOS interfacing method to be used in either type of application.

Since buffer/converter power consumption is very low, the required +5 volts can be provided by a simple regulator or even a resistive divider in some applications. In a multi-DAC system, one central, inexpensive three-terminal IC regulator can supply several level shifting devices.

### NOTE:

For a more complete explanation and detailed circuit connections, refer to AN-14, "Interfacing PMI D/A's with CMOS Logic."

### **BURN-IN CIRCUIT**

# **DAC-100**

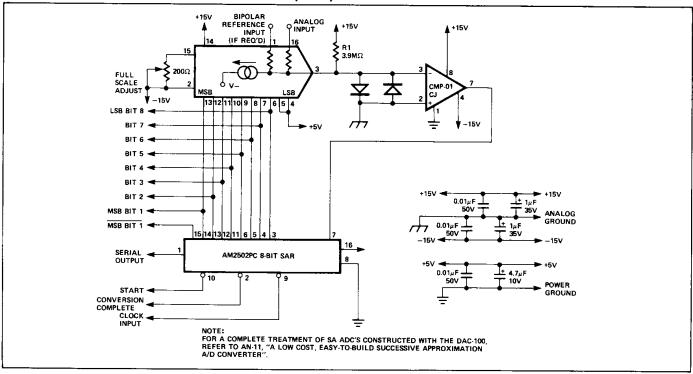

### SUCCESSIVE APPROXIMATION A/D CONVERTER (8-BIT)

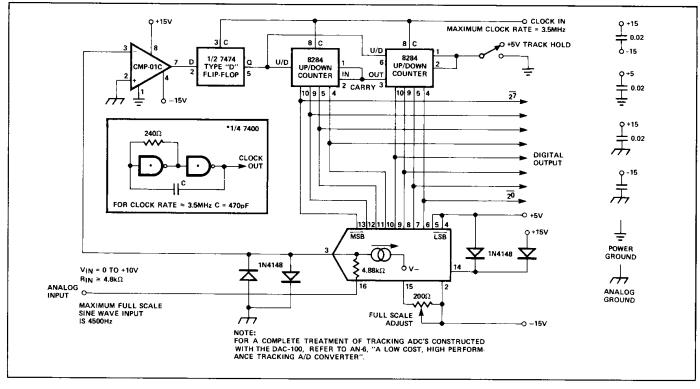

### TRACKING (SERVO-TYPE) A/D CONVERTER