# 34 MHz, CBFET Fast Settling Op Amp

## AD843

### FEATURES

AC PERFORMANCE Unity Gain Bandwidth: 34 MHz Fast Settling: 135 ns to 0.01% Slew Rate: 250 V/μs Stable at Gains of 1 or Greater Full Power Bandwidth: 3.9 MHz

### **DC PERFORMANCE**

Input Offset Voltage: 1 mV max (AD843K/B) Input Bias Current: 0.6 nA typ Input Voltage Noise: 19 nV/VHz Open Loop Gain: 30 V/mV into a 500  $\Omega$  Load **Output Current: 50 mA min** Supply Current: 13 mA max Available in 8-Pin Plastic Mini-DIP & Cerdip, 16-Pin SOIC, 20-Pin LCC and 12-Pin Hermetic Metal Can Packages Available in Tape and Reel in Accordance with **EIA-481A Standard** Chips and MIL-STD-883B Parts Also Available **APPLICATIONS High Speed Sample-and-Hold Amplifiers High Bandwidth Active Filters High Speed Integrators High Frequency Signal Conditioning**

### **PRODUCT DESCRIPTION**

The AD843 is a fast settling, 34 MHz, CBFET input op amp. The AD843 combines the low (0.6 nA) input bias currents characteristic of a FET input amplifier while still providing a 34 MHz bandwidth and a 135 ns settling time (to within 0.01% of final value for a 10 volt step). The AD843 is a member of the Analog Devices' family of wide bandwidth operational amplifiers. These devices are fabricated using Analog Devices' junction isolated complementary bipolar (CB) process. This process permits a combination of dc precision and wideband ac performance previously unobtainable in a monolithic op amp.

The 250 V/ $\mu$ s slew rate and 0.6 nA input bias current of the AD843 ensure excellent performance in high speed sample-and-hold applications and in high speed integrators. This amplifier is also ideally suited for high bandwidth active filters and high frequency signal conditioning circuits.

Unlike many high frequency amplifiers, the AD843 requires no external compensation and it remains stable over its full operating temperature range. It is available in five performance grades: the AD843J and AD843K are rated over the commercial temperature range of 0°C to +70°C. The AD843A and AD843B are rated over the industrial temperature range of -40°C to +85°C. The AD843S is rated over the military temperature range of -55°C to +125°C and is available processed to MIL-STD-883B, Rev. C.

### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

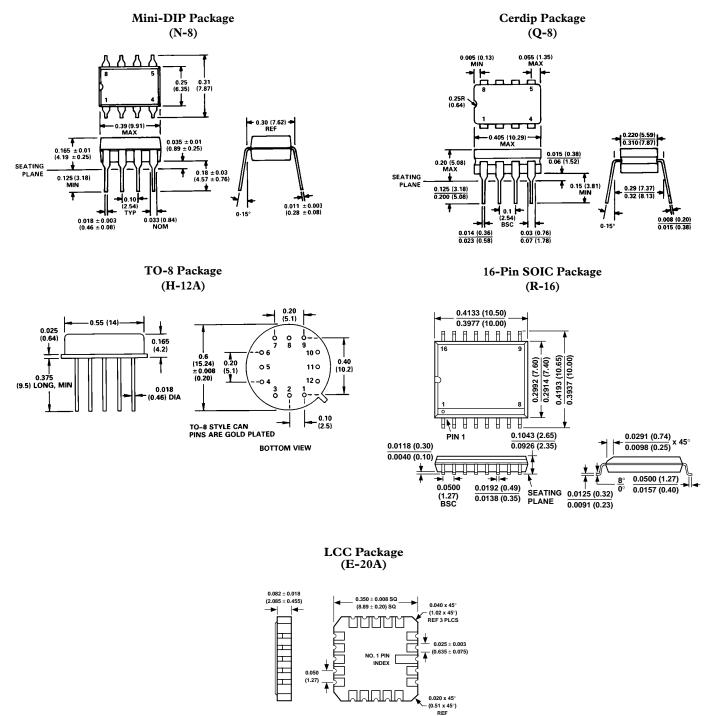

Plastic (N-8) and Cerdip (Q-8) Package

LCC (E-20A) Package

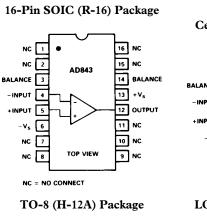

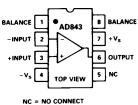

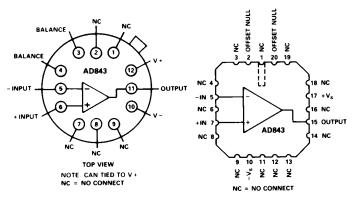

**CONNECTION DIAGRAMS**

The AD843 is offered in either 8-pin plastic DIP or hermetic cerdip packages, in 16-pin SOIC, 20-Pin LCC, or in a 12-pin metal can. Chips are also available.

### **PRODUCT HIGHLIGHTS**

- 1. The high slew rate, fast settling time and low input bias current of the AD843 make it the ideal amplifier for 12-bit D/A and A/D buffers, for high speed sample-and-hold amplifiers and for high speed integrator circuits. The AD843 can replace many FET input hybrid amplifiers such as the LH0032, LH4104 and OPA600.

- 2. Fully differential inputs provide outstanding performance in all standard high frequency op amp applications such as signal conditioning and active filters.

- 3. Laser wafer trimming reduces the input offset voltage to 1 mV max (AD843K and AD843B).

- 4. Although external offset nulling is unnecessary in many applications, offset null pins are provided.

- 5. The AD843 does not require external compensation at closed loop gains of 1 or greater.

© Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

#

| Model                                                                                                                                                    | Conditions                                                                                                                                                                                       | Min                                                                                    | AD843J/A<br>Typ                           | Max                    | Min                           | AD843K/E<br>Typ                           | 8<br>Max           | Min                                                                           | AD843S <sup>1</sup><br>Typ                | Max                | Units                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------|------------------------|-------------------------------|-------------------------------------------|--------------------|-------------------------------------------------------------------------------|-------------------------------------------|--------------------|-------------------------------------|

| INPUT OFFSET VOLTAGE <sup>1</sup><br>Offset Drift                                                                                                        | T <sub>MIN</sub> -T <sub>MAX</sub>                                                                                                                                                               |                                                                                        | 1.0<br>1.7<br>12                          | <b>2.0</b><br>4.0      |                               | 0.5<br>1.2<br>12                          | 1.0<br>2.0<br>35   |                                                                               | 1.0<br>3.0<br>12                          | 2.0<br>4.5         | mV<br>mV<br>μV/°C                   |

| INPUT BIAS CURRENT                                                                                                                                       | Initial (T <sub>J</sub> = +25°C)<br>Warmed-Up <sup>2</sup><br>T <sub>MIN</sub> -T <sub>MAX</sub>                                                                                                 |                                                                                        | 50<br>0.8                                 | <b>2.5</b> 60/160      |                               | 40<br>0.6                                 | 1.0<br>23/65       |                                                                               | 50<br>0.8                                 | <b>2.5</b> 2600    | pA<br>nA<br>nA                      |

| INPUT OFFSET CURRENT                                                                                                                                     | Initial ( $T_J = +25^{\circ}C$ )<br>Warmed-Up <sup>2</sup><br>$T_{MIN}$ - $T_{MAX}$                                                                                                              |                                                                                        | 30<br>0.25                                | <b>1.0</b><br>23/64    |                               | 20<br>0.2                                 | <b>0.4</b><br>9/26 |                                                                               | 30<br>0.25                                | <b>1.0</b><br>1025 | pA<br>nA<br>nA                      |

| INPUT CHARACTERISTICS<br>Input Resistance<br>Input Capacitance                                                                                           |                                                                                                                                                                                                  |                                                                                        | 10 <sup>10</sup><br>6                     |                        |                               | 10 <sup>10</sup><br>6                     |                    |                                                                               | 10 <sup>10</sup><br>6                     |                    | Ω<br>pF                             |

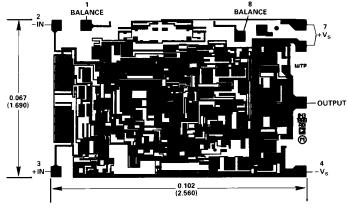

| INPUT VOLTAGE RANGE<br>Common Mode                                                                                                                       |                                                                                                                                                                                                  | ±10                                                                                    | +12,<br>-13                               |                        | ±10                           | +12,<br>-13                               |                    | ±10                                                                           | +12,<br>-13                               |                    | V                                   |

| COMMON-MODE REJECTION                                                                                                                                    |                                                                                                                                                                                                  | <b>60</b><br>60                                                                        | 72<br>72                                  |                        | 70<br>68                      | 76<br>76                                  |                    | 60<br>60                                                                      | 72<br>72                                  |                    | dB<br>dB                            |

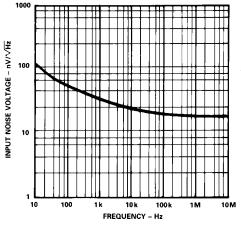

| INPUT VOLTAGE NOISE<br>Wideband Noise                                                                                                                    | f = 10 kHz<br>10 Hz to 10 MHz                                                                                                                                                                    |                                                                                        | 19<br>60                                  |                        |                               | 19<br>60                                  |                    |                                                                               | 19<br>60                                  |                    | $nV/\sqrt{Hz}$ $\mu V \ rms$        |

| OPEN LOOP GAIN                                                                                                                                           |                                                                                                                                                                                                  | <b>15</b><br>10                                                                        | 25<br>20                                  |                        | 20<br>10                      | 30<br>25                                  |                    | 15<br>10                                                                      | 30<br>25                                  |                    | V/mV<br>V/mV                        |

| OUTPUT CHARACTERISTICS<br>Voltage                                                                                                                        | $R_{LOAD} \geq 500~\Omega$                                                                                                                                                                       | ±10                                                                                    | +11.5,<br>-12.6                           |                        | ±10                           | +11.5,<br>-12.6                           |                    | ±10                                                                           | +11.5,<br>-12.6                           |                    | V                                   |

| Current<br>Output Resistance                                                                                                                             | V <sub>OUT</sub> = ±10 V<br>Open Loop                                                                                                                                                            | 50                                                                                     | 12                                        |                        | 50                            | 12                                        |                    | 50                                                                            | 12                                        |                    | mA<br>Ω                             |

| FREQUENCY RESPONSE<br>Unity Gain Bandwidth<br>Full Power Bandwidth <sup>3</sup><br>Rise Time<br>Overshoot<br>Slew Rate<br>Settling Time                  | $\begin{split} V_{OUT} &= 90 \text{ mV } p\text{-}p\\ V_{O} &= 20 \text{ V } p\text{-}p\\ R1 &\geq 500 \ \Omega\\ A_{VCL} &= -1\\ A_{VCL} &= -1\\ A_{VCL} &= -1\\ 10 \text{ V Step} \end{split}$ | 2.5<br>160                                                                             | 34<br>3.9<br>10<br>15<br>250              |                        | 2.5<br>160                    | 34<br>3.9<br>10<br>15<br>250              |                    | 2.5<br>160                                                                    | 34<br>3.9<br>10<br>15<br>250              |                    | MHz<br>MHz<br>ns<br>%<br>V/µs       |

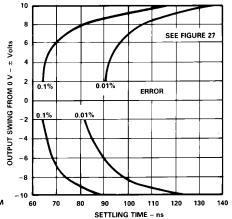

| Overdrive Recovery<br>Differential Gain<br>Differential Phase                                                                                            | $A_{VCL} = -1$<br>to 0.1%<br>to 0.01%<br>-Overdrive<br>+Overdrive<br>f = 4.4 MHz<br>f = 4.4 MHz                                                                                                  |                                                                                        | 95<br>135<br>200<br>700<br>0.025<br>0.025 |                        |                               | 95<br>135<br>200<br>700<br>0.025<br>0.025 |                    |                                                                               | 95<br>135<br>200<br>700<br>0.025<br>0.025 |                    | ns<br>ns<br>ns<br>ns<br>%<br>Degree |

| POWER SUPPLY<br>Rated Performance<br>Operating Range<br>Quiescent Current                                                                                | T <sub>MIN</sub> -T <sub>MAX</sub>                                                                                                                                                               | ±4.5                                                                                   | ±15<br>12<br>12.3                         | <b>±18</b><br>13<br>14 | ±4.5                          | ±15<br>12<br>12.3                         | ±18<br>13<br>14    | ±4.5                                                                          | ±15<br>12<br>12.5                         | ±18<br>13<br>16    | V<br>V<br>mA<br>mA                  |

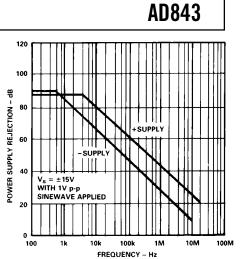

| Rejection Ratio<br>Rejection Ratio                                                                                                                       | ±5 V to ±18 V<br>T <sub>MIN</sub> -T <sub>MAX</sub>                                                                                                                                              | 65<br>62                                                                               | 76<br>76                                  |                        | 70<br>68                      | 80<br>80                                  |                    | 65<br>62                                                                      | 76<br>76                                  |                    | dB<br>dB                            |

| TEMPERATURE RANGE<br>Operating, Rated Performance<br>Commercial (0°C to +70°C)<br>Industrial (-40°C to +85°C)<br>Military (-55°C to +125°C) <sup>4</sup> |                                                                                                                                                                                                  | AD843J<br>AD843A                                                                       |                                           |                        | AD843K<br>AD843B              |                                           |                    | AD843S                                                                        |                                           |                    |                                     |

| PACKAGE OPTIONS<br>Plastic (N-8)<br>Cerdip (Q-8)<br>Metal Can (H-12A)<br>LCC (E-20A)<br>SOIC (R-16)<br>Tape & Reel<br>Chips                              |                                                                                                                                                                                                  | AD843JN<br>AD843AQ<br>AD843JR-16<br>AD843JR-16-REEL<br>AD843JR-16-REEL7<br>AD843JCHIPS |                                           |                        | AD843KN<br>AD843BQ<br>AD843BH |                                           |                    | AD843SQ, AD843SQ/883B<br>AD843SH, AD843SH/883B<br>AD843SE/883B<br>AD843SCHIPS |                                           |                    |                                     |

### AD843

#### NOTES

<sup>1</sup>Standard Military Drawings Available: 5962-9098001M2A (SE/883B), 5962-9098001MXA (SH/883B), 5962-9098001MPA (SQ/883B). <sup>2</sup>Specifications are guaranteed after 5 minutes at  $T_A = +25^{\circ}$ C.

<sup>3</sup>Full power bandwidth = Slew Rate/2  $\pi$ V peak.

<sup>4</sup>All "S" grade  $T_{MIN}$ - $T_{MAX}$  specifications are tested with automatic test equipment at  $T_A = -55^{\circ}$ C and  $T_A = +125^{\circ}$ C.

Specifications subject to change without notice.

Specifications in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed although only those shown in **boldface** are tested on all production units.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

Supply Voltage .....±18 V Internal Power Dissipation<sup>2</sup> Plastic Package ..... 1.50 Watts Cerdip Package ..... 1.35 Watts 12-Pin Header Package ..... 1.80 Watts 16-Pin SOIC Package ..... 1.50 Watts 20-Pin LCC Package ..... 1.00 Watt Output Short Circuit Duration ..... Indefinite Differential Input Voltage ..... +V<sub>S</sub> and -V<sub>S</sub> Storage Temperature Range (N, R) ..... -65°C to +125°C Storage Temperature Range (Q, H, E) .... -65°C to +150°C **Operating Temperature Range** AD843J/R .....  $0^{\circ}C$  to  $+70^{\circ}C$ Lead Temperature Range (Soldering 60 sec) ..... +300°C ESD Rating ..... 500 V

#### NOTES

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>8-Pin Plastic Package:  $\theta_{JA} = 100^{\circ}$ C/Watt 8-Pin Cerdip Package:  $\theta_{JA} = 110^{\circ}$ C/Watt 12-Pin Header Package:  $\theta_{JA} = 80^{\circ}$ C/Watt 16-Pin SOIC Package:  $\theta_{JA} = 100^{\circ}$ C/Watt 20-Pin LCC Package:  $\theta_{JA} = 150^{\circ}$ C/Watt

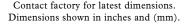

#### **METALIZATION PHOTOGRAPH**

SUBSTRATE CONNECTED TO  $+ V_S$

## **AD843–Typical Characteristics**

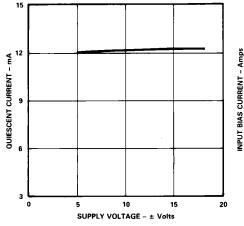

Figure 4. Quiescent Current vs. Supply Voltage

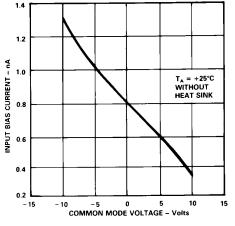

Figure 7. Input Bias Current vs. Common Mode Voltage

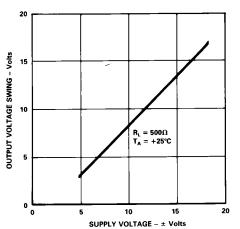

Figure 2. Output Voltage Swing vs. Supply Voltage

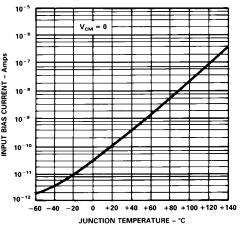

*Figure 5. Input Bias Current vs. Junction Temperature*

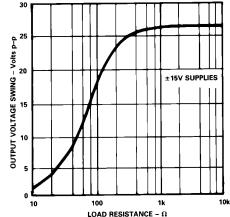

*Figure 3. Output Voltage Swing vs. Load Resistance*

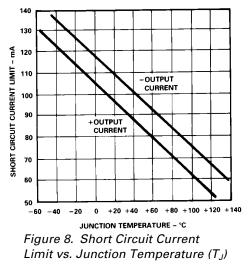

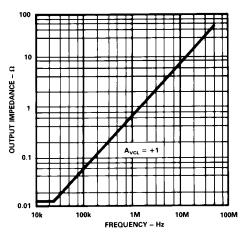

*Figure 6. Output Impedance vs. Frequency*

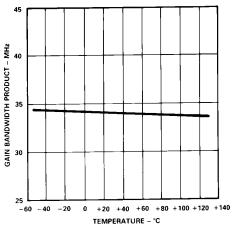

Figure 9. Gain Bandwidth Product vs. Temperature

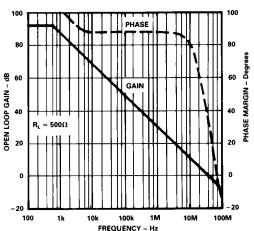

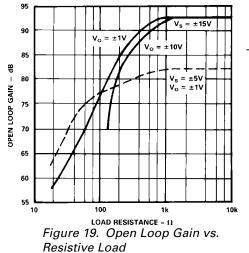

Figure 10. Open Loop Gain and Phase Margin vs. Frequency

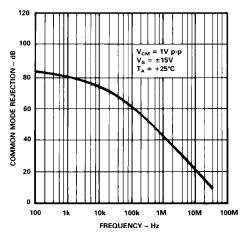

Figure 13. Common Mode Rejection vs. Frequency

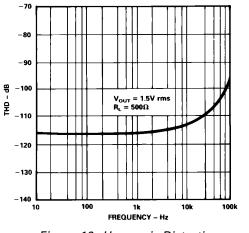

Figure 16. Harmonic Distortion vs. Frequency

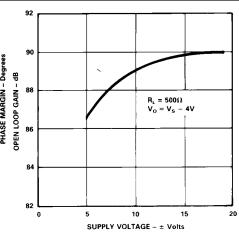

Figure 11. Open Loop Gain vs. Supply Voltage

Figure 12. Power Supply Rejection vs. Frequency

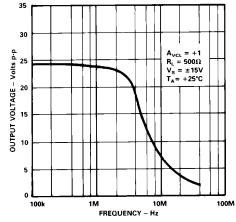

Figure 14. Large Signal Frequency Response

Figure 17. Input Noise Voltage Spectral Density

Figure 15. Output Swing and Error vs. Settling Time

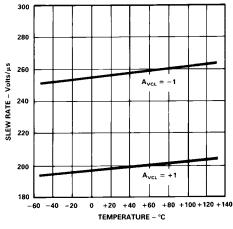

Figure 18. Slew Rate vs. Temperature

## **AD843–Typical Characteristics**

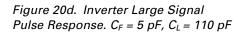

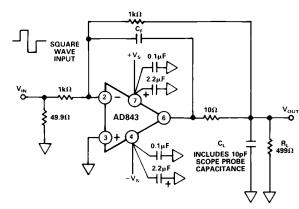

Figure 20a. Inverting Amplifier Connection

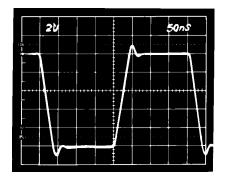

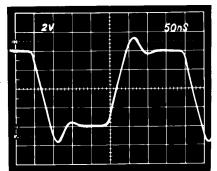

Figure 20b. Inverter Large Signal Pulse Response.  $C_F = 0$ ,  $C_L = 10 \text{ pF}$

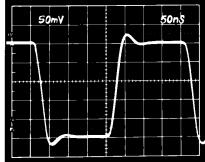

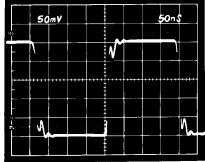

Figure 20c. Inverter Small Signal Pulse Response.  $C_F = 0$ ,  $C_L = 10$  pF

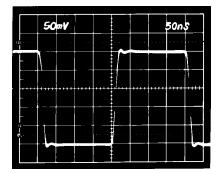

Figure 20e. Inverter Small Signal Pulse Response.  $C_F = 5 pF$ ,  $C_L = 110 pF$

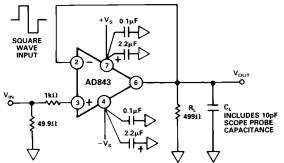

Figure 21a. Unity Gain Inverter Circuit for Driving Capacitive Loads

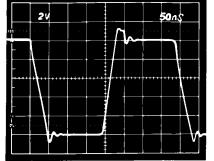

Figure 21b. Inserter Cap Load Large Signal Pulse Response.  $C_F = 15 \text{ pF}, C_L = 410 \text{ pF}$

Figure 21c. Inverter Cap Load Small Signal Pulse Response.  $C_F = 15 \text{ pF}, C_L = 410 \text{ pF}$

### AD843

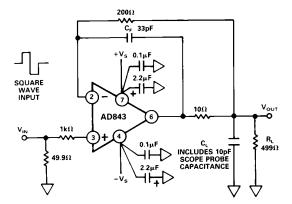

Figure 22a. Unity Gain Buffer Amplifier

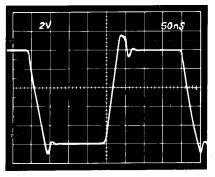

Figure 22b. Buffer Large Signal Pulse Response.  $C_L = 10 \text{ pF}$

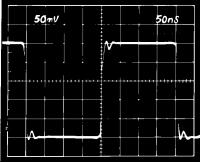

Figure 22c. Buffer Small Signal Pulse Response.  $C_L = 10 \text{ pF}$

Figure 23a. Unity Gain Buffer Circuit for Driving Capacitive Loads

Figure 23b. Buffer Cap Load Large Signal Pulse Response.  $C_F = 33 \text{ pF}, C_L = 10 \text{ pF}$

Figure 23c. Buffer Cap Load Small Signal Pulse Response.  $C_F = 33 \text{ pF}$ ,  $C_L = 10 \text{ pF}$

Figure 23d. Buffer Cap Load Large Signal Pulse Response.  $C_F = 33 \text{ pF}, C_L = 110 \text{ pF}$

Figure 23e. Buffer Cap Load Small Signal Pulse Response.  $C_F = 33 \text{ pF}, C_L = 110 \text{ pF}$

## AD843

### **GROUNDING AND BYPASSING**

Like most high bandwidth amplifiers, the AD843 is sensitive to capacitive loading. Although it will drive capacitive loads up to 20 pF without degradation of its rated performance, both an increased capacitive load drive capability and a "cleaner" (nonringing) pulse response can be obtained from the AD843 by using the circuits illustrated in Figures 20 to 23. The addition of a 5 pF feedback capacitor to the unity gain inverter connection (Figure 20a) substantially reduces the circuit's overshoot, even when it is driving a 110 pF load. This can be seen by comparing the waveforms of Figures 20b through 20e. To drive capacitive loads greater than 100 pF, the load should be decoupled from the amplifier's output by a 10  $\Omega$  resistor and the feedback capacitor, C<sub>F</sub>, should be connected directly between the amplifier's output and its inverting input (Figure 21a). When using a 15 pF feedback capacitor, this circuit can drive 400 pF with less than 20% overshoot, as illustrated in Figures 21b and 21c. Increasing capacitor C<sub>F</sub> to 47 pF also increases the capacitance drive capability to 1000 pF, at the expense of a 10:1 reduction in bandwidth compared with the simple unity gain inverter circuit of Figure 20a.

Unity gain voltage followers (buffers) are more sensitive to capacitive loads than are inverting amplifiers because there is no attenuation of the feedback signal. The AD843 can drive 10 pF to 20 pF when connected in the basic unity gain buffer circuit of Figure 22a.

The 1 k $\Omega$  resistor in series with the AD843's noninverting input serves two functions: first, together with the amplifier's input capacitance, it forms a low-pass filter which slows down the actual signal seen by the AD843. This helps reduce ringing on the amplifier's output voltage. The resistor's second function is to limit the current into the amplifier when the differential input voltage exceeds the total supply voltage.

The AD843 will deliver a much "cleaner" pulse response when connected in the somewhat more elaborate follower circuit of Figure 23a. Note the reduced overshoot in Figure 23b and 23c as compared to Figures 22b and 22c.

For maximum bandwidth, in most applications, input and feedback resistors used with the AD843 should have resistance values equal to or less than 1.5 k $\Omega$ . Even with these low resistance values, the resultant RC time constant formed between them and stray circuit capacitances is large enough to cause peaking in the amplifier's response. Adding a small capacitor, C<sub>F</sub>, as shown in Figures 20a to 23a will reduce this peaking and flatten the overall frequency response. C<sub>F</sub> will normally be less than 10 pF in value.

The AD843 can drive resistive loads over the range of 500  $\Omega$  to  $\infty$  with no change in dynamic response. While a 499  $\Omega$  load was used in the circuits of Figures 20-23, the performance of these circuits will be essentially the same even if this load is removed or changed to some other value, such as 2 k $\Omega$ .

To obtain the "cleanest" possible transient response when driving heavy capacitive loads, be sure to connect bypass capacitors directly between the power supply pins of the AD843 and ground as outlined in "grounding and bypassing."

### **GROUNDING AND BYPASSING**

In designing practical circuits using the AD843, the user must keep in mind that some special precautions are needed when dealing with high frequency signals. Circuits must be wired using short interconnect leads. Ground planes should be used whenever possible to provide both a low resistance, low inductance circuit path and to minimize the effects of high frequency coupling. IC sockets should be avoided, since their increased interlead capacitance can degrade the bandwidth of the device.

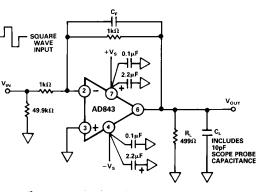

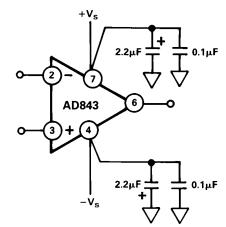

Power supply leads should be bypassed to ground as close as possible to the pins of the amplifier. Again, the component leads should be kept very short. As shown in Figure 24, a parallel combination of a 2.2  $\mu$ F tantalum and a 0.1  $\mu$ F ceramic disc capacitor is recommended.

Figure 24. Recommended Power Supply Bypassing for the AD843 (DIP Pinout)

### USING A HEAT SINK

The AD843 consumes less quiescent power than most precision high speed amplifiers and is specified to operate without using a heat sink. However, when driving low impedance loads, the current applied to the load can be 4 to 5 times greater than the quiescent current. This will produce a noticeable temperature rise, which will increase input bias currents. The use of a small heat sink, such as the Mouser Electronics #33HS008 is recommended.

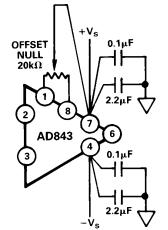

Offset Null Configuration (DIP Pinout)

### SAMPLE-AND-HOLD AMPLIFIER CIRCUITS

#### A Fast Switching Sample & Hold Circuit

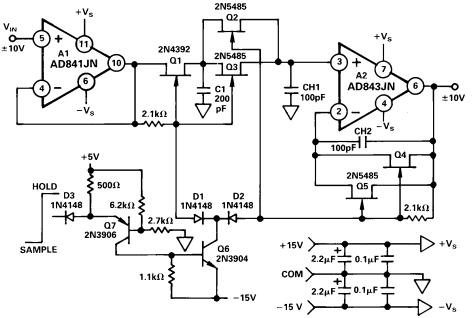

A sample-and-hold circuit possessing short acquisition time and low aperture delay can be built using an AD843 and discrete JFET switches. The circuit of Figure 25 employs five n-channel JFETs (with turn-on times of 35 ns) and an AD843 op amp (which can settle to 0.01% in 135 ns). The circuit has an aperture delay time of 50 ns and an acquisition time of 1 µs or less.

This circuit is based on a noninverting open loop architecture, using a differential hold capacitor to reduce the effects of pedestal error. The charge that is removed from CH1 by Q2 and Q3 is offset by the charge removed from CH2 by Q4 and Q5. This circuit can tolerate low hold capacitor values (approximately 100 pF), which improve acquisition time, due to the small gateto-drain capacitance of the discrete JFETs. Although pedestal error will vary with input signal level, making trimming more difficult, the circuit has the advantages of high bandwidth and short acquisition times. In addition, it will exhibit some nonlinearity because both amplifiers are operating with a common-mode input. Amplifier A2, however, contributes less than 0.025% linearity error, due to its 72 dB common-mode rejection ratio. To make sure the circuit accommodates a wide  $\pm 10$  V input range, the gates of the JFETs must be connected to a potential near the -15 V supply. The level-shift circuitry (diode D3, PNP transistor Q7, and NPN transistor Q6) shifts the TTL level S/H command to provide for an adequate pinch-off voltage for the JFET switches over the full input voltage range.

The JFETs Q2, Q3, Q4 and Q5 across the two hold capacitors ensure signal acquisition for all conditions of  $V_{\rm IN}$  and  $V_{\rm OUT}$  when the circuit switches from the sample to the hold mode. Transistor Q1 provides an extra stage of isolation between the output of amplifier A1 and the hold capacitor CH1.

When selecting capacitors for use in a sample-and-hold circuit, the designer should choose those types with low dielectric absorption and low temperature coefficients. Silvered-mica capacitors exhibit low (0 to 100 ppm/°C) temperature coefficients and will still work in temperatures exceeding 200°C. It is also recommend that the user test the chosen capacitor to insure that its value closely matches that printed on it since not all capacitors are fully tested by their manufacturers for absolute tolerance.

Figure 25. A Fast Switching Sample-and-Hold Amplifier

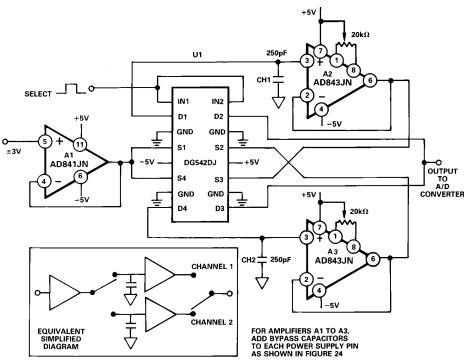

### A PING-PONG S/H AMPLIFIER

For improved throughput over the circuit of Figure 25, a "pingpong" architecture may be used. A ping-pong circuit overcomes some of the problems associated with high speed S/H amplifiers by allowing the use of a larger hold capacitor for a given sample rate: this will reduce the associated feedthrough, droop and pedestal errors.

Figure 26 illustrates a simple, four-chip ping-pong sample-andhold amplifier circuit. This design increases throughput by using one channel to acquire a new sample while another channel holds the previous sample. Instead of having to reacquire the signal when switching from hold to sample mode, it alternately connects the outputs from Channel 1 or from Channel 2 to the A/D converter. In this case, the throughput is the slew rate and settling time of the output amplifiers, A2 and A3. A high speed CB amplifier, A1, follows the input signal. U1, a dual wideband "T" switch, connects the input buffer amp to one of the two output amplifiers while selecting the complementary amplifier to drive the A/D input. For example, when "select" is at logic high, A1 drives CH1, A2 tracks the input signal and the output of A3 is connected to the input of the A/D converter. At the same time, A3 holds an analog value and its output is connected to the input of the A/D converter. When the select command goes to logic LOW, the two output amplifiers alternate functions.

Since the input to the A/D converter is the alternated "held" outputs from A1 and A2, the offset voltage mismatch of the two amplifiers will show up as nonlinearity and, therefore, distortion in the output signal. To minimize this, potentiometers can be used to adjust the offsets of the output amplifiers until they are

equal. Alternatively, an autocalibration circuit using two D/A converters can be employed. This can also be used to calibrate out the effects of offset voltage drift over temperature.

The switch choice, for U1s, is critical in this type of design. The DG542 utilizes "T" switching techniques on each channel for exceptionally low crosstalk and for high isolation. The part fur-

ther improves these specifications by using ground pins between the signal pins. With an input frequency of 5 MHz, crosstalk and isolation are -85 dB and -75 dB, respectively. A limitation of this switch is that it operates from a maximum -5 V negative supply, making bipolar operation more difficult. It is recommended that amplifiers A1, A2 and A3 operate from the same -5 V supply to minimize any potential latch-up problems.

Figure 26. A Ping-Pong Sample-and-Hold Amplifier

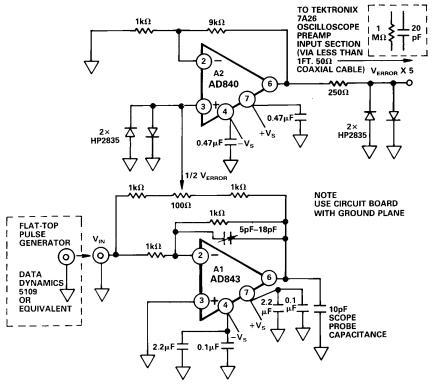

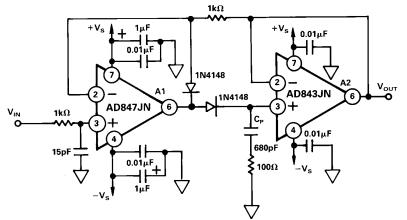

Figure 27. Settling Time Test Circuit

### **MEASURING AD843 SETTLING TIME**

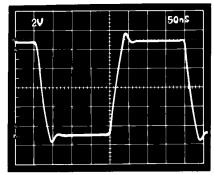

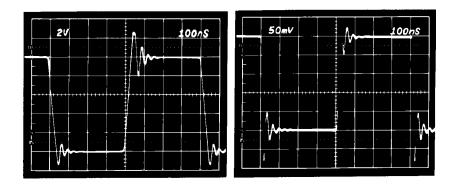

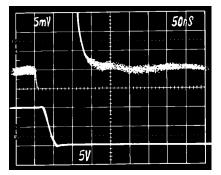

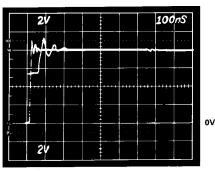

Figure 28 shows the dynamic response of the AD843 while operating in the settling time test circuit of Figure 27. The input of the settling time fixture is driven by a flat-top pulse generator. The error signal output from A1, the AD843 under test, is amplified by op amp A2 and then clamped by two high speed Schottky diodes.

Figure 28. Settling Characteristics: +10 V to 0 V Step. Upper Trace: Amplified Error Voltage (0.01%/Div) Lower Trace: Output of AD843 Under Test (5 V/Div)

The error signal is clamped to prevent it from greatly overloading the oscilloscope preamp. A Tektronix oscilloscope preamp type 7A26 was chosen because it will recover from the approximately 0.4 volt overload, quickly enough to allow accurate measurement of the AD843's 135 ns settling time. Amplifier A2 is a very high speed op amp; it provides a voltage gain of 10, providing a total gain of 5 from the error signal to the oscilloscope input.

### A FAST PEAK DETECTOR CIRCUIT

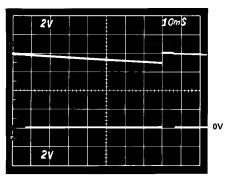

The peak detector circuit of Figure 29, can accurately capture the amplitude of input pulses as narrow as 200 ns and can hold their value with a droop rate of less than 20  $\mu$ V/µs. This circuit will capture the peak value of positive polarity waveforms; to detect negative peaks, simply reverse the polarity of the two diodes.

The high bandwidth and 200 V/ $\mu$ s slew rate of amplifier A2, an AD843, allows the detector's output to "keep up" with its input thus minimizing overshoot. The low (<1 nA) input current of the AD843 ensures that the droop rate is limited only by the reverse leakage of diode D2, which is typically <10 nA for the type shown. The low droop rate is apparent in Figure 30. The

detector's output (top trace) loses slightly over a volt of the 8 volt peak input value (bottom trace) in 75 ms, or a rate of approximately  $16 \,\mu V/\mu s$ .

TOP TRACE: PEAK DETECTOR OUTPUT BOTTOM TRACE: INPUT, 8V PEAK @ 125Hz Figure 30. Peak Detector Response to 125 Hz Pulse Train

TOP TRACE: PEAK DETECTOR OUTPUT, 8V BOTTOM TRACE: INPUT VOLTAGE, 8V PEAK, 650ns PULSE WIDTH

### Figure 31. Peak Capture Time

Amplifier A1, an AD847, can drive 680 pF hold capacitor,  $C_P$ , fast enough to "catch-up" with the next peak in 100 ns and still settle to the new value in 250 ns, as illustrated in Figure 31. *Reducing* the value of capacitor  $C_P$  to 100 pF will maximize the speed of this circuit at the expense of increased overshoot and droop. Since the AD847 can drive an arbitrarily large value of capacitance,  $C_P$  can be *increased* to reduce droop, at the expense of response time.

Figure 29. A Fast Peak Detector Circuit

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).