# **TDA8757A**

Triple 8-bit ADC 205 Msps

Rev. 01 — 22 March 2002

**Preliminary data**

# 1. General description

The TDA8757A is a triple 8-bit ADC for the digitizing of large bandwidth RGB/YUV signals at a sampling rate up to 205 Msps.

The IC supports display resolutions up to 1600 × 1200 (UXGA) at 75 Hz.

The IC also includes a PLL that can be locked to the horizontal line frequency and generates the ADC clock. The PLL jitter is minimized for high resolution PC graphics applications. An external clock signal can also be used to clock the ADC.

The outputs are available either on one port up to 110 Msps or on two ports up to 205 Msps. The operating mode is selectable with the serial interface for either I<sup>2</sup>C-bus or 3-wire serial bus (3W-bus) operation.

The clamp level, the gain and the other settings are controllable through the serial interface.

#### 2. Features

- Triple 8-bit ADC

- Sampling rate up to 205 Msps

- IC controllable by a serial interface which can be I<sup>2</sup>C-bus or 3W-bus, selected by a TTL input pin

- Three clamps for programming a clamping code from −63.5 to +64 in steps of ½ LSB (RGB) and from +120 to +136 in steps of ½ LSB (YUV)

- Three controllable amplifiers: gain controlled through the serial interface to produce a full-scale resolution of ½ LSB peak-to-peak

- Amplifier bandwidth of 250 MHz

- Low gain variation with temperature

- PLL controllable with the serial interface to generate the ADC clock which can be locked to any line frequency of 15 to 150 kHz

- Integrated PLL divider

- Programmable phase clock adjustment cells

- Internal voltage regulators

- TTL compatible digital inputs and outputs

- Outputs on one port or demultiplexed on two ports; selectable with the serial interface

- Chip enable high-impedance ADC output

- Power-down mode

- 1.7 W power dissipation

- Sync on green extractor.

# 3. Applications

- RGB/YUV high-speed digitizing

- LCD panels drive

- LCD projection systems

- VGA to UXGA (1600 × 1200 at 75 Hz) modes.

# 4. Quick reference data

Table 1: Quick reference data

| Symbol                        | Parameter                                                 | Conditions                                                                                            | Min  | Тур  | Max  | Unit   |

|-------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|--------|

| V <sub>CCA</sub>              | analog supply voltage for PLL and the RGB channels        |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| $V_{DDD}$                     | logic supply voltage for I <sup>2</sup> C-bus and 3W-bus  |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| V <sub>CCD</sub>              | digital supply voltage                                    |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| V <sub>CCO</sub>              | output stages supply voltage for PLL and the RGB channels |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| V <sub>CCA(PLL)</sub>         | analog PLL supply voltage                                 |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| V <sub>CCO(PLL)</sub>         | output PLL supply voltage                                 |                                                                                                       | 4.75 | 5.0  | 5.25 | V      |

| I <sub>CCA</sub>              | analog supply current for the RGB channels                |                                                                                                       | -    | 135  | -    | mA     |

| I <sub>DDD</sub>              | logic supply current for I <sup>2</sup> C-bus and 3W-bus  |                                                                                                       | -    | 1    | -    | mA     |

| I <sub>CCD</sub>              | digital supply current                                    |                                                                                                       | _    | 95   | _    | mA     |

| I <sub>CCO</sub>              | output stages supply current                              |                                                                                                       | -    | 80   | _    | mA     |

| I <sub>CCA(PLL)</sub>         | analog PLL supply current                                 |                                                                                                       | -    | 34   | _    | mA     |

| f <sub>clk</sub>              | clock frequency                                           | normal (Dmx = $0$ )                                                                                   | _    | _    | 110  | MHz    |

|                               |                                                           | demultiplexed (Dmx = $1$ )                                                                            | _    | _    | 205  | MHz    |

| f <sub>ref(PLL)</sub>         | PLL reference clock frequency                             |                                                                                                       | 15   | _    | 150  | kHz    |

| f <sub>PLL</sub>              | output clock frequency range                              |                                                                                                       | 12   | _    | 205  | MHz    |

| INL                           | DC integral non-linearity                                 | from analog input to<br>digital output; full-scale;<br>sine wave input;<br>f <sub>clk</sub> = 205 MHz | -    | ±0.5 | ±1.5 | LSB    |

| DNL                           | DC differential non-linearity                             | from analog input to<br>digital output; full-scale;<br>sine wave input;<br>f <sub>clk</sub> = 205 MHz | -    | ±0.4 | ±1   | LSB    |

| $\Delta G_{amp}\!/\!\Delta T$ | amplifier gain stability variation with temperature       | V <sub>ref</sub> = 2.5 V with<br>100 ppm/°C maximum                                                   | _    | 325  | _    | ppm/°C |

| В                             | amplifier bandwidth                                       | $-3$ dB; $T_{amb} = 25$ °C                                                                            | 250  | -    | _    | MHz    |

| t <sub>set(ADC+AGC)</sub>     | settling time of the block<br>ADC + AGC                   | input signal settling<br>time <1 ns; settling to<br>1%; f <sub>i</sub> = 85 MHz                       | -    | 4    | _    | ns     |

Table 1: Quick reference data...continued

| Symbol            | Parameter                                     | Conditions                                  | Min | Тур | Max  | Unit |

|-------------------|-----------------------------------------------|---------------------------------------------|-----|-----|------|------|

| DR <sub>PLL</sub> | PLL divider ratio                             |                                             | 100 | _   | 4095 |      |

| P <sub>tot</sub>  | total power dissipation                       | f <sub>clk</sub> = 205 MHz; sine wave input | _   | 1.7 | _    | W    |

| JPLL(max)(p-p)    | maximum PLL phase jitter (peak-to-peak value) | f <sub>clk</sub> = 205 MHz                  | _   | 336 | _    | ps   |

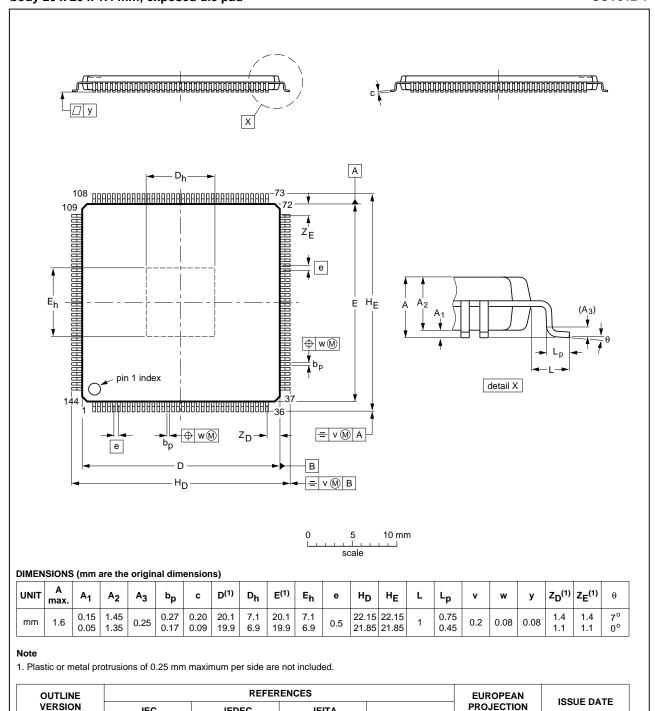

# 5. Ordering information

### **Table 2: Ordering information**

| Type number   | Package  |                                                             |        |                    |  |  |

|---------------|----------|-------------------------------------------------------------|--------|--------------------|--|--|

|               | Name     | Description Vers                                            |        | frequency<br>(MHz) |  |  |

| TDA8757AHL/17 | HLQFP144 | plastic thermal enhanced low profile quad flat package; SOT | Γ612-1 | 170                |  |  |

| TDA8757AHL/21 |          | 144 leads; body 20 × 20 × 1.4 mm; exposed die pad           |        | 205                |  |  |

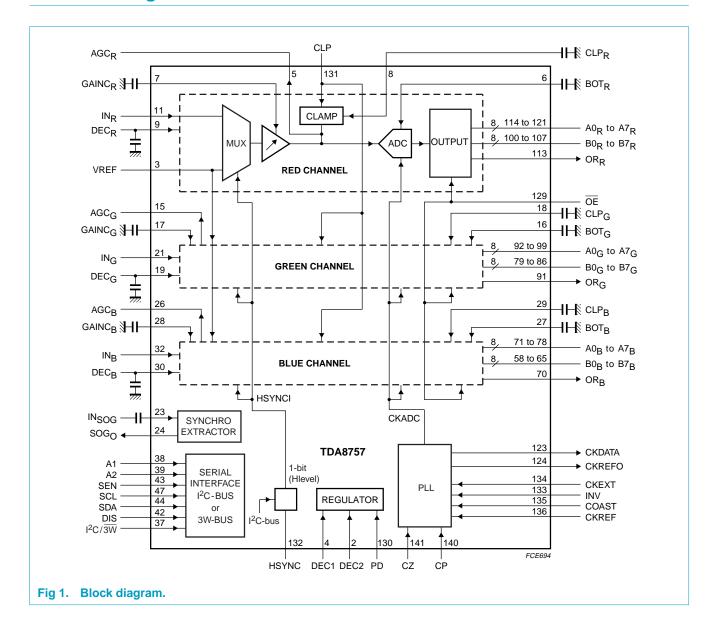

# 6. Block diagram

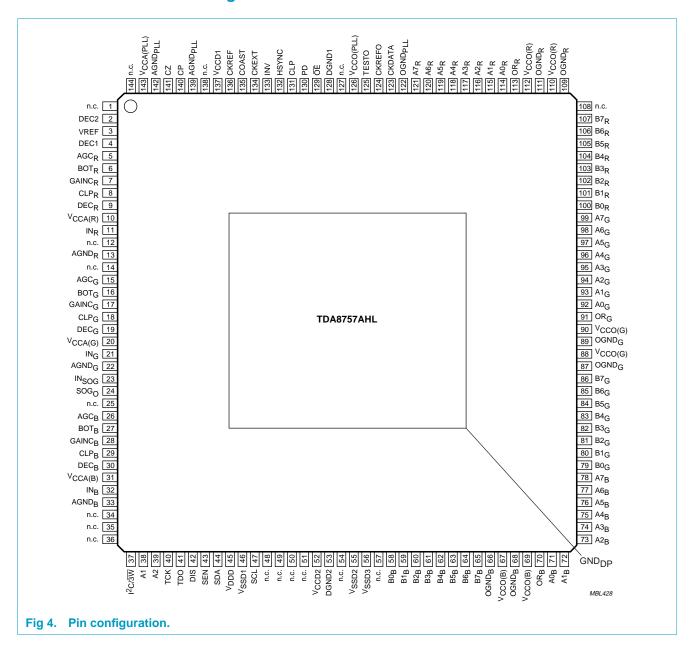

# 7. Pinning information

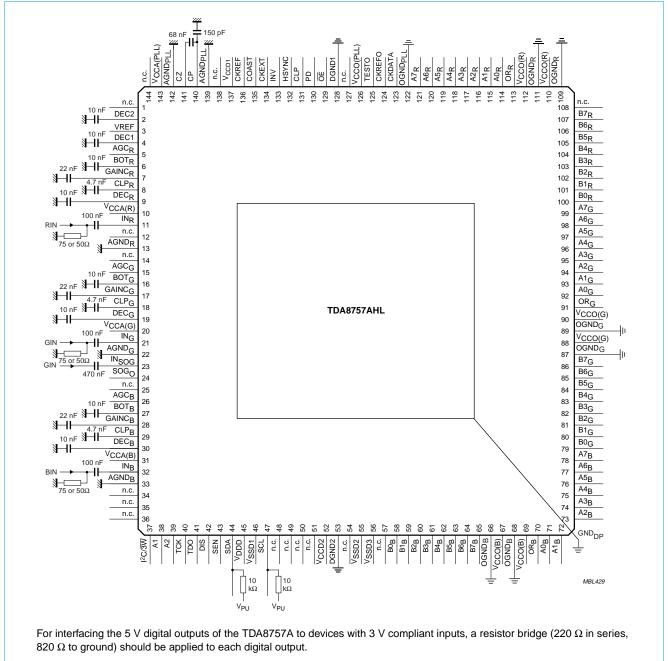

# 7.1 Pinning

### 7.2 Pin description

Table 3: Pin description

| Symbol | Pin | Description                             |

|--------|-----|-----------------------------------------|

| n.c.   | 1   | not connected                           |

| DEC2   | 2   | main regulator decoupling input 2       |

| VREF   | 3   | gain stabilizer voltage reference input |

| DEC1   | 4   | main regulator decoupling input 1       |

|        |     |                                         |

9397 750 09549

Table 3:

Pin description...continued

| Table 5.                        | i ili description |                                                                                    |

|---------------------------------|-------------------|------------------------------------------------------------------------------------|

| Symbol                          | Pin               | Description                                                                        |

| $AGC_R$                         | 5                 | red channel AGC output                                                             |

| $BOT_R$                         | 6                 | red channel ladder decoupling input (BOT)                                          |

| $GAINC_R$                       | 7                 | red channel gain capacitor input                                                   |

| CLP <sub>R</sub>                | 8                 | red channel clamp capacitor input                                                  |

| DECR                            | 9                 | red channel regulator decoupling input                                             |

| V <sub>CCA(R)</sub>             | 10                | red channel analog supply voltage                                                  |

| IN <sub>R</sub>                 | 11                | red channel analog input                                                           |

| n.c.                            | 12                | not connected                                                                      |

| $AGND_R$                        | 13                | red channel gain analog ground                                                     |

| n.c.                            | 14                | not connected                                                                      |

| $AGC_G$                         | 15                | green channel AGC output                                                           |

| $BOT_G$                         | 16                | green channel ladder decoupling input (BOT)                                        |

| GAINC <sub>G</sub>              | 17                | green channel gain capacitor input                                                 |

| CLP <sub>G</sub>                | 18                | green channel clamp capacitor input                                                |

| $DEC_G$                         | 19                | green channel regulator decoupling input                                           |

| V <sub>CCA(G)</sub>             | 20                | green channel analog supply voltage                                                |

| $IN_G$                          | 21                | green channel analog input                                                         |

| $AGND_G$                        | 22                | green channel gain analog ground                                                   |

| IN <sub>SOG</sub>               | 23                | sync on green channel input                                                        |

| SOGO                            | 24                | composite sync output                                                              |

| n.c.                            | 25                | not connected                                                                      |

| $AGC_B$                         | 26                | blue channel AGC output                                                            |

| BOTB                            | 27                | blue channel ladder decoupling input (BOT)                                         |

| $GAINC_B$                       | 28                | blue channel gain capacitor input                                                  |

| CLP <sub>B</sub>                | 29                | blue channel clamp capacitor input                                                 |

| DECB                            | 30                | blue channel regulator decoupling input                                            |

| V <sub>CCA(B)</sub>             | 31                | blue channel analog supply voltage                                                 |

| IN <sub>B</sub>                 | 32                | blue channel analog input                                                          |

| $AGND_B$                        | 33                | blue channel gain analog ground                                                    |

| n.c.                            | 34                | not connected                                                                      |

| n.c.                            | 35                | not connected                                                                      |

| n.c.                            | 36                | not connected                                                                      |

| I <sup>2</sup> C/ <del>3W</del> | 37                | selection input between I <sup>2</sup> C-bus (active HIGH) and 3W-bus (active LOW) |

| A1                              | 38                | I <sup>2</sup> C-bus address control input 1                                       |

| A2                              | 39                | I <sup>2</sup> C-bus address control input 2                                       |

| TCK                             | 40                | scan test mode input (active HIGH)                                                 |

| TDO                             | 41                | scan test output                                                                   |

| DIS                             | 42                | I <sup>2</sup> C-bus and 3W-bus disable control input (disable at HIGH level)      |

| SEN                             | 43                | select enable input for 3W-bus                                                     |

|                                 |                   |                                                                                    |

Table 3:

Pin description...continued

| Symbol              | Pin | Description                                              |

|---------------------|-----|----------------------------------------------------------|

| SDA                 | 44  | I <sup>2</sup> C-bus/3W-bus serial data input            |

| V <sub>DDD</sub>    | 45  | logic I <sup>2</sup> C-bus/3W-bus digital supply voltage |

| V <sub>SSD1</sub>   | 46  | logic I <sup>2</sup> C-bus/3W-bus digital ground 1       |

| SCL                 | 47  | I <sup>2</sup> C-bus/3W-bus serial clock input           |

| n.c.                | 48  | not connected                                            |

| n.c.                | 49  | not connected                                            |

|                     | 50  | not connected                                            |

| n.c.                | 51  | not connected                                            |

| n.c.                | 52  |                                                          |

| V <sub>CCD2</sub>   |     | digital supply voltage 2                                 |

| DGND2               | 53  | digital ground 2                                         |

| n.c.                | 54  | not connected                                            |

| V <sub>SSD2</sub>   | 55  | logic I <sup>2</sup> C-bus/3W-bus digital ground 2       |

| $V_{SSD3}$          | 56  | logic I <sup>2</sup> C-bus/3W-bus digital ground 3       |

| n.c.                | 57  | not connected                                            |

| B0 <sub>B</sub>     | 58  | blue channel ADC output B bit 0 (LSB)                    |

| B1 <sub>B</sub>     | 59  | blue channel ADC output B bit 1                          |

| B2 <sub>B</sub>     | 60  | blue channel ADC output B bit 2                          |

| B3 <sub>B</sub>     | 61  | blue channel ADC output B bit 3                          |

| B4 <sub>B</sub>     | 62  | blue channel ADC output B bit 4                          |

| B5 <sub>B</sub>     | 63  | blue channel ADC output B bit 5                          |

| B6 <sub>B</sub>     | 64  | blue channel ADC output B bit 6                          |

| B7 <sub>B</sub>     | 65  | blue channel ADC output B bit 7 (MSB)                    |

| OGND <sub>B</sub>   | 66  | blue channel ADC output B ground                         |

| $V_{CCO(B)}$        | 67  | blue channel ADC output B supply voltage                 |

| OGND <sub>B</sub>   | 68  | blue channel ADC output A ground                         |

| $V_{\text{CCO(B)}}$ | 69  | blue channel ADC output A supply voltage                 |

| OR <sub>B</sub>     | 70  | blue channel ADC output bit out of range                 |

| A0 <sub>B</sub>     | 71  | blue channel ADC output A bit 0 (LSB)                    |

| A1 <sub>B</sub>     | 72  | blue channel ADC output A bit 1                          |

| A2 <sub>B</sub>     | 73  | blue channel ADC output A bit 2                          |

| A3 <sub>B</sub>     | 74  | blue channel ADC output A bit 3                          |

| A4 <sub>B</sub>     | 75  | blue channel ADC output A bit 4                          |

| A5 <sub>B</sub>     | 76  | blue channel ADC output A bit 5                          |

| A6 <sub>B</sub>     | 77  | blue channel ADC output A bit 6                          |

| A7 <sub>B</sub>     | 78  | blue channel ADC output A bit 7 (MSB)                    |

| B0 <sub>G</sub>     | 79  | green channel ADC output B bit 0 (LSB)                   |

| B1 <sub>G</sub>     | 80  | green channel ADC output B bit 1                         |

| B2 <sub>G</sub>     | 81  | green channel ADC output B bit 2                         |

| B3 <sub>G</sub>     | 82  | green channel ADC output B bit 3                         |

| B4 <sub>G</sub>     | 83  | green channel ADC output B bit 4                         |

| B5 <sub>G</sub>     | 84  | green channel ADC output B bit 5                         |

|                     |     | · · · · · · · · · · · · · · · · · · ·                    |

Table 3:

Pin description...continued

| Table 3:            | Pin descriptioncontinued |                                                     |  |  |

|---------------------|--------------------------|-----------------------------------------------------|--|--|

| Symbol              | Pin                      | Description                                         |  |  |

| B6 <sub>G</sub>     | 85                       | green channel ADC output B bit 6                    |  |  |

| B7 <sub>G</sub>     | 86                       | green channel ADC output B bit 7 (MSB)              |  |  |

| OGND <sub>G</sub>   | 87                       | green channel ADC output B ground                   |  |  |

| $V_{CCO(G)}$        | 88                       | green channel ADC output B supply voltage           |  |  |

| $OGND_G$            | 89                       | green channel ADC output A ground                   |  |  |

| $V_{\text{CCO}(G)}$ | 90                       | green channel ADC output A supply voltage           |  |  |

| OR <sub>G</sub>     | 91                       | green channel ADC output bit out of range           |  |  |

| $A0_{G}$            | 92                       | green channel ADC output A bit 0 (LSB)              |  |  |

| A1 <sub>G</sub>     | 93                       | green channel ADC output A bit 1                    |  |  |

| A2 <sub>G</sub>     | 94                       | green channel ADC output A bit 2                    |  |  |

| $A3_G$              | 95                       | green channel ADC output A bit 3                    |  |  |

| $A4_{G}$            | 96                       | green channel ADC output A bit 4                    |  |  |

| $A5_G$              | 97                       | green channel ADC output A bit 5                    |  |  |

| A6 <sub>G</sub>     | 98                       | green channel ADC output A bit 6                    |  |  |

| A7 <sub>G</sub>     | 99                       | green channel ADC output A bit 7 (MSB)              |  |  |

| B0 <sub>R</sub>     | 100                      | red channel ADC output B bit 0 (LSB)                |  |  |

| B1 <sub>R</sub>     | 101                      | red channel ADC output B bit 1                      |  |  |

| B2 <sub>R</sub>     | 102                      | red channel ADC output B bit 2                      |  |  |

| B3 <sub>R</sub>     | 103                      | red channel ADC output B bit 3                      |  |  |

| B4 <sub>R</sub>     | 104                      | red channel ADC output B bit 4                      |  |  |

| B5 <sub>R</sub>     | 105                      | red channel ADC output B bit 5                      |  |  |

| B6 <sub>R</sub>     | 106                      | red channel ADC output B bit 6                      |  |  |

| B7 <sub>R</sub>     | 107                      | red channel ADC output B bit 7 (MSB)                |  |  |

| n.c.                | 108                      | not connected                                       |  |  |

| $OGND_R$            | 109                      | red channel ADC output B ground                     |  |  |

| $V_{CCO(R)}$        | 110                      | red channel ADC output B supply voltage             |  |  |

| $OGND_R$            | 111                      | red channel ADC output A ground                     |  |  |

| $V_{CCO(R)}$        | 112                      | red channel ADC output A supply voltage             |  |  |

| $OR_R$              | 113                      | red channel ADC output A bit out of range           |  |  |

| A0 <sub>R</sub>     | 114                      | red channel ADC output A bit 0 (LSB)                |  |  |

| A1 <sub>R</sub>     | 115                      | red channel ADC output A bit 1                      |  |  |

| A2 <sub>R</sub>     | 116                      | red channel ADC output A bit 2                      |  |  |

| A3 <sub>R</sub>     | 117                      | red channel ADC output A bit 3                      |  |  |

| A4 <sub>R</sub>     | 118                      | red channel ADC output A bit 4                      |  |  |

| A5 <sub>R</sub>     | 119                      | red channel ADC output A bit 5                      |  |  |

| A6 <sub>R</sub>     | 120                      | red channel ADC output A bit 6                      |  |  |

| A7 <sub>R</sub>     | 121                      | red channel ADC output A bit 7 (MSB)                |  |  |

| OGND <sub>PLI</sub> | 122                      | PLL digital ground                                  |  |  |

| CKDATA              | 123                      | output data clock                                   |  |  |

| CKREFO              | 124                      | output horizontal pulse synchronized to pixel clock |  |  |

| TESTO               | 125                      | output reserved for test                            |  |  |

|                     |                          |                                                     |  |  |

**Preliminary data**

10 of 37

Table 3: Pin description...continued

| Symbol                | Pin         | Description                                                                                     |

|-----------------------|-------------|-------------------------------------------------------------------------------------------------|

| V <sub>CCO(PLL)</sub> | 126         | PLL output supply voltage                                                                       |

| n.c.                  | 127         | not connected                                                                                   |

| DGND1                 | 128         | digital ground 1                                                                                |

| ŌĒ                    | 129         | output enable; active LOW (when $\overline{\text{OE}}$ is HIGH, the outputs are high-impedance) |

| PD                    | 130         | power-down control input (IC is in Power-down mode when this pin is HIGH)                       |

| CLP                   | 131         | clamp pulse input (clamp active HIGH)                                                           |

| HSYNC                 | 132         | horizontal synchronization pulse input                                                          |

| INV                   | 133         | PLL clock output inverter control input (invert when HIGH)                                      |

| CKEXT                 | 134         | external clock input                                                                            |

| COAST                 | 135         | PLL coast control input                                                                         |

| CKREF                 | 136         | PLL reference clock input                                                                       |

| V <sub>CCD1</sub>     | 137         | digital supply voltage 1                                                                        |

| n.c.                  | 138         | not connected                                                                                   |

| AGND <sub>PLL</sub>   | 139         | PLL analog ground                                                                               |

| СР                    | 140         | PLL filter input                                                                                |

| CZ                    | 141         | PLL filter input                                                                                |

| AGND <sub>PLL</sub>   | 142         | PLL analog ground                                                                               |

| V <sub>CCA(PLL)</sub> | 143         | PLL analog supply voltage                                                                       |

| n.c.                  | 144         | not connected                                                                                   |

| $GND_DP$              | exposed die | e pad connection                                                                                |

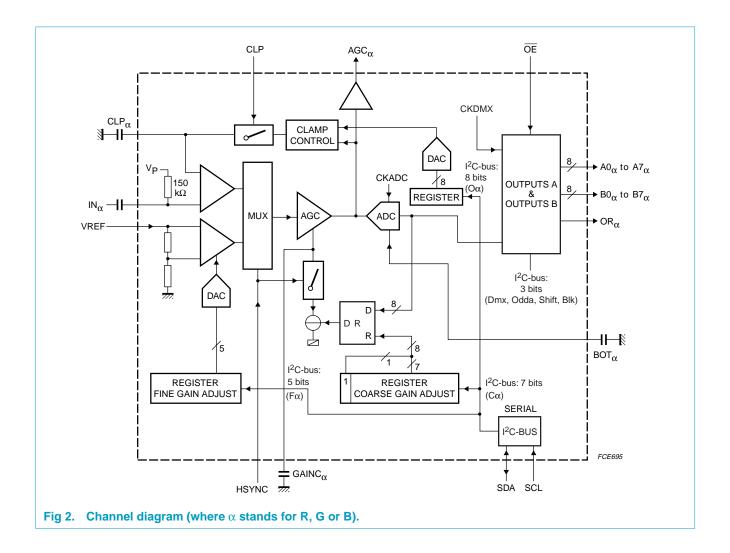

# 8. Functional description

This triple high-speed 8-bit ADC is designed to convert RGB/YUV signals, coming from an analog source, into digital data used by a LCD driver (pixel clock up to 205 MHz).

### 8.1 Analog video inputs

The RGB/YUV video inputs are externally AC coupled and are internally DC polarized.

The synchronization signals are also used by the device for the internal PLL and the gain calibration.

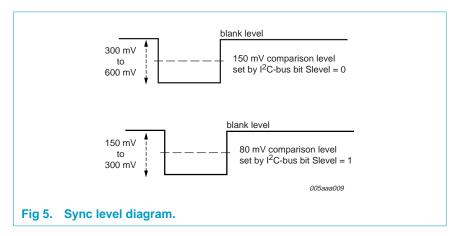

If the green video signal has composite sync (sync on green) it is possible to extract this composite sync by connecting the green signal to pin IN<sub>SOG</sub> (AC coupled). When the sync pulse amplitude is below 300 mV, the I<sup>2</sup>C-bus bit 'Slevel' has to be set to logic 1 (see Figure 5). The maximum amplitude for the sync pulse is 600 mV typical.

The composite sync is available at pin SOG<sub>O</sub> (TTL level compatible signal).

If this function is not used, pin  $\mathsf{IN}_{\mathsf{SOG}}$  should be connected to the analog power supply. In this event pin  $\mathsf{SOG}_{\mathsf{O}}$  is at LOW-level TTL.

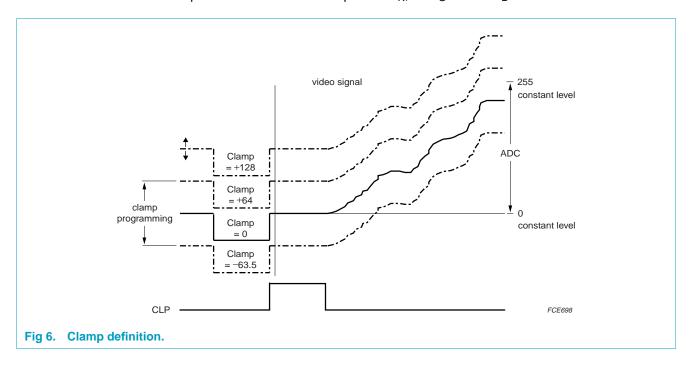

# 8.2 Clamps

Three independent parallel clamping circuits are used to clamp the video input signals on several black levels. The clamping levels may be set from -63.5 to +64 LSBs (RGB) and from +120 to +136 LSBs in steps of  $\frac{1}{2}$  LSB (YUV). They are controlled by changing the values in three 8-bit registers: OFFSETR, OFFSETG and OFFSETB (see Table 5). Each clamp must be able to correct an offset from  $\pm 100$  mV to  $\pm 10$  mV within 300 ns, and correct the total offset in 10 lines.

The clamping is done using the following principle: On the incoming of a TTL positive going pulse supplied on pin CLP, three external capacitors are loaded independently by the device in order to change the voltage level of each analog RGB input. The capacitors are connected to pins CLP<sub>R</sub>, CLP<sub>G</sub> and CLP<sub>B</sub>.

9397 750 09549

#### 8.2.1 Variable gain amplifiers

Three independent variable gain amplifiers are used to provide, for each channel, a full-scale input signal to the 8-bit ADC. The gain adjustment range is designed so that for an input range varying from 0.4 to 1.2 V (p-p), the output signal corresponds to the ADC full-scale input of 1 V (p-p).

To ensure that the gain does not vary over the whole operating temperature range a reference voltage  $V_{ref}$  = 2.5 V (DC), with a maximum variation of 100 ppm/°C, is supplied externally on pin VREF.

The calibration of the gains is done using the following principle. On the incoming of a pulse supplied to pin HSYNC, an internal multiplexer switches from the RGB video signals to a reference voltage ( ${}^{1}\!\!/_{16}V_{ref}$ ). The ADCs inputs become this reference signal and the three corresponding outputs are compared to pre-set values loaded in three 7-bit registers: COARSER, COARSEG and COARSEB. Depending on the result of the comparisons, the three gains are adjusted such that the ADC outputs become equal to the pre-set values in the registers. The three gains are simply controlled by changing the values in the COARSE registers.

The signal supplied on pin HSYNC, may be selected active HIGH or active LOW. The choice is done through the serial interface by setting bit 'Hlevel' in the control register (active HIGH when bit Hlevel = 0).

This active part of the signal has to occur during the blanking period of the signal in order not to interrupt the active video. Normally the horizontal synchronization signal, provided by the video source, is connected to pin HSYNC.

The values loaded in the gain registers (COARSER, COARSEG, COARSEB) are chosen among 68 values (see Table 6).

A fine correction is also used to finely tune the gain on the three channels and to compensate the channel-to-channel gain mismatch. The fine correction is done using the following principle: the three binary codes, stored in the three 5-bit registers (FINER, FINEG and FINEB) are converted into three analog voltages (with three DACs) and are independently added to the reference voltage ( $\frac{1}{16}V_{ref}$ ). Thus, three different reference voltages are used for the gain calibration of the three channels.

When the COARSE registers are set at full-scale, the resolution of the fine registers corresponds to  $\frac{1}{2}$  LSB peak-to-peak (see Equation 3).

#### 8.2.2 Important recommendations

The clamping and the gain calibration requisite two external signals (pulses). One signal is connected to pin CLP and the other is connected to pin HSYNC. It is very important that:

- The active part of these two signals occur during the blanking of the video signal, in order not to interrupt or disturb the active video.

- The active part of these two signals does not overlap on each other, in order to perform correctly the gain calibration and the clamping. Normally the clamp pulse is sent after the end of the horizontal synchronization pulse.

#### 8.2.3 ADCs

Three ADCs convert analog signals into three series of 8-bit codes, with a maximum clock frequency of 205 Msps. The ADCs input range is 1 V (p-p) full-scale and the pipeline delay is 1 clock cycle from the sampling to the data output. The reference ladders regulators are integrated.

#### 8.2.4 Data outputs

ADC outputs are straight binary. Pin  $\overline{OE}$  enables to switch the output status between active and high-impedance ( $\overline{OE}$  = HIGH). It is possible to force the outputs with a maximum 10 pF capacitive load. The timing must be checked very carefully if the capacitive loads are more than 10 pF.

It is possible to force the outputs to logic 0 during the gain calibration (during HSYNC pulse) and during the clamping (CLP pulse). This mode is activated through the serial interface by setting bit 'Blk' to logic 1 in register DEMUX.

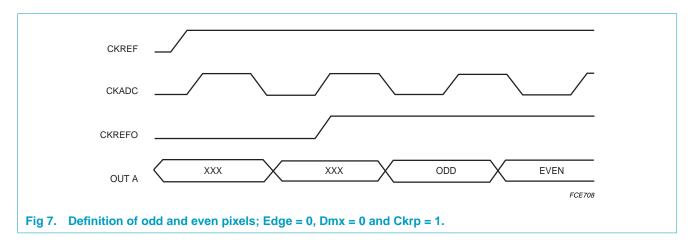

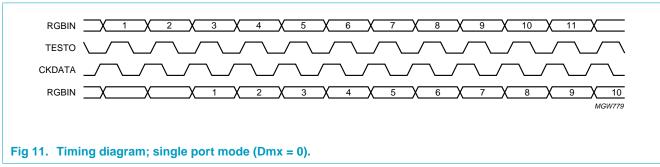

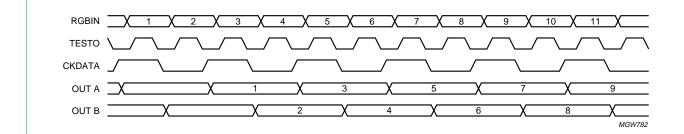

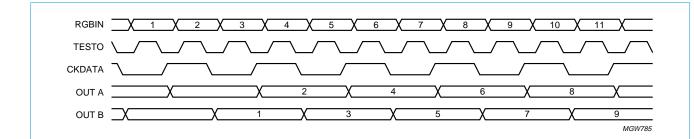

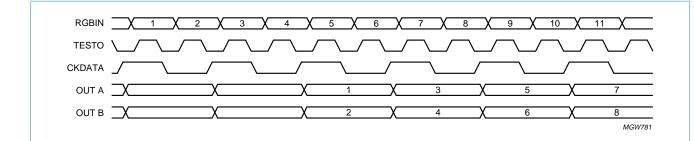

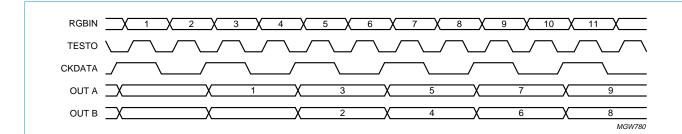

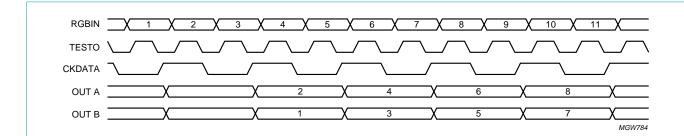

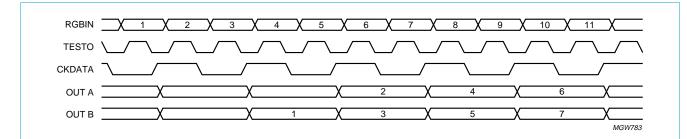

The TDA8757A provides outputs either on one port (port A) or on two ports (ports A and B). The selection is made with the serial interface by setting bit 'Dmx' to logic 0 or logic 1 in register DEMUX. When just one port is used (Dmx = 0), the unused ports are forced to LOW level. When two ports are used (Dmx = 1), it is possible to select the port that would provide the odd pixel by setting bit 'Odda' to logic 1 or logic 0 in register DEMUX; when this bit is logic 1, odd pixel on output of port A.

One out-of-range bit exists per channel (OR<sub>R</sub>, OR<sub>G</sub> and OR<sub>B</sub>). It will be at logic 1 when the signal is out-of-range of the ADC voltage ladder.

Finally, two configurations are possible: either the port A outputs and the port B outputs are both synchronous or they are interleaved. The selection is done by setting bit 'Shift' to logic 0 or logic 1 in register DEMUX.

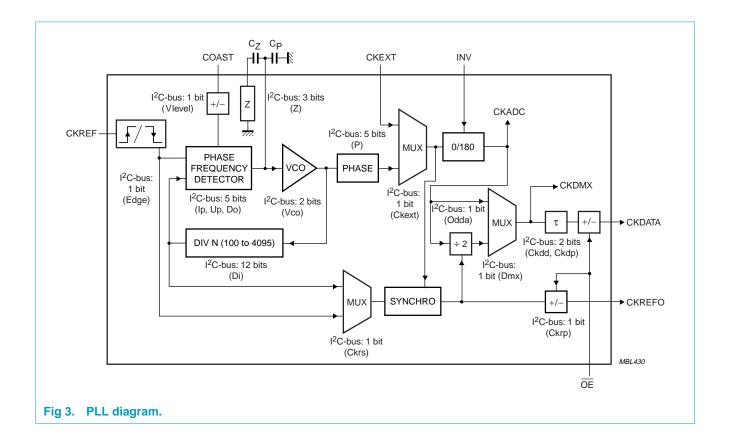

#### 8.2.5 PLL

The ADCs are clocked by either the internal PLL locked to the reference clock CKREF or an external clock connected to pin CKEXT. All parts of the PLL are on-chip except the loop filter capacitance. The selection is performed via the serial interface by setting bit 'Ckext' in register PHASE (Ckext = 1 when the external clock is used).

9397 750 09549

The reference clock (CKREF) range is between 15 and 150 kHz. Consequently, the VCO minimum frequency is 12 MHz and the maximum frequency is 205 MHz. The gain of the VCO part can be controlled through the serial interface, depending on the frequency range to which the PLL is locked.

Moreover, the PLL may be locked either on the rising or on the falling edge of the CKREF signal pulses. This choice is made via the serial interface by setting bit 'Edge' in register CONTROL (rising edge when bit 'Edge' = 0).

The charge pump current ( $I_{cp}$ ) enables to increase the PLL bandwidth. It is programmable through the serial interface by setting bits 'Ip2', 'Ip1' and 'Ip0' in the control register (see Table 8).

Different resistance values (R) for the filter can also be programmed through the serial interface by setting the bits 'Z2', 'Z1' and 'Z0' in register VCO (see Table 9).

To have optimal PLL performance, R and I<sub>cp</sub> must be chosen so that:

- The result of the product 'R × I<sub>cp</sub>' is smaller than a determined limit (Lim)

- The result of the product 'R × I<sub>cp</sub>' is as close as possible to this limit (Lim).

$$Lim = \frac{0.3\pi \times DR_{PLL} \times f_{ref}}{K_0} \tag{1}$$

#### where:

- DR<sub>PLL</sub> = the divider ratio, which is the ratio between the pixel frequency and the horizontal line frequency of the incoming signal. The setting of this parameter is performed through the serial interface with bits Di0 to Di11. These bits are present in the VCO-, divider- and phase registers.

- f<sub>ref</sub> = the frequency of the signal.

- K<sub>0</sub> = the VCO gain, which depends on the pixel frequency ranges given in Table 10.

In the event that several combinations of R and  $I_{cp}$  give the same result, a calculating of the damping factor ( $\xi$ ) for each couple becomes necessary.

The combination of R and  $I_{cp}$  whose damping factor is the closest to 1.5, generates the optimal PLL performance.

$$\xi = \frac{R \cdot C_Z}{2} \cdot \sqrt{\frac{K_0 \cdot I_{cp}}{DR_{PLL} \cdot (C_Z + C_P)}} \tag{2}$$

where  $C_Z$  and  $C_P$  are the external capacitors of the PLL loop filter. The recommended values are:  $C_Z = 68$  nF and  $C_P = 150$  pF.

Pin COAST is used to disconnect the PLL phase frequency detector during the frame flyback (vertical blanking) or the unavailability of the CKREF signal. This signal can normally be derived from the VSYNC signal.

The COAST signal may be active either HIGH or LOW by setting bit 'Vlevel' in the control register, through the serial interface (Vlevel = 0 when HIGH).

9397 750 09549

It is possible to control the phase of the ADC clock (CKADC), through the serial interface, with the included digital phase-shift controller. The phase register (5 bits) enables to shift the phase by steps of 11.25 deg.

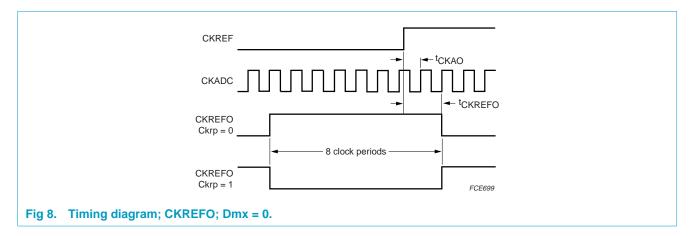

The CKREF signal is resynchronized by the synchro-block on the CKADC clock. The new reference is available on pin CKREFO. This synchronization may be done either with the CKREF signal directly, or with the output of the divider in the PLL (see Figure 3).

The selection is done via the serial interface by setting bit 'Ckrs' in the phase register (Ckrs = 1 when the CKREF signal is used). The polarity of the signal on pin CKREFO is controlled through the serial interface by setting bit 'Ckrp' in register DEMUX (positive polarity if Ckrp = 0). The width of this signal is fixed to 8 clock cycles.

The PLL provides also a CKDATA clock. This clock is synchronized on the data outputs whatever the output mode is.

It is possible to delay the CKDATA clock with a constant time ( $\tau=3$  ns, compared to the outputs) by setting bit 'Ckdd' to logic 1 in register DEMUX. Moreover, it is possible to reverse the CKDATA clock, referenced to the outputs, by setting bit 'Ckdp' in register DEMUX.

The maximum capacitive load for each clock output is 10 pF.

If an external clock is used, it has to be connected to pin CKEXT. Bit 'Ckext' and bit 'Ckrs' in the phase register have to be set at logic 1. Moreover, it is also important to disconnect the internal PLL by using the following settings:

- Set bit 'Do' in the control register to logic 1.

- Set bits 'Vco1' and 'Vco0' in register VCO to logic 0.

There is a delay between the input signal on pin CKREF and the corresponding output on pin CKREFO; see Figure 8. This delay is t<sub>CKREFO</sub>:

$t_{CKREFO}$  = either  $t_{CKAO}$  (if clock phase >01000) or  $t_{CKAO}$  +  $T_{CLK(pixel)}$  (if phase <01000)

$t_{CKAO} = t_{CLK(buffer)} + t_{phase selector}$

$t_{CLK(buffer)}$  = tbf and  $t_{phase \ selector} = \left(\frac{phase}{2\pi}\right) \cdot T_{CLK(pixel)}$

9397 750 09549

**Preliminary data**

# 9. I<sup>2</sup>C-bus and 3W-bus interfaces

# 9.1 Register definitions

The configuration of the registers is given in Table 4.

Table 4: I<sup>2</sup>C-bus and 3W-bus registers

| Function         | Sub | add       | ress      | ;         |    |           |            |    | Bit def | inition |         |      |      |       |      |     | Default   |

|------------------|-----|-----------|-----------|-----------|----|-----------|------------|----|---------|---------|---------|------|------|-------|------|-----|-----------|

| name             | Α7  | <b>A6</b> | <b>A5</b> | <b>A4</b> | А3 | <b>A2</b> | <b>A</b> 1 | A0 | MSB     |         |         |      |      |       |      | LSB | value     |

| SUBADDR          |     |           |           |           |    |           |            |    | Χ       | Х       | Χ       | Mode | Sa3  | Sa2   | Sa1  | Sa0 | XXX1 0000 |

| OFFSETR          | Χ   | Χ         | Χ         | Χ         | 0  | 0         | 0          | 0  | Or7     | Or6     | Or5     | Or4  | Or3  | Or2   | Or1  | Or0 | 0111 1111 |

| COARSER          | Χ   | Χ         | Χ         | Χ         | 0  | 0         | 0          | 1  | Or8     | Cr6     | Cr5     | Cr4  | Cr3  | Cr2   | Cr1  | Cr0 | 0010 0000 |

| FINER            | Χ   | Χ         | Χ         | Χ         | 0  | 0         | 1          | 0  | Χ       | Testvol | Testvoh | Fr4  | Fr3  | Fr2   | Fr1  | Fr0 | X000 0000 |

| OFFSETG          | Χ   | Χ         | Χ         | Χ         | 0  | 0         | 1          | 1  | Og7     | Og6     | Og5     | Og4  | Og3  | Og2   | Og1  | Og0 | 0111 1111 |

| COARSEG          | Χ   | Χ         | Χ         | Χ         | 0  | 1         | 0          | 0  | Og8     | Cg6     | Cg5     | Cg4  | Cg3  | Cg2   | Cg1  | Cg0 | 0010 0000 |

| FINEG            | Χ   | Χ         | Χ         | Χ         | 0  | 1         | 0          | 1  | Χ       | X       | Slevel  | Fg4  | Fg3  | Fg2   | Fg1  | Fg0 | XX00 0000 |

| OFFSETB          | Χ   | Χ         | Χ         | Χ         | 0  | 1         | 1          | 0  | Ob7     | Ob6     | Ob5     | Ob4  | Ob3  | Ob2   | Ob1  | Ob0 | 0111 1111 |

| COARSEB          | Χ   | Χ         | Χ         | Χ         | 0  | 1         | 1          | 1  | Ob8     | Cb6     | Cb5     | Cb4  | Cb3  | Cb2   | Cb1  | Cb0 | 0010 0000 |

| FINEB            | Χ   | Χ         | Χ         | Χ         | 1  | 0         | 0          | 0  | Χ       | X       | Cken    | Fb4  | Fb3  | Fb2   | Fb1  | Fb0 | XX00 0000 |

| CONTROL          | Χ   | Χ         | Χ         | Χ         | 1  | 0         | 0          | 1  | Vlevel  | Hlevel  | Edge    | Up   | Do   | lp2   | lp1  | lp0 | 0000 0111 |

| VCO              | Χ   | Χ         | Χ         | Χ         | 1  | 0         | 1          | 0  | Z2      | Z1      | Z0      | Vco1 | Vco0 | Di11  | Di10 | Di9 | 1011 1011 |

| DIVIDER<br>(LSB) | Χ   | Χ         | Χ         | Χ         | 1  | 0         | 1          | 1  | Di8     | Di7     | Di6     | Di5  | Di4  | Di3   | Di2  | Di1 | 0100 1100 |

| PHASE            | Χ   | Χ         | Χ         | Χ         | 1  | 1         | 0          | 0  | Di0     | Ckrs    | Ckext   | P4   | P3   | P2    | P1   | P0  | 0000 0000 |

| DEMUX            | Χ   | Χ         | Χ         | Χ         | 1  | 1         | 0          | 1  | Blk     | Shpixel | Ckrp    | Ckdp | Ckdd | Shift | Odda | Dmx | 1000 0111 |

#### 9.1.1 Subaddress

All the registers are defined by a subaddress of 7 bits: bit Mode refers to the mode which is used with the I<sup>2</sup>C-bus interface, bits 'Sa3' to 'Sa0' give the subaddress of each register.

Bit Mode, used only with the I<sup>2</sup>C-bus, allows two modes for the programming:

Mode 0 Each register is programmed independently, by giving its subaddress and its content.

Mode 1 All the registers are programmed one after the other, by giving this initial condition (XXX1 1111) as the subaddress state; thus, the registers are changed following the predefined sequence of 16 bytes (from subaddress 0000 to 1101).

The default values correspond to a VESA 1280  $\times$  1024 at 75 Hz graphic mode.

#### 9.1.2 Offset register

This register controls the clamp level for the RGB channels. The relationship between the programming code and the level of the clamp code is given in Table 5.

9397 750 09549

Table 5: Coding

| Programmed code | Clamp code | ADC output |  |

|-----------------|------------|------------|--|

| 0               | -63.5      |            |  |

| 1               | -63        | underflow  |  |

| 2               | -62.5      | - undernow |  |

|                 |            |            |  |

| 127             | 0          | 0          |  |

|                 |            |            |  |

| 254             | 63.5       | 63 or 64   |  |

| 255             | 64         | 64         |  |

| 256             | 120        | 120        |  |

|                 |            |            |  |

| 287             | 136        | 136        |  |

The default programmed value is:

- Programmed code = 127

- Clamp code = 0

- ADC output = 0.

### 9.1.3 Coarse and Fine registers

These two registers enable the gain control, the AGC gain with the coarse register and the reference voltage with the fine register. The coarse register programming equation is as follows:

$$GAIN = \left(\frac{N_{COARSE} + 1}{V_{ref} \cdot \left(1 - \frac{N_{FINE}}{32 \times 16}\right)}\right) \times \frac{1}{16} = \left(\frac{N_{COARSE} + 1}{V_{ref} \cdot (512 - N_{FINE})}\right) \times 32$$

(3)

Where:  $V_{ref} = 2.5 \text{ V}$ .

The gain correspondence is given in Table 6. The gain is linear with reference to the programming code ( $N_{\text{FINE}} = 0$ ).

Table 6: Typical gain correspondence (COARSE)

| N <sub>COARSE</sub> | Gain  | V <sub>i</sub> to be full-scale (V) |

|---------------------|-------|-------------------------------------|

| 32                  | 0.825 | 1.212                               |

| 99                  | 2.5   | 0.4                                 |

The default programmed value is as follows:

- N<sub>COARSE</sub> = 32

- Gain = 0.825

- V<sub>i</sub> to be full-scale = 1.212.

To modulate this gain, the fine register is programmed using the above equation. With a full-scale ADC input, the fine register resolution is a  $\frac{1}{2}$  LSB peak-to-peak (see Table 7 for N<sub>COARSE</sub> = 32).

Table 7: Typical gain correspondence (FINE)

| N <sub>FINE</sub> | Gain  | V <sub>i</sub> to be full-scale (V) |

|-------------------|-------|-------------------------------------|

| 0                 | 0.825 | 1.212                               |

| 31                | 0.878 | 1.139                               |

The default programmed value is:  $N_{FINE} = 0$ .

#### 9.1.4 Control register

COAST and HSYNC signals can be derived by setting the I<sup>2</sup>C-bus control bits 'Vlevel' and 'Hlevel' respectively. When bits 'Vlevel' and 'Hlevel' are set to zero, COAST and HSYNC are active HIGH.

Bit 'Edge' defines the rising or falling edge of CKREF to synchronize the PLL. It will be on the rising edge if the bit is a logic 0 and on the falling edge if the bit is at logic 1.

Bits 'Up' and 'Do' are used for the test, to force the charge pump current. These bits have to be logic 0 during normal use.

Bit 'Cken' is used for the test to check the CKADC internal signal. This bit has to be logic 0 during normal use.

Bits 'lp0', 'lp1' and 'lp2' control the charge pump current, to increase the bandwidth of the PLL, as shown in Table 8.

Table 8: Charge pump current control

| lp2 | lp1 | lp0 | Current (μA) |

|-----|-----|-----|--------------|

| 0   | 0   | 0   | 6.25         |

| 0   | 0   | 1   | 12.5         |

| 0   | 1   | 0   | 25           |

| 0   | 1   | 1   | 50           |

| 1   | 0   | 0   | 100          |

| 1   | 0   | 1   | 200          |

| 1   | 1   | 0   | 400          |

| 1   | 1   | 1   | 700          |

The default programmed value is as follows:

- Charge pump current = 700 μA

- Bits 'Up' and 'Do' are used for testing, normally they are set to logic 0

- Rising edge of CKREF: bit 'Edge' at logic 0

- COAST and HSYNC inputs are active HIGH: bits 'Vlevel' and 'Hlevel' at logic 0.

### 9.1.5 VCO register

Bits 'Z2', 'Z1' and 'Z0' enable the internal resistance for the VCO filter to be selected.

Table 9: VCO register bits

| <b>Z</b> 2 | Z1 | Z0 | Resistance (k $\Omega$ ) |

|------------|----|----|--------------------------|

| 0          | 0  | 0  | high-impedance           |

| 0          | 0  | 1  | 9                        |

| 0          | 1  | 0  | 6.4                      |

| 0          | 1  | 1  | 4.5                      |

| 1          | 0  | 0  | 3.2                      |

| 1          | 0  | 1  | 2.25                     |

| 1          | 1  | 0  | 1.6                      |

| 1          | 1  | 1  | 1.1                      |

Bits 'Vco1' and 'Vco0' control the VCO gain.

Table 10: VCO gain control

| Vco1 | Vco0 | VCO gain (MHz/V) | Pixel clock<br>frequency range<br>(MHz) |

|------|------|------------------|-----------------------------------------|

| 0    | 0    | 20               | 12 to 28                                |

| 0    | 1    | 30               | 28 to 55                                |

| 1    | 0    | 60               | 55 to 115                               |

| 1    | 1    | 115              | 115 to 205                              |

The default programmed value is as follows:

- Internal resistance =  $2.25 \text{ k}\Omega$

- VCO gain = 70 MHz/V.

#### 9.1.6 Divider register

This register controls the PLL frequency. Bits 'Di8' to 'Di0' are the LSB bits. The default programmed value is 0110 1001 1000 = 1688.

The MSB bits ('Di11', 'Di10' and 'Di9') and the LSB bit 'Di0' have to be programmed before bits 'Di8' to 'Di1' in order to have the required divider ratio. Bit 'Di0' is used for the parity divider number (Di0 = 0: even number; Di0 = 1: odd number). It should be noted that if the  $I^2C$ -bus programming is done in mode 1 and the bit 'Di0' has to be toggled, then the registers have to be loaded twice to have the update divider ratio.

## 9.1.7 Phase register

Bit 'Ckext' is logic 0 when the used clock is the PLL clock and logic 1 when the used clock is the external clock.

Bit 'Ckrs' is logic 1 when the synchronization is done with CKREF (see Figure 3).

Bits 'P4' to 'P0' are used to program the phase shift for clock CKDATA.

Table 11: Phase registers bits

| P4 | P3 | P2 | P1 | P0 | Phase shift (deg) |

|----|----|----|----|----|-------------------|

| 0  | 0  | 0  | 0  | 0  | 0                 |

| 0  | 0  | 0  | 0  | 1  | 11.25             |

|    |    |    |    |    |                   |

| 1  | 1  | 1  | 1  | 0  | 337.5             |

| 1  | 1  | 1  | 1  | 1  | 348.75            |

The default programmed value is as follows:

- No external clock: bit 'Ckext' is logic 0

- Phase shift for CKDATA is 0 deg.

#### 9.1.8 DEMUX register

The default programming is:

- Outputs forced to logic 0 during CLP and HSYNC pulses: bit 'Blk' = 1

- First pixel not shifted: bit 'Shpixel' = 0

- CKREFO with positive polarity: bit 'Ckrp' = 0

- CKDATA not reversed: bit 'Ckdp' = 0

- CKDATA not delayed: bit 'Ckdd' = 0

- Interleaved outputs: bit 'Shift' = 1

- Odd pixels on port A: bit 'Odda' = 1.

- Demultiplexed outputs: bit 'Dmx' = 1

For timing diagrams concerning various settings of this register, see Figure 11 - 13.

#### 9.1.9 Power-down mode

- When the supply is completely switched off, the registers are set to their default values; in that event they have to be reprogrammed if the required settings are different (e.g. through an EEPROM)

- When the device is in Power-down mode (pin PD = HIGH), the previously programmed register values remain unaffected.

### 9.2 I<sup>2</sup>C-bus protocol

Table 12: Register format

| A6 | A5 | A4 | А3 | A2 | A1 | Α0 | RW |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 1  | 1  | A2 | A1 | 0  |

The address of the circuit for the I<sup>2</sup>C-bus is 1001 1XX0.

Bits 'A1' and 'A0' are fixed by the potential on pins A2 and A1. Bit 'RW' must always be equal to logic 0 because it is not possible to read the data in the register. The timing and protocol for the I<sup>2</sup>C-bus are standard. Two sequences are available; see Table 13 and 14.

9397 750 09549

Table 13: Address sequence for mode 0

S = START condition, A = acknowledge bit (generated by the device) and P = STOP condition.

| S | IC ADDRESS A | SUBADDRESS A | DATA          | Α | SUBADDRESS A P |

|---|--------------|--------------|---------------|---|----------------|

|   |              | REGISTER1    | REGISTER1     |   | REGISTER2      |

|   |              |              | (see Table 4) |   |                |

#### Table 14: Address sequence for mode 1

S = START condition, A = acknowledge bit (generated by the device) and P = STOP condition.

| S | IC ADDRESS A | SUBADDRESS A | DATA          | Α | DATA      | Α | <br>Р |

|---|--------------|--------------|---------------|---|-----------|---|-------|

|   |              | XX11 1111    | REGISTER1     |   | REGISTER2 |   |       |

|   |              |              | (see Table 4) |   |           |   |       |

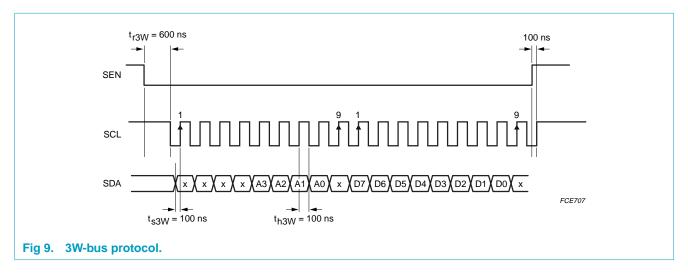

## 9.3 3W-bus protocol

For the 3W-bus, the first byte refers to the register address which is programmed. The second byte refers to the data to be sent to the chosen register (see Table 4).

Using a 3W-bus interface, an indefinite number of ICs can operate on the same system. Pin SEN is used to validate the circuits.

# 10. Limiting values

Table 15: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol    | Parameter                    | Conditions | Min  | Max  | Unit |

|-----------|------------------------------|------------|------|------|------|

| $V_{CCA}$ | analog supply voltage        |            | -0.3 | +7.0 | V    |

| $V_{DDD}$ | logic supply voltage         |            | -0.3 | +7.0 | V    |

| $V_{CCD}$ | digital supply voltage       |            | -0.3 | +7.0 | V    |

| $V_{CCO}$ | output stages supply voltage |            | -0.3 | +7.0 | V    |

Table 15: Limiting values...continued

In accordance with the Absolute Maximum Rating System (IEC 60134).

|                  |                            | • • •                 |      |      |      |

|------------------|----------------------------|-----------------------|------|------|------|

| Symbol           | Parameter                  | Conditions            | Min  | Max  | Unit |

| $\Delta V_{CC}$  | supply voltage differences |                       |      |      |      |

|                  | $V_{CCA} - V_{CCD}$        |                       | -1.0 | +1.0 | V    |

|                  | $V_{CCO} - V_{CCD}$        |                       | -1.0 | +1.0 | V    |

|                  | $V_{CCO} - V_{DDD}$        |                       | -1.0 | +1.0 | V    |

|                  | $V_{CCA} - V_{DDD}$        |                       | -1.0 | +1.0 | V    |

|                  | $V_{CCD} - V_{DDD}$        |                       | -1.0 | +1.0 | V    |

|                  | $V_{CCA} - V_{CCO}$        |                       | -1.0 | +1.0 | V    |

| $V_{i(RGB)}$     | RGB input voltage range    | referenced<br>to AGND | -0.3 | +7.0 | V    |

| Io               | output current             |                       | _    | 10   | mA   |

| T <sub>stg</sub> | storage temperature        |                       | -55  | +150 | °C   |

| T <sub>amb</sub> | ambient temperature        |                       | 0    | 70   | °C   |

| Tj               | junction temperature       |                       | _    | 150  | °C   |

|                  |                            |                       |      |      |      |

# 11. Thermal characteristics

**Table 16: Typical thermal characteristics**

| Symbol        | Parameter                                   | Conditions  | Value | Unit |

|---------------|---------------------------------------------|-------------|-------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | 30    | K/W  |

# 12. Characteristics

#### **Table 17: Characteristics**

$V_{CCA} = 4.75~V$  to 5.25~V (referenced to AGND);  $V_{CCD} = 4.75~V$  to 5.25~V (referenced to DGND);  $V_{DDD} = 4.75~V$  to 5.25~V (referenced to  $V_{SSD}$ );  $V_{CCO} = 4.75~V$  to 5.25~V (referenced to OGND); AGND, DGND, OGND and  $V_{SS}$  connected together;  $T_{amb} = 0$  to  $70~^{\circ}C$ ; typical values measured at  $V_{CCA} = V_{DDD} = V_{CCD} = V_{CCO} = 5~V$  and  $T_{amb} = 25~^{\circ}C$ ; unless otherwise specified.

| Symbol                                                                                  | Parameter                                                 | Conditions | Min  | Тур | Max  | Unit |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|------------|------|-----|------|------|

| Supplies                                                                                |                                                           |            |      |     |      |      |

| $V_{\text{CCA(PLL)}}, \\ V_{\text{CCA(R)}}, \\ V_{\text{CCA(G)}}, \\ V_{\text{CCA(B)}}$ | analog supply voltage for PLL and the RGB channels        |            | 4.75 | 5.0 | 5.25 | V    |

| $V_{DDD}$                                                                               | logic supply voltage for I <sup>2</sup> C-bus and 3W-bus  |            | 4.75 | 5.0 | 5.25 | V    |

| V <sub>CCD</sub>                                                                        | digital supply voltage                                    |            | 4.75 | 5.0 | 5.25 | V    |

| $V_{\text{CCO(PLL)}}, \\ V_{\text{CCO(R)}}, \\ V_{\text{CCO(G)}}, \\ V_{\text{CCO(B)}}$ | output stages supply voltage for PLL and the RGB channels |            | 4.75 | 5.0 | 5.25 | V    |

| I <sub>CCA(PLL)</sub>                                                                   | analog PLL supply current                                 |            | _    | 34  | _    | mA   |

9397 750 09549

Table 17: Characteristics...continued

$V_{CCA} = 4.75 \ V$  to  $5.25 \ V$  (referenced to AGND);  $V_{CCD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to DGND);  $V_{DDD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to V<sub>SSD</sub>);  $V_{CCO} = 4.75 \ V$  to  $5.25 \ V$  (referenced to OGND); AGND, DGND, OGND and  $V_{SS}$  connected together;  $T_{amb} = 0$  to  $70 \ ^{\circ}C$ ; typical values measured at  $V_{CCA} = V_{DDD} = V_{CCD} = V_{CCO} = 5 \ V$  and  $T_{amb} = 25 \ ^{\circ}C$ ; unless otherwise specified.

| Symbol                                                                                                                          | Parameter                                                    | Conditions                                                                                                  | Min   | Тур   | Max   | Unit   |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| $I_{CCA(R)}, I_{CCA(G)}, I_{CCA(B)}$                                                                                            | analog supply current for the RGB channels                   |                                                                                                             | _     | 135   | _     | mA     |

| I <sub>DDD</sub>                                                                                                                | logic supply current for I <sup>2</sup> C-bus and 3W-bus     |                                                                                                             | -     | 1     | _     | mA     |

| I <sub>CCD</sub>                                                                                                                | digital supply current                                       |                                                                                                             | _     | 95    | _     | mA     |

| $\begin{split} &I_{CCO(R),} \\ &I_{CCO(G),} \\ &I_{CCO(B),} \\ &I_{CCO(PLL)} \end{split}$                                       | output stages supply current for the RGB channels            | sine wave input                                                                                             | -     | 80    | _     | mA     |

| Icca(R), Icca(G): Icca(B) IDDD ICCD ICCO(R), ICCO(G), ICCO(B), ICCO(PLL) ΔVcc  Ptot Ppd R, G and B and B tset(ADC+AGC)  GCOARSE | supply voltage difference                                    |                                                                                                             |       |       |       |        |

|                                                                                                                                 | $V_{CCA} - V_{CCD}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

|                                                                                                                                 | $V_{CCO} - V_{CCD}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

|                                                                                                                                 | $V_{CCO} - V_{DDD}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

|                                                                                                                                 | $V_{CCA} - V_{DDD}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

|                                                                                                                                 | $V_{CCD} - V_{DDD}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

|                                                                                                                                 | $V_{CCA} - V_{CCO}$                                          |                                                                                                             | -0.25 | _     | +0.25 | V      |

| P <sub>tot</sub>                                                                                                                | total power dissipation                                      | sine wave input                                                                                             | _     | 1.7   | _     | W      |

| $P_{pd}$                                                                                                                        | power dissipation in Power-down mode                         |                                                                                                             | _     | 55    | _     | mW     |

| R, G and B am                                                                                                                   | plifiers                                                     |                                                                                                             |       |       |       |        |

| В                                                                                                                               | bandwidth                                                    | $-3$ dB; $T_{amb} = 25$ °C                                                                                  | 250   | _     | _     | MHz    |

| t <sub>set(ADC+AGC)</sub>                                                                                                       | settling time of the block<br>ADC + AGC                      | full-scale (black to white)<br>transition; input signal<br>settling time <1 ns; settling<br>to within 2 LSB | -     | 4     | _     | ns     |

| G <sub>COARSE</sub>                                                                                                             | coarse gain range                                            | minimum coarse gain;<br>code = 32                                                                           | _     | -1.67 | _     | dB     |

|                                                                                                                                 |                                                              | maximum coarse gain;<br>code = 99                                                                           | -     | 8     | -     | dB     |

| G <sub>FINE</sub>                                                                                                               | fine gain correction range                                   | minimum fine input code = 0                                                                                 | _     | 0     | _     | dB     |

|                                                                                                                                 |                                                              | maximum fine input code = 31                                                                                | _     | -0.5  | _     | dB     |

| $\Delta G_{amp} / \Delta T$                                                                                                     | amplifier gain stability variation with temperature          | V <sub>ref</sub> with 100 ppm/°C maximum variation                                                          | _     | 325   | _     | ppm/°C |

| I <sub>GC</sub>                                                                                                                 | gain current                                                 |                                                                                                             | _     | ±20   | _     | μΑ     |

| t <sub>stab</sub>                                                                                                               | amplifier gain adjustment speed from minimum to maximum gain | HSYNC active; capacitors<br>on pins 8, 16 and 24 are<br>22 nF                                               | -     | 25    | -     | mdB/μs |

|                                                                                                                                 |                                                              |                                                                                                             |       | 0.5   |       | \ /    |

| V <sub>ref</sub>                                                                                                                | amplifier reference voltage                                  |                                                                                                             | _     | 2.5   | _     | V      |

Table 17: Characteristics...continued

$V_{CCA} = 4.75 \ V$  to  $5.25 \ V$  (referenced to AGND);  $V_{CCD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to DGND);  $V_{DDD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to V<sub>SSD</sub>);  $V_{CCO} = 4.75 \ V$  to  $5.25 \ V$  (referenced to OGND); AGND, DGND, OGND and  $V_{SS}$  connected together;  $T_{amb} = 0$  to  $70 \ ^{\circ}C$ ; typical values measured at  $V_{CCA} = V_{DDD} = V_{CCD} = V_{CCO} = 5 \ V$  and  $T_{amb} = 25 \ ^{\circ}C$ ; unless otherwise specified.

| Symbol                  | Parameter                                       | Conditions                                                                                | Min | Тур    | Max   | Unit |

|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|-----|--------|-------|------|

| $V_{i(p-p)}$            | input voltage<br>(peak-to-peak value)           | corresponding to full-scale input at high gain                                            | -   | 0.4    | -     | V    |

|                         |                                                 | corresponding to full-scale output at low gain                                            | _   | _      | 1.212 | V    |

| Ci                      | input capacitance                               |                                                                                           | _   | 10     | _     | pF   |

| $G_{E(rms)}$            | channel-to-channel gain matching (RMS value)    | maximum coarse gain;<br>T <sub>amb</sub> = 25 °C                                          | _   | 1      | -     | %    |

|                         |                                                 | minimum coarse gain;<br>T <sub>amb</sub> = 25 °C                                          | _   | 5      | -     | %    |

| Clamps                  |                                                 |                                                                                           |     |        |       |      |

| P <sub>CLP</sub>        | precision                                       | maximum black level noise<br>on RGB channels = 10 mV;<br>$T_{amb}$ = 25 °C                | _   | 0.5    | -     | LSB  |

| t <sub>W(CLP)</sub>     | clamp pulse width                               |                                                                                           | 500 | _      | 2000  | ns   |

| CLP <sub>E</sub>        | channel-to-channel clamp matching               |                                                                                           | _   | 0.5    | _     | LSB  |

| A <sub>off</sub>        | code clamp reference                            | clamp register input code = 0                                                             | _   | -63.5  | _     | LSB  |

|                         |                                                 | clamp register input code = 255                                                           | _   | +64    | _     | LSB  |

|                         |                                                 | clamp register input code = 256                                                           | -   | +120   | _     | LSB  |

|                         |                                                 | clamp register input code = 287                                                           | _   | +135.5 | _     | LSB  |

| Phase-locked            | loop (PLL)                                      |                                                                                           |     |        |       |      |

| jPLL(max)(p-p)          | long term PLL phase jitter (peak-to-peak value) | f <sub>clk</sub> = 205 MHz                                                                | -   | 336    | _     | ps   |

| DR                      | divider ratio                                   |                                                                                           | 100 | _      | 4095  | _    |

| f <sub>ref</sub>        | reference clock frequency                       |                                                                                           | 15  | _      | 150   | kHz  |

| f <sub>PLL</sub>        | output clock frequency                          |                                                                                           | 12  | _      | 205   | MHz  |

| $\Delta\Phi_{\sf step}$ | phase drift <sup>[1]</sup>                      | standard at 160 Msps                                                                      | _   | _      | 2     | step |

| $\Phi_{\sf step}$       | phase shift step                                | $T_{amb} = 25  ^{\circ}C$                                                                 | _   | 11.25  | _     | deg  |

| ADCs                    |                                                 |                                                                                           |     |        |       |      |

| f <sub>s</sub>          | maximum sampling frequency                      |                                                                                           | 205 | _      | _     | MHz  |

| INL                     | DC integral non-linearity                       | from IC analog input to<br>digital output; sine wave<br>input; f <sub>clk</sub> = 205 MHz | -   | ±0.5   | ±1.5  | LSB  |

| DNL                     | DC differential non-linearity                   | from IC analog input to<br>digital output; sine wave<br>input; f <sub>clk</sub> = 205 MHz | _   | ±0.4   | ±1    | LSB  |

| ENOB <sup>[2]</sup>     | effective number of bits                        |                                                                                           | _   | 7.4    | _     | bits |

9397 750 09549

Table 17: Characteristics...continued

$V_{CCA} = 4.75 \ V$  to  $5.25 \ V$  (referenced to AGND);  $V_{CCD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to DGND);  $V_{DDD} = 4.75 \ V$  to  $5.25 \ V$  (referenced to V<sub>SSD</sub>);  $V_{CCO} = 4.75 \ V$  to  $5.25 \ V$  (referenced to OGND); AGND, DGND, OGND and  $V_{SS}$  connected together;  $T_{amb} = 0$  to  $70 \ ^{\circ}C$ ; typical values measured at  $V_{CCA} = V_{DDD} = V_{CCD} = V_{CCO} = 5 \ V$  and  $T_{amb} = 25 \ ^{\circ}C$ ; unless otherwise specified.

| Symbol                | Parameter                                    | Conditions                                                 | Min       | Тур       | Max | Unit |

|-----------------------|----------------------------------------------|------------------------------------------------------------|-----------|-----------|-----|------|

| Signal-to-no          | oise ratio                                   |                                                            |           |           |     |      |

| S/N                   | signal-to-noise ratio                        | $f_{clk} = 205 \text{ MHz}$                                | _         | 46        | _   | dB   |

| Spurious fre          | ee dynamic range                             |                                                            |           |           |     |      |

| SFDR                  | spurious free dynamic range                  | $f_{clk} = 205 \text{ MHz}$                                | _         | 57        | _   | dB   |

| Clock timing          | g output (CKDATA)                            |                                                            |           |           |     |      |

| η <sub>ext</sub>      | ADC clock duty factor                        |                                                            | 45        | 50        | 55  | %    |

| f <sub>clk(max)</sub> | maximum clock frequency                      |                                                            | _         | _         | 205 | MHz  |

| Clock timing          | g input (CKEXT)                              |                                                            |           |           |     |      |

| f <sub>clk(max)</sub> | maximum clock frequency                      |                                                            | _         | _         | 205 | MHz  |

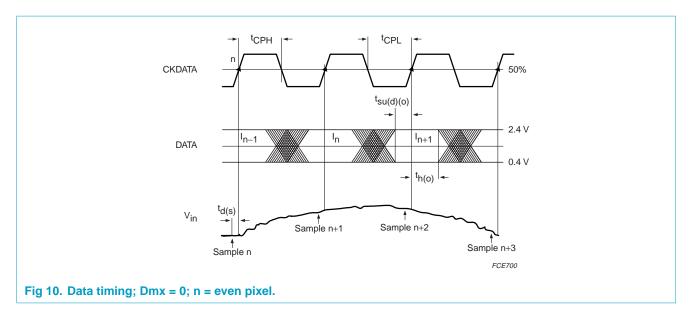

| t <sub>CPH</sub>      | clock pulse width HIGH                       |                                                            | 2.5       | _         | _   | ns   |

| t <sub>CPL</sub>      | clock pulse width LOW                        |                                                            | 2.5       | _         | _   | ns   |

| Data timing           | [3]                                          |                                                            |           |           |     |      |

| t <sub>d(s)</sub>     | sampling delay time                          | referenced to CKDATA                                       | -         | -7.5      | _   | ns   |

| t <sub>su(d)(o)</sub> | output data set-up time                      |                                                            | _         | <b>-7</b> | _   | ns   |

| t <sub>h(o)</sub>     | output hold time                             |                                                            | _         | 1         | _   | ns   |

| 3-state outp          | ut delay time                                |                                                            |           |           |     |      |

| t <sub>dZH</sub>      | output enable HIGH                           |                                                            | _         | 15        | _   | ns   |