# **ADC1213S series**

Single 12-bit ADC; 65 Msps, 80 Msps, 105 Msps or 125 Msps; serial JESD204A interface

Rev. 1 — 14 March 2011

**Product data sheet**

## 1. General description

The ADC1213S is a single channel 12-bit Analog-to-Digital Converter (ADC) optimized for high dynamic performance and low power at sample rates up to 125 Msps. Pipelined architecture and output error correction ensure the ADC1213S is accurate enough to guarantee zero missing codes over the entire operating range. Supplied from a 3 V source for analog and a 1.8 V source for the output driver, it outputs data in serial mode via a single differential lane, which complies with the JESD204A standard. The integration of Serial Peripheral Interface (SPI) allows the user to easily configure the ADCs and the serial output modes. The device also includes a programmable full-scale SPI to allow a flexible input voltage range from 1 V (p-p) to 2 V (p-p).

Excellent dynamic performance is maintained from the baseband to input frequencies of 170 MHz or more, making the ADC1213S ideal for use in communications, imaging, and medical applications.

#### 2. Features and benefits

- SNR, 70 dBFS; SFDR, 86 dBc

- Sample rates up to 125 Msps

- Single channel, 12-bit pipelined ADC core

- 3 V, 1.8 V power supplies

- Flexible input voltage range: 1 V (p-p) to 2 V (p-p)

- Serial output

- Compliant with JESD204A serial transmission standard

- Pin compatible with ADC1613S series, ADC1413S series, and ADC1113S125

- Input bandwidth, 600 MHz

- Power dissipation, 550 mW at 80 Msps

- SPI register programming

- Duty cycle stabilizer

- High Intermediate Frequency (IF) capability

- Offset binary, two's complement, gray code

- Power-down mode and Sleep mode

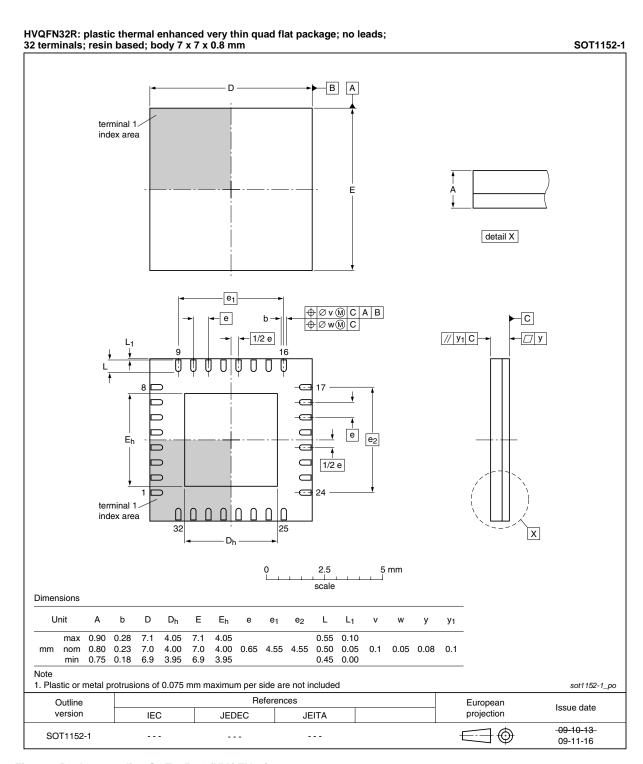

- HVQFN32 package

# 3. Applications

- Wireless and wired broadband communications

- Spectral analysis

- Ultrasound equipment

- Portable instrumentation

- Imaging systems

# 4. Ordering information

#### Table 1. Ordering information

| Type number      | Sampling                                                                                                                                                                                                                                                                                                                     | Package  |                                                                                                                            |           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------|-----------|

|                  | frequency (Msps)     Name     Description       125     HVQFN32R     plastic thermal enhand no leads; 32 terminal body 7 × 7 × 0.8 mm       105     HVQFN32R     plastic thermal enhand no leads; 32 terminal body 7 × 7 × 0.8 mm       80     HVQFN32R     plastic thermal enhand no leads; 32 terminal body 7 × 7 × 0.8 mm |          | Description                                                                                                                | Version   |

| ADC1213S125HN/C1 | 125                                                                                                                                                                                                                                                                                                                          | HVQFN32R | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; resin based; body $7\times7\times0.8$ mm     | SOT1152-1 |

| ADC1213S105HN/C1 | 105                                                                                                                                                                                                                                                                                                                          | HVQFN32R | no leads; 32 terminals; resin based;                                                                                       | SOT1152-1 |

| ADC1213S080HN/C1 | 80                                                                                                                                                                                                                                                                                                                           | HVQFN32R | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; resin based; body $7 \times 7 \times 0.8$ mm | SOT1152-1 |

| ADC1213S065HN/C1 | 65                                                                                                                                                                                                                                                                                                                           | HVQFN32R | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; resin based; body $7\times7\times0.8$ mm     | SOT1152-1 |

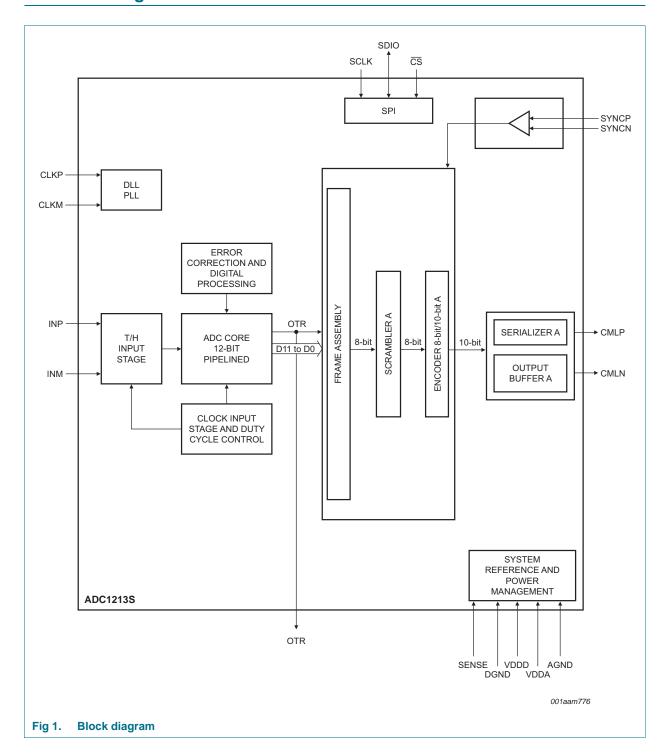

# 5. Block diagram

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

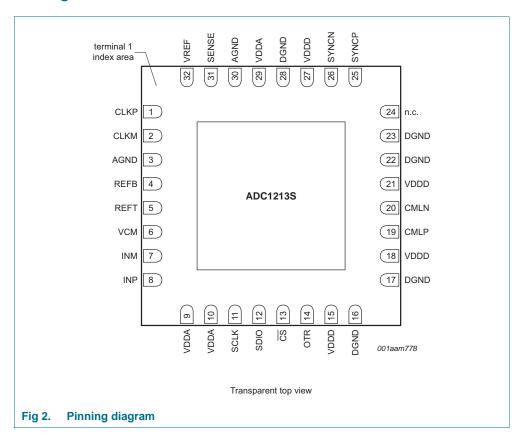

# 6. Pinning information

### 6.1 Pinning

#### 6.2 Pin description

Table 2. Pin description

|        | -   |         |                                |

|--------|-----|---------|--------------------------------|

| Symbol | Pin | Type[1] | Description                    |

| CLKP   | 1   | I       | clock input                    |

| CLKM   | 2   | I       | complementary clock input      |

| AGND   | 3   | G       | analog ground                  |

| REFB   | 4   | 0       | ADC bottom reference           |

| REFT   | 5   | 0       | ADC top reference              |

| VCM    | 6   | 0       | ADC output common voltage      |

| INM    | 7   | I       | ADC complementary analog input |

| INP    | 8   | I       | ADC analog input               |

| VDDA   | 9   | Р       | analog power supply 3 V        |

| VDDA   | 10  | Р       | analog power supply 3 V        |

| SCLK   | 11  | I       | SPI clock                      |

| SDIO   | 12  | I/O     | SPI data input/output          |

ADC1213S SER

All information provided in this document is subject to legal disclaimers.

Table 2. Pin description ...continued

| Symbol | Pin | Type[1] | Description                                       |

|--------|-----|---------|---------------------------------------------------|

| CS     | 13  | I       | chip select                                       |

| OTR    | 14  | 0       | out-of-range information                          |

| VDDD   | 15  | Р       | digital power supply 1.8 V                        |

| DGND   | 16  | G       | digital ground                                    |

| DGND   | 17  | G       | digital ground                                    |

| VDDD   | 18  | Р       | digital power supply 1.8 V                        |

| CMLP   | 19  | 0       | serial output                                     |

| CMLN   | 20  | 0       | serial complementary output                       |

| VDDD   | 21  | Р       | digital power supply 1.8 V                        |

| DGND   | 22  | G       | digital ground                                    |

| DGND   | 23  | G       | digital ground                                    |

| n.c.   | 24  | -       | not connected                                     |

| SYNCP  | 25  | I       | positive synchronization signal from the receiver |

| SYNCN  | 26  | I       | negative synchronization signal from the receiver |

| VDDD   | 27  | Р       | digital power supply 1.8 V                        |

| DGND   | 28  | G       | digital ground                                    |

| VDDA   | 29  | Р       | analog power supply 3 V                           |

| AGND   | 30  | G       | analog ground                                     |

| SENSE  | 31  | I       | reference programming pin                         |

| VREF   | 32  | I/O     | voltage reference input/output                    |

<sup>[1]</sup> P: power supply; G: ground; I: input; O: output; I/O: input/output.

# 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                      | Conditions | Min  | Max  | Unit |

|-----------------------|--------------------------------|------------|------|------|------|

| $V_{DDA}$             | analog supply voltage          |            | -0.4 | +4.6 | V    |

| V <sub>DDD(1V8)</sub> | digital supply voltage (1.8 V) |            | -0.4 | +2.5 | V    |

| T <sub>stg</sub>      | storage temperature            |            | -55  | +125 | °C   |

| T <sub>amb</sub>      | ambient temperature            |            | -40  | +85  | °C   |

| Tj                    | junction temperature           |            | -    | 125  | °C   |

# 8. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions |     | Тур  | Unit |

|----------------------|---------------------------------------------|------------|-----|------|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient |            | [1] | 25.6 | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | [1] | 8.6  | K/W  |

<sup>[1]</sup> Value for six layers board in still air with a minimum of 25 thermal vias.

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

# 9. Static characteristics

Table 5. Static characteristics [1]

| Symbol                 | Parameter                        | Conditions                              | Min          | Тур  | Max          | Unit |

|------------------------|----------------------------------|-----------------------------------------|--------------|------|--------------|------|

| Supplies               |                                  |                                         |              | •    |              |      |

| $V_{DDA}$              | analog supply voltage            |                                         | 2.85         | 3.0  | 3.4          | V    |

| V <sub>DDD(1V8)</sub>  | digital supply voltage (1.8 V)   |                                         | 1.65         | 1.8  | 1.95         | V    |

| I <sub>DDA</sub>       | analog supply current            | $f_{clk}$ = 125 Msps;<br>$f_i$ = 70 MHz | -            | 185  | -            | mA   |

| I <sub>DDD(1V8)</sub>  | digital supply current (1.8 V)   | $f_{clk}$ = 125 Msps;<br>$f_i$ = 70 MHz | -            | 75   | -            | mA   |

| P <sub>tot</sub>       | total power dissipation          | f <sub>clk</sub> = 125 Msps             | -            | 690  | -            | mW   |

|                        |                                  | $f_{clk} = 105 \text{ Msps}$            | -            | 625  | -            | mW   |

|                        |                                  | f <sub>clk</sub> = 80 Msps              | -            | 550  | -            | mW   |

|                        |                                  | f <sub>clk</sub> = 65 Msps              | -            | 495  | -            | mW   |

| Р                      | power dissipation                | Power-down mode                         | -            | 30   | -            | mW   |

|                        |                                  | Standby mode                            | -            | 150  | -            | mW   |

| Clock input            | s: pins CLKP and CLKM (          | AC-coupled)                             |              |      |              |      |

| Low-Voltage            | Positive Emitter-Coupled L       | .ogic (LVPECL)                          |              |      |              |      |

| V <sub>i(clk)dif</sub> | differential clock input voltage | peak-to-peak                            | -            | 1.6  | -            | V    |

| SINE                   |                                  |                                         |              |      |              |      |

| V <sub>i(clk)dif</sub> | differential clock input voltage | peak                                    | ±0.8         | ±3.0 | -            | V    |

| Low Voltage            | Complementary Metal Oxid         | de Semiconductor (LVCMC                 | OS)          |      |              |      |

| $V_{IL}$               | LOW-level input voltage          |                                         | -            | -    | $0.3V_{DDA}$ | V    |

| V <sub>IH</sub>        | HIGH-level input voltage         | )                                       | $0.7V_{DDA}$ | -    | -            | V    |

| SPI: pins C            | S, SDIO, and SCLK                |                                         |              |      |              |      |

| V <sub>IL</sub>        | LOW-level input voltage          |                                         | 0            | -    | $0.3V_{DDA}$ | V    |

| V <sub>IH</sub>        | HIGH-level input voltage         | )                                       | $0.7V_{DDA}$ | -    | $V_{DDA}$    | V    |

| I <sub>IL</sub>        | LOW-level input current          |                                         | -10          | -    | +10          | μΑ   |

| l <sub>iH</sub>        | HIGH-level input current         | !                                       | <b>-50</b>   | -    | +50          | μΑ   |

| Cı                     | input capacitance                |                                         | -            | 4    | -            | pF   |

| Analog inpu            | uts: pins INP and INM            |                                         |              |      |              |      |

| l <sub>l</sub>         | input current                    | track mode                              | <b>-</b> 5   | -    | +5           | μΑ   |

| R <sub>I</sub>         | input resistance                 | track mode                              | -            | 15   | -            | Ω    |

| Cı                     | input capacitance                | track mode                              | -            | 5    | -            | pF   |

| $V_{I(cm)}$            | common-mode input voltage        | track mode                              | 1.1          | 1.5  | 2            | V    |

| B <sub>i</sub>         | input bandwidth                  |                                         | -            | 600  | -            | MHz  |

| $V_{I(dif)}$           | differential input voltage       | peak-to-peak                            | 1            | -    | 2            | V    |

|                        |                                  |                                         |              |      |              |      |

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

Table 5. Static characteristics ... continued [1]

| Symbol              | Parameter                                  | Conditions                                       | Min                       | Тур                 | Max        | Unit                |

|---------------------|--------------------------------------------|--------------------------------------------------|---------------------------|---------------------|------------|---------------------|

|                     | ntrolled regulator output: p               | in VCM                                           |                           |                     |            |                     |

| V <sub>O(cm)</sub>  | common-mode output voltage                 |                                                  | -                         | 0.5V <sub>DDA</sub> | -          | V                   |

| $I_{O(cm)}$         | common-mode output<br>current              |                                                  | -                         | 4                   | -          | mA                  |

| Reference           | voltage input/output: pin V                | REF                                              |                           |                     |            |                     |

| V <sub>VREF</sub>   | voltage on pin VREF                        | output                                           | 0.5                       | -                   | 1          | V                   |

|                     |                                            | input                                            | 0.5                       | -                   | 1          | V                   |

| Data outpu          | ts: pins CMLP, CMLN                        |                                                  |                           |                     |            |                     |

| Output leve         | Is, $V_{DDD(1V8)} = 1.8 \text{ V}$ ; SWING | _SEL[2:0] = 000                                  |                           |                     |            |                     |

| V <sub>OL</sub>     | LOW-level output                           | DC-coupled; output                               | -                         | 1.5                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.35                | -          | V                   |

| V <sub>OH</sub>     | HIGH-level output                          | DC-coupled; output                               | -                         | 1.8                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.65                | -          | V                   |

| Output leve         | Is, $V_{DDD(1V8)} = 1.8 \text{ V}$ ; SWING | _SEL[2:0] = 001                                  |                           |                     |            |                     |

| $V_{OL}$            | LOW-level output                           | DC-coupled; output                               | -                         | 1.45                | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.275               | -          | V                   |

| V <sub>OH</sub>     | HIGH-level output                          | DC-coupled; output                               | -                         | 1.8                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.625               | -          | V                   |

| Output leve         | Is, $V_{DDD(1V8)} = 1.8 \text{ V}$ ; SWING | _SEL[2:0] = 010                                  |                           |                     |            |                     |

| $V_{OL}$            | LOW-level output                           | DC-coupled; output                               | -                         | 1.4                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.2                 | -          | V                   |

| V <sub>OH</sub>     | HIGH-level output                          | DC-coupled; output                               | -                         | 1.8                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.6                 | -          | V                   |

| Output leve         | Is, $V_{DDD(1V8)} = 1.8 \text{ V}$ ; SWING | _SEL[2:0] = 011                                  |                           |                     |            |                     |

| V <sub>OL</sub>     | LOW-level output                           | DC-coupled; output                               | -                         | 1.35                | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.125               | -          | V                   |

| V <sub>OH</sub>     | HIGH-level output                          | DC-coupled; output                               | -                         | 1.8                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.575               | -          | V                   |

| Output leve         | Is, $V_{DDD(1V8)} = 1.8 \text{ V}$ ; SWING | _SEL[2:0] = 100                                  |                           |                     |            |                     |

| V <sub>OL</sub>     | LOW-level output                           | DC-coupled; output                               | -                         | 1.3                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.05                | -          | V                   |

| V <sub>OH</sub>     | HIGH-level output                          | DC-coupled; output                               | -                         | 1.8                 | -          | V                   |

|                     | voltage                                    | AC-coupled                                       | -                         | 1.55                | -          | V                   |

| Serial conf         | iguration: pins SYNCP, SYN                 | NCN                                              |                           |                     |            |                     |

| V <sub>IL</sub>     | LOW-level input voltage                    | differential; input                              | -                         | 0.95                | -          | V                   |

| V <sub>IH</sub>     | HIGH-level input voltage                   | differential; input                              | -                         | 1.47                | -          | V                   |

| Accuracy            |                                            |                                                  |                           |                     |            |                     |

| INL                 | integral non-linearity                     |                                                  | -5                        | -                   | +5         | LSE                 |

| DNL                 | differential non-linearity                 | guaranteed no missing codes                      | -0.95                     | ±0.5                | +0.95      | LSE                 |

| E <sub>offset</sub> | offset error                               |                                                  | -                         | ±2                  | -          | mV                  |

| ADC1213S_SER        |                                            | All information provided in this document is sub | ject to legal disclaimers |                     | © NXP B.V. | 2011. All rights re |

Table 5. Static characteristics ... continued [1]

| Symbol | Parameter                    | Conditions                                       | Min | Тур        | Max | Unit |

|--------|------------------------------|--------------------------------------------------|-----|------------|-----|------|

| $E_G$  | gain error                   | full-scale                                       | -   | $\pm~0.5$  | -   | %    |

| Supply |                              |                                                  |     |            |     |      |

| PSRR   | power supply rejection ratio | 200 mV (p-p) on pin<br>VDDA; f <sub>i</sub> = DC | -   | <b>–54</b> | -   | dB   |

<sup>[1]</sup> Typical values measured at  $V_{DDA}=3$  V,  $V_{DDD(1V8)}=1.8$  V,  $T_{amb}=25$  °C. Minimum and maximum values are across the full temperature range  $T_{amb}=-40$  °C to +85 °C at  $V_{DDA}=3$  V,  $V_{DDD(1V8)}=1.8$  V;  $V_{i(INP)}-V_{i(INM)}=-1$  dBFS; internal reference mode; 100  $\Omega$  differential applied to serial outputs; unless otherwise specified.

# 10. Dynamic characteristics

Product data sheet

#### 10.1 Dynamic characteristics

| Table 6. Dynamic characteristics [1] |

|--------------------------------------|

|--------------------------------------|

| Symbol                        | Parameter                            | Conditions               | AD  | C1213S | 065 | AD  | C1213S | 080 | AD  | C1213S | 105 | ADC1213S125 |      |     | Unit |

|-------------------------------|--------------------------------------|--------------------------|-----|--------|-----|-----|--------|-----|-----|--------|-----|-------------|------|-----|------|

|                               |                                      |                          | Min | Тур    | Max | Min | Тур    | Max | Min | Тур    | Max | Min         | Тур  | Max |      |

| α <sub>2H</sub>               | second harmonic                      | $f_i = 3 \text{ MHz}$    | -   | 87     | -   | -   | 87     | -   | -   | 86     | -   | -           | 88   | -   | dBc  |

|                               | level                                | $f_i = 30 \text{ MHz}$   | -   | 86     | -   | -   | 86     | -   | -   | 86     | -   | -           | 87   | -   | dBc  |

|                               |                                      | $f_i = 70 \text{ MHz}$   | -   | 85     | -   | -   | 85     | -   | -   | 84     | -   | -           | 85   | -   | dBc  |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 82     | -   | -   | 82     | -   | -   | 81     | -   | -           | 83   | -   | dBc  |

| αзн                           | α <sub>3H</sub> third harmonic level | f <sub>i</sub> = 3 MHz   | -   | 86     | -   | -   | 86     | -   | -   | 85     | -   | -           | 87   | -   | dBc  |

|                               |                                      | $f_i = 30 \text{ MHz}$   | -   | 85     | -   | -   | 85     | -   | -   | 85     | -   | -           | 86   | -   | dBc  |

|                               |                                      | $f_i = 70 \text{ MHz}$   | -   | 84     | -   | -   | 84     | -   | -   | 83     | -   | -           | 84   | -   | dBc  |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 81     | -   | -   | 81     | -   | -   | 80     | -   | -           | 82   | -   | dBc  |

| THD total harmonic distortion | f <sub>i</sub> = 3 MHz               | -                        | 83  | -      | -   | 83  | -      | -   | 82  | -      | -   | 84          | -    | dBc |      |

|                               | distortion                           | $f_i = 30 \text{ MHz}$   | -   | 82     | -   | -   | 82     | -   | -   | 82     | -   | -           | 83   | -   | dBc  |

|                               |                                      | $f_i = 70 \text{ MHz}$   | -   | 81     | -   | -   | 81     | -   | -   | 80     | -   | -           | 81   | -   | dBc  |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 78     | -   | -   | 78     | -   | -   | 77     | -   | -           | 79   | -   | dBc  |

| ENOB                          | effective number of bits             | f <sub>i</sub> = 3 MHz   | -   | 11.3   | -   | -   | 11.3   | -   | -   | 11.3   | -   | -           | 11.3 | -   | bits |

|                               |                                      | $f_i = 30 \text{ MHz}$   | -   | 11.3   | -   | -   | 11.3   | -   | -   | 11.3   | -   | -           | 11.2 | -   | bits |

|                               |                                      | $f_i = 70 \text{ MHz}$   | -   | 11.2   | -   | -   | 11.2   | -   | -   | 11.2   | -   | -           | 11.2 | -   | bits |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 11.1   | -   | -   | 11.1   | -   | -   | 11.1   | -   | -           | 11.1 | -   | bits |

| SNR                           | signal-to-noise ratio                | f <sub>i</sub> = 3 MHz   | -   | 70.0   | -   | -   | 69.9   | -   | -   | 69.8   | -   | -           | 69.6 | -   | dBFS |

|                               |                                      | $f_i = 30 \text{ MHz}$   | -   | 69.5   | -   | -   | 69.5   | -   | -   | 69.5   | -   | -           | 69.4 | -   | dBFS |

|                               |                                      | $f_i = 70 \text{ MHz}$   | -   | 69.2   | -   | -   | 69.2   | -   | -   | 69.1   | -   | -           | 60.0 | -   | dBFS |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 68.8   | -   | -   | 68.8   | -   | -   | 68.7   | -   | -           | 68.6 | -   | dBFS |

| SFDR                          | spurious-free                        | f <sub>i</sub> = 3 MHz   | -   | 86     | -   | -   | 86     | -   | -   | 85     | -   | -           | 87   | -   | dBc  |

|                               | dynamic range                        | $f_i = 30 \text{ MHz}$   | -   | 85     | -   | -   | 85     | -   | -   | 85     | -   | -           | 86   | -   | dBc  |

|                               |                                      | f <sub>i</sub> = 70 MHz  | -   | 84     | -   | -   | 84     | -   | -   | 83     | -   | -           | 84   | -   | dBc  |

|                               |                                      | f <sub>i</sub> = 170 MHz | -   | 81     | -   | -   | 81     | -   | -   | 80     | -   | -           | 82   | -   | dBc  |

**ADC1213S series**

Product data sheet

Table 6. Dynamic characteristics ...continued[1]

| Symbol                         | Parameter               | Conditions               | AD  | ADC1213S065 |     |     | ADC1213S080 |     |     | C1213S | 105 | AD  | Unit |     |     |

|--------------------------------|-------------------------|--------------------------|-----|-------------|-----|-----|-------------|-----|-----|--------|-----|-----|------|-----|-----|

|                                |                         |                          | Min | Тур         | Max | Min | Тур         | Max | Min | Тур    | Max | Min | Тур  | Max |     |

| IMD intermodulation distortion | $f_i = 3 \text{ MHz}$   | -                        | 89  | -           | -   | 89  | -           | -   | 88  | -      | -   | 89  | -    | dBc |     |

|                                | distortion              | $f_i = 30 \text{ MHz}$   | -   | 88          | -   | -   | 88          | -   | -   | 88     | -   | -   | 88   | -   | dBc |

|                                | f <sub>i</sub> = 70 MHz | -                        | 87  | -           | -   | 87  | -           | -   | 86  | -      | -   | 86  | -    | dBc |     |

|                                |                         | f <sub>i</sub> = 170 MHz | -   | 84          | -   | -   | 85          | -   | -   | 83     | -   | -   | 84   | -   | dBc |

| $\alpha_{ct(ch)}$              | channel crosstalk       | f <sub>i</sub> = 70 MHz  | -   | 100         | -   | -   | 100         | -   | -   | 100    | -   | -   | 100  | -   | dBc |

<sup>[1]</sup> Typical values measured at  $V_{DDA} = 3 \text{ V}$ ,  $V_{DDD(1V8)} = 1.8 \text{ V}$ ,  $T_{amb} = 25 ^{\circ}\text{C}$ . Minimum and maximum values are across the full temperature range  $T_{amb} = -40 ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  at  $V_{DDA} = 3 \text{ V}$ ,  $V_{DDD(1V8)} = 1.8 \text{ V}$ ;  $V_{I(INP)} - V_{I(INM)} = -1 \text{ dBFS}$ ; internal reference mode;  $100 \Omega$  differential applied to serial outputs; unless otherwise specified.

#### 10.2 Clock and digital output timing

le 7. Clock and digital output characteristics [1]

| Table 1.               | Clock and digital out | out characteristics == |     |             |     |             |     |     |             |     |     |     |      |     |      |

|------------------------|-----------------------|------------------------|-----|-------------|-----|-------------|-----|-----|-------------|-----|-----|-----|------|-----|------|

| Symbol                 | Parameter             | Conditions             | AD  | ADC1213S065 |     | ADC1213S080 |     |     | ADC1213S105 |     |     | AD  | Unit |     |      |

|                        |                       |                        | Min | Тур         | Max | Min         | Тур | Max | Min         | Тур | Max | Min | Тур  | Max |      |

| pins CLK               | P and CLKM            |                        |     |             |     |             |     |     |             |     |     |     |      |     |      |

| f <sub>clk</sub>       | clock frequency       |                        | 20  | -           | 65  | 60          | -   | 80  | 75          | -   | 105 | 100 | -    | 125 | Msps |

| t <sub>lat(data)</sub> | data latency time     | clock cycles           | 307 | -           | 850 | 250         | -   | 283 | 190         | -   | 226 | 160 | -    | 170 | ns   |

| $\delta_{\text{clk}}$  | clock duty cycle      | DCS_EN = logic 1       | 30  | 50          | 70  | 30          | 50  | 70  | 30          | 50  | 70  | 30  | 50   | 70  | %    |

| t <sub>d(s)</sub>      | sampling delay time   | е                      | -   | 0.8         | -   | -           | 0.8 | -   | -           | 0.8 | -   | -   | 0.8  | -   | ns   |

| t <sub>wake</sub>      | wake-up time          |                        | -   | 76          | -   | -           | 76  | -   | -           | 76  | -   | -   | 76   | -   | μS   |

<sup>[1]</sup> Typical values measured at V<sub>DDA</sub> = 3 V, V<sub>DDD(1V8)</sub> = 1.8 V, T<sub>amb</sub> = 25 °C. Minimum and maximum values are across the full temperature range T<sub>amb</sub> = -40 °C to +85 °C at V<sub>DDA</sub> = 3 V, V<sub>DDD(1V8)</sub> = 1.8 V; V<sub>i(INP)</sub> - V<sub>i(INM)</sub> = -1 dBFS; internal reference mode; 100 Ω differential applied to serial outputs; unless otherwise specified.

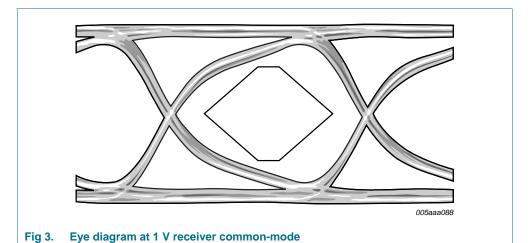

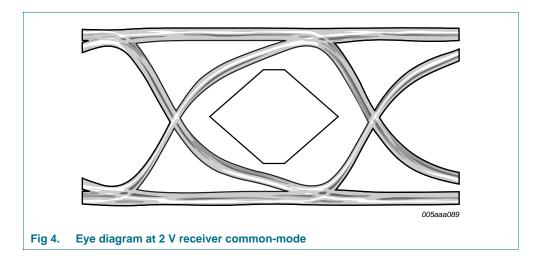

# 10.3 Serial output timing

The eye diagram of the serial output is shown in <u>Figure 3</u> and <u>Figure 4</u>. Test conditions are:

- 3.125 Gbps data rate

- T<sub>amb</sub> = 25 °C

- DC-coupling with two different receiver common-mode voltages

Downloaded from Elcodis.com electronic components distributor

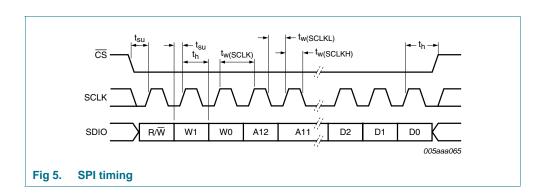

## 10.4 SPI timing

Table 8. SPI timing characteristics [1]

| Conditions<br>dth    | Min<br>-<br>-      | <b>Typ</b> 40        | Max<br>-               | <b>Unit</b><br>ns     |

|----------------------|--------------------|----------------------|------------------------|-----------------------|

|                      | -                  |                      | -                      | ns                    |

| lse                  | _                  |                      |                        |                       |

|                      |                    | 16                   | -                      | ns                    |

| lse                  | -                  | 16                   | -                      | ns                    |

| data to<br>SCLK HIGH | -                  | 5                    | -                      | ns                    |

| CS to<br>SCLK HIGH   | -                  | 5                    | -                      | ns                    |

| data to<br>SCLK HIGH | -                  | 2                    | -                      | ns                    |

| CS to<br>SCLK HIGH   | -                  | 2                    | -                      | ns                    |

| (                    | -                  | 25                   | -                      | MHz                   |

|                      | CS to<br>SCLK HIGH | CS to -<br>SCLK HIGH | CS to - 2<br>SCLK HIGH | CS to - 2 - SCLK HIGH |

[1] Typical values measured at  $V_{DDA}=3$  V,  $V_{DDD(1V8)}=1.8$  V,  $T_{amb}=25$  °C. Minimum and maximum values are across the full temperature range  $T_{amb}=-40$  °C to +85 °C at  $V_{DDA}=3$  V,  $V_{DDD(1V8)}=1.8$  V;  $V_{i(INP)}-V_{i(INM)}=-1$  dBFS; internal reference mode; 100  $\Omega$  differential applied to serial outputs; unless otherwise specified.

# 11. Application information

#### 11.1 Analog inputs

#### 11.1.1 Input stage description

The analog input of the ADC1213S supports a differential or a single-ended input drive. Optimal performance is achieved using differential inputs with the common-mode input voltage ( $V_{I(cm)}$ ) on pins INP and INM set to 0.5 $V_{DDA}$ .

The full-scale analog input voltage range is configurable between 1 V (p-p) and 2 V (p-p) via a programmable internal reference (see Section 11.2 and Table 21).

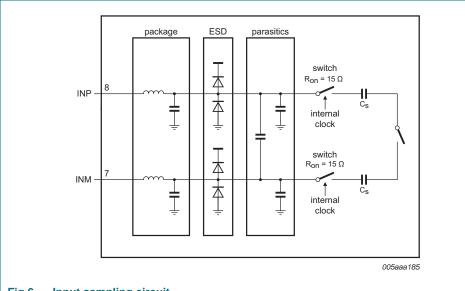

<u>Figure 6</u> shows the equivalent circuit of the sample-and-hold input stage, including ElectroStatic Discharge (ESD) protection and circuit and package parasitics.

Fig 6. Input sampling circuit

The sample phase occurs when the internal clock (derived from the clock signal on pin CLKP/CLKM) is HIGH. The voltage is then held on the sampling capacitors. When the clock signal goes LOW, the stage enters the hold phase and the voltage information is transmitted to the ADC core.

#### 11.1.2 Anti-kickback circuitry

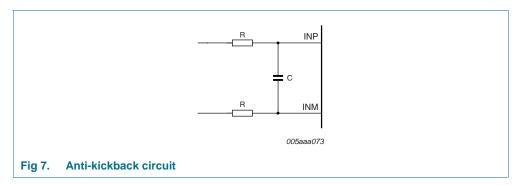

Anti-kickback circuitry (RC filter in <u>Figure 7</u>) is needed to counteract the effects of a charge injection generated by the sampling capacitance.

The RC filter is also used to filter noise from the signal before it reaches the sampling stage. The value of the capacitor should be chosen to maximize noise attenuation without degrading the settling time excessively.

ADC1213S\_SER

The component values are determined by the input frequency and should be selected so as not to affect the input bandwidth.

Table 9. RC-coupling versus input frequency, typical values

| Input frequency (MHz) | Resistance (Ω) | Capacitance (pF) |

|-----------------------|----------------|------------------|

| 3                     | 25             | 12               |

| 70                    | 12             | 8                |

| 170                   | 12             | 8                |

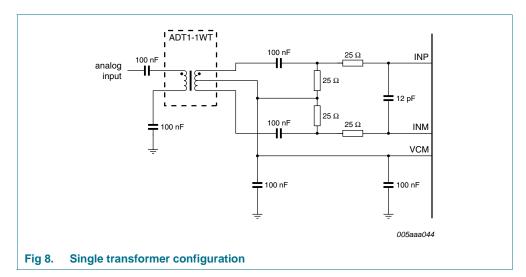

#### 11.1.3 Transformer

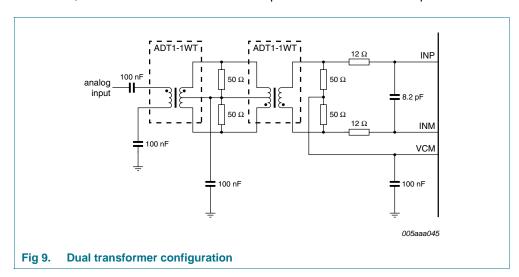

The configuration of the transformer circuit is determined by the input frequency. The configuration shown in Figure 8 would be suitable for a baseband application.

The configuration shown in <u>Figure 9</u> is recommended for high frequency applications. In both cases, the choice of transformer is a compromise between cost and performance.

#### 11.2 System reference and power management

#### 11.2.1 Internal/external reference

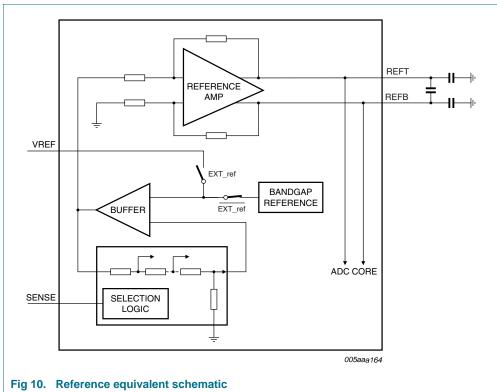

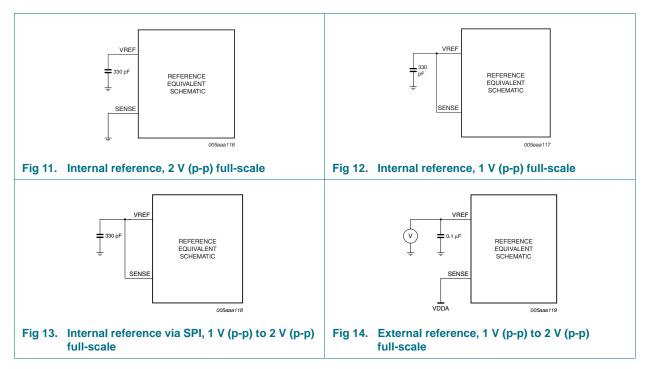

The ADC1213S has a stable and accurate built-in internal reference voltage to adjust the ADC full-scale. This reference voltage can be set internally via SPI or with pins VREF and SENSE (see Figure 11 to Figure 14), in 1 dB steps between 0 dB and –6 dB, via SPI control bits INTREF[2:0] (when bit INTREF\_EN = logic 1; see Table 21). The equivalent reference circuit is shown in Figure 10. An external reference is also possible by providing a voltage on pin VREF as described in Figure 14.

rig to. Reference equivalent schematic

If bit INTREF\_EN is set to logic 0, the reference voltage is determined either internally or externally as detailed in <u>Table 10</u>.

Table 10. Reference modes

| Mode                           | SPI bit, "Internal reference" | SENSE pin                                        | VREF pin                           | Full-scale,<br>(V (p-p)) |

|--------------------------------|-------------------------------|--------------------------------------------------|------------------------------------|--------------------------|

| Internal (Figure 11)           | 0                             | GND                                              | GND 330 pF capacitor to GND        |                          |

| Internal (Figure 12)           | 0                             | VREF pin = SENSE pin and 330 pF capacitor to GND |                                    | 1                        |

| Internal, SPI mode (Figure 13) | 1                             | VREF pin = SENSE pin and 330 pF capacitor to GND |                                    | 1 to 2                   |

| External (Figure 14)           | 0                             | $V_{DDA}$                                        | external voltage from 0.5 V to 1 V | 1 to 2                   |

<u>Figure 11</u> to <u>Figure 14</u> illustrate how to connect the SENSE and VREF pins to select the required reference voltage source.

Downloaded from Elcodis.com electronic components distributor

#### 11.2.2 Programmable full-scale

The full-scale is programmable between 1 V (p-p) to 2 V (p-p) (see <u>Table 11</u>).

Table 11. Reference SPI gain control

| INTREF[2:0] | Level (dB) | Full-scale (V (p-p)) |

|-------------|------------|----------------------|

| 000         | 0          | 2                    |

| 001         | -1         | 1.78                 |

| 010         | -2         | 1.59                 |

| 011         | -3         | 1.42                 |

| 100         | -4         | 1.26                 |

| 101         | <b>-</b> 5 | 1.12                 |

| 110         | -6         | 1                    |

| 111         | not used   | X                    |

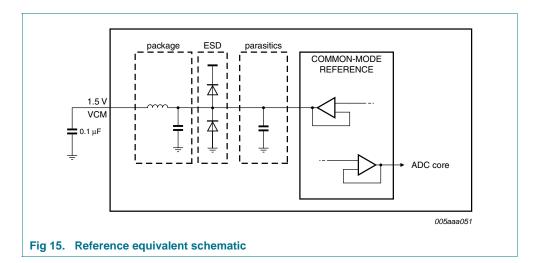

# 11.2.3 Common-mode output voltage (V<sub>O(cm)</sub>)

An 0.1  $\mu$ F filter capacitor should be connected between pin VCM and ground to ensure a low-noise common-mode output voltage. When AC-coupled, this pin can be used to set the common-mode reference for the analog inputs, for instance via a transformer middle point.

ADC1213S\_SER

Downloaded from Elcodis.com electronic components distributor

#### 11.2.4 Biasing

The common-mode input voltage  $(V_{I(cm)})$  on pins INP and INM should be set externally to  $0.5V_{DDA}$  for optimal performance and should always be between 0.9 V and 2 V.

#### 11.3 Clock input

#### 11.3.1 Drive modes

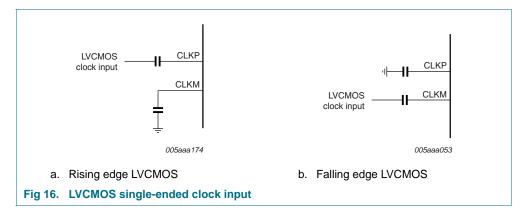

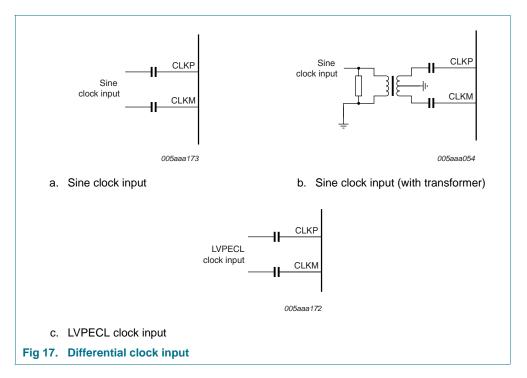

The ADC1213S can be driven differentially (LVPECL). It can also be driven by a single-ended LVCMOS signal connected to pin CLKP (CLKM should be connected to ground via a capacitor).

ADC1213S\_SER

#### 11.3.2 Equivalent input circuit

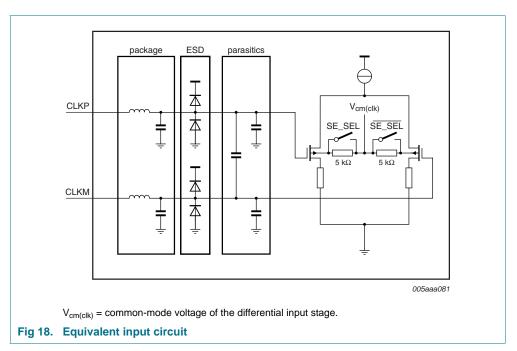

The equivalent circuit of the input clock buffer is shown in Figure 18. The common-mode voltage of the differential input stage is set via internal 5 k $\Omega$  resistors.

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

Single-ended or differential clock inputs can be selected via the SPI (see <u>Table 20</u>). If single-ended is selected, the input pin (CLKM or CLKP) is selected via control bit SE SEL.

If single-ended is implemented without setting bit SE\_SEL accordingly, the unused pin should be connected to ground via a capacitor.

#### 11.3.3 Duty cycle stabilizer

The duty cycle stabilizer can improve the overall performance of the ADC by compensating the input clock signal duty cycle. When the duty cycle stabilizer is active (bit DCS\_EN = logic 1; see  $\underline{\text{Table 20}}$ ), the circuit can handle signals with duty cycles of between 30 % and 70 % (typical). When the duty cycle stabilizer is disabled (DCS\_EN = logic 0), the input clock signal should have a duty cycle of between 45 % and 55 %.

Table 12. Duty cycle stabilizer

| bit DCS_EN | Description                   |

|------------|-------------------------------|

| 0          | duty cycle stabilizer disable |

| 1          | duty cycle stabilizer enable  |

#### 11.3.4 Clock input divider

The ADC1213S contains an input clock divider that divides the incoming clock by a factor of 2 (when bit CLKDIV2\_SEL = logic 1; see <u>Table 20</u>). This feature allows the user to deliver a higher clock frequency with better jitter performance, leading to a better SNR result once acquisition has been performed.

#### 11.4 Digital outputs

#### 11.4.1 Serial output equivalent circuit

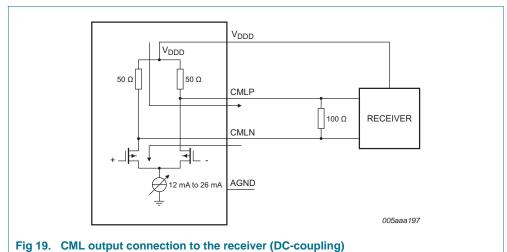

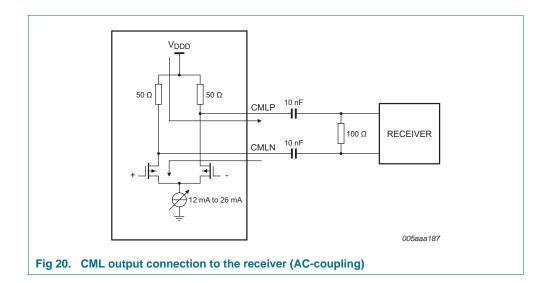

The JESD204A standard specifies that if the receiver and the transmitter are DC-coupled, both must be fed from the same supply.

The output should be terminated when 100  $\Omega$  (typical) is reached at the receiver side.

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

20 of 39

#### 11.5 JESD204A serializer

For more information about the JESD204A standard refer to the JEDEC web site.

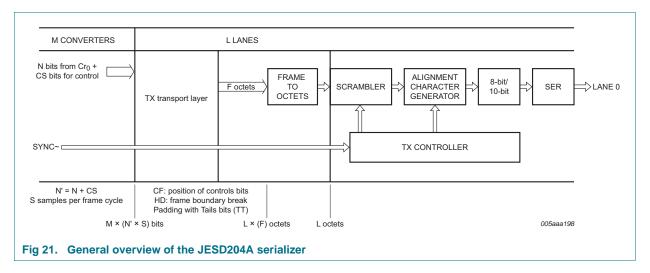

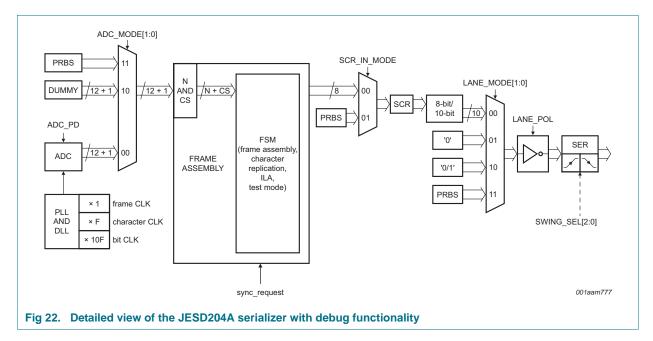

#### 11.5.1 Digital JESD204A formatter

The block placed after the ADC core is used to implement all functions of the JESD204A standard. This ensures signal integrity and guarantees the clock and the data recovery at the receiver side.

The block is highly parameterized and can be configured in various ways depending on the sampling frequency and the number of lanes used.

ADC1213S\_SER

#### 11.5.2 ADC core output codes versus input voltage

<u>Table 13</u> shows the data output codes for a given analog input voltage.

Table 13. Output codes versus input voltage

| INP-INM (V) | Offset binary  | Two's complement | OTR |

|-------------|----------------|------------------|-----|

| < -1        | 0000 0000 0000 | 1000 0000 0000   | 1   |

| -1.0000000  | 0000 0000 0000 | 1000 0000 0000   | 0   |

| -0.9995117  | 0000 0000 0001 | 1000 0000 0001   | 0   |

| -0.9990234  | 0000 0000 0010 | 1000 0000 0010   | 0   |

| -0.9985352  | 0000 0000 0011 | 1000 0000 0011   | 0   |

| -0.9980469  | 0000 0000 0100 | 1000 0000 0100   | 0   |

|             | ••••           |                  | 0   |

| -0.0009766  | 0111 1111 1110 | 1111 1111 1110   | 0   |

| -0.0004883  | 0111 1111 1111 | 1111 1111 1111   | 0   |

| 0.0000000   | 1000 0000 0000 | 0000 0000 0000   | 0   |

| +0.0004883  | 1000 0000 0001 | 0000 0000 0001   | 0   |

| +0.0009766  | 1000 0000 0010 | 0000 0000 0010   | 0   |

|             | ••••           |                  | 0   |

| +0.9980469  | 1111 1111 1011 | 0111 1111 1011   | 0   |

| +0.9985352  | 1111 1111 1100 | 0111 1111 1100   | 0   |

| +0.9990234  | 1111 1111 1101 | 0111 1111 1101   | 0   |

| +0.9995117  | 1111 1111 1110 | 0111 1111 1110   | 0   |

| +1.0000000  | 1111 1111 1111 | 0111 1111 1111   | 0   |

| > +1        | 1111 1111 1111 | 0111 1111 1111   | 1   |

22 of 39

#### 11.6 Serial Peripheral Interface (SPI)

#### 11.6.1 Register description

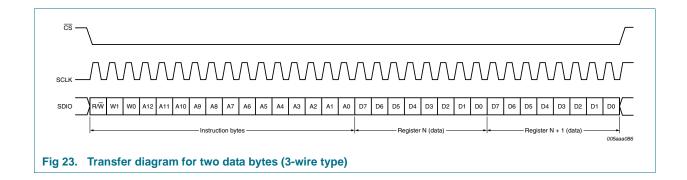

The ADC1213S serial interface is a synchronous serial communications port allowing for easy interfacing with many industry microprocessors. It provides access to the registers that control the operation of the chip in both read and write modes.

This interface is configured as a 3-wire type (SDIO as bidirectional pin).

Pin SCLK acts as the serial clock and pin  $\overline{\text{CS}}$  acts as the serial chip select.

Each read/write operation is sequenced by the  $\overline{CS}$  signal and enabled by a LOW level to to drive the chip with N bytes, depending on the content of the instruction byte (see Table 14).

Table 14. Instruction bytes for the SPI

|             | MSB    | MSB |    |     |     |     |    | LSB |

|-------------|--------|-----|----|-----|-----|-----|----|-----|

| Bit         | 7      | 6   | 5  | 4   | 3   | 2   | 1  | 0   |

| Description | R/W[1] | W1  | WO | A12 | A11 | A10 | A9 | A8  |

|             | A7     | A6  | A5 | A4  | А3  | A2  | A1 | A0  |

<sup>[1]</sup> R/W indicates whether a read (logic 1) or write (logic 0) transfer occurs after the instruction byte.

Table 15. Read or Write mode access description

| R/W[1] | Description          |

|--------|----------------------|

| 0      | Write mode operation |

| 1      | Read mode operation  |

<sup>[1]</sup> Bits W1 and W0 indicate the number of bytes transferred.

Table 16. Number of bytes to be transferred

| W1 | W0 | Number of bytes transferred |

|----|----|-----------------------------|

| 0  | 0  | 1 byte                      |

| 0  | 1  | 2 bytes                     |

| 1  | 0  | 3 bytes                     |

| 1  | 1  | 4 or more bytes             |

Bits A12 to A0 indicate the address of the register being accessed. In the case of a multiple byte transfer, this address is the first register to be accessed. An address counter is incremented to access subsequent addresses.

The steps involved in a data transfer are as follows:

- 1. The falling edge on pin  $\overline{\text{CS}}$  in combination with a rising edge on pin SCLK determine the start of communications.

- 2. The first phase is the transfer of the 2-byte instruction.

- 3. The second phase is the transfer of the data which can be vary in length but is always a multiple of 8 bits. The MSB is always sent first (for instruction and data bytes).

- 4. A rising edge on pin  $\overline{\text{CS}}$  indicates the end of data transmission.

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

#### 11.6.2 Channel control

| Table 17. | Register | allocation map |

|-----------|----------|----------------|

|           |          |                |

| Address | Register name                | Access[1] |                  |                   |              | В                         | it definition  |                |                 |                | Default[2]   |

|---------|------------------------------|-----------|------------------|-------------------|--------------|---------------------------|----------------|----------------|-----------------|----------------|--------------|

| (hex)   |                              |           | Bit 7            | Bit 6             | Bit 5        | Bit 4                     | Bit 3          | Bit 2          | Bit 1           | Bit 0          | (bin)        |

| ADC con | trol register                |           | 1                |                   |              | 1                         |                |                | '               | ı              |              |

| 0003    | SPI control                  | R/W       | -                | -                 | -            | -                         | -              | -              | ENABLE          | -              | 1111 1111    |

| 0005    | Reset and<br>Operating modes | R/W       | SW_RST           | -                 | -            | -                         | -              | -              | PD[1            | :0]            | 0000<br>0000 |

| 0006    | Clock                        | R/W       | -                | -                 | -            | SE_SEL                    | DIFF_SE        | -              | CLKDIV2_SEL     | DCS_EN         | 0000<br>000* |

| 8000    | Vref                         | R/W       | -                | -                 | -            | -                         | INTREF_EN      |                | INTREF[2:0]     |                | 0000<br>0000 |

| 0013    | Offset                       | R/W       | -                | - DIG_OFFSET[5:0] |              |                           |                |                | 0000<br>0000    |                |              |

| 0014    | Test pattern 1               | R/W       | -                | -                 | -            | -                         | -              | TESTPAT_1[2:0] |                 | 0]             | 0000<br>0000 |

| 0015    | Test pattern 2               | R/W       |                  | TESTPAT_2[11:4]   |              |                           |                |                | 0000<br>0000    |                |              |

| 0016    | Test pattern 3               | R/W       |                  | TESTPAT           | _3[3:0]      |                           | -              | -              | -               | -              | 0000<br>0000 |

| JESD204 | A control                    |           |                  |                   |              |                           |                |                |                 |                |              |

| 0801    | Ser_Status                   | R         | RXSYNC<br>_ERROR | RES               | SERVED[2     | :0]                       | 0              | 0              | POR_TST         | RESERVED       | 0010<br>0000 |

| 0802    | Ser_Reset                    | R/W       | SW_RST           | 0                 | 0            | 0                         | FSM_SW_<br>RST | 0              | 0               | 0              | 0000<br>0000 |

| 0805    | Ser_Control1                 | R/W       | 0                | RESERVED          | SYNC_<br>POL | SYNC_<br>SINGLE_<br>ENDED | 1              | REV_<br>SCR    | REV_<br>ENCODER | REV_<br>SERIAL | 0100<br>1001 |

| 8080    | Ser_Analog_Ctrl              | R/W       | 0                | 0                 | 0            | 0                         | 0              |                | SWING_SEL[2     | :0]            | 0000<br>0011 |

| 0809    | Ser_ScramblerA               | R/W       | 0                |                   |              |                           | LSB_INIT[6:    | 0]             |                 |                | 0000<br>0000 |

| Table 17.    | Register allocati | on mapcontinued |

|--------------|-------------------|-----------------|

| A alalua a a | Danieten mense    | A[1]            |

Product data sheet

Rev. 1 — 14 March 2011

| Address | Register name  | Access <sup>[1]</sup> | Bit definition |                 |        |           |             |              |        |          | Default[2]   |

|---------|----------------|-----------------------|----------------|-----------------|--------|-----------|-------------|--------------|--------|----------|--------------|

| (hex)   |                |                       | Bit 7          | Bit 6           | Bit 5  | Bit 4     | Bit 3       | Bit 2        | Bit 1  | Bit 0    | (bin)        |

| A080    | Ser_ScramblerB | R/W                   |                |                 | '      | MS        | B_INIT[7:0] |              |        |          | 1111 111     |

| 080B    | Ser_PRBS_Ctrl  | R/W                   | 0              | 0               | 0      | 0         | 0           | 0            | PRBS_T | YPE[1:0] | 0000<br>0000 |

| 0820    | Cfg_0_DID      | R                     |                |                 |        |           | DID[7:0]    |              |        |          | 1110 110     |

| 0821    | Cfg_1_BID      | R/W*                  | 0              | 0               | 0      | 0         |             | BI           | D[3:0] |          | 0000<br>1010 |

| 0822    | Cfg_3_SCR_L    | R/W*                  | SCR            | 0               | 0      | 0         | 0           | 0            | 0      | L        | 0000<br>0000 |

| 0823    | Cfg_4_F        | R/W*                  | 0              | 0               | 0      | 0         | 0           |              | F[2:0] |          | 0000 0**     |

| 0824    | Cfg_5_K        | R/W*                  | 0              | 0               | 0      |           |             | K[4:0]       |        |          | 000* ****    |

| 0825    | Cfg_6_M        | R/W*                  | 0              | 0               | 0      | 0         | 0           | 0            | 0      | М        | 0000<br>000* |

| 0826    | Cfg_7_CS_N     | R/W*                  | 0              | CS[0]           | 0      | 0         |             | N[3:0]       |        |          | 0100<br>0010 |

| 0827    | Cfg_8_Np       | R/W*                  | 0              | 0               | 0      |           |             | NP[4:0]      |        |          | 0000 111     |

| 0828    | Cfg_9_S        | R/W*                  | 0              | 0               | 0      | 0         | 0           | 0            | 0      | S        | 0000<br>0000 |

| 0829    | Cfg_10_HD_CF   | R/W*                  | HD             | 0               | 0      | 0         | 0           | 0            | CF     | [1:0]    | *000<br>0000 |

| 082D    | Cfg_02_2_LID   | R/W*                  | 0              | 0               | 0      |           |             | LID[4:0]     |        |          | 0001<br>1100 |

| 084D    | Cfg02_13_FCHK  | R                     |                |                 |        | F         | CHK[7:0]    |              |        |          | **** ****    |

| 0871    | Lane_0_Ctrl    | R/W                   | 0              | SCR_IN_<br>MODE | LANE_I | MODE[1:0] | 0           | LANE_<br>POL | 0      | LANE_PD  | 0000<br>0000 |

| 0891    | ADC_0_Ctrl     | R/W                   | 0              | 0               | ADC_N  | MODE[1:0] | 0           | 0            | 0      | ADC_PD   | 0000<br>0000 |

<sup>[1]</sup> An "\*" in the Access column means that this register is subject to control access conditions in Write mode.

<sup>[2]</sup> An \*\*\* in the Default column replaces a bit of which the value depends on the binary level of external pins (e.g. CFG[3:0], Swing[1:0], Scrambler).

### 11.6.3 Register description

#### 11.6.3.1 ADC control registers

Table 18. Register SPI control (address 0003h)

Default values are highlighted.

| Bit    | Symbol | Access | Value  | Description                           |

|--------|--------|--------|--------|---------------------------------------|

| 7 to 2 | -      | -      | 111111 | not used                              |

| 1      | ENABLE | R/W    |        | ADC SPI control enable:               |

|        |        |        | 0      | ADC does not get the next SPI command |

|        |        |        | 1      | ADC gets the next SPI command         |

| 0      | -      | -      | 1      | not used                              |

#### Table 19. Register Reset and Power-down mode (address 0005h)

Default values are highlighted.

| Bit    | Symbol  | Access | Value | Description                          |

|--------|---------|--------|-------|--------------------------------------|

| 7      | SW_RST  | R/W    |       | reset digital part:                  |

|        |         |        | 0     | no reset                             |

|        |         |        | 1     | performs a reset of the digital part |

| 6 to 2 | -       | -      | 00000 | not used                             |

| 1 to 0 | PD[1-0] | R/W    |       | Power-down mode:                     |

|        |         |        | 00    | normal (power-up)                    |

|        |         |        | 01    | full power-down                      |

|        |         |        | 10    | sleep                                |

|        |         |        | 11    | normal (power-up)                    |

#### Table 20. Register Clock (address 0006h)

Default values are highlighted.

| Bit    | Symbol      | Access | Value | Description                                   |

|--------|-------------|--------|-------|-----------------------------------------------|

| 7 to 5 | -           | -      | 000   | not used                                      |

| 4      | SE_SEL      | R/W    |       | select SE clock input pin:                    |

|        |             |        | 0     | select CLKM input                             |

|        |             |        | 1     | select CLKP input                             |

| 3      | DIFF_SE     | R/W    |       | differential/single-ended clock input select: |

|        |             |        | 0     | fully differential                            |

|        |             |        | 1     | single-ended                                  |

| 2      | -           | -      | 0     | not used                                      |

| 1      | CLKDIV2_SEL | R/W    |       | select clock input divider by 2:              |

|        |             |        | 0     | disable                                       |

|        |             |        | 1     | enable                                        |

| 0      | DCS_EN      | R/W    |       | duty cycle stabilizer enable:                 |

|        |             |        | 0     | disable                                       |

|        |             |        | 1     | enable                                        |

ADC1213S\_SER

Table 21. Register Vref (address 0008h)

Default values are highlighted.

| Bit    | Symbol      | Access | Value | Description                             |

|--------|-------------|--------|-------|-----------------------------------------|

| 7 to 4 | -           | -      | 0000  | not used                                |

| 3      | INTREF_EN   | R/W    |       | enable internal programmable VREF mode: |

|        |             |        | 0     | disable                                 |

|        |             |        | 1     | enable                                  |

| 2 to 0 | INTREF[2:0] | R/W    |       | programmable internal reference:        |

|        |             |        | 000   | 0 dB (FS = 2 V)                         |

|        |             |        | 001   | −1 dB (FS = 1.78 V)                     |

|        |             |        | 010   | -2  dB (FS = 1.59  V)                   |

|        |             |        | 011   | -3  dB (FS = 1.42  V)                   |

|        |             |        | 100   | -4 dB (FS = 1.26 V)                     |

|        |             |        | 101   | −5 dB (FS = 1.12 V)                     |

|        |             |        | 110   | -6 dB (FS = 1 V)                        |

|        |             |        | 111   | not used                                |

#### Table 22. Digital offset adjustment (address 0013h)

Default values are highlighted.

| Register offset | Register offset |                 |  |  |  |  |  |

|-----------------|-----------------|-----------------|--|--|--|--|--|

| Decimal         | DIG_OFFSET[5:0] | DIG_OFFSET[5:0] |  |  |  |  |  |

| +31             | 011111          | +31 LSB         |  |  |  |  |  |

|                 |                 |                 |  |  |  |  |  |

| 0               | 000000          | 0               |  |  |  |  |  |

|                 |                 | •••             |  |  |  |  |  |

| -32             | 100000          | -32 LSB         |  |  |  |  |  |

#### Table 23. Register Test pattern 1 (address 0014h)

Default values are highlighted.

| Bit       | Symbol         | Access | Value | Description                                                    |

|-----------|----------------|--------|-------|----------------------------------------------------------------|

| 7 to 3    | -              | -      | 00000 | not used                                                       |

| 2 to 0 TE | TESTPAT_1[2:0] | R/W    |       | digital test pattern:                                          |

|           |                |        | 000   | off                                                            |

|           |                |        | 001   | mid-scale                                                      |

|           |                |        | 010   | - FS                                                           |

|           |                |        | 011   | + FS                                                           |

|           |                |        | 100   | toggle '11111111'/'00000000'                                   |

|           |                |        | 101   | custom test pattern, to be written in register 0015h and 0016h |

|           |                |        | 110   | '010101'                                                       |

|           |                |        | 111   | '101010'                                                       |

Downloaded from Elcodis.com electronic components distributor

#### Table 24. Register Test pattern 2 (address 0015h)

Default values are highlighted.

| Bit    | Symbol          | Access | Value    | Description                               |

|--------|-----------------|--------|----------|-------------------------------------------|

| 7 to 0 | TESTPAT_2[11:4] | R/W    | 00000000 | custom digital test pattern (bit 11 to 4) |

#### Table 25. Register Test pattern 3 (address 0016h)

Default values are highlighted.

| Bit    | Symbol         | Access | Value | Description                              |

|--------|----------------|--------|-------|------------------------------------------|

| 7 to 4 | TESTPAT_3[3:0] | R/W    | 0000  | custom digital test pattern (bit 3 to 0) |

| 3 to 0 | -              | -      | 0000  | not used                                 |

#### 11.6.4 JESD204A digital control registers

#### Table 26. SER\_Status (address 0801h)

Default values are highlighted.

| Bit    | Symbol        | Access | Value | Description                                  |

|--------|---------------|--------|-------|----------------------------------------------|

| 7      | RXSYNC_ERROR  | R      | 0     | set to 1 when a synchronization error occurs |

| 6 to 4 | RESERVED[2:0] | -      | 010   | reserved                                     |

| 3 to 2 | -             | -      | 00    | not used                                     |

| 1      | POR_TST       | R      | 0     | power-on-reset                               |

| 0      | RESERVED      | -      | 0     | reserved                                     |

#### Table 27. SER\_Reset (address 0802h)

Default values are highlighted.

| Bit    | Symbol     | Access | Value | Description                                                               |

|--------|------------|--------|-------|---------------------------------------------------------------------------|

| 7      | SW_RST     | R/W    | 0     | initiates a software reset of the JESD204A unit                           |

| 6 to 4 | -          | -      | 000   | not used                                                                  |

| 3      | FSM_SW_RST | R/W    | 0     | initiates a software reset of the internal state machine of JESD204A unit |

| 2 to 0 | -          | -      | 000   | not used                                                                  |

#### Table 28. SER\_Control1 (address 0805h)

Default values are highlighted.

| Bit | Symbol            | Access | Value | Description                                            |

|-----|-------------------|--------|-------|--------------------------------------------------------|

| 7   | -                 | -      | 0     | not used                                               |

| 3   | RESERVED          | -      | 0     | reserved                                               |

| 5   | SYNC_POL          | R/W    |       | defines the synchronization signal polarity:           |

|     |                   |        | 0     | synchronization signal is active LOW                   |

|     |                   |        | 1     | synchronization signal is active HIGH                  |

| 4   | SYNC_SINGLE_ENDED | R/W    |       | defines the input mode of the synchronization signal:  |

|     |                   |        | 0     | synchronization input mode is set in Differential mode |

|     |                   |        | 1     | synchronization input mode is set in Single-ended mode |

| 3   | -                 | -      | 1     | not used                                               |

| 2   | REV_SCR           | -      |       | LSB are swapped to MSB at the scrambler input:         |

|     |                   |        | 0     | disable                                                |

|     |                   |        | 1     | enable                                                 |

ADC1213S\_SER All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 1 — 14 March 2011 29 of 39

Table 28. SER\_Control1 (address 0805h) ...continued

Default values are highlighted.

| Bit | Symbol      | Access | Value | Description                                               |

|-----|-------------|--------|-------|-----------------------------------------------------------|

| 1   | REV_ENCODER | -      |       | LSB are swapped to MSB at the 8-bit/10-bit encoder input: |

|     |             |        | 0     | disable                                                   |

|     |             |        | 1     | enable                                                    |

| 0   | REV_SERIAL  | -      |       | LSB are swapped to MSB at the lane input:                 |

|     |             |        | 0     | disable                                                   |

|     |             |        | 1     | enable                                                    |

#### Table 29. SER\_Analog\_Ctrl (address 0808h)

Default values are highlighted.

| Bit    | Symbol         | Access | Value | Description                                |

|--------|----------------|--------|-------|--------------------------------------------|

| 7 to 3 | -              | -      | 00000 | not used                                   |

| 2 to 0 | SWING_SEL[2:0] | R/W    | 011   | defines the swing output for the lane pads |

#### Table 30. SER\_ScramblerA (address 0809h)

Default values are highlighted.

| Bit    | Symbol        | Access | Value   | Description                                                            |

|--------|---------------|--------|---------|------------------------------------------------------------------------|

| 7      | -             | -      | 0       | not used                                                               |

| 6 to 0 | LSB_INIT[6:0] | R/W    | 0000000 | defines the initialization vector for the scrambler polynomial (lower) |

#### Table 31. SER\_ScramblerB (address 080Ah)

Default values are highlighted.

| Bit    | Symbol        | Access | Value    | Description                                                            |

|--------|---------------|--------|----------|------------------------------------------------------------------------|

| 7 to 0 | MSB_INIT[7:0] | R/W    | 11111111 | defines the initialization vector for the scrambler polynomial (upper) |

#### Table 32. SER\_PRBS\_Ctrl (address 080Bh)

Default values are highlighted.

| Bit    | Symbol         | Access | Value             | Description                                                                    |

|--------|----------------|--------|-------------------|--------------------------------------------------------------------------------|

| 7 to 2 | -              | -      | 000000            | not used                                                                       |

| 1 to 0 | PRBS_TYPE[1:0] | R/W    |                   | defines the type of Pseudo-Random Binary Sequence (PRBS) generator to be used: |

|        |                |        | <b>00</b> (reset) | PRBS-7                                                                         |

|        |                |        | 01                | PRBS-7                                                                         |

|        |                |        | 10                | PRBS-23                                                                        |

|        |                |        | 11                | PRBS-31                                                                        |

#### Table 33. Cfg\_0\_DID (address 0820h)

Default values are highlighted.

| Bit    | Symbol   | Access | Value    | Description                                       |

|--------|----------|--------|----------|---------------------------------------------------|

| 7 to 0 | DID[7:0] | R      | 11101101 | defines the device (= link) identification number |

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

#### Table 34. Cfg\_1\_BID (address 0821h)

Default values are highlighted.

| Bit    | Symbol   | Access | Value | Description                            |

|--------|----------|--------|-------|----------------------------------------|

| 7 to 4 | -        | -      | 0000  | not used                               |

| 3 to 0 | BID[3:0] | R/W    | 1010  | defines the bank ID – extension to DID |

#### Table 35. Cfg\_3\_SCR\_L (address 0822h)

Default values are highlighted.

| Bit    | Symbol | Access | Value  | Description                                               |

|--------|--------|--------|--------|-----------------------------------------------------------|

| 7      | SCR    | R/W    | 0      | scrambling enabled                                        |

| 6 to 1 | -      | -      | 000000 | not used                                                  |

| 0      | L      | R/W    | 0      | defines the number of lanes per converter device, minus 1 |

#### Table 36. Cfg\_4\_F (address 0823h)

Default values are highlighted.

| Bit    | Symbol | Access | Value | Description                                     |

|--------|--------|--------|-------|-------------------------------------------------|

| 7 to 3 | -      | -      | 00000 | not used                                        |

| 2 to 0 | F[2:0] | R/W    | ***   | defines the number of octets per frame, minus 1 |

#### Table 37. Cfg\_5\_K (address 0824h)

Default values are highlighted.

| Bit    | Symbol | Access | Value | Description                                          |

|--------|--------|--------|-------|------------------------------------------------------|

| 7 to 5 | -      | -      | 000   | not used                                             |

| 4 to 0 | K[4:0] | R/W    | ****  | defines the number of frames per multiframe, minus 1 |

#### Table 38. Cfg\_6\_M (address 0825h)

Default values are highlighted.

| Bit    | Symbol | Access | Value   | Description                                          |

|--------|--------|--------|---------|------------------------------------------------------|

| 7 to 1 | -      | -      | 0000000 | not used                                             |

| 0      | M      | R/W    | *       | defines the number of converters per device, minus 1 |

#### Table 39. Cfg\_7\_CS\_N (address 0826h)

Default values are highlighted.

| Bit    | Symbol | Access | Value | Description                                            |

|--------|--------|--------|-------|--------------------------------------------------------|

| 7      | -      | -      | 0     | not used                                               |

| 6      | CS[0]  | R/W    | 1     | defines the number of control bits per sample, minus 1 |

| 5 to 4 | -      | -      | 00    | not used                                               |

| 3 to 0 | N[3:0] | R/W    | 0010  | defines the converter resolution                       |

#### Table 40. Cfg\_8\_Np (address 0827h)

Default values are highlighted.

| Bit    | Symbol  | Access | Value | Description                                          |

|--------|---------|--------|-------|------------------------------------------------------|

| 7 to 5 | -       | -      | 000   | not used                                             |

| 4 to 0 | NP[4:0] | R/W    | 01111 | defines the total number of bits per sample, minus 1 |

ADC1213S\_SER

All information provided in this document is subject to legal disclaimers.

#### Table 41. Cfg\_9\_S (address 0828h)

Default values are highlighted.

| Bit    | Symbol | Access | Value   | Description                                             |

|--------|--------|--------|---------|---------------------------------------------------------|

| 7 to 1 | -      | -      | 0000000 | not used                                                |

| 0      | S      | R/W    | 0       | defines number of samples per converter per frame cycle |

#### Table 42. Cfg\_10\_HD\_CF (address 0829h)

Default values are highlighted.