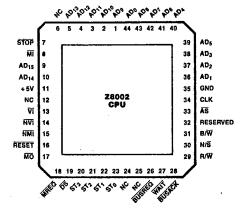

# Z8001<sup>®</sup> / Z8002<sup>®</sup> Military Z8000<sup>®</sup> CPU Central Processing Unit

T.49-17-07

# Zilog

## Military Electrical Specification

#### September 1988

#### **FEATURES**

- Regular, easy-to-use architecture

- Instruction set more powerful than many minicomputers

- Directly addresses 8 Mbytes

- Eight user-selectable addressing modes

- Seven data types that range from bits to 32-bit long words and byte and word strings

- System and Normal operating modes

- Separate code, data, and stack spaces

- Sophisticated interrupt structure

- Resource-shaping capabilities for multiprocessing systems

- Multi-programming support

- Compiler support

- Memory management and protection provided by Z8010™ Memory Management Unit

- 32-bit operations, including signed multiply and divide

- Z-BUS® compatible

- 4, 6, and 10 MHz clock rate

#### **GENERAL DESCRIPTION**

The Z8000 is an advanced high-end 16-bit microprocessor that spans a wide variety of applications ranging from simple stand-alone computers to complex parallel-processing systems. Essentially a monolithic minicomputer central processing unit, the Z8000 CPU is characterized by an instruction set more powerful than many minicomputers; abundant resources in registers, data types, addressing modes and addressing range, and a regular architecture that enhances throughput by avoiding critical bottlenecks such as implied or dedicated registers.

CPU resources include sixteen 16-bit general-purpose registers, seven data types that range from bits to 32-bit long words and byte and word strings, and eight user-selectable addressing modes. The 110 distinct instruction types can be combined with the various data types and addressing modes to form a powerful set of 414 instructions. Moreover, the instruction set is regular; most instructions can use any

of the five main addressing modes and can operate on byte, word, and long-word data types.

The CPU can operate in either the system or normal mode. The distinction between these two modes permits privileged operations, thereby improving operating system organization and implementation. Multiprogramming is supported by the "atomic" Test and Set instruction; multiprocessing by a combination of instruction and hardware features; and compilers by multiple stacks, special instructions, and addressing modes.

The Z8000 CPU is offered in two versions: the Z8001 segmented CPU and the Z8002 nonsegmented CPU. The main difference is in addressing range. The Z8001 can directly address 8 megabytes of memory; the Z8002 directly addresses 64 kilobytes. The two operating modes—system and normal—and the distinction between code,

data, and stack spaces within each mode allows memory extension up to 48 megabytes for the Z8001 and 384 kilobytes for the Z8002.

To meet the requirements of complex, memory-intensive applications, a companion memory-management device is offered for the Z8001. The Z8010 Memory Management Unit manages the large address space by providing features such as segment relocation and memory protection.

The Z8001 can be used with or without the Z8010. If used by itself, the Z8001 still provides an 8 megabyte direct addressing range, extendable to 48 megabytes.

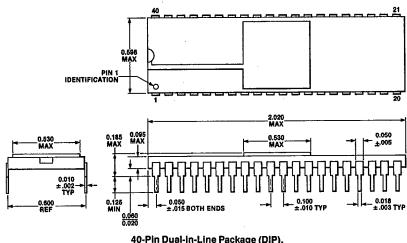

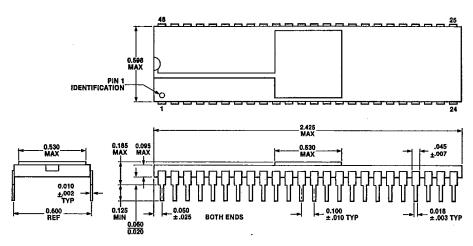

The Z8001, Z8002, and Z8010 are fabricated with high-density, high-performance scaled n-channel silicon-gate depletion-load technology, and are housed in dual-in-line packages (DIPS) and leadless chip carriers (LCC).

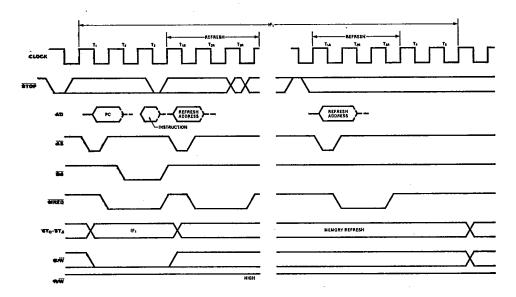

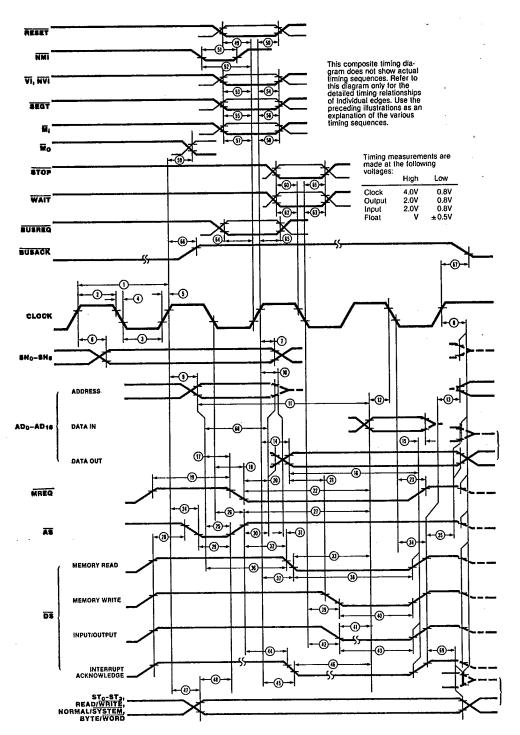

#### **Z8000 CPU TIMING**

The Z8000 CPU executes instructions by stepping through sequences of basic machine cycles, such as memory read or write, I/O device read or write, interrupt acknowledge, and internal execution. Each of these basic cycles requires three to ten clock cycles to execute. Instructions that require more clock cycles to execute are broken up into several machine cycles. Thus no machine cycle is longer than ten clock cycles and fast response to a Bus Request is quaranteed.

The instruction opcode is fetched by a normal memory read operation. A memory refresh cycle can be inserted just after the completion of any first instruction fetch (IF<sub>1</sub>) cycle and can also be inserted while the following instructions are being executed: MULT, MULTL, DIV, DIVL, HALT, all Shift instructions, all Block Move instructions, and the Multi-Micro

Request instruction (MREQ).

The following timing diagrams show the relative timing relationships of all CPU signals during each of the basic operations. When a machine cycle requires additional clock cycles for CPU internal operation, one to five clock cycles are added. Memory and I/O read and write, as well as interrupt acknowledge cycles, can be extended by activating the WAIT input. For exact timing information, refer to the composite timing diagram.

Note that the WAIT input is not synchronized in the Z8000 and that the setup and hold times for WAIT, relative to the clock, must be met. If asynchronous WAIT signals are generated, they must be synchronized with the CPU clock before entering the Z8000.

address offset.)

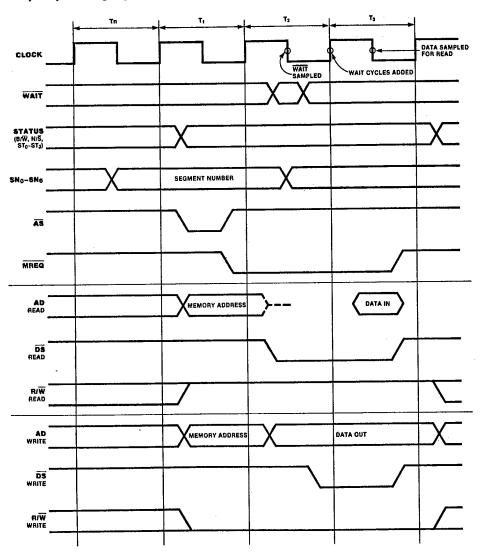

### MEMORY READ AND WRITE

Memory read and instruction fetch cycles are identical, except for the status information on the  $ST_0$ - $ST_3$  outputs. During a memory read cycle, a 16-bit address is placed on the  $AD_0$ - $AD_{15}$  outputs early in the first clock period, as shown in Figure 1. In the Z8001, the 7-bit segment number is output on  $SN_0$ - $SN_6$  one clock period earlier than the 16-bit

A valid address is indicated by the rising edge of Address Strobe. Status and mode information become valid early in the memory access cycle and remain stable throughout. The state of the WAIT input is sampled in the middle of the second clock cycle by the falling edge of Clock. If WAIT is

T-49-17-07

Low, an additional clock period is added between  $T_2$  and  $T_3$ . WAIT is sampled again in the middle of this wait cycle, and additional wait states can be inserted: this allows interfacing slow memories. No control outputs change during wait states

Although Z8000 memory is word organized, memory is addressed as bytes. All instructions are word-aligned, using even addresses. Within a 16-bit word, the most significant byte ( $D_8$ - $D_{15}$ ) is addressed by the low-order address ( $A_0$  = Low), and the least significant byte ( $D_0$ - $D_7$ ) is addressed by the high-order address ( $A_0$  = High).

Figure 1. Memory Read and Write Timing

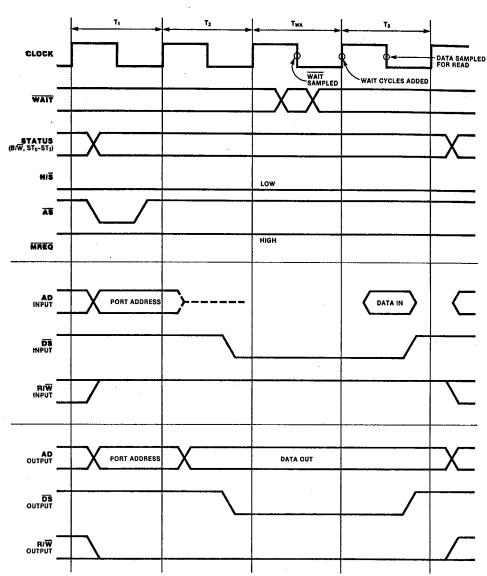

#### INPUT/OUTPUT

T-49-17-07

I/O timing is similar to memory read/write timing, except that one wait state is automatically (T<sub>WA</sub>) inserted between

$\rm T_2$  and  $\rm T_3$  (Figure 2). Both the segmented Z8001 and the nonsegmented Z8002 use 16-bit I/O addresses.

Figure 2. Input/Output Timing

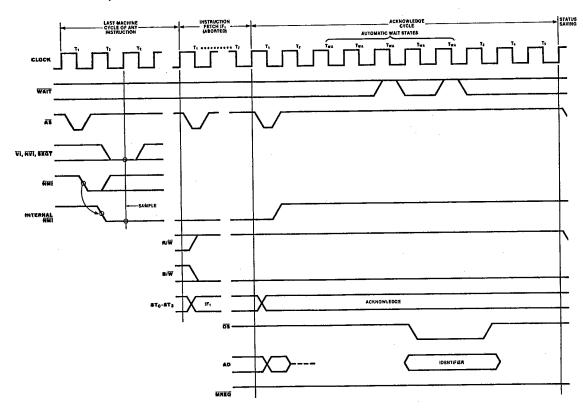

## INTERRUPT AND SEGMENT TRAP REQUEST AND ACKNOWLEDGE

The Z8000 CPU recognizes three interrupt inputs (non-maskable, vectored, and nonvectored) and a segmentation trap input. Any High-to-Low transition on the  $\overline{\text{NMI}}$  input is asynchronously edge detected and sets the internal  $\overline{\text{NMI}}$  latch. The  $\overline{\text{VI}}$ ,  $\overline{\text{NVI}}$ , and  $\overline{\text{SEGT}}$  inputs, as well as the state of the internal  $\overline{\text{NMI}}$  latch, are sampled at the end of  $T_2$  in the last machine cycle of any instruction.

In response to an interrupt or trap, the subsequent IF $_1$  cycle is exercised, but ignored. The internal state of the CPU is not altered and the instruction will be refetched and executed after the return from the interrupt routine. The program counter is not updated, but the system stack pointer is decremented in preparation for pushing starting information onto the system stack.

The next machine cycle is the interrupt acknowledge cycle.

This cycle has five automatic wait states, with additional wait states possible, as shown in Figure 3.

After the last wait state, the CPU reads the information on AD<sub>0</sub>-AD<sub>15</sub> and temporarily stores it, to be saved on the stack later in the acknowledge sequence. This word identifies the source of the interrupt or trap. For the nonvectored and nonmaskable interrupts, all 16 bits can represent peripheral device status information. For the vectored interrupt, the low byte is the jump vector, and the high byte can be extra user status. For the segmentation trap, the *high* byte is the Memory Management Unit identifier and the *low* byte is undefined.

After the acknowledge cycle, the N/S output indicates the automatic change to system mode.

Figure 3. Interrupt and Segment Trap Request/Acknowledge Timing

#### **STATUS SAVING SEQUENCE**

T-49-17-07

The machine cycles, following the interrupt acknowledge or segmentation trap acknowledge cycle, push the old status information on the system stack in the following order: the 16-bit program counter; the 7-bit segment number (Z8001 only); the flag control word; and finally the interrupt/trap identifier. Subsequent machine cycles fetch the new program status from the program status area, and then branch to the interrupt/trap service routine.

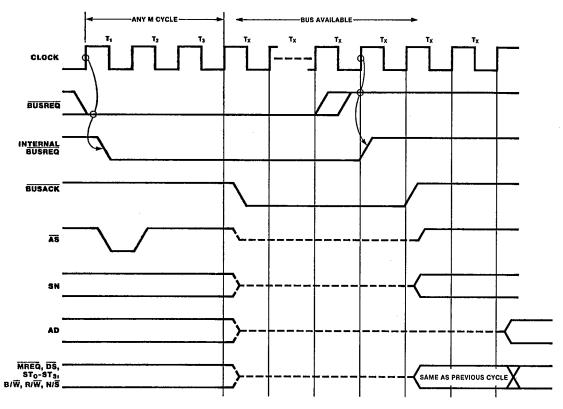

#### **BUS REQUEST ACKNOWLEDGE TIMING**

A Low on the BUSREQ input indicates to the CPU that another device is requesting the Address/Data and control buses. The asynchronous BUSREQ input is synchronized at the beginning of any machine cycle (Figure 4). BUSREQ takes priority over WAIT. If BUSREQ is Low, an internal synchronous BUSREQ signal is generated, which—after completion of the current machine cycle—causes the BUSACK output to go Low and all bus outputs to go into the

high-impedance state. The requesting device—typically a DMA—can then control the bus.

When BUSREQ is released, it is synchronized with the rising clock edge; the BUSACK output goes High one clock period later, indicating that the CPU will again take control of the bus.

Figure 4. Bus Request/Acknowledge Timing

STOP

T-49-17-07

The STOP input is sampled by the last falling clock edge

immediately preceding any IF1 cycle (Figure 5) and before the second word of an EPA instruction is fetched. If STOP is found Low during the IF<sub>1</sub> cycle, a stream of memory refresh cycles is inserted after T<sub>3</sub>, again sampling the STOP input on each falling clock edge in the middle of the T<sub>3</sub> states. During the EPA instruction, both EPA instruction words are fetched but any data transfer or subsequent instruction fetch is

postponed until STOP is sampled High. This refresh operation does not use the refresh prescaler or its divideby-four clock prescaler; rather, it double-increments the refresh counter every three clock cycles. When STOP is found High again, the next refresh cycle is completed, any remaining T states of the IF1 cycle are then executed, and the CPU continues its operation.

Figure 5. Stop Timing

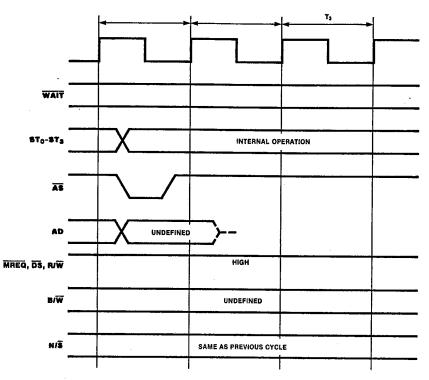

#### INTERNAL OPERATION

T-49-17-07

Certain extended instructions, such as Multiply and Divide, and some special instructions need additional time for the execution of internal operations. In these cases, the CPU goes through a sequence of internal operation machine cycles, each of which is three to eight clock cycles long (Figure 6). This allows fast response to Bus Request and Refresh Request, because bus request or refresh cycles can be inserted at the end of any internal machine cycle.

Figure 6. Internal Operation Timing

#### HALT

A HALT instruction executes an unlimited number of 3-cycle internal operations, interspersed with memory refresh cycles whenever requested. An interrupt, segmentation trap, or reset are the only exits from a HALT instruction.

The CPU samples the  $\overline{VI}$ ,  $\overline{NVI}$ ,  $\overline{NMI}$ , and  $\overline{SEGT}$  inputs at the beginning of every  $T_3$  cycle. If an input is found active during two consecutive samples, the subsequent IF $_1$  cycle is exercised, but ignored, and the normal interrupt acknowledge cycle is started.

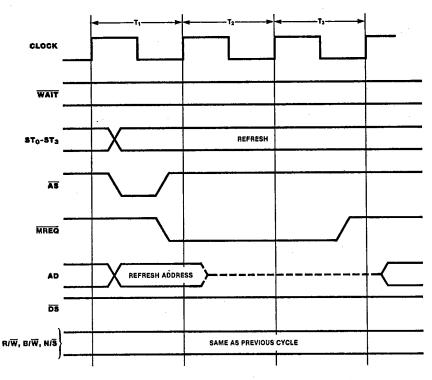

#### **MEMORY REFRESH**

When the 6-bit prescaler in the refresh counter has been decremented to zero, a refresh cycle consisting of three T-states is started as soon as possible (that is, after the next IF1 cycle or Internal Operation cycle).

The 9-bit refresh counter value is put on the low-order side of the address bus (AD $_0$ -AD $_8$ ); AD $_9$ -AD $_{15}$  are undefined (Figure 7). Since the memory is word-organized, A $_0$  is always Low during refresh and the refresh counter is always

incremented by two, thus stepping through 256 consecutive refresh addresses on  $AD_1$ - $AD_8$ . Unless disabled, the presettable prescaler runs continuously and the delay in starting a refresh cycle is therefore not cumulative.

While the STOP input is Low, a continuous stream of memory refresh cycles, each three T-states long, is executed without using the refresh prescaler.

Figure 7. Memory Refresh Timing

#### RESET

A Low on the  $\overline{\text{RESET}}$  input causes the following results within five clock cycles (Figure 8):

- AD<sub>0</sub>-AD<sub>15</sub> are 3-stated

- AS, DS, MREQ, ST<sub>0</sub>-ST<sub>3</sub>, BUSACK, and MO are forced High

- SN<sub>0</sub>-SN<sub>6</sub> are forced Low

- Refresh is disabled

- R/W, B/W, and N/S are not affected

When RESET has been High for three clock periods, three consecutive memory read cycles are executed in the system mode for the Z8001. The Z8002 has two consecutive read cycles. In the Z8001 the first cycle reads the flag and control word from location 0002, the next reads the 7-bit program counter segment number from location 0004, the next reads the 16-bit PC offset from location0006, and the following IF, cycle starts the program. In the Z8002, the first cycle reads the flag and control word from location 0002, the next reads the PC from location 0004, and the following IF, cycle starts the program.

#### COMPOSITE AC TIMING DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Guaranteed by characterization/design.

Voltages on all pins with respect

T-49-17-0

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### STANDARD TEST CONDITIONS

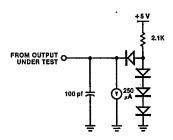

The DC Characteristics section listed below applies for the following standard test conditions, unless otherwise noted.

Military Operating Temperature Range (T<sub>C</sub>) -55°C to +125°C

Standard Military Test Condition  $+4.5V \le V_{CC} \le +5.5V$

All voltages are referenced to GND (0V). Positive current flows into the referenced pln.

All AC parameters assume a total load capacitance (including parasitic capacitances) or 100 pf max, except for parameter 6 (50 pf max). Timing references between two output signals assume a load difference of 50 pf max.

#### **DC CHARACTERISTICS**

| Symbol              | Parameter                            | Min                    | Max                    | Unit | Condition                          |

|---------------------|--------------------------------------|------------------------|------------------------|------|------------------------------------|

| V <sub>CH</sub>     | Clock Input High Voltage             | V <sub>CC</sub> = 0.4a | V <sub>CC</sub> + 0.3° | ٧    | Driven by External Clock Generator |

| VCL                 | Clock Input Low Voltage              | -0.3c                  | 0.45a                  | ٧    | Driven by External Clock Generator |

| VIH                 | Input High Voltage                   | 2.2a                   | V <sub>CC</sub> + 0.3° | ٧    |                                    |

| VIH RESET           | Input High Voltage on RESET pin      | 2.4a                   | V <sub>CC</sub> + 0.3° | ٧    |                                    |

| V <sub>IH NMI</sub> | Input High Voltage on NMI pin        | 2.48                   | V <sub>CC</sub> + 0.3° | ٧    |                                    |

| VĮL                 | Input Low Voltage                    | 0.3c                   | 0.8a                   | ٧    |                                    |

| VOH                 | Output High Voltage                  | 2,48                   |                        | ٧    | $I_{OH} = -250 \mu\text{A}$        |

| VoL                 | Output Low Voltage                   |                        | 0.4a                   | ٧    | $I_{OL} = +2.0  \text{mA}$         |

| fil.                | Input Leakage                        |                        | ± 10a                  | μΑ   | $0.4 \le V_{ N} \le +2.4V$         |

| ILSEGT              | Max input Current on SEGT pin        |                        |                        |      |                                    |

|                     | (8001 only)                          |                        | 200a                   | μΑ   |                                    |

| loL                 | Output Leakage                       |                        | ± 10a                  | μΑ   | 0.4 ≤ V <sub>IN</sub> ≤ +2.4V      |

| loc                 | V <sub>CC</sub> Power Supply Current |                        | 400a                   | mΑ   | 4,6 and 10 MHz                     |

Parameter Test Status:

- a Tested

- b Guaranteed

- Guaranteed by Characterization/Design

#### **AC CHARACTERISTICS†**

T-49-17-07

| Number | Symbol      | Parameter                                                | Z800<br>4 M<br>Min |                  | Z80<br>6 M<br>Min |                                               | 28001<br>10 Mi<br>Min |       |

|--------|-------------|----------------------------------------------------------|--------------------|------------------|-------------------|-----------------------------------------------|-----------------------|-------|

|        |             |                                                          | 250a               | 2000a            | 165a              | 2000a                                         | 100a                  | 2000a |

| 1<br>2 | TcC<br>TwCh | Clock Cycle Time                                         | 200⊶<br>105a       | 2000             | 70a               | 2000~                                         | 40a                   | 2000- |

|        | TwCl        | Clock Width (High)                                       | 105a               |                  | 70ª               |                                               | 40a                   |       |

| 3<br>4 | TfC         | Clock Width (Low) Clock Fall Time                        | 1034               | 20a              | 70-               | 15a                                           | 40-                   | 10a   |

| 5      | TrC         | Clock Rise Time                                          |                    | 20a              |                   | 15a                                           |                       | 10a   |

| 6      | TdC(SNv)    | Clock 1 to Segment Number Valid (50 pf load) (8001 only) |                    | 130a             |                   | 110a                                          |                       | 80a   |

| 7      | TdC(SNn)    | Clock 1 to Segment Number Not Valid<br>(8001 only)       | 20a                |                  | 10a               |                                               | 0a                    |       |

| 8      | TdC(Bz)     | Clock † to Bus Float                                     |                    | 65°              |                   | 55°                                           |                       | 50°   |

| 9      | TdC(A)      | Clock 1 to Address Valid                                 |                    | 100 <sup>a</sup> |                   | 75a                                           |                       | 55a   |

| 10     | TdC(Az)     | Clock 1 to Address Float                                 |                    | 65°              |                   | 55°                                           |                       | 50°   |

| 11     | TdA(DR)     | Address Valid to Read Data Required Valid                |                    | 475d*            |                   | 305d*                                         |                       | 180d* |

| 12     | TsDR(C)     | Read Data to Clock ↓ Setup time                          | 30a                |                  | 20a               |                                               | 10a                   | -     |

| 13     | TdDS(A)     | DS ↑ to Address Active                                   | *b08               |                  | 45d*              |                                               | 20d*                  |       |

| 14     | TdC(DW)     | Clock ↑ to Write Data Valid                              |                    | 100a             |                   | 75a .                                         |                       | 60a   |

| 15     | ThDR(DS)    | Read Data to DS ↑ Hold Time                              | 0a                 |                  | 0a                |                                               | 0a                    |       |

| 16     | TdDW(DS)    | Write Data Valid to DS ↑ Delay                           | 295d*              |                  | 195d*             | . <u>.                                   </u> | 110 <sup>d</sup> *    |       |

| 17     | TdA(MR)     | Address Valid to MREQ ↓ Delay                            | 55d*               |                  | 35d*              |                                               | 20d*                  |       |

| 18     | TdC(MR)     | Clock ↓ to MREQ ↓ Delay                                  |                    | 80a              |                   | 70a                                           |                       | 40a   |

| 19     | TwMRh       | MREQ Width (High)                                        | 210d*              |                  | 135d*             |                                               | 80d <b>*</b>          |       |

| 20     | TdMR(A)     | MREQ ↓ to Address Not Active                             | 70d*               |                  | 35d*              |                                               | 20d*                  |       |

| 21     | TdDW(DSW)   | Write Data Valid to DS ↓ (Write) Delay                   | 55d*               |                  | 35d*              |                                               | 15 <sup>d</sup> *     |       |

| 22     | TdMR(DR)    | MREQ ↓ to Read Data Required Valid                       |                    | 370d*            |                   | 230d*                                         |                       | 140d* |

| 23     | TdC(MR)     | Clock ↓ MREQ ↑ Delay                                     |                    | 80a              |                   | 60a                                           |                       | 45a   |

| 24     | TdC(ASf)    | Clock ↑ to AS ↓ Delay                                    |                    | 80a              |                   | 60a                                           |                       | 40a   |

| 25     | TdA(AS)     | Address Valid to AS † Delay                              | 55d*               |                  | 35d*              |                                               | 20d*                  |       |

| 26     | TdC(ASr)    | Clock ↓ to AS ↑ Delay                                    |                    | 90a              |                   | 80a                                           |                       | 40a   |

| 27     | TdAS(DR)    | ĀS ↑ to Read Data Required Valid                         |                    | 360d*            |                   | 220d*                                         |                       | 140d* |

| 28     | TdDS(AS)    | DS ↑ to AS ↓ Delay                                       | 70d*               |                  | 35d*              |                                               | 15 <b>d</b> *         |       |

| 29     | TwAS        | AS Width (Low)                                           | 85d*               |                  | 55d*              |                                               | 30d*                  |       |

| 30     | TdAS(A)     | AS ↑ to Address Not Active Delay                         | 70d*               |                  | 45d*              |                                               | 20d*                  |       |

| 31     | TdAz(DSR)   | Address Float to DS (Read) ↓ Delay                       | 0c                 |                  | 0c                | -                                             | 0c                    |       |

| 32     | TdAS(DSR)   | AS ↑ to DS (Read) ↓ Delay                                | 80d*               |                  | 55d*              |                                               | 30d*                  |       |

| 33     | TdDSR(DR)   | DS (Read) ↓ to Read Data Required Valid                  |                    | 205d*            |                   | 130d*                                         |                       | 70d   |

| 34     | TdC(DSr)    | Clock ↓ to DS↑ Delay                                     |                    | 70a              |                   | 65a                                           |                       | 45a   |

| 35     | TdDS(DW)    | DS 1 to Write Data Not Valid                             | 75d*               |                  | 45d*              |                                               | 25d*                  |       |

17E D

Parameter Test Status:

a Tested b Guaranteed

<sup>\*</sup>Clock-cycle time-dependent characteristics. See Footnotes to AC Characteristics. †Units in nanoseconds (ns).

c Guaranteed by Characterization/Design d Calculated Parameter—Not Directly Tested

## ■ 9984043 0013690 2 **■**

#### AC CHARACTERISTICS† (Continued)

T-49-17-07

|                |           |                                          | Z800<br>4 Mi     | iz               | Z800 <sup>-</sup><br>6 MH | łz              | Z8001<br>10 M | Hz .        |

|----------------|-----------|------------------------------------------|------------------|------------------|---------------------------|-----------------|---------------|-------------|

| Number         | Symbol    | Parameter                                | Min              | Max              | Min                       | Max             | Min           | Max         |

| <b>3</b> 6     | TdA(DSR)  | Address Valid to DS (Read) ↓ Delay       | 180d*            |                  | 110d*                     |                 | 65d*          |             |

| 37             | TdC(DSR)  | Clock ↑ to DS (Read) ↓ Delay             |                  | 120a             |                           | 85a             |               | 60a         |

| 38             | Twdsr     | DS (Read) Width (Low)                    | 275d*            |                  | 185 <b>d</b> *            |                 | 110d*         |             |

| 39             | TdC(DSW)  | Clock ↓ to DS (Write) ↓ Delay            |                  | 95a              |                           | 80a             |               | 60a         |

| 40             | TwDSW     | DS (Write) Width (Low)                   | 185ď*            |                  | 110d*                     |                 | 75d*          |             |

| 41             | TdDSI(DR) | DS (I/O) ↓ to Read Data Required Valid   |                  | 330d*            |                           | 210d*           |               | 120d*       |

| 42             | TdC(DSf)  | Clock ↓ to DS (I/O) ↓ Delay              |                  | 120a             |                           | 90a             |               | 60a         |

| 43             | TwDS      | DS (I/O) Width (Low)                     | 410d*            |                  | 255d*                     |                 | 160d*         |             |

| 44             | TdAS(DSA) | AS ↑ to DS (Acknowledge) ↓ Delay         | 1065d*           |                  | 690d*                     |                 | 410d*         |             |

| <b>4</b> 5     | TdC(D\$A) | Clock ↑ to DS (Acknowledge) ↓ Delay      |                  | 120a             |                           | 85a             |               | 65a         |

| 46             | TdDSA(DR) | DS (Acknowledge) ↓ to Read Data Required | •                |                  |                           |                 |               | <del></del> |

|                |           | Delay                                    |                  | 455d*            |                           | 295d*           |               | 165d*       |

| 47             | TdC(S)    | Clock 1 to Status Valid Delay            |                  | 110a             |                           | 85a             |               | 65a         |

| 48             | TdS(AS)   | Status Valid to AS ↑ Delay               | 50d*             |                  | 30d*                      |                 | 20d*          |             |

| 49             | TsR(C)    | RESET to Clock † Setup Time              | 180a             |                  | 70 <sup>a</sup>           |                 | 50a           |             |

| 50             | ThR(C)    | RESET to Clock † Hold Time               | 0a               |                  | 0a                        |                 | 0a            |             |

| 51             | TwNMI     | NMI Width (Low)                          | 100a             |                  | 70a                       |                 | 50a           |             |

| 52             | TsNMI(C)  | NMI to Clock † Setup Time                | 140a             |                  | 70a                       |                 | 50a           |             |

| 53             | TsVI(C)   | VI, NVI to Clock ↑ Setup Time            | 110 <sup>a</sup> |                  | 50a                       |                 | 40a           |             |

| 54             | ThVI(C)   | VI, NVI to Clock ↑ Hold Time             | 20a              |                  | 20a                       |                 | 10a           |             |

| 55             | TsSGT(C)  | SEGT to Clock † Setup Time (8001 only)   | 70a              |                  | 55a                       |                 | 40a           |             |

| 56             | ThSGT(C)  | SEGT to Clock † Hold Time (8001 only)    | 0a.              |                  | 0a                        |                 | 0a            |             |

| 57             | TsMI(C)   | MI to Clock † Setup Time                 | 180a             |                  | 140a                      |                 | 80a           |             |

| 58             | ThMI(C)   | MI to Clock † Hold Time                  | 0a               |                  | 0a                        |                 | 0a            |             |

| 59             | TdC(MO)   | Clock ↑ to MO Delay                      |                  | 120a             |                           | 85a             |               | 65a         |

| 60             | TsSTP(C)  | STOP to Clock ↓ Setup Time               | 140 <sup>a</sup> |                  | 100a                      |                 | 50a           |             |

| 61             | ThSTP(C)  | STOP to Clock ↓ Hold Time                | 0a               |                  | 0a                        | -               | 0a            |             |

| 62             | TsW(C)    | WAIT to Clock ↓ Setup Time               | 50a              |                  | 30a                       |                 | 20a           |             |

| <b>6</b> 3     | ThW(C)    | WAIT to Clock ↓ Hold Time                | 10a              |                  | 10a                       |                 | 5a            |             |

| 64             | TsBRQ(C)  | BUSREQ to Clock † Setup Time             | 90a              |                  | 80a                       |                 | 60a           |             |

| 65             | ThBRQ(C)  | BUSREQ to Clock 1 Hold Time              | 10a              |                  | 10a                       |                 | 5a            |             |

| 66             | TdC(BAKr) | Clock † to BUSACK † Delay                |                  | 100a             |                           | 75a             |               | 60a         |

| 67             | TdC(BAKf) | Clock ↑ to BUSACK ↓ Delay                |                  | 100 <sup>a</sup> |                           | 75 <sup>a</sup> |               | 60a         |

| <del>6</del> 8 | TwA       | Address Valid Width                      | 150d*            |                  | 95d*                      |                 | 50d*          |             |

| 69             | TdDS(S)   | DS 1 to STATUS Not Valid                 | 80d*             |                  | 55d*                      |                 | 30d*          |             |

<sup>\*</sup>Clock-cycle time-dependent characteristics. See Footnotes to AC Characteristics. †Units in nanoseconds (ns).

Parameter Test Status:

a Tested b Guaranteed

Guaranteed by Characterization/Design

Calculated Parameter—Not Directly Tested

### **FOOTNOTES TO AC CHARACTERISTICS**

T-49-17-07

| Number | Symbol    | Z8001/2<br>4 MHz<br>Equation | Z8001/2<br>6 MHz<br>Equation | Z8001/2<br>10 MHz<br>Equation |

|--------|-----------|------------------------------|------------------------------|-------------------------------|

| 11     | TdA(DR)   | 2TcC + TwCh - 130 ns         | 2TcC + TwCh - 95 ns          | 2TcC + TwCh - 60 ns           |

| 13     | TdDS(A)   | TwCl - 25 ns                 | TwCl - 25 ns                 | TwCl - 20 ns                  |

| 16     | TdDW(DS)  | TcC + TwCh - 60 ns           | TcC + TwCh - 40 ns           | TcC + TwCh - 30 ns            |

| 17     | TdA(MR)   | TwCh - 50 ns                 | TwCh - 35 ns                 | TwCh - 20 ris                 |

| 19     | TwMRh     | TcC - 40 ns                  | TcC - 30 ns                  | TcC - 20 ns                   |

| 20     | TdMR(A)   | TwCl - 35 ns                 | TwCl - 35 ns                 | TwCl - 20 ns                  |

| 21     | TdDW(DSW) | TwCh - 50 ns                 | TwCh - 35 ns                 | TwCh - 25 ns                  |

| 22     | TdMR(DR)  | 2TcC - 130 ns                | 2TcC - 100 ns                | 2TcC - 60 ns                  |

| 25     | TdA(AS)   | TwCh - 50 ns                 | TwCh - 35 ns                 | TwCh - 20 ns                  |

| 27     | TdAS(DR)  | 2TcC - 140 ns                | 2TcC - 110 ns                | 2TcC - 60 ns                  |

| 28     | TdDS(AS)  | TwCl - 35 ns                 | TwCl - 35 ns                 | TwCl - 25 ns                  |

| 29     | TwAS      | TwCh - 20 ns                 | TwCh - 15 ns                 | TwCh - 10 ns                  |

| 30     | TdAS(A)   | TwCl - 35 ns                 | TwCl - 25 ns                 | TwCl - 20 ns                  |

| 32     | TdAS(DSR) | TwCl - 25 ns                 | TwCl - 15 ns                 | TwCl - 10 ns                  |

| 33     | TdDSR(DR) | TcC + TwCh - 150 ns          | TcC • TwCh - 105 ns          | TcC + TwCh - 70 ns            |

| 35     | TdDS(DW)  | TwCl - 30 ns                 | TwCl - 25 ns                 | TwCl - 15 ns                  |

| 36     | TdA(DSR)  | TcC - 70 ns                  | TcC - 55 ns                  | TcC - 35 ns                   |

| 38     | TwDSR     | TcC + TwCh - 80 ns           | TcC + TwCh - 50 ris          | TcC + TwCh - 30 ns            |

| 40     | TwDSW     | TcC - 65 ns                  | TcC - 55 ns                  | TcC - 25 ns                   |

| 41     | TdDSI(DR) | 2TcC - 170 ns                | 2TcC - 120 ns                | 2TcC - 80 ns                  |

| 43     | TwDS      | 2TcC - 90 ns                 | 2TcC - 75 ns                 | 2TcC - 40 ns                  |

| 44     | TdAS(DSA) | 4TcC + TwCl - 40 ns          | 4TcC + TwCl - 40 ns          | 4TcC + TwCl - 30 ns           |

| 46     | TdDSA(DR) | 2TcC + TwCh - 150 ns         | 2TcC + TwCh - 105 ns         | 2TcC + TwCh - 75 ns           |

| 48     | TdS(AS)   | TwCh - 55 ns                 | TwCh - 40 ns                 | TwCh - 20 ns                  |

| 68     | TwA       | TcC - 90 ns                  | TcC - 70 ns                  | TcC - 50 ns                   |

| 69     | TdDS(s)   | TwCl - 25 ns                 | TwCl - 15 ns                 | TwCl - 10 ns                  |

AC Timing Test Conditions

V<sub>OL</sub> = 0.8V V<sub>OH</sub> = 2.0V V<sub>IL</sub> = 0.8V V<sub>IH</sub> = 2.4V V<sub>ILC</sub> = 0.45V V<sub>IHC</sub> = V<sub>CC</sub> - 0.4V

#### PIN DESCRIPTION

AD<sub>0</sub>-AD<sub>15</sub>. Address/Data (inputs/outputs, active High, 3-state). These multiplexed address and data lines are used for I/O and to address memory.

AS. Address Strobe (output, active Low, 3-state). The rising edge of AS indicates addresses are valid.

BUSACK. Bus Acknowledge (output active Low). A Low on this line indicates the CPU has relinquished control of the

BUSREQ. Bus Request (input, active Low). This line must be driven Low to request the bus from the CPU.

B/W. Byte/Word (output, Low = Word, 3-state). This signal defines the type of memory reference on the 16-bit address/data bus.

CLK. System Clock (input). CLK is a 5V single-phase time-base input.

DS. Data Strobe (output, active Low, 3-state). This line times the data in and out of the CPU.

MREQ. Memory Request (output, active Low, 3-state). A Low on this line indicates that the address/data bus holds a memory address.

MI, MO. Multi-Micro In, Multi-Micro Out (input and output, active Low). These two lines form a resource-request daisy chain that allows one CPU in a multi-microprocessor system to access a shared resource.

NMI. Non-Maskable Interrupt (edge triggered, input, active Low). A high-to-low transition on NMI requests a nonmaskable interrupt. The NMI interrupt has the highest priority of the three types of interrupts.

T-49-17-07

N/S. Normal/System Mode (output, Low = System Mode, 3-state), N/S indicates the CPU is in the normal or system mode.

NVI. Non-Vectored Interrupt (input, active Low). A Low on this line requests a non-vectored interrupt.

RESET. Reset (input, active Low). A Low on this line resets the CPU.

R/W. Read/Write (output, Low = Write, 3-state). R/W indicates that the CPU is reading from or writing to memory or

SEGT. Segment Trap (input, active Low). The Memory Management Unit interrupts the CPU with a Low on this line when the MMU detects a segmentation trap. Input on Z8001 only.

SN<sub>0</sub>-SN<sub>6</sub>. Segment Number (outputs, active High, 3-state). These lines provide the 7-bit segment number used to address one of 128 segments by the Z8010 memory Management Unit. Output by the Z8001 only.

ST<sub>0</sub>-ST<sub>3</sub>. Status (outputs, active High, 3-state). These lines specify the CPU status.

STOP. Stop (input, active Low). This input can be used to single-step instruction execution.

VI. Vectored Interrupt (input, active Low). A Low on this line requests a vectored interrupt.

WAIT. Wait (input, active Low). This line indicates to the CPU that the memory or I/O device is not ready for data transfer.

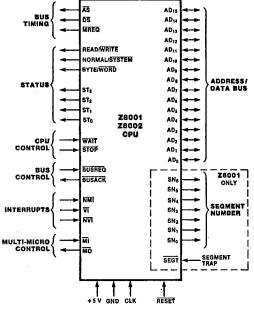

Figure 9, Z8000 CPU Pin Functions

Downloaded from Elcodis.com electronic components distributor

AD<sub>2</sub>

AD<sub>11</sub>

NVI ☐ 12

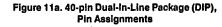

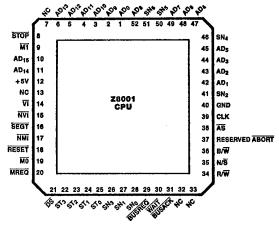

#### **PACKAGE PINOUTS**

40 AD<sub>0</sub> 39 AD<sub>1</sub> 38 AD<sub>7</sub>

37 AD, 36 AD, 35 AD,

33 AD2 32 AD1 31 GND

AD<sub>3</sub>

30 CLOCK

29 AS 28 NC NMI [ 13 27 B/W RESET 🔲 MO 🗆 15 N/S MREO 16 25 🗖 R/W 24 BUSACK 23 WAIT DS 🔲 17 ST<sub>3</sub> 18 22 GUSREG 21 STo

Figure 10a. 48-pin Dual-In-Line Package (DIP), Pin Assignments

Z8002

NC = No connection

Figure 10b. 52-pin Chip Carrier, Pin Assignments

Figure 11b. 44-pin Chip Carrier, Pin Assignments

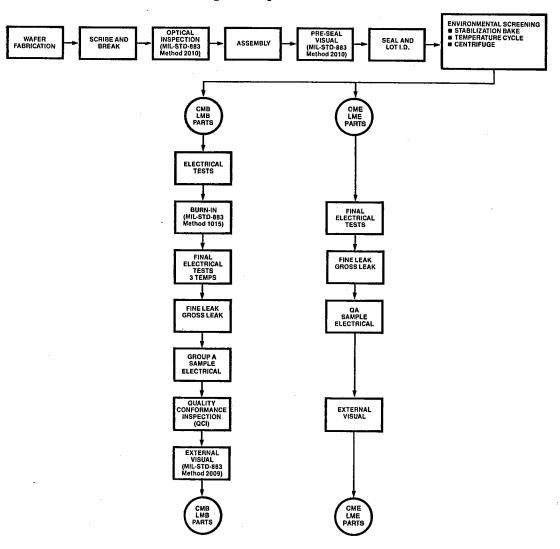

#### MIL-STD-883 MILITARY PROCESSED PRODUCT

T-49-17-07

- Mil-Std-883 establishes uniform methods and procedures for testing microelectronic devices to insure the electrical, mechanical, and environmental integrity and reliability that is required for military applications.

- Mil-Std-883 Class B is the industry standard product assurance level for military ground and aircraft application.

- Compliant to 883 Class B, Revision C process requirements.

- The total reliability of a system depends upon tests that are designed to stress specific quality and reliability concerns that affect microelectronic products.

- The following tables detail the 100% screening and electrical tests, sample electrical tests, and Qualification/ Quality Conformance testing required.

#### **Zilog Military Product Flow**

## Table I MIL-STD-883 Class B Screening Requirements Method 5004 (Note 4)

| Test                                 | Mil-Std-883<br>Method | Test Condition                                                                                                                          | Requiremen |

|--------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

| Internal Visual                      | 2010                  | Condition B                                                                                                                             | 100%       |

| Stabilization Bake                   | 1008                  | Condition C                                                                                                                             | 100%       |

| Temperature Cycle                    | 1010                  | Condition C                                                                                                                             | 100%       |

| Constant Acceleration (Centrifuge)   | 2001                  | Condition E or D <sup>(Note 1)</sup> , Y <sub>1</sub> Axis Only                                                                         | 100%       |

| Initial Electrical Tests             |                       | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +25 °C                                                            | 100%       |

| Burn-In                              | 1015                  | Condition D <sup>(Note 2)</sup> , 160 hours,<br>T <sub>A</sub> = +125 °C                                                                | 100%       |

| Interim Electrical Tests             |                       | Zilog Military Electrical Specification<br>Static/DCT <sub>C</sub> = +25°C                                                              | 100%       |

| PDA Calculation                      |                       | PDA = 5%                                                                                                                                | 100%       |

| Final Electrical Tests               |                       | Zllog Military Electrical Specification<br>Static/DCT <sub>C</sub> = +125°C, -55°C<br>Functional, Switching/ACT <sub>C</sub> =<br>+25°C | 100%       |

| Fine Leak                            | 1014                  | Condition B.                                                                                                                            | 100%       |

| Gross Leak                           | 1014                  | Condition C                                                                                                                             | 100%       |

| Quality Conformance Inspection (QCI) |                       | •                                                                                                                                       |            |

| Group A Each Inspection Lot          | 5005                  | (See Table II)                                                                                                                          | Sample     |

| Group B Every Week                   | 5005                  | (See Table III)                                                                                                                         | Sample     |

| Group C Periodically(Note 3)         | 5005                  | (See Table IV)                                                                                                                          | Sample     |

| Group D Periodically(Note 3)         | 5005                  | (See Table V)                                                                                                                           | Sample     |

| External Visual                      | 2009                  |                                                                                                                                         | 100%       |

| QA—Ship                              |                       |                                                                                                                                         | 100%       |

#### NOTES:

- Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

In process of fully implementing of Condition D Burn-in Circuits. Contact factory for copy of specific burn-in circuit available.

Performed periodically as required by Mil-Std-883, paragraph 1.2.1 b(17).

Processing fully compliant to Mil-Std-883 Revision C requirements.

# Table II Group A Sample Electrical Tests MIL-STD-883 Method 5005

| Subgroup    | Tests          | Temperature (T <sub>C</sub> ) | Sample<br>Size |

|-------------|----------------|-------------------------------|----------------|

| Subgroup 1  | Static/DC      | + 25 °C                       | 100%           |

| Subgroup 2  | Static/DC      | + 125°C                       | 116/0          |

| Subgroup 3  | Static/DC      | -55°C                         | 116/0          |

| Subgroup 7  | Functional     | +25°C                         | 100%           |

| Subgroup 8  | Functional     | - 55°C and +125°C             | 116/0          |

| Subgroup 9  | Switching/AC   | +25°C                         | 100%           |

| Subgroup 10 | Switching/AC   | + 125°C                       | 116/0          |

| Subgroup 11 | Switching / AC | -55°C                         | 116/0          |

|             |                |                               |                |

- The specific parameters to be included for tests in each subgroup shall be as specified in the applicable detail electrical specification. Where no parameters have been identified in a particular subgroup or test within a subgroup, no Group A testing is required for that subgroup or test.

Group A testing by subgroup or within subgroups may be performed in any sequence unless otherwise specified.

- If any failure occurs during sample testing of any subgroup then the lot is 100% tested at the failed subgroup only.

Table III Group B

Sample Test Performed Every Week to

Test Construction and Insure Integrity of Assembly Process.

MIL-STD-883 Method 5005

| Subgroup                          | Mil-Std-883<br>Method Test Condition |                                    | Quantity or<br>LTPD/Max Acce |  |

|-----------------------------------|--------------------------------------|------------------------------------|------------------------------|--|

| Subgroup 2 Resistance to Solvents | 2015                                 |                                    | 4/0                          |  |

| Subgroup 3<br>Solderability       | 2003                                 | Solder Temperature<br>+245°C ± 5°C | 15(Note 1)                   |  |

| Subgroup 5 Bond Strength          | 2011                                 | С                                  | 15(Note 2)                   |  |

Number of leads inspected selected from a minimum of 3 devices.

Number of bond pulls selected from a minimum of 4 devices.

# Table IV Group C Sample Test Performed Periodically to Verify Integrity of the Die. MIL-STD-883 Method 5005

| Subgroup                    | Mil-Std-883<br>Method | Test Condition                                                                | Quantity or<br>LTPD/Max Accept |

|-----------------------------|-----------------------|-------------------------------------------------------------------------------|--------------------------------|

| Subgroup 1                  |                       |                                                                               |                                |

| Steady State Operating Life | 1005                  | Condition D <sup>(Note 1)</sup> , 1000 hours at<br>+ 125 °C                   | 5                              |

| End Point Electrical Tests  |                       | Zilog Military Electrical Specification T <sub>C</sub> = +25°C, +125°C, -55°C |                                |

<sup>1.</sup> In process of fully implementing Condition D Burn-In Circuits. Contact factory for copy of specific burn-in circuit available.

Table V Group D

Sample Test Performed Periodically to Insure Integrity of the Package.

MIL-STD-883 Method 5005

|                                                        | WIT-21 D-99           | S METROS SOUS                                                               |                                |

|--------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|--------------------------------|

| Subgroup                                               | Mil-Std-883<br>Method | Test Condition                                                              | Quantity or<br>LTPD/Max Accept |

| Subgroup 1<br>Physical Dimensions                      | 2016                  |                                                                             | 15                             |

| Subgroup 2<br>Lead Integrity                           | 2004                  | Condition B <sub>2</sub> or D(Note 1)                                       | 15                             |

| Subgroup 3<br>Thermal Shock                            | 1011                  | Condition B minimum,<br>15 cycles minimum                                   |                                |

| Temperature Cycling                                    | 1010                  | Condition C, 100 cycles minimum                                             | 15                             |

| Moisture Resistance                                    | 1004                  |                                                                             |                                |

| Seal<br>3a) Fine Leak<br>3b) Gross Leak                | 1014                  | 3a) Condition B<br>3b) Condition C                                          |                                |

| Visual Examination                                     | 1004 or 1010          |                                                                             |                                |

| End Point Electrical Tests                             | ٠                     | Zilog Military Electrical Specification $T_C = +25$ °C, $+125$ °C, $-55$ °C |                                |

| Subgroup 4<br>Mechanical Shock                         | 2002                  | Condition B minimum                                                         |                                |

| Vibration Variable Frequency                           | 2007                  | Condition A minimum                                                         |                                |

| Constant Acceleration (Centrifuge)                     | 2001                  | Condition E or D(Note 2), Y1 Axis Only                                      | 15                             |

| Seal<br>4a) Fine Leak<br>4b) Gross Leak                | 1014                  | 4a) Condition B<br>4b) Condition C                                          |                                |

| Visual Examination                                     | 1010 or 1011          |                                                                             |                                |

| End Point Electrical Tests                             |                       | Zilog Military Electrical Specification $T_C = +25$ °C, $+125$ °C, $-55$ °C |                                |

| Subgroup 5<br>Salt Atmosphere                          | 1009                  | Condition A minimum                                                         |                                |

| Seal<br>5a) Fine Leak<br>5b) Gross Leak                | 1014                  | 5a) Condition <b>B</b><br>5b) Condition C                                   | 15                             |

| Visual Examination                                     | 1009                  |                                                                             |                                |

| Subgroup 6<br>Internal Water Vapor Content             | 1018                  | 5,000 ppm. maximum water content at +100 °C                                 | 3/0 or 5/1                     |

| Subgroup 7 <sup>(Note 3)</sup> Adhesion of Lead Finish | 2025                  |                                                                             | 15(Note 4)                     |

| Subgroup 8 <sup>(Note 5)</sup><br>Lid Torque           | 2024                  |                                                                             | 5/0                            |

- NOTES:

1. Lead Integrity Condition D for leadless chip carriers.

2. Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

- Not applicable to leadless chip carriers.

LTPD based on number of leads.

Not applicable for solder seal packages.

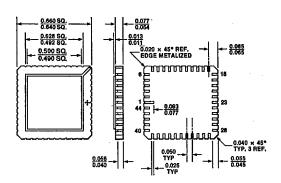

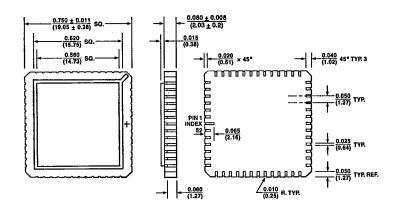

#### **PACKAGE INFORMATION**

## PACKAGE INFORMATION (Continued)

48-Pin Dual-in-Line Package (DIP), Ceramic

44-Pin Leadless Chip Carrier (LCC), Ceramic, JEDEC Type C

52-Pin Leadless Chip Carrier (LCC), Ceramic, JEDEC Type C

#### **ORDERING INFORMATION**

Z8001 Segmented CPU, 4.0 MHz

48-pin DIP

52-pin LCC

Z0800104CMB

Z0800104LMB

Z8001 Segmented CPU, 6.0 MHz

48-pin DiP

52-pin LCC

Z0800106CME

Z0800106LME

Z0800106CMB

Z0800106LMB

Z8001 Segmented CPU, 10.0 MHz

48-pin DIP

52-pin LCC

Z0800110CME

Z0800110LME

Z0800110CMB

Z0800110LMB

**Z8002 Non-Segmented CPU, 4.0 MHz 40-pin DIP 44-pin LCC Z08002**04CMB **Z08002**04CMJ\*

**Z8002 Non-Segmented CPU, 6.0 MHz 40-pin DIP 44-pin LCC**Z0800206CME

Z0800206CME

Z0800206CMB

Z0800206LMB

Z8002 Non-Segmented CPU, 10.0 MHz

Z0800206CMJ\*

40-pin DIP

44-pin LCC

Z0800210CME

Z0800210LME

Z0800210CMB

Z0800210LMB

Codes

PACKAGE

C = Ceramic

L = Ceramic LCC

TEMPERATURE

$M = -55^{\circ}C$  to  $+125^{\circ}C$

ENVIRONMENTAL

E = Hermetic Standard

B = 833 Class B Military

J = JAN 38510 Military

Example:

Z0800104CMB is an 8001, 4 MHz, Ceramic DIP, -55°C to +125°C, 883 Class B Military Flow (Revision C Compliant).

Z 0 8001 0 4 C M B

Environmental Flow Temperature

Package

Speed

Product Number

Zilog Prefix

\*See MIL-M-38510 Slash Sheet 520 for flow and electrical specifications for Z8002 (4 and 6 MHz).