# LM555JAN

**OBSOLETE** September 27, 2010

# **Timer**

# **General Description**

The LM555 is a highly stable device for generating accurate time delays or oscillation. Additional terminals are provided for triggering or resetting if desired. In the time delay mode of operation, the time is precisely controlled by one external resistor and capacitor. For astable operation as an oscillator, the free running frequency and duty cycle are accurately controlled with two external resistors and one capacitor. The circuit may be triggered and reset on falling waveforms, and the output circuit can source or sink up to 200mA or drive TTL circuits.

# **Features**

- Direct replacement for SE555/NE555

- Timing from microseconds through hours

- Operates in both astable and monostable modes

- Adjustable duty cycle

- Output can source or sink 200 mA

- Output and supply TTL compatible

- Temperature stability better than 0.005% per °C

- Normally on and normally off output

# **Applications**

- Precision timing

- Pulse generation

- Sequential timing

- Time delay generation

- Pulse width modulation

- Pulse position modulation

- Linear ramp generator

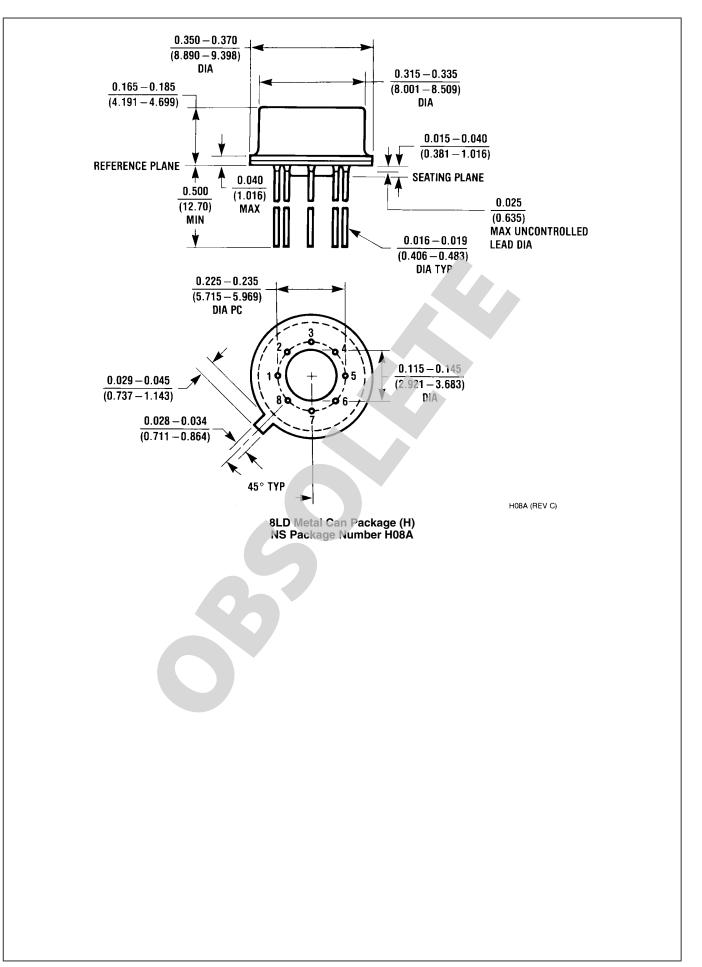

# **Ordering Information**

| NS Part Number | JAN Part Number  | NS Package Number | Package Description |

|----------------|------------------|-------------------|---------------------|

| JL555SPA       | JM38510/10901SPA | J08A              | 8LD Ceramic Dip     |

| JL555SGA       | JM38510/10901SGA | H08A              | 8LD Metal Can       |

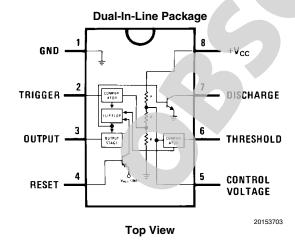

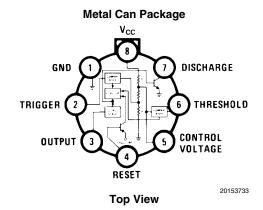

# **Connection Diagrams**

# **Schematic Diagram** Q21 CONTROL 5 3 -○ OUTPUT TRIGGER O 019 20153701

# **Absolute Maximum Ratings** (Note 1)

Supply Voltage +18V

Discharge Current +200mA

Output Sink Current +200mA

Output Source Current -200mA

Power Dissipation (Note 2)

Maximum Junction Temperature (T<sub>Jmax)</sub> +175°C

Storage Temperature Range  $-65^{\circ}\text{C} \le \text{T}_{\text{A}} \le +150^{\circ}\text{C}$

Soldering Information (Soldering 10 Seconds) 300°C

Thermal Resistance

ESD Tolerance (Note 3)

θ<sub>JA</sub>

CERDIP Still Air

CERDIP 500LF / Min Air Flow

Metal Can Still Air

Metal Can 500LF / Min Air Flow

θ<sub>JC</sub>

CERDIP

Metal Can

123°C/W 69°C/W 171°C/W 92°C/W 18°C/W 41°C/W

# **Recommended Operating Conditions**

Supply Voltage Range +4.5V to +16V<sub>DC</sub>

# **Quality Conformance Inspection**

Mil-Std-883, Method 5005 - Group A

| Subgroup | Description         | Temp °C |

|----------|---------------------|---------|

| 1        | Static tests at     | 25      |

| 2        | Static tests at     | 125     |

| 3        | Static tests at     | -55     |

| 4        | Dynamic tests at    | 25      |

| 5        | Dynamic tests at    | 125     |

| 6        | Dynamic tests at    | -55     |

| 7        | Functional tests at | 25      |

| 8A       | Functional tests at | 125     |

| 8B       | Functional tests at | -55     |

| 9        | Switching tests at  | 25      |

| 10       | Switching tests at  | 125     |

| 11       | Switching tests at  | -55     |

| 12       | Settling time at    | 25      |

| 13       | Settling time at    | 125     |

| 14       | Settling time at    | -55     |

# **Electrical Characteristics DC Parameters**

| Symbol                       | Parameter                       | Conditions                                      | Notes                 | Min  | Max   | Unit | Sub-<br>groups |

|------------------------------|---------------------------------|-------------------------------------------------|-----------------------|------|-------|------|----------------|

| I <sub>cc</sub>              | Power Supply Current            | V <sub>CC</sub> = 4.5V                          |                       |      | 5.0   | mA   | 1, 2, 3        |

|                              |                                 | V <sub>CC</sub> = 16.5V                         |                       |      | 20    | mA   | 1, 2, 3        |

| $\overline{V_{\text{Trig}}}$ | Trigger Voltage                 | V <sub>CC</sub> = 4.5V                          |                       | 1.3  | 1.8   | V    | 1              |

| •                            |                                 |                                                 |                       | 1.3  | 2.1   | V    | 2              |

|                              |                                 |                                                 |                       | 1.15 | 1.8   | V    | 3              |

|                              |                                 | V <sub>CC</sub> = 16.5V                         |                       | 5.2  | 5.8   | V    | 1              |

|                              |                                 |                                                 |                       | 5.2  | 6.1   | V    | 2              |

| -                            |                                 |                                                 |                       | 5.0  | 5.8   | V    | 3              |

| $I_{Trig}$                   | Trigger Current                 | V <sub>CC</sub> = 16.5V                         |                       | -5.0 |       | μΑ   | 1, 2, 3        |

| $V_{Th}$                     | Threshold Voltage               | $V_{CC} = 4.5V$                                 |                       | 2.7  | 3.3   | V    | 1              |

|                              |                                 |                                                 |                       | 2.6  | 3.4   | V    | 2, 3           |

|                              |                                 | V <sub>CC</sub> = 16.5V                         |                       | 10.7 | 11.3  | V    | 1              |

| -                            |                                 |                                                 |                       | 10.6 | 11.4  | V    | 2, 3           |

| $I_{Th}$                     | Threshold Current               | V <sub>CC</sub> = 16.5V                         |                       |      | 250   | nA   | 1, 2           |

|                              |                                 |                                                 |                       |      | 2,500 | nA   | 3              |

| $V_{OL}$                     | Logical "0" Output Voltage      | V <sub>CC</sub> = 4.5V, I <sub>Sink</sub> = 5mA |                       |      | 0.25  | V    | 1              |

|                              |                                 |                                                 |                       |      | 0.35  | V    | 2, 3           |

|                              |                                 | $V_{CC} = 4.5V$ , $I_{Sink} = 50mA$             |                       |      | 2.2   | V    | 1, 2           |

|                              |                                 |                                                 |                       |      | 2.6   | V    | 3              |

|                              |                                 | $V_{CC} = 16.5V, I_{Sink} = 10mA$               |                       |      | 0.15  | V    | 1, 3           |

|                              |                                 |                                                 |                       |      | 0.25  | V    | 2              |

|                              |                                 | $V_{CC} = 16.5V, I_{Sink} = 50mA$               |                       |      | 0.5   | V    | 1, 3           |

|                              |                                 |                                                 |                       |      | 0.7   | V    | 2              |

|                              |                                 | $V_{CC} = 16.5V$ , $I_{Sink} = 100mA$           |                       |      | 2.2   | V    | 1              |

|                              |                                 |                                                 |                       |      | 2.8   | V    | 2, 3           |

| $V_{OH}$                     | Logical "1" Output Voltage      | $V_{CC} = 4.5V$ , $ _{Source} = -100mA$         |                       | 2.6  |       | V    | 1, 2           |

|                              |                                 |                                                 |                       | 2.2  |       | V    | 3              |

|                              |                                 | $V_{CC} = 16.5V, I_{Source} = -100mA$           |                       | 14.6 |       | V    | 1, 2           |

|                              |                                 |                                                 |                       | 14   |       | V    | 3              |

| I <sub>CEX</sub>             | Discharge Transistor Leakage    | V <sub>CC</sub> = 16.5V                         |                       |      | 100   | nA   | 1, 3           |

|                              | Current                         |                                                 |                       |      | 3,000 | nA   | 2              |

| $V_{Sat}$                    | Discharge Transistor Saturation | V <sub>CC</sub> = 16.5V                         |                       |      | 0.8   | V    | 1, 3           |

|                              | Voltage                         |                                                 |                       |      | 1.0   | V    | 2              |

| V <sub>R</sub>               | Reset Voltage                   | V <sub>CC</sub> = 16.5V                         | (Note 4),<br>(Note 5) | 0.1  | 1.3   | V    | 1, 2, 3        |

| $I_R$                        | Reset Current                   | V <sub>CC</sub> = 16.5V                         |                       | -1.6 |       | mA   | 1, 2, 3        |

# **AC Parameters**

| Symbol           | Parameter              | Conditions              | Notes | Min | Max | Unit | Sub-<br>groups |

|------------------|------------------------|-------------------------|-------|-----|-----|------|----------------|

| t <sub>PLH</sub> | Propagation Delay Time | V <sub>CC</sub> = 4.5V  |       |     | 800 | nS   | 9, 11          |

|                  |                        |                         |       |     | 900 | nS   | 10             |

|                  |                        | V <sub>CC</sub> = 16.5V |       |     | 800 | nS   | 9, 11          |

|                  |                        |                         |       |     | 900 | nS   | 10             |

| •                | •                      | •                       |       |     |     |      |                |

| Symbol                            | Parameter                                     | Conditions                                                         | Notes    | Min   | Max   | Unit  | Sub-<br>groups |

|-----------------------------------|-----------------------------------------------|--------------------------------------------------------------------|----------|-------|-------|-------|----------------|

| t <sub>PHL</sub>                  | Propagation Delay Time                        | V <sub>CC</sub> = 4.5V                                             |          |       | 12    | μS    | 9, 10, 11      |

|                                   |                                               | V <sub>CC</sub> = 16.5V                                            |          |       | 12    | μS    | 9, 10, 11      |

| t <sub>TLH</sub>                  | Transition Time                               | $V_{CC} = 4.5V$                                                    |          |       | 300   | nS    | 9, 10, 11      |

|                                   |                                               | V <sub>CC</sub> = 16.5V                                            |          |       | 300   | nS    | 9, 10, 11      |

| t <sub>THL</sub>                  | Transition Time                               | $V_{CC} = 4.5V$                                                    |          |       | 300   | nS    | 9, 10, 11      |

|                                   |                                               | V <sub>CC</sub> = 16.5V                                            |          |       | 300   | nS    | 9, 10, 11      |

| t <sub>DOH</sub>                  | Time Delay Output High                        | $V_{CC} = 4.5V$                                                    |          | 106.7 | 113.3 | μS    | 9, 10, 11      |

|                                   | $R_T = 1K\Omega$                              | V <sub>CC</sub> = 16.5V                                            |          | 106.7 | 113.3 | μS    | 9, 10, 11      |

|                                   | Time Delay Output High                        | $V_{CC} = 4.5V$                                                    |          | 10.67 | 11.33 | mS    | 9, 10, 11      |

|                                   | $R_T = 100K\Omega$                            | V <sub>CC</sub> = 16.5V                                            |          | 10.67 | 11.33 | mS    | 9, 10, 11      |

| $\Delta t_D / \Delta V_{CC}$      | Drift In Time Delay                           | $\Delta V_{CC} = 12,$<br>$V_{CC} = 4.5V$ to 16.5V                  | (Note 6) | -220  | 220   | nS/V  | 9              |

| Δt <sub>D</sub> / ΔT              | Temperature Coefficient of Time Delay         | V <sub>CC</sub> = 16.5V                                            |          | -11   | 11    | nS/°C | 10, 11         |

| t <sub>Ch</sub>                   | Capacitor Charge Time                         | $V_{CC} = 4.5V$                                                    |          | 120   | 156   | μS    | 9, 10, 11      |

|                                   | $R_T = 1K\Omega$                              | V <sub>CC</sub> = 16.5V                                            |          | 120   | 156   | μS    | 9, 10, 11      |

|                                   | Capacitor Charge Time                         | $V_{CC} = 4.5V$                                                    |          | 11.3  | 15    | mS    | 9, 10, 11      |

|                                   | $R_T = 100K\Omega$                            | V <sub>CC</sub> = 16.5V                                            |          | 11.3  | 15    | mS    | 9, 10, 11      |

| t <sub>Dis</sub>                  | Capacitor Discharge Time                      | $V_{CC} = 4.5V$                                                    |          | 57.5  | 80    | μS    | 9, 10, 11      |

|                                   | $R_T = 1K\Omega$                              | V <sub>CC</sub> = 16.5V                                            |          | 57.5  | 80    | μS    | 9, 10, 11      |

|                                   | Capacitor Discharge Time                      | V <sub>CC</sub> = 4.5V                                             |          | 5.4   | 7.7   | mS    | 9, 10, 11      |

|                                   | $R_T = 100K\Omega$                            | V <sub>CC</sub> = 16.5V                                            |          | 5.4   | 7.7   | mS    | 9, 10, 11      |

| $\Delta t_{Ch}$ / $\Delta V_{CC}$ | Drift In Capacitor Charge Time                | $\Delta V_{CC} = 12,$<br>$V_{CC} = 4.5 \text{V to } 16.5 \text{V}$ |          | -820  | 820   | nS/V  | 9              |

| Δt <sub>Ch</sub> / ΔT             | Temperature Coefficient Capacitor Charge Time | V <sub>CC</sub> = 16.5V                                            | (Note 6) | -68   | 68    | nS/°C | 10, 11         |

| t <sub>Res</sub>                  | Reset Time                                    | $V_{CC} = 16.5V$                                                   |          |       | 1.5   | μS    | 9, 11          |

|                                   |                                               |                                                                    |          |       | 2.0   | μS    | 10             |

# **DC Drift Parameters**

Delta calculations performed on JAN S devices at Group B, Subgroup 5, only.

| Symbol           | Parameter                               | Conditions                                        | Notes | Min   | Max  | Unit | Sub-<br>groups |

|------------------|-----------------------------------------|---------------------------------------------------|-------|-------|------|------|----------------|

| $V_{Trig}$       | Trigger Voltage                         | V <sub>CC</sub> = 16.5V                           |       | -0.05 | 0.05 | ٧    | 1              |

| V <sub>Th</sub>  | Threshold Voltage                       | V <sub>CC</sub> = 16.5V                           |       | -0.05 | 0.05 | V    | 1              |

| V <sub>OL</sub>  | Logical "0" Output Voltage              | V <sub>CC</sub> = 16.5V, I <sub>Sink</sub> = 10mA |       | -0.05 | 0.05 | V    | 1              |

| I <sub>CEX</sub> | Discharge Transistor Leakage<br>Current | V <sub>CC</sub> = 16.5V                           |       | -50   | 50   | nA   | 1              |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

Note 3: Human body model, 1.5K $\Omega$  in series with 100pF.

Note 4: Parameter tested go-no-go, only.

Note 5: Datalog reading of 0.7V will reflect the Reset Voltage levels passing and a reading of 0.5V or 1.5V reflects the Reset voltage levels failing the low level or high level respectfully.

Note 6: Calculated parameter.

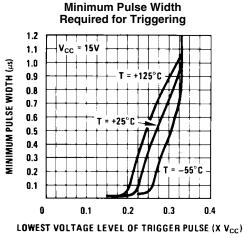

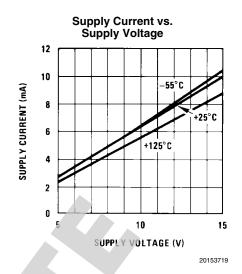

# **Typical Performance Characteristics**

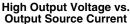

20153721

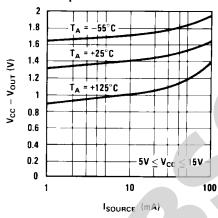

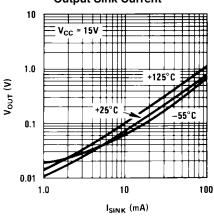

# Low Output Voltage vs. Output Sink Current

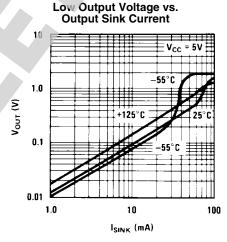

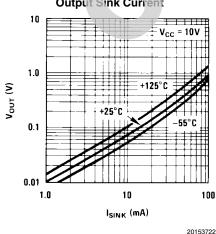

# Low Output Voltage vs. Output Sink Current

20153723

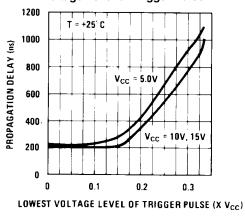

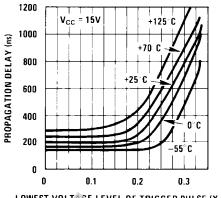

# Output Propagation Delay vs. Voltage Level of Trigger Pulse

# Output Propagation Delay vs. Voltage Level of Trigger Pulse

LOWEST VOLTAGE LEVEL OF TRIGGER PULSE (X Vcc)

20153725

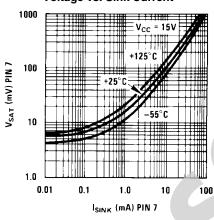

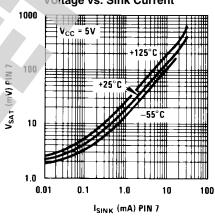

### Discharge Transistor (Pin 7) Voltage vs. Sink Current

20153724

20153726

# Discharge Transistor (Pin 7) Voltage vs. Sink Current

20153727

# **Applications Information**

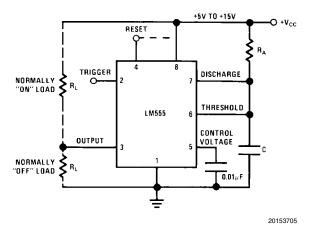

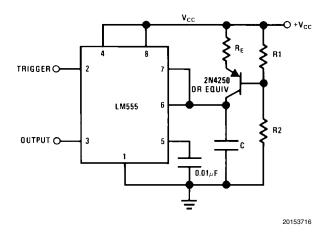

### **MONOSTABLE OPERATION**

In this mode of operation, the timer functions as a one-shot (*Figure 1*). The external capacitor is initially held discharged by a transistor inside the timer. Upon application of a negative trigger pulse of less than 1/3  $\rm V_{CC}$  to pin 2, the flip-flop is set which both releases the short circuit across the capacitor and drives the output high.

FIGURE 1. Monostable

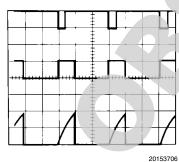

The voltage across the capacitor then increases exponentially for a period of t = 1.1  $\rm R_A$  C, at the end of which time the voltage equals 2/3  $\rm V_{CC}$ . The comparator then resets the flipflop which in turn discharges the capacitor and drives the output to its low state. *Figure 2* shows the waveforms generated in this mode of operation. Since the charge and the threshold level of the comparator are both directly proportional to supply voltage, the timing interval is independent of supply.

$V_{CC} = 5V$   $TIME = 0.1 \ ms/DIV.$   $R_{A} = 9.1k\Omega$

$C = 0.01 \mu F$

Top Trace: Input 5V/Div.

Middle Trace: Output 5V/Div.

Bottom Trace: Capacitor Voltage 2V/Div.

FIGURE 2. Monostable Waveforms

During the timing cycle when the output is high, the further application of a trigger pulse will not effect the circuit so long as the trigger input is returned high at least 10µs before the end of the timing interval. However the circuit can be reset

during this time by the application of a negative pulse to the reset terminal (pin 4). The output will then remain in the low state until a trigger pulse is again applied.

When the reset function is not in use, it is recommended that it be connected to  $V_{\text{CC}}$  to avoid any possibility of false triggering.

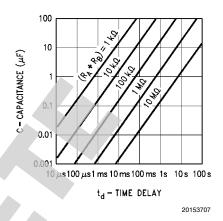

Figure 3 is a nomograph for easy determination of R, C values for various time delays.

**NOTE:** In monostable operation, the trigger should be driven high before the end of timing cycle.

FIGURE 3. Time Delay

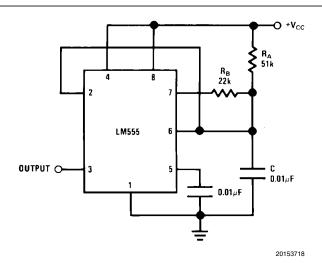

### **ASTABLE OPERATION**

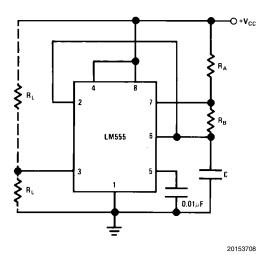

If the circuit is connected as shown in *Figure 4* (pins 2 and 6 connected) it will trigger itself and free run as a multivibrator. The external capacitor charges through  $R_{\rm A}+R_{\rm B}$  and discharges through  $R_{\rm B}$ . Thus the duty cycle may be precisely set by the ratio of these two resistors.

FIGURE 4. Astable

In this mode of operation, the capacitor charges and discharges between 1/3  $V_{\rm CC}$  and 2/3  $V_{\rm CC}.$  As in the triggered mode, the charge and discharge times, and therefore the frequency are independent of the supply voltage.

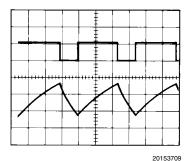

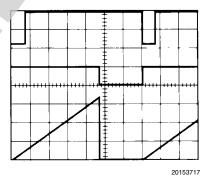

Figure 5 shows the waveforms generated in this mode of operation.

$V_{CC} = 5V$ TIME = 20µs/DIV.

$C = 0.01 \mu F$

Top Trace: Output 5V/Div.

Bottom Trace: Capacitor Voltage 1V/Div.

$R_A = 3.9k\Omega$  $R_B = 3k\Omega$

### FIGURE 5. Astable Waveforms

The charge time (output high) is given by:

$$t_1 = 0.693 (R_A + R_B) C$$

And the discharge time (output low) by:

$$t_2 = 0.693 (R_B) C$$

Thus the total period is:

$$T = t_1 + t_2 = 0.693 (R_A + 2R_B) C$$

The frequency of oscillation is:

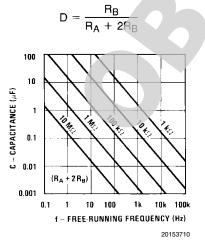

$$f = \frac{1}{T} = \frac{1.44}{(R_A + 2 R_B) C}$$

Figure 6 may be used for quick determination of these RC values.

The duty cycle is:

**FIGURE 6. Free Running Frequency**

### **FREQUENCY DIVIDER**

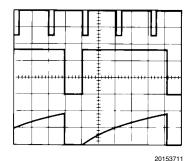

The monostable circuit of *Figure 1* can be used as a frequency divider by adjusting the length of the timing cycle. *Figure 7* shows the waveforms generated in a divide by three circuit.

$V_{CC} = 5V$ TIME = 20µs/DIV.  $R_A = 9.1k\Omega$

Top Trace: Input 4V/Div. Middle Trace: Output 2V/Div. Bottom Trace: Capacitor 2V/Div.

$C = 0.01 \mu F$

# FIGURE 7. Frequency Divider

## **PULSE WIDTH MODULATOR**

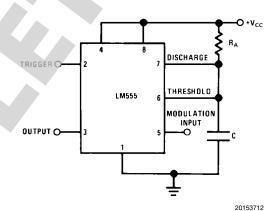

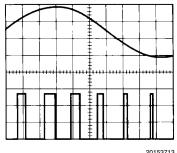

When the timer is connected in the monostable mode and triggered with a continuous pulse train, the output pulse width can be modulated by a signal applied to pin 5. *Figure 8* shows the circuit, and in *Figure 9* are some waveform examples.

FIGURE 8. Pulse Width Modulator

$V_{CC} = 5V$  Top Trace: Modulation 1V/Div. TIME = 0.2 ms/DIV. Bottom Trace: Output Voltage 2V/Div.

$R_A = 9.1k\Omega$

$C = 0.01 \mu F$

FIGURE 9. Pulse Width Modulator

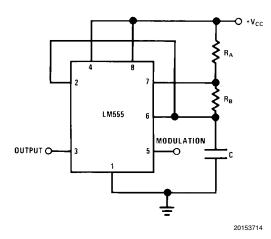

## **PULSE POSITION MODULATOR**

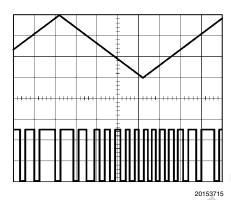

This application uses the timer connected for astable operation, as in *Figure 10*, with a modulating signal again applied to the control voltage terminal. The pulse position varies with the modulating signal, since the threshold voltage and hence

the time delay is varied. *Figure 11* shows the waveforms generated for a triangle wave modulation signal.

**FIGURE 10. Pulse Position Modulator**

$V_{CC} = 5V$ TIME = 0.1 ms/DIV.

Top Trace: Modulation Input 1V/Div.

Modulation Input 1V/Div.

$R_A = 3.9k\Omega$

$R_B = 3k\Omega$  $C = 0.01\mu F$

FIGURE 11. Pulse Position Modulator

## **LINEAR RAMP**

When the pull-up resistor,  $R_{\rm A}$ , in the monostable circuit is replaced by a constant current source, a linear ramp is generated. *Figure 12* shows a circuit configuration that will perform this function.

FIGURE 12.

Figure 13 shows waveforms generated by the linear ramp. The time interval is given by:

$$T = \frac{2/3 \text{ V}_{CC} \text{ R}_{E} (\text{R}_{1} + \text{R}_{2}) \text{ C}}{\text{R}_{1} \text{ V}_{CC} - \text{V}_{BE} (\text{R}_{1} + \text{R}_{2})}$$

$$\text{V}_{BE} \cong 0.6 \text{V}$$

V<sub>BE</sub> 0.6V

$V_{CC} = 5V$

Top Trace: Input 3V/Div.

TIME = 20µs/DIV. Middle Trace: Output 5V/Div.

$R_1 = 47k\Omega$  Bottom Trace: Capacitor Voltage 1V/Div.

$R_2 = 100 k\Omega$   $R_E = 2.7 \ k\Omega$   $C = 0.01 \ \mu F$

FIGURE 13. Linear Ramp

# **50% DUTY CYCLE OSCILLATOR**

For a 50% duty cycle, the resistors  $\rm R_A$  and  $\rm R_B$  may be connected as in *Figure 14*. The time period for the output high is the same as previous,  $\rm t_1=0.693~R_A$  C. For the output low it is  $\rm t_2=$

$$\left[ (R_A \, R_B)/(R_A \, + \, R_B) \right] C \, \, \ell n \left[ \frac{R_B - 2 R_A}{2 R_B - \, R_A} \right]$$

Thus the frequency of oscillation is

$$\mathfrak{f}=\frac{1}{t_1+t_2}$$

FIGURE 14. 50% Duty Cycle Oscillator

Note that this circuit will not oscillate if  $\rm R_B$  is greater than 1/2  $\rm R_A$  because the junction of  $\rm R_A$  and  $\rm R_B$  cannot bring pin 2 down to 1/3  $\rm V_{CC}$  and trigger the lower comparator.

# **ADDITIONAL INFORMATION**

Adequate power supply bypassing is necessary to protect associated circuitry. Minimum recommended is  $0.1\mu F$  in parallel with  $1\mu F$  electrolytic.

Lower comparator storage time can be as long as  $10\mu s$  when pin 2 is driven fully to ground for triggering. This limits the monostable pulse width to  $10\mu s$  minimum.

Delay time reset to output is  $0.47\mu s$  typical. Minimum reset pulse width must be  $0.3\mu s$ , typical.

Pin 7 current switches within 30ns of the output (pin 3) voltage.

# **Revision History**

| Date Released | Revision | Section                          | Changes                                                                                                                                                                  |

|---------------|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/04/05      | А        | New Release to corporate format  | 1 MDS datasheet converted into corporate format. MJLM555-X Rev 1A0 to be archived                                                                                        |

| 07/25/06      | В        | Applications Information, page 8 | Correct a typo in the paragraph after figure 1 (change the word internal to interval) to reflect same change made to Commercial data sheet. Revision A will be Archived. |

| 09/27/2010    | С        | Obsolete Data Sheet              | End Of Life on Product/NSID Sept. 1998                                                                                                                                   |

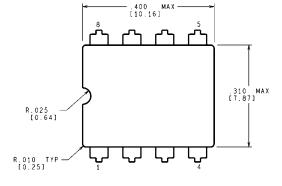

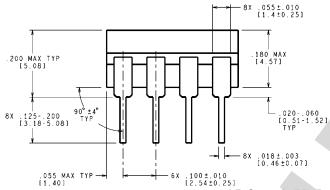

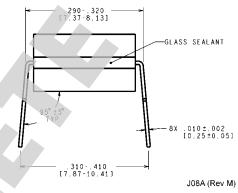

# Physical Dimensions inches (millimeters) unless otherwise noted

## CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

8LD Ceramic Dip Package (J) NS Package Number J03A

# **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com

National Semiconductor Asia **Pacific Technical Support Center** Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: ipn.feedback@nsc.com

201537 Version 3 Revision 1 Print Date/Time: 2010/10/01 00:30:59