# **2.0 GHz PLL Frequency** Synthesizers

# Include On–Board 64/65 Prescalers

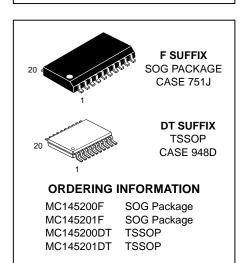

The MC145200 and MC145201 are single–package synthesizers with serial interfaces capable of direct usage up to 2.0 GHz. A special architecture makes these PLLs very easy to program because a byte–oriented format is utilized. Due to the patented BitGrabber<sup>™</sup> registers, no address/steering bits are required for *random access* of the three registers. Thus, tuning can be accomplished via a 3–byte serial transfer to the 24–bit A register. The interface is both SPI and MICROWIRE<sup>™</sup> compatible.

Each device features a single-ended current source/sink phase detector output and a double-ended phase detector output. Both phase detectors have linear transfer functions (no dead zones). The maximum current of the single-ended phase detector output is determined by an external resistor tied from the Rx pin to ground. This current can be varied via the serial port.

The MC145200 features logic–level converters and high–voltage phase/ frequency detectors; the detector supply may range up to 9.5 V. The MC145201 has lower–voltage phase/frequency detectors optimized for single–supply systems of 5 V  $\pm$ 10%.

Each part includes a differential RF input which may be operated in a single-ended mode. Also featured are on-board support of an external crystal and a programmable reference output. The R, A, and N counters are fully programmable. The C register (configuration register) allows the parts to be configured to meet various applications. A patented feature allows the C register to shut off unused outputs, thereby minimizing system noise and interference.

In order to have consistent lock times and prevent erroneous data from being loaded into the counters, on-board circuitry synchronizes the update of the A register if the A or N counters are loading. Similarly, an update of the R register is synchronized if the R counter is loading.

The double–buffered R register allows new divide ratios to be presented to the three counters (R, A, and N) simultaneously.

- Maximum Operating Frequency: 2000 MHz @ Vin = 200 mV p-p

- Operating Supply Current: 12 mA Nominal

- Operating Supply Voltage Range (V<sub>DD</sub> and V<sub>CC</sub> Pins): 4.5 to 5.5 V

- Operating Supply Voltage Range of Phase Detectors (VPD Pin) MC145200: 8.0 to 9.5 V MC145201: 4.5 to 5.5 V

- Current Source/Sink Phase Detector Output Capability: 2 mA Maximum

- Gain of Current Source/Sink Phase/Frequency Detector Controllable via Serial Port

- Operating Temperature Range: 40 to +85°C

- R Counter Division Range: (1 and) 5 to 8191

- Dual-Modulus Capability Provides Total Division up to 262,143

- High–Speed Serial Interface: 4 Mbps

- OUTPUT A Pin, When Configured as Data Out, Permits Cascading of Devices

- Two General–Purpose Digital Outputs OUTPUT A: Totem–Pole (Push–Pull)

- OUTPUT B: Open–Drain

- Power–Saving Standby Feature with Orderly Recovery for Minimizing Lock Times, Standby Current: 30  $\mu A$

- Evaluation Kit Available (Part Numbers MC145200EVK and MC145201EVK)

- See Application Note AN1253/D for Low–Pass Filter Design, and AN1277/D for Offset Reference PLLs for Fine Resolution or Fast Hopping

BitGrabber is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

REV 4 1/98 TN98012300

© Motorola, Inc. 1998

| Р      | IN ASSI | GNMENT               |

|--------|---------|----------------------|

| REFout | [1•     | 20 REF <sub>in</sub> |

| LD     | [ 2     | 19 🛛 D <sub>in</sub> |

| ٩R     | 3       | 18 🛛 CLK             |

| φV     | [ 4     | 17 🛛 ENB             |

| VPD    | [ 5     | 16 🗌 OUTPUT A        |

| PDout  | 6       | 15 🗌 OUTPUT B        |

| GND    | 07      | 14 🛛 V <sub>DD</sub> |

| Rx     | 8 🛛     | 13 🛛 TEST 2          |

| TEST 1 | 0       | 12 🛛 V <sub>CC</sub> |

| fin    | [ 10    | 11 ] f <sub>in</sub> |

#### **BLOCK DIAGRAM**

PIN 7 = GND (COMMON GROUND)

MAXIMUM RATINGS\* (Voltages Referenced to GND, unless otherwise stated)

| Symbol                               | Parameter                                                          | Value                        | Unit |

|--------------------------------------|--------------------------------------------------------------------|------------------------------|------|

| V <sub>CC</sub> ,<br>V <sub>DD</sub> | DC Supply Voltage (Pins 12 and 14)                                 | -0.5 to +6.0                 | V    |

| V <sub>PD</sub>                      | DC Supply Voltage (Pin 5) MC1452<br>MC1452                         |                              | V    |

| V <sub>in</sub>                      | DC Input Voltage                                                   | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Vout                                 | DC Output Voltage<br>(except OUTPUT B, PD <sub>out</sub> ,         | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Vout                                 | DC Output Voltage (OUTPUT B, PD <sub>out</sub> , $\phi_R$ , $\phi$ | V) -0.5 to VPD +0.5          | V    |

| I <sub>in</sub> , I <sub>PD</sub>    | DC Input Current, per Pin (Includes $V_{PD}$ )                     | ±10                          | mA   |

| lout                                 | DC Output Current, per Pin                                         | ±20                          | mA   |

| IDD                                  | DC Supply Current, $V_{DD}$ and GND Pins                           | ±30                          | mA   |

| PD                                   | Power Dissipation, per Package                                     | 300                          | mW   |

| T <sub>stg</sub>                     | Storage Temperature                                                | -65 to +150                  | °C   |

| ТL                                   | Lead Temperature,<br>1 mm from Case for 10 seconds                 | 260                          | °C   |

\* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descriptions section.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Voltages Referenced to GND}, T_A = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise stated}; MC145200: V_{PD} = 8.0 \text{ to } 9.5 \text{ V}; MC145201: V_{PD} = 4.5 \text{ to } 5.5 \text{ V} \text{ with } V_{DD} \leq V_{PD}.)$

| Symbol           | Parameter                                                                                                                    | Test Condition                                                                                                                                                                                                                                           | Guaranteed<br>Limit   | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|

| VIL              | Maximum Lo <u>w–Le</u> vel Input Voltage<br>(D <sub>in</sub> , CLK, ENB, REF <sub>in</sub> )                                 | Device in Reference Mode, DC Coupled                                                                                                                                                                                                                     | $0.3 \times V_{DD}$   | V    |

| VIH              | Minimum Hig <u>h–Le</u> vel Input Voltage<br>(D <sub>In</sub> , CLK, ENB, REF <sub>In</sub> )                                | Device in Reference Mode, DC Coupled                                                                                                                                                                                                                     | $0.7 \times V_{DD}$   | V    |

| V <sub>hys</sub> | Minimum Hysteresis Voltage (CLK, ENB)                                                                                        |                                                                                                                                                                                                                                                          | 300                   | mV   |

| VOL              | Maximum Low–Level Output Voltage<br>(REF <sub>out</sub> , OUTPUT A)                                                          | $I_{out} = 20 \ \mu A$ , Device in Reference Mode                                                                                                                                                                                                        | 0.1                   | V    |

| Vон              | Minimum High–Level Output Voltage<br>(REF <sub>out</sub> , OUTPUT A)                                                         | $I_{out} = -20 \ \mu$ A, Device in Reference Mode                                                                                                                                                                                                        | V <sub>DD</sub> – 0.1 | V    |

| IOL              | $\begin{array}{l} \mbox{Minimum Low-Level Output Current} \\ (\mbox{REF}_{out}, \mbox{LD}, \phi_{R}, \phi_{V}) \end{array}$  | $V_{out} = 0.4 V$                                                                                                                                                                                                                                        | 0.36                  | mA   |

| IOH              | $\begin{array}{l} \mbox{Minimum High-Level Output Current} \\ (\mbox{REF}_{out}, \mbox{LD}, \phi_{R}, \phi_{V}) \end{array}$ | $V_{out} = V_{DD} - 0.4 V$ for REF <sub>out</sub> , LD<br>$V_{out} = V_{PD} - 0.4 V$ for $\phi_R$ , $\phi_V$                                                                                                                                             | -0.36                 | mA   |

| IOL              | Minimum Low–Level Output Current<br>(OUTPUT A, OUTPUT B)                                                                     | $V_{out} = 0.4 V$                                                                                                                                                                                                                                        | 1.0                   | mA   |

| lон              | Minimum High–Level Output Current<br>(OUTPUT A Only)                                                                         | $V_{out} = V_{DD} - 0.4 V$                                                                                                                                                                                                                               | - 0.6                 | mA   |

| l <sub>in</sub>  | Maximum Inp <u>ut Le</u> akage Current<br>(D <sub>in</sub> , CLK, ENB, REF <sub>in</sub> )                                   | $V_{in} = V_{DD}$ or GND, Device in XTAL Mode                                                                                                                                                                                                            | ± 1.0                 | μA   |

| l <sub>in</sub>  | Maximum Input Current<br>(REF <sub>in</sub> )                                                                                | V <sub>in</sub> = V <sub>DD</sub> or GND, Device in Reference Mode                                                                                                                                                                                       | ± 150                 | μA   |

| loz              | Maximum Output Leakage Current (PD <sub>OUt</sub> )                                                                          | Vout = VPD - 0.5 or 0.5 VMC145200Output in High-Impedance StateMC145201                                                                                                                                                                                  | ± 150<br>± 200        | nA   |

| loz              | Maximum Output Leakage Current<br>(OUTPUT B)                                                                                 | V <sub>out</sub> = V <sub>PD</sub> or GND,<br>Output in High–Impedance State                                                                                                                                                                             | ± 10                  | μA   |

| ISTBY            | Maximum Standby Supply Current<br>(V <sub>DD</sub> + V <sub>PD</sub> Pins)                                                   | $V_{in} = V_{DD}$ or GND; Outputs Open; Device in Standby<br>Mode, Shut–Down Crystal Mode or REF <sub>OUt</sub> –Static–Low<br>Reference Mode; OUTPUT B Controlling V <sub>CC</sub> per<br>Figure 22                                                     | 30                    | μA   |

| IPD              | Maximum Phase Detector<br>Quiescent Current (V <sub>PD</sub> Pin)                                                            | $ \begin{array}{l} \mbox{Bit C6} = \mbox{High Which Selects Phase Detector A,} \\ \mbox{PD}_{out} = \mbox{Open, PD}_{out} = \mbox{Static Low or High, Bit C4} = \mbox{Low} \\ \mbox{Which is $\textit{not}$ Standby, $I_{Rx} = 113 $\mu$A} \end{array} $ |                       | μA   |

|                  |                                                                                                                              | Bit C6 = Low Which Selects Phase Detector B, $\phi_R$ and $\phi_V$ = Open, $\phi_R$ and $\phi_V$ = Static Low or High, Bit C4 = Low Which is <i>not</i> Standby                                                                                          | 30                    |      |

| Γ                | Total Operating Supply Current<br>(VDD + VPD + VCC Pins)                                                                     |                                                                                                                                                                                                                                                          | *                     | mA   |

\* The nominal value = 12 mA. This is not a guaranteed limit.

### ANALOG CHARACTERISTICS—CURRENT SOURCE/SINK OUTPUT—PDout

(I<sub>out</sub>  $\leq$  2 mA, V<sub>DD</sub> = V<sub>CC</sub> = 4.5 to 5.5 V, V<sub>DD</sub>  $\leq$  V<sub>PD</sub>. Voltages Referenced to GND)

| Parameter                                | Test Condition                                     | V <sub>PD</sub> | Guaranteed<br>Limit | Unit |

|------------------------------------------|----------------------------------------------------|-----------------|---------------------|------|

| Maximum Source Current Variation         | MC145200: $V_{out} = 0.5 \times V_{PD}$            | 8.0             | ± 20                | %    |

|                                          |                                                    | 9.5             | ± 20                |      |

|                                          | MC145201: V <sub>out</sub> = 0.5 × V <sub>PD</sub> | 4.5             | ± 20                | %    |

|                                          |                                                    | 5.5             | ± 20                |      |

| Maximum Sink-vs-Source Mismatch (Note 3) | MC145200: V <sub>out</sub> = 0.5 × V <sub>PD</sub> | 8.0             | 12                  | %    |

|                                          |                                                    | 9.5             | 12                  |      |

|                                          | MC145201: V <sub>out</sub> = 0.5 × V <sub>PD</sub> | 4.5             | 12                  | %    |

|                                          |                                                    | 5.5             | 12                  | 1    |

| Output Voltage Range (Note 3)            | MC145200: $I_{out}$ variation $\leq 20\%$          | 8.0             | 0.5 to 7.5          | V    |

|                                          |                                                    | 9.5             | 0.5 to 9.0          |      |

|                                          | MC145201: $I_{out}$ variation $\leq 20\%$          | 4.5             | 0.5 to 4.0          | V    |

|                                          |                                                    | 5.5             | 0.5 to 5.0          | 1    |

NOTES:

1. Percentages calculated using the following formula: (Maximum Value – Minimum Value)/Maximum Value.

2. See Rx Pin Description for external resistor values.

3. This parameter is guaranteed for a given temperature within -40 to  $+85^{\circ}$ C.

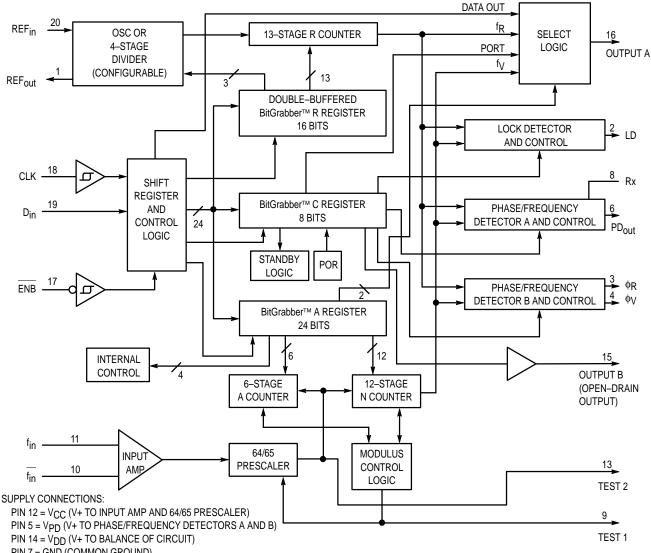

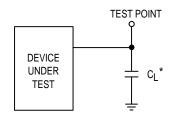

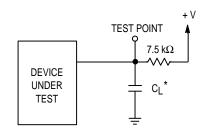

# **AC INTERFACE CHARACTERISTICS** ( $V_{DD}$ = 4.5 to 5.5 V, $T_A$ = - 40 to +85°C, $C_L$ = 50 pF, Input $t_r$ = $t_f$ = 10 ns; MC145200: $V_{PD}$ = 8.0 to 9.5 V; MC145201: $V_{PD}$ = 4.5 to 5.5 V with $V_{DD} \le V_{PD}$ )

| Symbol                              | Parameter                                                                                    | Figure No. | Guaranteed<br>Limit | Unit |

|-------------------------------------|----------------------------------------------------------------------------------------------|------------|---------------------|------|

| fclk                                | Serial Data Clock Frequency (Note: Refer to Clock t <sub>w</sub> below)                      | 1          | dc to 4.0           | MHz  |

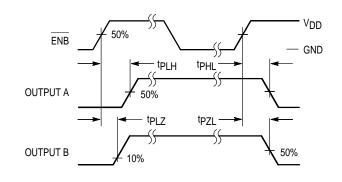

| <sup>t</sup> PLH <sup>, t</sup> PHL | Maximum Propagation Delay, CLK to OUTPUT A (Selected as Data Out)                            | 1, 5       | 105                 | ns   |

| <sup>t</sup> PLH <sup>, t</sup> PHL | Maximum Propagation Delay, ENB to OUTPUT A (Selected as Port)                                | 2, 5       | 100                 | ns   |

| <sup>t</sup> PZL <sup>, t</sup> PLZ | Maximum Propagation Delay, ENB to OUTPUT B                                                   | 2, 6       | 120                 | ns   |

| <sup>t</sup> TLH <sup>, t</sup> THL | Maximum Output Transition Time, OUTPUT A and OUTPUT B;<br>t <sub>THL</sub> only, on OUTPUT B | 1, 5, 6    | 100                 | ns   |

| C <sub>in</sub>                     | Maximum Input Capacitance – D <sub>in</sub> , ENB, CLK,                                      |            | 10                  | pF   |

#### TIMING REQUIREMENTS

(V<sub>DD</sub> = 4.5 to 5.5 V, T<sub>A</sub> = -40 to  $+85^{\circ}$ C, Input t<sub>f</sub> = t<sub>f</sub> = 10 ns unless otherwise indicated)

| Symbol                                              | Parameter                                            | Figure No. | Guaranteed<br>Limit | Unit   |

|-----------------------------------------------------|------------------------------------------------------|------------|---------------------|--------|

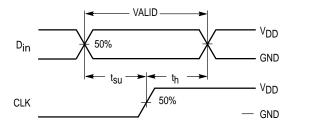

| t <sub>su</sub> , t <sub>h</sub>                    | Minimum Setup and Hold Times, D <sub>in</sub> vs CLK | 3          | 20                  | ns     |

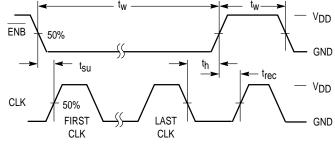

| t <sub>su</sub> , t <sub>h</sub> , t <sub>rec</sub> | Minimum Setup, Hold and Recovery Times, ENB vs CLK   | 4          | 100                 | ns     |

| t <sub>w</sub>                                      | Minimum Pulse Width, ENB                             | 4          | *                   | cycles |

| t <sub>w</sub>                                      | Minimum Pulse Width, CLK                             | 1          | 125                 | ns     |

| t <sub>r</sub> , t <sub>f</sub>                     | Maximum Input Rise and Fall Times, CLK               | 1          | 100                 | μs     |

\* The minimum limit is 3  $\text{REF}_{in}$  cycles or 195  $f_{in}$  cycles, whichever is greater.

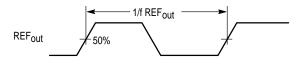

# SWITCHING WAVEFORMS

Figure 3.

Figure 4.

\*Includes all probe and fixture capacitance.

\*Includes all probe and fixture capacitance.

#### Figure 6. Test Circuit

|                   |                                                                                                |                                                                                                                                                                 | Figure |                        | inteed<br>g Range          |        |

|-------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|----------------------------|--------|

| Symbol            | Parameter                                                                                      | Test Condition                                                                                                                                                  | No.    | Min                    | Max                        | Unit   |

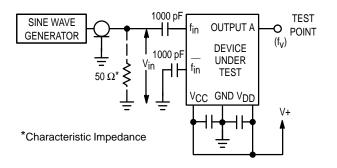

| Vin               | Input Voltage Range, f <sub>in</sub>                                                           | 500 MHz $\leq$ f <sub>in</sub> $\leq$ 2000 MHz                                                                                                                  | 7      | 200                    | 1500                       | mV p–p |

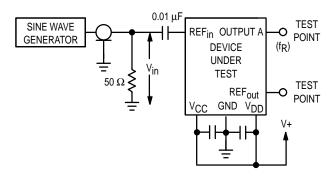

| fref              | Input Frequency, REF <sub>in</sub> MC145200<br>Externally Driven in<br>Reference Mode MC145201 | $ \begin{array}{l} V_{in} \geq 400 \mbox{ mV } pp \\ V_{in} \geq 1 \mbox{ V } pp \\ V_{in} \geq 400 \mbox{ mV } pp \\ V_{in} \geq 1 \mbox{ V } pp \end{array} $ | 8      | 13<br>6*<br>12<br>4.5* | 27<br>27<br>27<br>27<br>27 | MHz    |

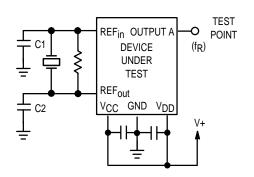

| <sup>f</sup> XTAL | Crystal Frequency, Crystal Mode                                                                | C1 $\leq$ 30 pF, C2 $\leq$ 30 pF, Includes Stray Capacitance                                                                                                    | 9      | 2                      | 15                         | MHz    |

| fout              | Output Frequency, REFout                                                                       | C <sub>L</sub> = 30 pF                                                                                                                                          | 10, 12 | dc                     | 10                         | MHz    |

| f                 | Operating Frequency of the Phase Detectors                                                     |                                                                                                                                                                 |        | dc                     | 2                          | MHz    |

| t <sub>W</sub>    | Output Pulse Width, LD, $\phi_R$ , and $\phi_V$ , — MC145200, MC145201                         | $f_R$ in Phase with $f_V$ , $C_L = 50$ pF,<br>$V_{PD} = 5.5$ V, $V_{DD} = V_{CC} = 5.0$ V                                                                       | 11, 12 | 17                     | 85                         | ns     |

| ttlh,<br>tthl     | Output Transition Times, LD, $\phi_V$ , and $\phi_R - MC145201$                                | $C_L = 50 \text{ pF}, V_{PD} = 5.5 \text{ V},$<br>$V_{DD} = V_{CC} = 5.0 \text{ V}$                                                                             | 11, 12 | _                      | 65                         | ns     |

| C <sub>in</sub>   | Input Capacitance f <sub>in</sub><br>REF <sub>in</sub>                                         |                                                                                                                                                                 |        | _                      | TBD<br>5                   | pF     |

\*If lower frequency is desired, use wave shaping or higher amplitude sinusoidal signal.

Figure 7. Test Circuit

Figure 9. Test Circuit–Crystal Mode

Figure 8. Test Circuit–Reference Mode

Figure 10. Switching Waveform

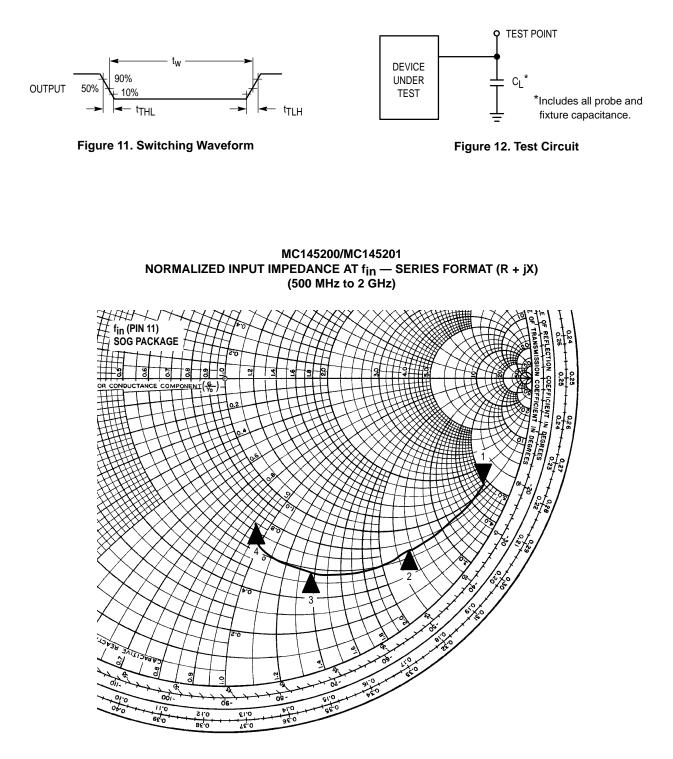

| Marker | Frequency<br>(GHz) | Resistance<br>(Ω) | Capacitive<br>Reactance (Ω) | Capacitance<br>(pF) |

|--------|--------------------|-------------------|-----------------------------|---------------------|

| 1      | 0.5                | 59.0              | - 240                       | 1.33                |

| 2      | 1                  | 34.7              | – 118                       | 1.35                |

| 3      | 1.5                | 28.3              | - 68.7                      | 1.54                |

| 4      | 2                  | 37.4              | - 45.7                      | 1.74                |

MOTOROLA

#### DIGITAL INTERFACE PINS

#### Din

# Serial Data Input (Pin 19)

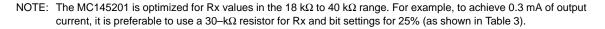

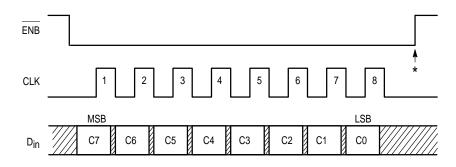

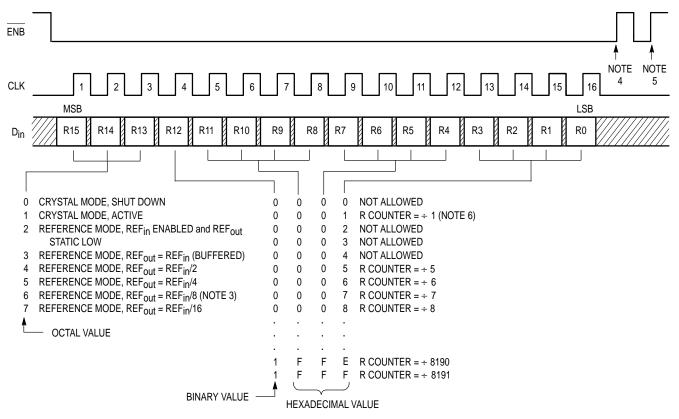

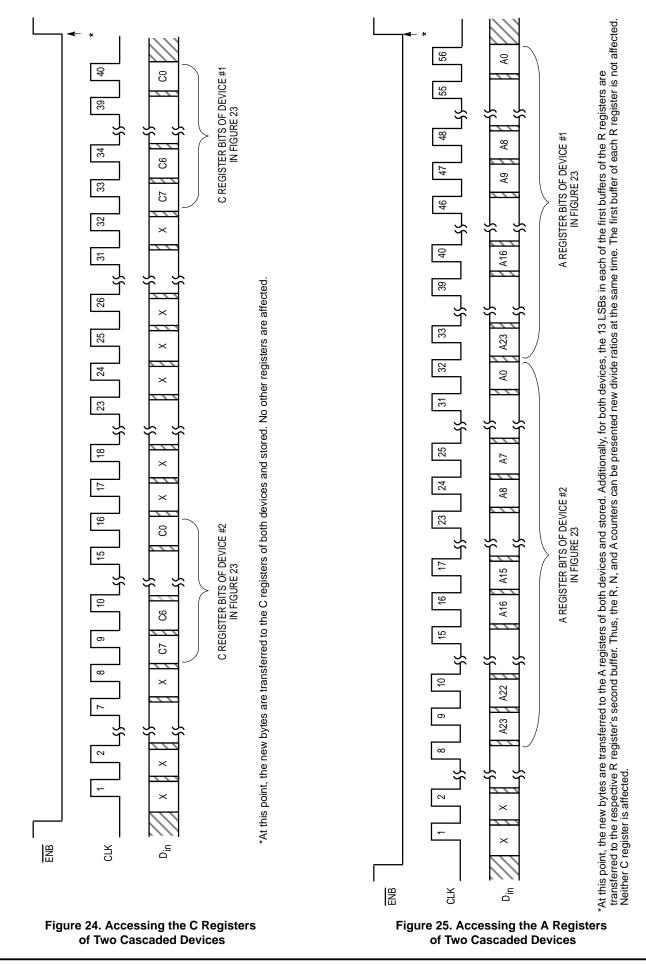

The bit stream begins with the most significant bit (MSB) and is shifted in on the low-to-high transition of CLK. The bit pattern is 1 byte (8 bits) long to access the C or configuration register, 2 bytes (16 bits) to access the first buffer of the R register, or 3 bytes (24 bits) to access the A register (see Table 1). The values in the C, R, and A registers do not change during shifting because the transfer of data to the registers is controlled by ENB.

#### CAUTION

The value programmed for the N–counter must be greater than or equal to the value of the A–counter.

The 13 least significant bits (LSBs) of the R register are double–buffered. As indicated above, data is latched into the first buffer on a 16–bit transfer. (The 3 MSBs are not double–buffered and have an immediate effect after a 16–bit transfer.) The second buffer of the R register contains the 13 bits for the R counter. This second buffer is loaded with the contents of the first buffer when the A register is loaded (a 24–bit transfer). This allows presenting new values to the R, A, and N counters simultaneously. If this is not required, then the 16–bit transfer may be followed by pulsing ENB low with no signal on the CLK pin. This is an alternate method of transferring data to the second buffer of the R register (see Figure 17).

The bit stream needs neither address nor steering bits due to the innovative BitGrabber registers. Therefore, all bits in the stream are available to be data for the three registers. Random access of any register is provided. That is, the registers may be accessed in any sequence. Data is retained in the registers over a supply range of 4.5 to 5.5 V. The formats are shown in Figures 15, 16, and 17.

$D_{in}$  typically switches near 50% of V\_DD to maximize noise immunity. This input can be directly interfaced to CMOS devices with outputs guaranteed to switch near rail-to-rail. When interfacing to NMOS or TTL devices, either a level shifter (MC74HC14A, MC14504B) or pull-up resistor of 1 k $\Omega$  to 10 k $\Omega$  must be used. Parameters to consider when sizing the resistor are worst-case IOL of the driving device, maximum tolerable power consumption, and maximum data rate.

| Table 1. Register Access                                 |

|----------------------------------------------------------|

| (MSBs are shifted in first; C0, R0, and A0 are the LSBs) |

| Number                                            | Accessed                                                                        | Bit                                                         |

|---------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|

| of Clocks                                         | Register                                                                        | Nomenclature                                                |

| 8<br>16<br>24<br>Other Values ≤ 32<br>Values > 32 | C Register<br>R Register<br>A Register<br>See Figure 13<br>See Figures<br>22–25 | C7, C6, C5,, C0<br>R15, R14, R13,, R0<br>A23, A22, A21,, A0 |

#### CLK Serial Data Clock Input (Pin 18)

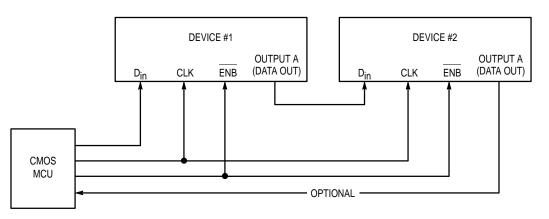

Low-to-high transitions on CLK shift bits available at the  $D_{in}$  pin, while high-to-low transitions shift bits from OUTPUT A (when configured as Data Out, see Pin 16). The 24–1/2-stage shift register is static, allowing clock rates down to dc in a continuous or intermittent mode.

Eight clock cycles are required to access the C register. Sixteen clock cycles are needed for the first buffer of the R register. Twenty–four cycles are used to access the A register. See Table 1 and Figures 15, 16, and 17. The number of clocks required for cascaded devices is shown in Figures 24 through 26.

CLK typically switches near 50% of V<sub>DD</sub> and has a Schmitt-triggered input buffer. Slow CLK rise and fall times are allowed. See the last paragraph of  $D_{in}$  for more information.

#### NOTE

To guarantee proper operation of the power-on reset (POR) circuit, the CLK pin must <u>be held</u> at GND (with ENB being a don't care) or ENB must be held at the potential of the V+ pin (with CLK being a don't care) during power-up. As an alternative, the bit sequence of Figure 13 may be used.

#### ENB

#### Active Low Enable Input (Pin 17)

This pin is used to activate the serial int<u>erface</u> to allow the transfer of data to/from the device. When ENB is in an inactive high state, shifting is inhibited and the port is <u>held</u> in the initialized state. To transfer data to the device, ENB (which must start inactive high) is taken low, a serial transfer is made via D<sub>in</sub> and CLK, and ENB is taken back high. The low-to-high transition on ENB transfers data to the C or A registers and first buffer of the R register, depending on the data stream length per Table 1.

#### NOTE

Transitions on ENB must not be attempted while CLK is high. This puts the device out of synchronization with the microcontroller. Resynchronization occurs when ENB is high and CLK is low.

This input is also Schmitt–triggered and switches near 50% of  $V_{DD}$ , thereby minimizing the chance of loading erroneous data into the registers. See the last paragraph of **D**<sub>in</sub> for more information.

For POR information, see the note for the CLK pin.

# OUTPUT A

#### **Configurable Digital Output (Pin 16)**

OUTPUT A is selectable as  $f_R$ ,  $f_V$ , Data Out, or Port. Bits A22 and A23 in the A register control the selection; see Figure 16.

If A23 = A22 = high, OUTPUT A is configured as  $f_R$ . This signal is the buffered output of the 13–stage R counter. The  $f_R$  signal appears as normally low and pulses high, and can be used to verify the divide ratio of the R counter. This ratio extends from 5 to 8191 and is determined by the binary value loaded into bits R0 through R12 in the R register. Also, direct access to the phase detectors via the REF<sub>in</sub> pin is allowed by choosing a divide value of 1 (see Figure 17). The maximum frequency at which the phase detectors operate is 2 MHz. Therefore, the frequency of  $f_R$  should not exceed 2 MHz.

If A23 = high and A22 = low, OUTPUT A is configured as  $f_V$ . This signal is the buffered output of the 12–stage N counter. The  $f_V$  signal appears as normally low and pulses high, and can be used to verify the operation of the prescaler, A counter, and N counter. The divide ratio between the  $f_{in}$  input and the  $f_V$  signal is N × 64 + A. N is the divide ratio of the N counter and A is the divide ratio of the A counter. These ratios are determined by bits loaded into the A register. See Figure 16. The maximum frequency at which the phase detectors operate is 2 MHz. Therefore, the frequency of  $f_V$  should not exceed 2 MHz.

If A23 = low and A22 = high, OUTPUT A is configured as Data Out. This signal is the serial output of the 24–1/2–stage shift register. The bit stream is shifted out on the high–to–low transition of the CLK input. Upon power up, OUTPUT A is automatically configured as Data Out to facilitate cascading devices.

If A23 = A22 = low, OUTPUT A is configured as Port. This signal is a general–purpose digital output which may be used as an MCU port expander. This signal is low when the Port bit (C1) of the C register is low, and high when the Port bit is high.

#### OUTPUT B

#### **Open–Drain Digital Output (Pin 15)**

This signal is a general–purpose digital output which may be used as an MCU port expander. This signal is low when the Out B bit (C0) of the C register is low. When the Out B bit is high, OUTPUT B assumes the high–impedance state. OUTPUT B may be pulled up through an external resistor or active circuitry to any voltage less than or equal to the potential of the V<sub>PD</sub> pin. **Note**: the maximum voltage allowed on the V<sub>PD</sub> pin is 9.5 V for the MC145200 and 5.5 V for the MC145201.

Upon power–up, power–on reset circuitry forces OUT-PUT B to a low level.

#### **REFERENCE PINS**

# REF<sub>in</sub> and REF<sub>out</sub> Reference Input and Reference Output (Pins 20 and 1)

Configurable pins for a Crystal or an External Reference. This pair of pins can be configured in one of two modes: the crystal mode or the reference mode. Bits R13, R14, and R15 in the R register control the modes as shown in Figure 17.

In crystal mode, these pins form a reference oscillator when connected to terminals of an external parallel-resonant crystal. Frequency-setting capacitors of appropriate values as recommended by the crystal supplier are connected from each of the two pins to ground (up to a maximum of 30 pF each, including stray capacitance). An external resistor of 1 M $\Omega$  to 15 M $\Omega$  is connected directly across the pins to ensure linear operation of the amplifier. The device is designed to operate with crystals up to 15 MHz; the required connections are shown in Figure 8. To turn on the oscillator, bits R15, R14, and R13 must have an octal value of one (001 in binary, respectively). This is the active-crystal mode shown in Figure 17. In this mode, the crystal oscillator runs and the R Counter divides the crystal frequency, unless the part is in standby. If the part is placed in standby via the C register, the oscillator runs, but the R counter is stopped. However, if bits R15 to R13 have a value of 0, the oscillator is stopped, which saves additional power. This is the shutdown crystal mode (shown in Figure 17) and can be engaged whether in standby or not.

In the reference mode, REF<sub>in</sub> (Pin 20) accepts a signal up to 27 MHz from an external reference oscillator, such as a TCXO. A signal swinging from at least the V<sub>IL</sub> to V<sub>IH</sub> levels listed in the Electrical Characteristics table may be directly coupled to the pin. If the signal is less than this level, ac coupling must be used as shown in Figure 8. Due to an on-board resistor which is engaged in the reference modes, an external biasing resistor tied between REF<sub>in</sub> and REF<sub>out</sub> is not required.

With the reference mode, the REF<sub>out</sub> pin is configured as the output of a divider. As an example, if bits R15, R14, and R13 have an octal value of seven, the frequency at REF<sub>out</sub> is the REF<sub>in</sub> frequency divided by 16. In addition, Figure 17 shows how to obtain ratios of eight, four, and two. A ratio of one-to-one can be obtained with an octal value of three. Upon power up, a ratio of eight is automatically initialized. The maximum frequency capability of the REF<sub>out</sub> pin is 10 MHz. Therefore, for REF<sub>in</sub> frequencies above 10 MHz, the one-to-one ratio may not be used. Likewise, for REF<sub>in</sub> frequencies above 20 MHz, the ratio must be more than two.

If REF<sub>out</sub> is unused, an octal value of two should be used for R15, R14, and R13 and the REF<sub>out</sub> pin should be floated. A value of two allows REF<sub>in</sub> to be functional while disabling REF<sub>out</sub>, which minimizes dynamic power consumption and electromagnetic interference (EMI).

#### LOOP PINS

#### fin and fin

# Frequency Inputs (Pins 11 and 10)

These pins are frequency inputs from the VCO. These pins feed the on-board RF amplifier which drives the 64/65 prescaler. These inputs may be fed differentially. However, they usually are used in a single-ended configuration (shown in Figure 7). Note that  $f_{in}$  is driven while  $f_{in}$  must be tied to ground via a capacitor.

Motorola does not recommend driving  $f_{in}$  while terminating  $f_{in}$  because this configuration is not tested for sensitivity. The sensitivity is dependent on the frequency as shown in the Loop Specifications table.

#### PDout

#### Single–Ended Phase/Freq. Detector Output (Pin 6)

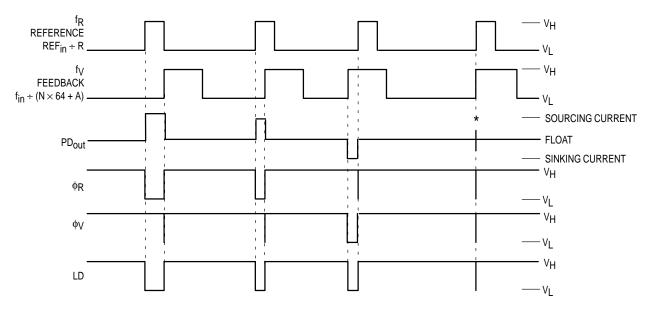

This is a three–state current–source/sink output for use as a loop error signal when combined with an external low–pass filter. The phase/frequency detector is characterized by a linear transfer function (no dead zone). The operation of the phase/ frequency detector is described below and is shown in Figure 18.

POL bit (C7) in the C register = low (see Figure 15)

- Frequency of  $f_V > f_R$  or Phase of  $f_V$  Leading  $f_R$ : currentsinking pulses from a floating state

- Frequency of  $f_V < f_R$  or Phase of  $f_V$  Lagging  $f_R$ : current– sourcing pulses from a floating state

- Frequency and Phase of  $f_V = f_R$ : essentially a floating state; voltage at pin determined by loop filter

- POL bit (C7) = high Frequency of  $f_V > f_R$  or Phase of  $f_V$  Leading  $f_R$ : current–

- sourcing pulses from a floating state

- Frequency of  $f_V < f_R$  or Phase of  $f_V$  Lagging  $f_R$ : currentsinking pulses from a floating state

Frequency and Phase of  $f_V = f_R$ : essentially a floating state; voltage at pin determined by loop filter

This output can be enabled, disabled, and inverted via the C register. If desired,  $PD_{out}$  can be forced to a floating state by utilization of the disable feature in the C register (bit C6). This is a patented feature. Similarly,  $PD_{out}$  is forced to the floating state when the device is put into standby (STBY bit C4 = high).

The PD<sub>out</sub> circuit is powered by VPD. The phase detector gain is controllable by bits C3, C2, and C1: gain (in amps per radian) = PD<sub>out</sub> current divided by  $2\pi$ .

# $\phi_R$ and $\phi_V$ (Pins 3 and 4) Double–Ended Phase/Frequency Detector Outputs

These outputs can be combined externally to generate a loop error signal. Through use of a Motorola patented technique, the detector's dead zone has been eliminated. Therefore, the phase/frequency detector is characterized by a linear transfer function. The operation of the phase/frequency detector is shown in Figure 18.

POL bit (C7) in the C register = low (see Figure 15)

- Frequency of  $f_V > f_R$  or Phase of  $f_V$  Leading  $f_R: \phi_V =$  negative pulses,  $\phi_R =$  essentially high

- Frequency of  $f_V < f_R$  or Phase of  $f_V$  Lagging  $f_R: \phi_V =$  essentially high,  $\phi_R =$  negative pulses

- Frequency and Phase of  $f_V = f_R: \phi_V$  and  $\phi_R$  remain essentially high, except for a small minimum time period when both pulse low in phase

POL bit (C7) = high

- Frequency of  $f_V > f_R$  or Phase of  $f_V$  Leading  $f_R: \phi_R =$  negative pulses,  $\phi_V =$  essentially high

- Frequency of  $f_V < f_R$  or Phase of  $f_V$  Lagging  $f_R: \phi_R =$  essentially high,  $\phi_V =$  negative pulses

- Frequency and Phase of  $f_V = f_R$ :  $\phi_V$  and  $\phi_R$  remain essentially high, except for a small minimum time period when both pulse low in phase

These outputs can be enabled, disabled, and interchanged via C register bits C6 or C4. This is a patented feature. Note that when disabled or in standby,  $\phi_R$  and  $\phi_V$  are forced to their rest condition (high state).

The  $\phi_R$  and  $\phi_V$  output signal swing is approximately from GND to VPD.

#### LD

#### Lock Detector Output (Pin 2)

This output is essentially at a high level with narrow lowgoing pulses when the loop is locked ( $f_R$  and  $f_V$  of the same phase and frequency). The output pulses low when  $f_V$  and  $f_R$ are out of phase or different frequencies. LD is the logical ANDing of  $\phi_R$  and  $\phi_V$  (see Figure 18).

This output can be enabled and disabled via the C register. This is a patented feature. Upon power up, on-chip initialization circuitry disables LD to a static low logic level to prevent a false "lock" signal. If unused, LD should be disabled and left open.

The LD output signal swing is approximately from GND to  $\ensuremath{\mathsf{V_{DD}}}$  .

# Rx

# External Resistor (Pin 8)

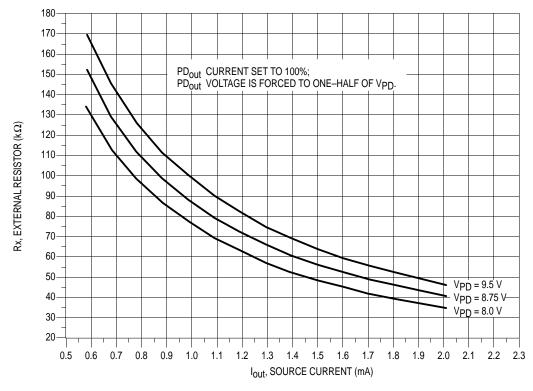

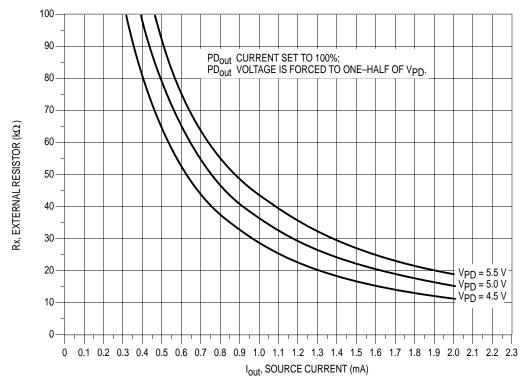

A resistor tied between this pin and GND, in conjunction with bits in the C register, determines the amount of current that the PD<sub>out</sub> pin sinks and sources. When bits C2 and C3 are both set high, the maximum current is obtained at PD<sub>out</sub>; see Tables 2 and 3 for other values of current. To achieve a maximum current of 2 mA, the resistor should be about 47 k $\Omega$  when V<sub>PD</sub> is 9 V or about 18 k $\Omega$  when V<sub>PD</sub> is 5.0 V. See Figure 14 if lower maximum current values are desired.

When the  $\phi_R$  and  $\phi_V$  outputs are used, the Rx pin may be floated.

#### **TEST POINT PINS**

# TEST 1

#### Modulus Control Signal (Pin 9)

This pin may be used in conjunction with the Test 2 pin for access to the on–board 64/65 prescaler. When Test 1 is low, the prescaler divides by 65. When high, the prescaler divides by 64.

#### CAUTION

This pin is an unbuffered output and *must* be floated in an actual application. This pin must be attached to an isolated pad with no trace.

# TEST 2

# Prescaler Output (Pin 13)

This pin may be used to access to the on-board 64/65 prescaler output.

#### CAUTION

This pin is an unbuffered output and *must* be floated in an actual application. This pin must be attached to an isolated pad with no trace.

#### POWER SUPPLY PINS

# VDD

#### **Positive Power Supply (Pin 14)**

This pin supplies power to the main CMOS digital portion of the device. The voltage range is + 4.5 to + 5.5 V with respect to the GND pin.

For optimum performance, V<sub>DD</sub> should be bypassed to GND using a low-inductance capacitor mounted very close to these pins. Lead lengths on the capacitor should be minimized.

# Vcc

# Positive Power Supply (Pin 12)

This pin supplies power to the RF amp and 64/65 prescaler. The voltage range is +4.5 to +5.5 V with respect to the GND pin. In the standby mode, the V<sub>CC</sub> pin still draws a few milliamps from the power supply. This current drain can be eliminated with the use of transistor Q1 as shown in Figure 22.

For optimum performance, V<sub>CC</sub> should be bypassed to GND using a low-inductance capacitor mounted very close to these pins. Lead lengths on the capacitor should be minimized.

# VPD Positive Power Supply (Pin 5)

This pin supplies power to both phase/frequency detectors A and B. The voltage applied on this pin must be no less than the potential applied to the V<sub>DD</sub> pin. The maximum voltage can be +9.5 V with respect to the GND pin for the MC145200 and +5.5 V for the MC145201.

For optimum performance, VPD should be bypassed to GND using a low-inductance capacitor mounted very close to these pins. Lead lengths on the capacitor should be minimized.

#### GND Ground (Pin 7)

Common ground.

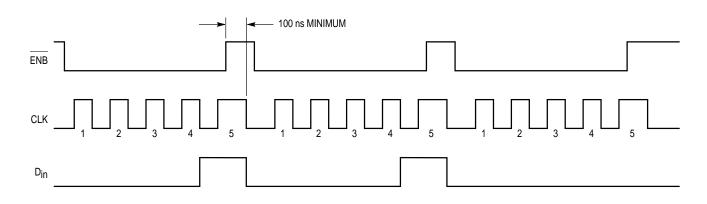

NOTE: It may not be convenient to control the ENB or CLK pins during power up per the Pin Descriptions. If this is the case, the part may be initialized through the serial port as shown in the figure above. The sequence is similar to accessing the registers except that the CLK must remain high at least 100 ns after ENB is brought high. Note that 3 groups of 5 bits are needed.

| $\label{eq:MC145200} \begin{array}{l} \text{MC145200} \\ \text{Nominal PD}_{out} \text{ Spurious Current vs } f_R \text{ Frequency} \\ (1 \ \text{V} < \text{PD}_{out} < \text{V}_{PD} - 1\text{V}) \end{array}$ |     |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| f <sub>R</sub> Current<br>(kHz) (RMS nA)                                                                                                                                                                         |     |  |  |

| 10                                                                                                                                                                                                               | 1.6 |  |  |

| 20                                                                                                                                                                                                               | 5.3 |  |  |

| 50                                                                                                                                                                                                               | 22  |  |  |

| 100                                                                                                                                                                                                              | 95  |  |  |

| 200                                                                                                                                                                                                              | 320 |  |  |

$\label{eq:MC145201} \begin{array}{l} \text{Nominal PD}_{out} \text{ Spurious Current vs } f_R \text{ Frequency} \\ (1 \ V < \ PD_{out} < \ V_{PD} - 1 V) \end{array}$

| <sup>f</sup> R<br>(kHz) | Current<br>(RMS nA) |  |  |

|-------------------------|---------------------|--|--|

| 10                      | 3.6                 |  |  |

| 20                      | 4.6                 |  |  |

| 50                      | 17                  |  |  |

| 100                     | 75                  |  |  |

| 200                     | 244                 |  |  |

|                         |                     |  |  |

NOTE: For information on spurious current measurement see AN1253/D, "An Improved PLL Design Method Without  $\omega_{\text{II}}$  and  $\zeta$ ".

Table 2. PD<sub>out</sub> Current, C1 = Low with OUTPUT A *NOT* Selected as "Port"; Also, Default Mode When OUTPUT A Selected as "Port"

| C3 | C2 PD <sub>out</sub> Curren |      |

|----|-----------------------------|------|

| 0  | 0                           | 70%  |

| 0  | 1                           | 80%  |

| 1  | 0                           | 90%  |

| 1  | 1                           | 100% |

# Table 3. PD<sub>out</sub> Current, C1 = High with OUTPUT A NOTSelected as "Port"

| C3 | C2 PD <sub>out</sub> Curre |      |

|----|----------------------------|------|

| 0  | 0                          | 25%  |

| 0  | 1                          | 50%  |

| 1  | 0                          | 75%  |

| 1  | 1                          | 100% |

Nominal MC145200 PDout Source Current vs Rx Resistance

Nominal MC145201 PDout Source Current vs Rx Resistance

Figure 14.

\* At this point, the new byte is transferred to the C register and stored. No other registers are affected.

- C7 POL: Selects the output polarity of the phase/frequency detectors. When set high, this bit inverts the polarity of PD<sub>out</sub> and interchanges the  $\phi_R$  function with  $\phi_V$  as depicted in Figure 18. Also see the phase detector output pin descriptions for more information. This bit is cleared low at power up.

- C6 PDA/B: Selects which phase/frequency detector is to be used. When set high, enables the output of phase/ frequency detector A (PD<sub>out</sub>) and disables phase/frequency detector B by forcing  $\phi_R$  and  $\phi_V$  to the static high state. When cleared low, phase/frequency detector B is enabled ( $\phi_R$  and  $\phi_V$ ) and phase/frequency detector A is disabled with PD<sub>out</sub> forced to the high–impedance state. This bit is cleared low at power up.

- C5 LDE: Enables the lock detector output (LD) when set high. When the bit is cleared low, the LD output is forced to a static low level. This bit is cleared low at power up.

- C4 STBY: When set high, places the CMOS section of device, which is powered by the V<sub>DD</sub> and V<sub>PD</sub> pins, in the standby mode for reduced power consumption: PD<sub>out</sub> is forced to the high–impedance state, φ<sub>R</sub> and φ<sub>V</sub> are forced high, the A, N, and R counters are inhibited from counting, and the Rx current is shut off. In standby, the state of LD is determined by bit C5. C5 low forces LD low (no change). C5 high forces LD static high. During standby, data is retained in the A, R, and C registers. The condition of REF/OSC circuitry is determined by the control bits in the R register: R13, R14, and R15. However, if REF<sub>out</sub> = static low is selected, the internal feedback resistor is disconnected and the input is inhibited when in standby; in addition, the REF<sub>in</sub> input only presents a capacitive load. NOTE: Standby does not affect the other modes of the REF/OSC circuitry.

When C4 is reset low, the part is taken out of standby in 2 steps. First, the REF<sub>in</sub> (only in one mode) resistor is reconnected, all counters are enabled, and the Rx current is enabled. Any  $f_R$  and  $f_V$  signals are inhibited from toggling the phase/frequency detectors and lock detector. Second, when the first  $f_V$  pulse occurs, the R counter is jam loaded, and the phase/frequency and lock detectors are initialized. Immediately after the jam load, the A, N, and R counters begin counting down together. At this point, the  $f_R$  and  $f_V$  pulses are enabled to the phase and lock detectors. (Patented feature.)

- C3, C2 I2, I1: Controls the PD<sub>out</sub> source/sink current per Tables 2 and 3. With both bits high, the maximum current (as set by Rx per Figure 14) is available. Also, see C1 bit description.

- C1 Port: When the OUTPUT A pin is selected as "Port" via bits A22 and A23, C1 determines the state of OUTPUT A. When C1 is set high, OUTPUT A is forced high; C1 low forces OUTPUT A low. When OUTPUT A is NOT selected as "Port," C1 controls whether the PD<sub>OUt</sub> step size is 10% or 25%. (See Tables 2 and 3.) When low, steps are 10%. When high, steps are 25%. Default is 10% steps when OUTPUT A is selected as "Port." The Port bit is not affected by the standby mode.

- C0 Out B: Determines the state of OUTPUT B. When C0 is set high, OUTPUT B is high-impedance; C0 low forces OUTPUT B low. The Out B bit is not affected by the standby mode. This bit is cleared low at power up.

Figure 15. C Register Access and Format (8 Clock Cycles are Used)

1. A power-on initialize circuit forces the OUTPUT A function to default to Data Out.

The values programmed for the N counter must be greater than or equal to the values programmed for the A counter. This results in a total divide value = N x 64 + A. <u>പ്</u> പ്

At this point, the three new bytes are transferred to the A register. In addition, the 13 LSBs in the first buffer of the R register are transferred to the R register's second buffer. Thus, the R, N, and A counters can be presented new divide ratios at the same time. The first buffer of the R register is not affected. The C register is not affected.

MC145200•MC145201

14

#### NOTES:

- 1. Bits R15 through R13 control the configurable "OSC or 4-stage divider" block (see Block Diagram).

- 2. Bits R12 through R0 control the "13-stage R counter" block (see Block Diagram).

- 3. A power-on initialize circuit forces a default REF<sub>in</sub> to REF<sub>out</sub> ratio of eight.

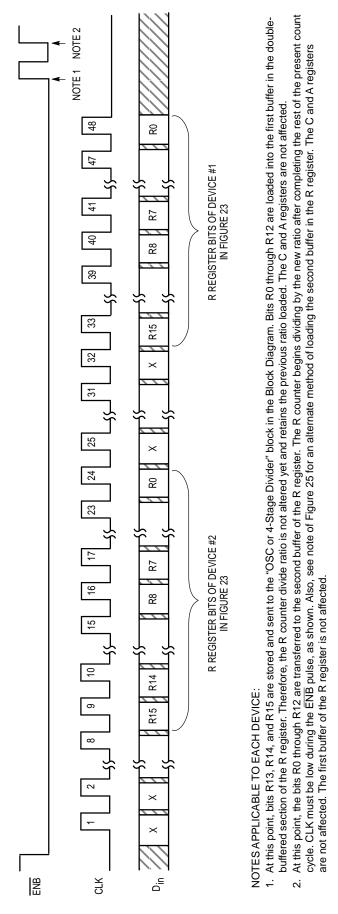

- 4. At this point, bits R13, R14, and R15 are stored and sent to the "OSC or 4–Stage Divider" block in the Block Diagram. Bits R0 through R12 are loaded into the first buffer in the double–buffered section of the R register. Therefore, the R counter divide ratio is not altered yet and retains the previous ratio loaded. The C and A registers are not affected.

- 5. At this point, bits R0 through R12 are transferred to the second buffer of the R register. The R counter begins dividing by the new ratio after completing the rest of the present count cycle. CLK must be low during the ENB pulse, as shown. Also, see note 3 of Figure 16 for an alternate method of loading the second buffer in the R register. The C and A registers are not affected. The first buffer of the R register is not affected.

- 6. Allows direct access to reference input of phase/frequency detectors.

# Figure 17. R Register Access and Format (16 Clock Cycles Are Used)

V<sub>H</sub> = High voltage level

VL = Low voltage level

\*At this point, when both  $f_R$  and  $f_V$  are in phase, the output source and sink circuits are turned on for a short interval. NOTE: The PD<sub>out</sub> either sources or sinks current during out–of–lock conditions. When locked in phase and frequency, the output is high impedance and the voltage at that pin is determined by the low–pass filter capacitor. PD<sub>out</sub>,  $\phi_R$ , and  $\phi_V$  are shown with the polarity bit (POL) = low; see Figure 14 for POL.

#### Figure 18. Phase/Frequency Detectors and Lock Detector Output Waveforms

#### **DESIGN CONSIDERATIONS**

#### **CRYSTAL OSCILLATOR CONSIDERATIONS**

The following options may be considered to provide a reference frequency to Motorola's CMOS frequency synthesizers.

#### Use of a Hybrid Crystal Oscillator

Commercially available temperature–compensated crystal oscillators (TCXOs) or crystal–controlled data clock oscillators provide very stable reference frequencies. An oscillator capable of CMOS logic levels at the output may be direct or dc coupled to REF<sub>in</sub>. If the oscillator does not have CMOS logic levels on the outputs, capacitive or ac coupling to REF<sub>in</sub> may be used (see Figure 8).

For additional information about TCXOs and data clock oscillators, please consult the latest version of the *eem Electronic Engineers Master Catalog*, the *Gold Book*, or similar publications.

#### **Design an Off-Chip Reference**

The user may design an off-chip crystal oscillator using discrete transistors or ICs specifically developed for crystal oscillator applications, such as the MC12061 MECL device. The reference signal from the MECL device is ac coupled to REF<sub>in</sub> (see Figure 8). For large amplitude signals (standard CMOS logic levels), dc coupling may be used.

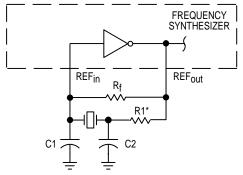

#### Use of the On-Chip Oscillator Circuitry

The on-chip amplifier (a digital inverter) along with an appropriate crystal may be used to provide a reference source frequency. A fundamental mode crystal, parallel resonant at the desired operating frequency, should be connected as shown in Figure 19.

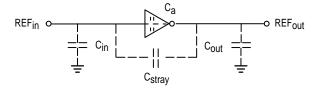

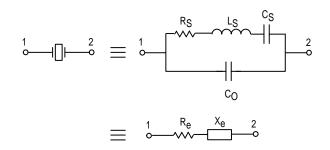

The crystal should be specified for a loading capacitance (C<sub>L</sub>) which does not exceed approximately 20 pF when used at the highest operating frequency of 15 MHz. Assuming R1 = 0  $\Omega$ , the shunt load capacitance (C<sub>L</sub>) presented across the crystal can be estimated to be:

$$C_{L} = \frac{C_{in}C_{out}}{C_{in}+C_{out}} + C_{a} + C_{stray} + \frac{C1 \cdot C2}{C1 + C2}$$

where

$C_{in} = 5 \text{ pF}$  (see Figure 20)  $C_{out} = 6 \text{ pF}$  (see Figure 20)  $C_a = 1 \text{ pF}$  (see Figure 20)

C1 and C2 = external capacitors (see Figure 19) C<sub>stray</sub> = the total equivalent external circuit stray capacitance appearing across the crystal terminals

The oscillator can be "trimmed" on–frequency by making a portion or all of C1 variable. The crystal and associated components must be located as close as possible to the REF<sub>in</sub> and REF<sub>out</sub> pins to minimize distortion, stray capacitance, stray inductance, and startup stabilization time. Circuit stray capacitance can also be handled by adding the appropriate stray value to the values for C<sub>in</sub> and C<sub>out</sub>. For this approach, the term C<sub>stray</sub> becomes 0 in the above expression for C<sub>L</sub>.

Power is dissipated in the effective series resistance of the crystal,  $R_e$ , in Figure 21. The maximum drive level specified by the crystal manufacturer represents the maximum stress that the crystal can withstand without damage or excessive shift in operating frequency. R1 in Figure 19 limits the drive level. The use of R1 is not necessary in most cases.

To verify that the maximum dc supply voltage does not cause the crystal to be overdriven, monitor the output frequency ( $f_R$ ) at OUTPUT A as a function of supply voltage. (REF<sub>out</sub> is not used because loading impacts the oscillator.) The frequency should increase very slightly as the dc supply voltage is increased. An overdriven crystal decreases in frequency or becomes unstable with an increase in supply voltage. The operating supply voltage must be reduced or R1 must be increased in value if the overdriven condition exists. The user should note that the oscillator start–up time is proportional to the value of R1.

Through the process of supplying crystals for use with CMOS inverters, many crystal manufacturers have developed expertise in CMOS oscillator design with crystals. Discussions with such manufacturers can prove very helpful (see Table 4).

#### **RECOMMENDED READING**

Technical Note TN-24, Statek Corp.

Technical Note TN–7, Statek Corp.

E. Hafner, "The Piezoelectric Crystal Unit–Definitions and Method of Measurement", *Proc. IEEE*, Vol. 57, No. 2, Feb. 1969.

D. Kemper, L. Rosine, "Quartz Crystals for Frequency Control", *Electro–Technology*, June 1969.

P. J. Ottowitz, "A Guide to Crystal Selection", *Electronic Design*, May 1966.

D. Babin, "Designing Crystal Oscillators", *Machine Design*, March 7, 1985.

D. Babin, "Guidelines for Crystal Oscillator Design", *Machine Design*, April 25, 1985.

\* May be needed in certain cases. See text.

#### Figure 19. Pierce Crystal Oscillator Circuit

# Figure 20. Parasitic Capacitances of the Amplifier and C<sub>stray</sub>

NOTE: Values are supplied by crystal manufacturer (parallel resonant crystal).

#### Figure 21. Equivalent Crystal Networks

| Table 4. Partial List of Crystal Manufacturers |                                                                   |  |  |  |

|------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| Motoro                                         | la — Internet Address http://motorola.com (Search for resonators) |  |  |  |

|                                                | United States Crystal Corp.                                       |  |  |  |

|                                                | Crystek Crystal                                                   |  |  |  |

|                                                | Statek Corp.                                                      |  |  |  |

|                                                | Fox Electronics                                                   |  |  |  |

Table 4. Partial List of Crystal Manufacturers

NOTE: Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of crystal manufacturers.

NOTE:

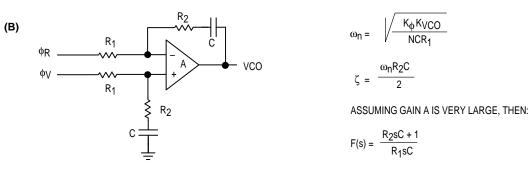

For (A), using K<sub>0</sub> in amps per radian with the filter's impedance transfer function, Z(s), maintains units of volts per radian for the detector/ filter combination. Additional sideband filtering can be accomplished by adding a capacitor C' across R. The corner  $\omega_{\rm C}$  = 1/RC' should be chosen such that  $\omega_n$  is not significantly affected.

NOTE:

For (B), R1 is frequently split into two series resistors; each resistor is equal to R1 divided by 2. A capacitor CC is then placed from the midpoint to ground to further filter the error pulses. The value of C<sub>C</sub> should be such that the corner frequency of this network does not significantly affect ωn.

\* The  $\phi_R$  and  $\phi_V$  outputs are fed to an external combiner/loop filter. The  $\phi_R$  and  $\phi_V$  outputs swing rail-to-rail. Therefore, the user should be careful not to exceed the common mode input range of the op amp used in the combiner/loop filter.

#### **DEFINITIONS:**

N = Total Division Ratio in Feedback Loop

$K_{\phi}$  (Phase Detector Gain) =  $I_{PDout}/2\pi$  amps per radian for  $PD_{out}$  $K_{\phi}$  (Phase Detector Gain) =  $V_{PD}/2\pi$  volts per radian for  $\phi_V$  and  $\phi_R$

$K_{VCO}$  (VCO Transfer Function) =  $\frac{2\pi\Delta f_{VCO}}{\Delta V_{VCO}}$  radians per volt

For a nominal design starting point, the user might consider a damping factor  $\zeta \approx 0.7$  and a natural loop frequency  $\omega_{\Pi} \approx (2\pi f_R/50)$  where f<sub>R</sub> is the frequency at the phase detector input. Larger ω<sub>n</sub> values result in faster loop lock times and, for similar sideband filtering, higher f<sub>R</sub>-related VCO sidebands.

Either loop filter (A) or (B) is frequently followed by additional sideband filtering to further attenuate fR-related VCO sidebands. This additional filtering may be active or passive.

#### **RECOMMENDED READING:**

Gardner, Floyd M., Phaselock Techniques (second edition). New York, Wiley-Interscience, 1979.

Manassewitsch, Vadim, Frequency Synthesizers: Theory and Design (second edition). New York, Wiley-Interscience, 1980.

Blanchard, Alain, Phase-Locked Loops: Application to Coherent Receiver Design. New York, Wiley-Interscience, 1976.

Egan, William F., Frequency Synthesis by Phase Lock. New York, Wiley-Interscience, 1981.

Rohde, Ulrich L., Digital PLL Frequency Synthesizers Theory and Design. Englewood Cliffs, NJ, Prentice-Hall, 1983.

Berlin, Howard M., Design of Phase-Locked Loop Circuits, with Experiments. Indianapolis, Howard W. Sams and Co., 1978.

Kinley, Harold, The PLL Synthesizer Cookbook. Blue Ridge Summit, PA, Tab Books, 1980.

Seidman, Arthur H., Integrated Circuits Applications Handbook, Chapter 17, pp. 538–586. New York, John Wiley & Sons.

Fadrhons, Jan, "Design and Analyze PLLs on a Programmable Calculator," EDN. March 5, 1980.

AN535, Phase–Locked Loop Design Fundamentals, Motorola Semiconductor Products, Inc., 1970.

AR254, Phase-Locked Loop Design Articles, Motorola Semiconductor Products, Inc., Reprinted with permission from Electronic Design, 1987

AN1253/D, An Improved PLL Design Method Without ωn and ζ, Motorola Semiconductor Products, Inc., 1995.

#### NOTES:

- When used, the φ<sub>R</sub> and φ<sub>V</sub> outputs are fed to an external combiner/loop filter. See the Phase– Locked Loop – Low–Pass Filter Design page for additional information.

- 2. Transistor Q1 is required only if the standby feature is needed. Q1 permits the bipolar section of the device to be shut down via use of the general–purpose digital pin, OUTPUT B. If the standby feature is not needed, tie Pin 12 directly to the power supply.

- 3. For optimum performance, bypass the V<sub>CC</sub>, V<sub>DD</sub>, and V<sub>PD</sub> pins to GND with low–inductance capacitors.

- 4. The R counter is programmed for a divide value =  $REF_{in}/f_R$ . Typically,  $f_R$  is the tuning resolution required for the VCO. Also, the VCO frequency divided by  $f_R = N_T = N \times 64 + A$ ; this determines the values (N, A) that must be programmed into the N and A counters, respectively.

#### Figure 22. Example Application

NOTE: See related Figures 24 through 26; these bit streams apply to the MC145190, MC145191, MC145200, and MC145201.

#### Figure 23. Cascading Two Devices

MOTOROLA

Figure 26. Accessing the R Registers of Two Cascaded Devices

MOTOROLA

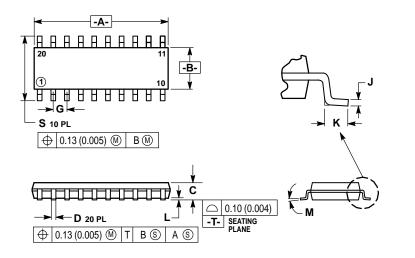

### PACKAGE DIMENSIONS

#### **F SUFFIX** SOG (SMALL OUTLINE GULL-WING) PACKAGE CASE 751J-02

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER. DIMENSIONS A AND B DO NOT INCLUDE 2 3.

- MOLD PROTRUSION. 4 MAXIMUM MOLD PROTRUSION 0.15 (0.006)

- PER SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 12.55       | 12.80 | 0.494     | 0.504 |

| В   | 5.10        | 5.40  | 0.201     | 0.213 |

| С   | -           | 2.00  | -         | 0.079 |

| D   | 0.35        | 0.45  | 0.014     | 0.018 |

| G   | 1.27 BSC    |       | 0.050 BSC |       |

| J   | 0.18        | 0.23  | 0.007     | 0.009 |

| Κ   | 0.55        | 0.85  | 0.022     | 0.033 |

| L   | 0.05        | 0.20  | 0.002     | 0.008 |

| М   | 0°          | 7°    | 0°        | 7°    |

| S   | 7.40        | 8.20  | 0.291     | 0.323 |

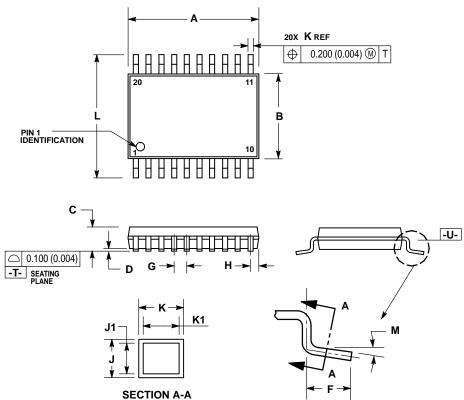

DT SUFFIX **TSSOP (THIN SHRUNK SMALL OUTLINE PACKAGE)** CASE 948D-03

NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER. 1.

- 2 CONTROLLING DIMENSION: MILLIMETER. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. SHALL NOT EXCEED 0.25 (0.010) PER SIDE. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.08 (0.03) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM 3.

- 4

- 5. EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- 6.

- DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM PLANE -U-7.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   |             | 6.60  |           | 0.260 |

| В   | 4.30        | 4.50  | 0.169     | 0.177 |

| С   |             | 1.20  |           | 0.047 |

| D   | 0.05        | 0.25  | 0.002     | 0.010 |

| F   | 0.45        | 0.55  | 0.018     | 0.022 |

| G   | 0.65 BSC    |       | 0.026 BSC |       |

| Н   | 0.275       | 0.375 | 0.011     | 0.015 |

| J   | 0.09        | 0.24  | 0.004     | 0.009 |

| J1  | 0.09        | 0.18  | 0.004     | 0.007 |

| K   | 0.16        | 0.32  | 0.006     | 0.013 |

| K1  | 0.16        | 0.26  | 0.006     | 0.010 |

| L   | 6.30        | 6.50  | 0.248     | 0.256 |

| Μ   | 0°          | 10°   | 0°        | 10°   |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(Motorola** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

Mfax™: RMFAX0@email.sps.mot.com

- TOUCHTONE 1–602–244–6609

Motorola Fax Back System

- US & Canada ONLY 1–800–774–1848

- http://sps.motorola.com/mfax/

$\Diamond$

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141, 4–32–1 Nishi–Gotanda, Shagawa–ku, Tokyo, Japan. 03–5487–8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

CUSTOMER FOCUS CENTER: 1-800-521-6274