# ML145145 4-Bit Data Bus Input PLL Frequency Synthesizer

#### INTERFACES WITH SINGLE-MODULUS PRESCALERS

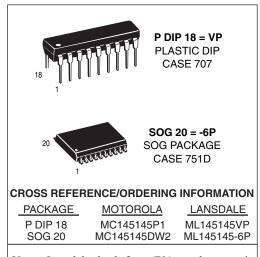

Legacy Device: Motorola MC145145-2

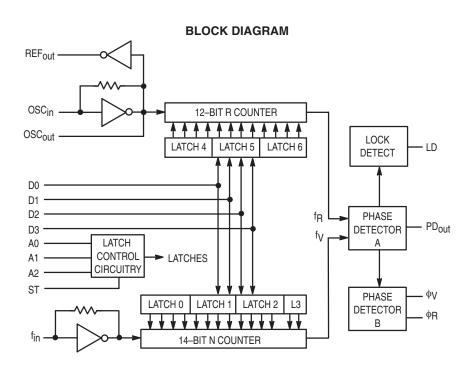

The ML145145 is programmed by a 4-bit input, with strobe and address lines. The device features consist of a reference oscillator, 12-bit programmable reference divider, digital phase detector, 14-bit programmable divide-by-N counter, and the necessary latch circuitry for accepting the 4-bit input data.

- Operating Temperature Range: TA 40 to 85°C

- Low Power Consumption Through the Use of CMOS Technology

- 3.0 to 9.0 V Supply Range

- Single Modulus 4–Bit Data Bus Programming

- $\div$ N Range = 3 to 16,383,  $\div$ R Range = 3 to 4,095

- "Linearized" Digital Phase Detector Enhances Transfer Function Linearity

- Two Error Signal Options: Single–Ended (Three–State) Double–Ended

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol                               | Parameter                                             | Value                        | Unit |

|--------------------------------------|-------------------------------------------------------|------------------------------|------|

| V <sub>DD</sub>                      | DC Supply Voltage                                     | -0.5 to +10                  | ٧    |

| Vin, Vout                            | Input or Output Voltage (DC or Transient)             | -0.5 to V <sub>DD</sub> +0.5 | V    |

| l <sub>in</sub> , l <sub>out</sub>   | Input or Output Current (DC or Transient),<br>per Pin | ±10                          | mA   |

| IDD, ISS                             | Supply Current, VDD or VSS Pins                       | ±30                          | mA   |

| PD                                   | Power Dissipation, per Package†                       | 500                          | mW   |

| T <sub>stg</sub> Storage Temperature |                                                       | -65 to +150                  | °C   |

| TL                                   | Lead Temperature, 1 mm from Case for<br>10 Seconds    | 260                          | °C   |

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Descriptions section.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to these high–impedance circuits. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \le (V_{in} \text{ or } V_{out}) \le V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD), except for inputs with pull-up devices. Unused outputs must be left open.

#### ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|                 |                                                                                   |                                                                                                            | VDD               | -40°C             |                     | 25°C              |                     | 85°C              |                      |        |

|-----------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------|-------------------|---------------------|-------------------|---------------------|-------------------|----------------------|--------|

| Symbol          | Parameter                                                                         | Test Conditions                                                                                            | v                 | Min               | Max                 | Min               | Max                 | Min               | Max                  | Unit   |

| VDD             | Power Supply Voltage Range                                                        |                                                                                                            | 1                 | 3.0               | 9.0                 | 3.0               | 9.0                 | 3.0               | 9.0                  | ٧      |

| I <sub>SS</sub> | Dynamic Supply Current                                                            | f <sub>in</sub> = OSC <sub>in</sub> = 10 MHz,<br>1 V p-p ac coupled sine wave<br>R = 128, A = 32, N = 128  | 3.0<br>5.0<br>9.0 | =                 | 3.5<br>10<br>30     | =                 | 3.0<br>7.5<br>24    | _                 | 3.0<br>7.5<br>24     | mA     |

| Iss             | Quiescent Supply Current                                                          | V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub><br>I <sub>out</sub> = 0 μA                            | 3.0<br>5.0<br>9.0 | =                 | 800<br>1200<br>1600 | _                 | 800<br>1200<br>1600 | =                 | 1600<br>2400<br>3200 | μА     |

| Vin             | Input Voltage — fin, OSCin                                                        | Input ac coupled sine wave                                                                                 | -                 | 500               | -                   | 500               | _                   | 500               | -                    | mV p−p |

| VIL             | Low-Level Input Voltage —<br>fin. OSCin                                           | V <sub>out</sub> ≥2.1 V Input<br>V <sub>out</sub> ≥3.5 V dc coupled<br>V <sub>out</sub> ≥6.3 V square wave | 3.0<br>5.0<br>9.0 | =                 | 0<br>0<br>0         | =                 | 0<br>0<br>0         | =                 | 0<br>0<br>0          | ٧      |

| VIH             | High-Level Input Voltage — fin. OSCin                                             | V <sub>out</sub> ≤0.9 V Input<br>V <sub>out</sub> ≤1.5 V dc coupled<br>V <sub>out</sub> ≤2.7 V square wave | 3.0<br>5.0<br>9.0 | 3.0<br>5.0<br>9.0 | _                   | 3.0<br>5.0<br>9.0 |                     | 3.0<br>5.0<br>9.0 | =                    | ٧      |

| V <sub>IL</sub> | Low-Level Input Voltage —<br>except fin, OSCin                                    |                                                                                                            | 3.0<br>5.0<br>9.0 | =                 | 0.9<br>1.5<br>2.7   | =                 | 0.9<br>1.5<br>2.7   | =                 | 0.9<br>1.5<br>2.7    | V      |

| VIH             | High-Level Input Voltage — except fin, OSCin                                      |                                                                                                            | 3.0<br>5.0<br>9.0 | 2.1<br>3.5<br>6.3 | _                   | 2.1<br>3.5<br>6.3 | =                   | 2.1<br>3.5<br>6.3 | =                    | V      |

| lin             | Input Current (fin, OSCin)                                                        | Vin = VDD or VSS                                                                                           | 9.0               | ± 2.0             | ±50                 | ± 2.0             | ± 25                | ± 2.0             | ± 22                 | μА     |

| ΙτL             | Input Leakage Current<br>(all inputs except f <sub>in</sub> , OSC <sub>in</sub> ) | V <sub>in</sub> = V <sub>SS</sub>                                                                          | 9.0               | _                 | -0.3                | -                 | - 0.1               | -                 | -1.0                 | μА     |

| ľН              | Input Leakage Current<br>(all inputs except f <sub>in</sub> , OSC <sub>in</sub> ) | V <sub>in</sub> = V <sub>DD</sub>                                                                          | 9.0               | -                 | 0.3                 |                   | 0.1                 | -                 | 1.0                  | μА     |

| Cin             | Input Capacitance                                                                 |                                                                                                            | -                 | _                 | 10                  | -                 | 10                  | _                 | 10                   | pF     |

| VOL             | Low-Level Output Voltage<br>OSCout                                                | I <sub>out</sub> = 0 μA<br>Vin = V <sub>DD</sub>                                                           | 3.0<br>5.0<br>9.0 | _                 | 0.9<br>1.5<br>2.7   | =                 | 0.9<br>1.5<br>2.7   | =                 | 0.9<br>1.5<br>2.7    | V      |

| Vон             | High-Level Output Voltage —<br>OSCout                                             | I <sub>out</sub> = 0 μA<br>V <sub>in</sub> = V <sub>SS</sub>                                               | 3.0<br>5.0<br>9.0 | 2.1<br>3.5<br>6.3 | =                   | 2.1<br>3.5<br>6.3 | =                   | 2.1<br>3.5<br>6.3 | =                    | ٧      |

(continued)

<sup>†</sup>Power Dissipation Temperature Derating: Plastic DIP: -12 mW/°C from 65 to 85°C SOG Package: -7.0 mW/°C from 65 to 85°C

### ELECTRICAL CHARACTERISTICS (continued)

|        |                                                |                                                                                  | VDD               | -40°C                  |                      | 25°C                   |                      | 85°C                   |                      |      |

|--------|------------------------------------------------|----------------------------------------------------------------------------------|-------------------|------------------------|----------------------|------------------------|----------------------|------------------------|----------------------|------|

| Symbol | Parameter                                      | Test Conditions                                                                  | V                 | Min                    | Max                  | Min                    | Max                  | Min                    | Max                  | Unit |

| VOL    | Low-Level Output Voltage —<br>Other Outputs    | l <sub>out</sub> = 0 μA                                                          | 3.0<br>5.0<br>9.0 | _                      | 0.05<br>0.05<br>0.05 | =                      | 0.05<br>0.05<br>0.05 | _                      | 0.05<br>0.05<br>0.05 | ٧    |

| VOH    | High-Level Output Voltage —<br>Other Outputs   | I <sub>out</sub> ≈ 0 μA                                                          | 3.0<br>5.0<br>9.0 | 2.95<br>4.95<br>8.95   | _                    | 2.95<br>4.95<br>8.95   | _                    | 2.95<br>4.95<br>8.95   |                      | V    |

| IOL    | Low-Level Sinking Current —<br>Lock Detect     | V <sub>out</sub> = 0.3 V<br>V <sub>out</sub> = 0.4 V<br>V <sub>out</sub> = 0.5 V | 3.0<br>5.0<br>9.0 | 0.25<br>0.64<br>1.3    | =                    | 0.2<br>0.51<br>1.0     | =                    | 0.15<br>0.36<br>0.7    |                      | mA   |

| IOH    | High-Level Sourcing<br>Current — Lock Detect   | V <sub>Out</sub> = 2.7 V<br>V <sub>Out</sub> = 4.6 V<br>V <sub>Out</sub> = 8.5 V | 3.0<br>5.0<br>9.0 | -0.25<br>-0.64<br>-1.3 | _                    | -0.2<br>-0.51<br>-1.0  | _                    | -0.15<br>-0.36<br>-0.7 |                      | mA   |

| IOL    | Low-Level Sinking Current —<br>Other Outputs   | V <sub>Out</sub> = 0.3 V<br>V <sub>Out</sub> = 0.4 V<br>V <sub>Out</sub> = 0.5 V | 3.0<br>5.0<br>9.0 | 0.44<br>0.64<br>1.3    | _<br>_<br>_          | 0.35<br>0.51<br>1.0    | _                    | 0.22<br>0.36<br>0.7    | _                    | mA   |

| IOH    | High-Level Sourcing<br>Current — Other Outputs | V <sub>Out</sub> = 2.7 V<br>V <sub>Out</sub> = 4.6 V<br>V <sub>Out</sub> = 8.5 V | 3.0<br>5.0<br>9.0 | -0.44<br>-0.64<br>-1.3 | <u>-</u>             | -0.35<br>-0.51<br>-1.0 | =                    | -0.22<br>-0.36<br>-0.7 |                      | mA   |

| loz    | Output Leakage Current—<br>PD <sub>out</sub>   | V <sub>out</sub> = V <sub>DD</sub> or V <sub>SS</sub><br>Output in Off State     | 9.0               | _                      | ± 0.3                | _                      | ± 0.1                | _                      | ± 1.0                | μА   |

| Cout   | Output Capacitance - PDout                     | PD <sub>out</sub> — Three-State                                                  | -                 | _                      | 10                   | _                      | 10                   |                        | 10                   | pF   |

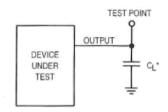

# AC ELECTRICAL CHARACTERISTICS (C<sub>L</sub> = 50 pF, input $t_f = t_f = 10 \text{ ns}$ )

| Symbol          | Parameter                                                                                                     | Figure<br>No. | V <sub>DD</sub>   | Guaranteed Limit<br>25°C           | Guaranteed Limit<br>-40 to 85°C    | Unit |

|-----------------|---------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------------------------|------------------------------------|------|

| t <sub>w</sub>  | Output Pulse Width, φ <sub>R</sub> , φ <sub>V</sub> , and LD with f <sub>R</sub> in Phase with f <sub>V</sub> | 1, 5          | 3.0<br>5.0<br>9.0 | 25 to 200<br>20 to 100<br>10 to 70 | 25 to 260<br>20 to 125<br>10 to 80 | ns   |

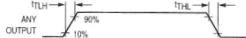

| tTLH- tTHL      | Maximum Output Transition Time, LD                                                                            | 2, 5          | 3.0<br>5.0<br>9.0 | 180<br>90<br>70                    | 200<br>120<br>90                   | ns   |

| tTLH, tTHL      | Maximum Output Transition Time, Other Outputs                                                                 | 2, 5          | 3.0<br>5.0<br>9.0 | 160<br>80<br>60                    | 175<br>100<br>65                   | ns   |

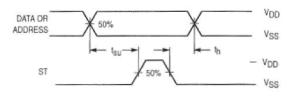

| t <sub>su</sub> | Minimum Setup Time, Data to ST                                                                                | 3             | 3.0<br>5.0<br>9.0 | 10<br>10<br>10                     | =                                  | ns   |

| t <sub>su</sub> | Minimum Setup Time, Address to ST                                                                             | 3             | 3.0<br>5.0<br>9.0 | 25<br>20<br>15                     |                                    | ns   |

| th              | Minimum Hold Time, Address to ST                                                                              | 3             | 3.0<br>5.0<br>9.0 | 10<br>10<br>10                     |                                    | ns   |

| th              | Minimum Hold Time, Data to ST                                                                                 | 3             | 3.0<br>5.0<br>9.0 | 25<br>20<br>15                     |                                    | ns   |

| t <sub>w</sub>  | Minimum Input Pulse Width, ST                                                                                 | 4             | 3.0<br>5.0<br>9.0 | 40<br>30<br>20                     |                                    | ns   |

# SWITCHING WAVEFORMS

\* f<sub>R</sub> in phase with f<sub>V</sub>

Figure 1.

Figure 2.

Figure 4.

\* Includes all probe and fixture capacitance.

Figure 5. Test Circuit

FREQUENCY CHARACTERISTICS (Voltages Referenced to VSS, CL = 50 pF, Input t<sub>f</sub> = t<sub>f</sub> = 10 ns unless otherwise indicated)

|        |                              | Test Conditions                                      | V <sub>DD</sub> -40 |     | 0°C | 25°C |     | 85°C |     |      |

|--------|------------------------------|------------------------------------------------------|---------------------|-----|-----|------|-----|------|-----|------|

| Symbol | Parameter                    |                                                      | V                   | Min | Max | Min  | Max | Min  | Max | Unit |

| fi     | Input Frequency (fin. OSCin) | R≥8, A≥0, N≥8                                        | 3.0                 |     | 6.0 | 1-   | 6.0 | _    | 6.0 | MHz  |

|        |                              | Vin = 500 mV p-p ac coupled                          | 5.0                 | -   | 15  | _    | 15  | _    | 15  | l    |

|        |                              | sine wave                                            | 9.0                 | _   | 15  | -    | 15  | -    | 15  |      |

|        |                              | R≥8, A≥0, N≥8                                        | 3.0                 | _   | 12  | _    | 12  | _    | 7.0 | MHz  |

|        |                              | V <sub>in</sub> = 1.0 V p-p ac coupled               | 5.0                 | -   | 22  | _    | 20  | -    | 20  |      |

|        |                              | sine wave                                            | 9.0                 |     | 25  | -    | 22  | -    | 22  |      |

|        |                              | R≥8, A≥0, N≥8                                        | 3.0                 | -   | 13  | -    | 12  | -    | 8.0 | MHz  |

|        |                              | V <sub>in</sub> ≈ V <sub>DD</sub> to V <sub>SS</sub> | 5.0                 | _   | 25  | -    | 22  | _    | 22  |      |

|        |                              | dc coupled square wave                               | 9.0                 |     | 25  | -    | 25  | _    | 25  |      |

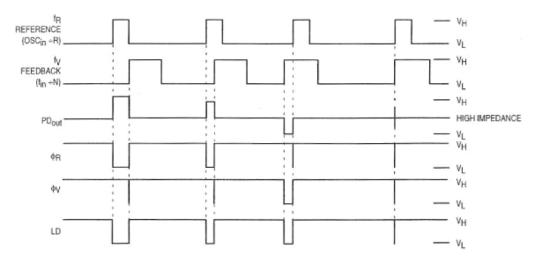

V<sub>H</sub> = High voltage level.

V<sub>L</sub> = Low voltage level.

At this point, when both f<sub>R</sub> and f<sub>V</sub> are in phase, the output is forced to near mid supply.

NOTE: The PD<sub>out</sub> generates error pulses during out-of-lock conditions. When locked in phase and frequency, the output is high impedance and the voltage at that pin is determined by the low-pass filter capacitor.

Figure 6. Phase/Frequency Detectors and Lock Detector Output Waveforms

#### PIN DESCRIPTIONS

#### **INPUT PINS**

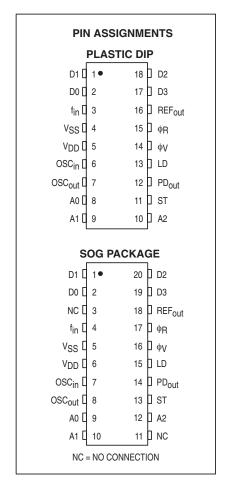

### D0 - D3

# Data Inputs (PDIP - Pins 2, 1, 18, 17; SOG - Pins 2, 1, 20, 19)

Information at these inputs is transferred to the internal latches when the ST input is in the high state. D3 is most significant bit.

# fin

# Frequency Input (PDIP – Pin 3, SOG – Pin 4)

Input to ÷N portion of synthesizer. f<sub>in</sub> is typically derived from the loop VCO and is ac couples. For larger amplitude signals (standard CMOS – logic levels) dc coupling may be used.

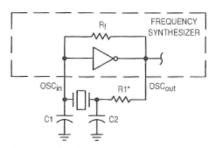

#### OSCin/OSCout

# Reference Oscillator Input/Output (PDIP – Pins 6, 7; SOG – Pins 7, 8)

These pins form an on–chip reference oscillator when connected to terminals of an external parallel resonant crystal. Frequency setting capacitors of appropriate value must be connected from  $OSC_{in}$  to ground and  $OSC_{out}$  to ground.  $OSC_{in}$  may also serve as input for an externally–generated reference signal. This signal is typically AC coupled to  $OSC_{in}$  but for larger amplitude signals (standard CMOS–logic levels) DC coupling may also be used. In the external refrence mode, no connection is required to  $OSC_{out}$ .

#### A0 - A2

# Address Inputs (PDIP – Pins 8, 9, 10; SOG – Pins 9, 10, 12)

A0, A1 and A2 are used to define which latch receives the information on the data input lines. The addresses refer to the following latches:

| A2 | A1 | A0 | Selected | Function       | D0 | D1 | D2 | D3 |

|----|----|----|----------|----------------|----|----|----|----|

| 0  | 0  | 0  | Latch 0  | + N Bits       | 0  | 1  | 2  | 3  |

| 0  | 0  | 1  | Latch 1  | ÷ N Bits       | 4  | 5  | 6  | 7  |

| 0  | 1  | 0  | Latch 2  | ÷ N Bits       | 8  | 9  | 10 | 11 |

| 0  | 1  | 1  | Latch 3  | ÷ N Bits       | 12 | 13 | -  | _  |

| 1  | 0  | 0  | Latch 4  | Reference Bits | 0  | 1  | 2  | 3  |

| 1  | 0  | 1  | Latch 5  | Reference Bits | 4  | 5  | 6  | 7  |

| 1  | 1  | 0  | Latch 6  | Reference Bits | 8  | 9  | 10 | 11 |

| 1  | 1  | 1  | _        | _              | -  | -  | -  | _  |

# ST

# Strobe Transfer (PDIP - Pin 11, SOG - Pin 13)

The rising edge of strobe transfers data into the addressed

latch, the falling edge of strobe latches data into the latch. This pin should normally be held low to avoid loading latches with invalid data.

#### **OUTPUT PINS**

#### **PDout**

# Single-Ended Phase Detector output (PDIP - Pin 12, SOG - Pin 14)

Three-state output of phase detector for use as loop-error signal.

Frequency  $f_V > f_R$  or  $f_V$  Leading: Negative Pulses Frequency  $f_V < f_R$  or  $f_V$  Lagging: Positive Pulses

Frequency  $f_V = f_R$  and Phase Coincidence: High-Impedance State

#### LD

## Lock Detector Signal (PDIP – Pin 13, SOG – Pin 15)

High level when loop is locked (fR, fV of same phase and frequency). Pulses low when loop is out of lock.  $\phi V$ ,  $\phi R$

## Phase Detect or Outputs (PDIP – Pin 12, SOG – Pin 14)

These phase detector outputs can be combined externally for a loop–error signal. A single–ended output is also available for this purpose (see PD<sub>out</sub>).

If frequency  $f_V$  is greater than  $f_R$  or if the phase of  $f_V$  is leading, then error information is provided by  $\phi V$  pulsing low.  $\phi R$  remains essentially high.

If the frequency of fV - fR and both are in phase, then both  $\phi V$  and  $\phi R$  remain high except for a small minimum time period when both pulse low in phase.

# **REFout**

#### Buffered Reference Output (DIP – Pin 16, SOG – Pin 18)

Buffered output of on-chip reference oscillator or externally provided reference-input signal.

#### POWER SUPPLY PINS

VSS

**Ground (PDIP - Pin 4, SOG - Pin 5)**

Circuit Ground

#### **VDD**

### Positive Power Supply (PDIP - Pin 5, SOG - Pin 6)

The positive supply voltage may range from 3.0 to 9.0 V with respect to VSS.

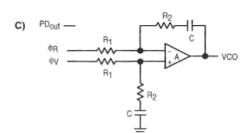

#### DESIGN CONSIDERATIONS

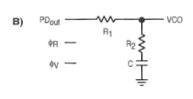

#### PHASE-LOCKED LOOP -- LOW-PASS FILTER DESIGN

$$\omega_{n} = \sqrt{\frac{K_{\Phi}K_{VCO}}{NR_{1}C}}$$

$$\zeta = \frac{N\omega_{n}}{2K_{\Phi}K_{VCO}}$$

$$\omega_{\Pi} = \sqrt{\frac{K_{\Phi}K_{VCO}}{NC(R_1 + R_2)}}$$

$$\zeta = 0.5 \omega_{\Pi} \left(R_2C + \frac{N}{K_{\Phi}K_{VCO}}\right)$$

$$F(s) = \frac{R_2sC + 1}{R_2SC + 1}$$

$$\begin{split} &\omega_{\Pi} = -\sqrt{\frac{K_{\Phi} K_{VCO}}{NCR_{1}}}\\ &\zeta = -\frac{\omega_{\Pi} R_{2}C}{2}\\ &\text{ASSUMING GAIN A IS VERY LARGE, THEN:} \end{split}$$

$$F(s) = -\frac{R_2sC + 1}{R_1sC}$$

NOTE: Sometimes R<sub>1</sub> is split into two series resistors, each R<sub>1</sub> ÷ 2. A capacitor C<sub>C</sub> is then placed from the midpoint to ground to further filter  $\phi_V$  and  $\phi_R$ . The value of  $C_C$  should be such that the corner frequency of this network does not significantly affect  $\omega_R$ .

DEFINITIONS:

N=Total Division Ratio in feedback loop

$K_{\phi}$  (Phase Detector Gain) =  $V_{DD}/4\pi$  for  $PD_{Out}$   $K_{\phi}$  (Phase Detector Gain) =  $V_{DD}/2\pi$  for  $\phi_V$  and  $\phi_R$

$$K_{VCO} (VCO Gain) = \frac{2\pi \Delta f_{VCO}}{\Delta V_{VCO}}$$

for a typical design  $w_n$  (Natural Frequency)  $\approx \frac{2\pi fr}{10}$ (at phase detector input).

Damping Factor:  $\zeta \equiv 1$

#### CRYSTAL OSCILLATOR CONSIDERATIONS

The following options may be considered to provide a reference frequency to Motorola's CMOS frequency synthesizers.

#### Use of a Hybrid Crystal Oscillator

Commercially available temperature—compensated crystal oscillators (TCXOs) or crystal—controlled data clock oscillators provide very stable reference frequencies. An oscillator capable of sinking and sourcing 50  $\square A$  at CMOS logic levels may be direct or DC coupled to OSC $_{in}.$  In general, the highest frequency capability is obtained utilizing a direct—coupled square wave having a rail—to—rail (VDD to VSS) voltage swing. If the oscillator does not have CMOS logic levels on the outputs, capacitive or AC coupling to OSC $_{in}$  may be used. OSC $_{out}$ , and unbuffered output, should be left floating.

For additional information about TCXOs and data clock oscillators, please consult the latest version of the *eem Electronic Engineers Master Catalog*, the *Gold Book*, or similar publications.

### Design an Off-Chip Reference

The user may design an off–chip crystal oscillator using ICs specifically developed for crystal oscillator applications, such as the ML12061 MECL device. The reference signal from the MECL device is ac coupled to OSC<sub>in</sub>. For large amplitude signals (standard CMOS logic levels), DC coupling is used. OSC<sub>out</sub>, an unbuffered output, should be left floating. In general, the highest frequency capability is obtained with a direct–coupled square wave having rail–to–rail voltage swing.

# Use of the On-Chip Oscillator Circuitry

The on—chip amplifier (a digital inverter) along with an appropriate crystal may be used to provide a reference source frequency. A fundamental mode crystal, parallel resonant at the desired operating frequency, should be connected as shown in Figure 7.

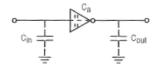

For  $V_{DD} = 5.0$  V, the crystal should be specified for a loading capacitanc.  $C_L$ , which does not exceed 32 pf for frequencies to approximately 8.0 to 15 MHz and 10 pF for higher frequencies. These are guidelines that provide a reasonable compromise between IC capacitance, drive capability, swamping c-variations in stray and IC input/output capacitance, and realistic  $C_L$  values. The shunt load capacitance.  $C_L$ , presented across the crystal can be estimated to be:

$$C_{L} = \frac{C_{in}C_{out}}{C_{in} + C_{out}} + C_{a} + C_{0} + \frac{C1 \cdot C2}{C1 + C2}$$

where

Cin = 5.0 pf (see Figure 8)

Cout = 6.0 pf (see Figure 8)

Ca = 1.0 pf (see Figure 8)

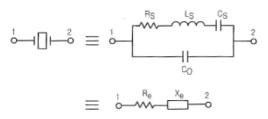

CO = the crystal's holder capacitance (see Figure 9)

C1 and C2 = external capacitors (see Figure 7)

The oscillator can be "trimmed" on-frequency by making a

portion of all of C1 variable. The crystal and associated components must be located as close as possible to the  $OSC_{in}$  and  $OSC_{out}$  pins to minimize distortion, stray capacitance, stray inductance and startup stablilization time. In some cases, stray capacitance should be added to the value for  $C_{in}$  and  $C_{out}$ .

Power is dissipated in the effective series resistance of the crystal  $R_e$ , in Figure 9. The drive level specified by the crystal manufacturer is the maximum stress that a crystal can withstand without damage or excessive shift in frequency. R1 in Figure 7 limits the drive level. The use of R1 may not be necessary in some cases (i.e.,  $R1 = 0~\Omega$ )

To verify that the maximum dc supply voltage does not overdrive the crystal, monitor the output frequency as a function of voltage at OSC<sub>out</sub>. (Care should be taken to minimize loading.) The frequency should increase very slightly as the dc supply voltage is increased. An overdriven crystal will decrease in frequency or become unstable with an increase in supply voltage. The operating supply voltage must be reduced or R1 must be increased in value if the overdriven condition exists. The user should note that the oscillator start—up time is proportional to the value of R1.

Through the process of supplying crystals for use with CMOS inverters, many crystal manufactureres have developed expertise in CMOS oscillator design with crystals. Discussions with such manufacturers can prove very helpful (see Table 1).

\* May be deleted in certain cases. See text.

Figure 7. Pierce Crystal Oscillator Circuit

Figure 8. Parasitic Capacitances of the Amplifier

NOTE: Values are supplied by crystal manufacturer (parallel resonant crystal).

Figure 9. Equivalent Crystal Networks

Table 1. Partial List of Crystal Manufacturers

| Name                        | Address                               | Phone          |  |  |

|-----------------------------|---------------------------------------|----------------|--|--|

| United States Crystal Corp. | 3605 McCart Ave., Ft. Worth, TX 76110 | (817) 921-3013 |  |  |

| Crystek Crystal             | 2351 Crystal Dr., Ft. Myers, FL 33907 | (813) 936-2109 |  |  |

| Statek Corp.                | 512 N. Main St., Orange, CA 92668     | (714) 639-7810 |  |  |

NOTE: Lansdale cannot recommend one supplier over another and in no way suggests that this is a complete listing of crystal manufacturers.

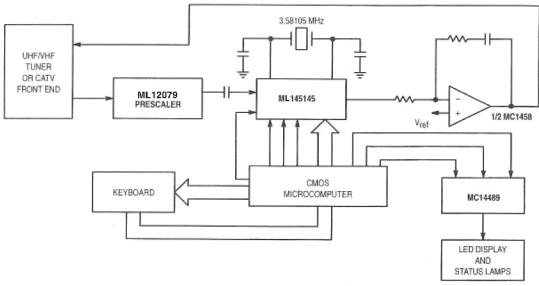

Figure 10. TV/CATV Tuning System

#### RECOMMENDED READING

Technical Note TN-24, Stated Corp. Technical Note TN-\7, Stated Corp.

E. Hafner, "The Piezoelectric Crystal Unit – Definitions and Method of Measurement", *Proc IEEE*, Vol. 57, No. 2 Feb.,

D. Kemper, L. Rosine, "Quartz Crystals for Frequency Control", *Electro–Technology*, June, 1969.

P.J. Ottowitz, "A Guide to Crystal Selection", *Electronic Design*, May, 1966.

### LEGACY APPLICATIONS

The features of the ML145145 permit bus operation with a dedicated wire needed only for the strobe input. In a micro-

processor–controlled system this strobe input is accessed when the PLL is addressed. The remaining data and address inputs will directly interface to the microprocessor's data and address buses.

The  $\div$  R programability is used to advantage in Figure 10. Here, the nominal  $\div$  R value is 3667, but by programming small changes in this value, fine tuning is accomplised. Better tuning resolution is achievable with this method than by changing the  $\div$  N due to the use of the large fixed prescaling value of  $\div$  256 provided by the ML12079.

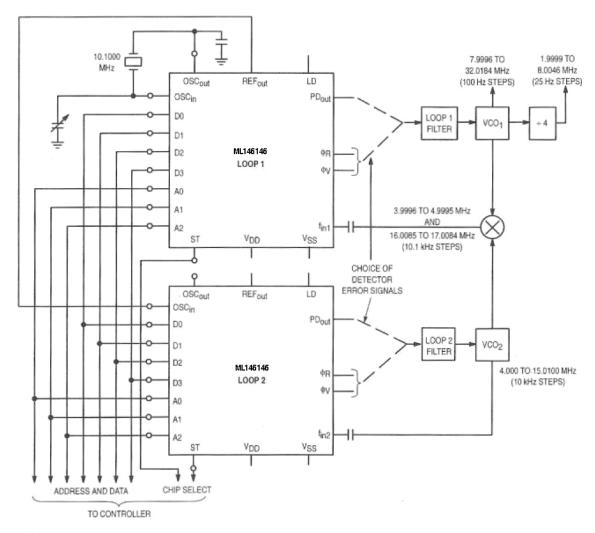

The two-loop synthesizer, in Figure 11, takes advantage of these features to control the phase-locked loop with a minumum of dedicated lines while preserving optimal loop performance. Both 25 Hz and 100 Hz steps are provided while the relatively large reference frequencies of 10 Khz or 10.1 kHz are maintained.

- 1. Table 2 provides program sequence for the + N1 (Loop 1) and + N2 (Loop 2) Counters.

- 2. + R1 = 1000, fR1 = 10.1 kHz, + R2 = 1010, fR2 = 10 kHz.

- 3.  $f_{VCO1} = N1(f_{R1}) + N2(f_{R2}) = N1(f_{R2} + \Delta f) + N2(f_{R2})$  where  $\Delta f = 100$  Hz. 4. Other  $f_{R1}$  and  $f_{R2}$  values may be used with appropriate + N1 and + N2 changes.

Figure 11. Two-Loop Synthesizer Provides 25 and 100 Hz Frequency Steps While Maintaining High Detector Comparison Frequencies of 10 and 10.1 kHz

+ N2 fvCO2 (MHz) + N1 fin1 (MHz) fvCO1 (MHz) 4.0000 7.9996 3.9996 400 7.9997 399 4.0097 3.9900 . 4.9995 3.0100 8.0095 495 301 4.0100 8.0096 401 4.0000 8.0097 "A" "B" 400 ¥ 8.0195 ¥ 3.0200 303 402 4.0200 8.0196 401 "B" 4.0100 8.0197 ¥ 8.0295 3.0300 303 Increasing In 100 Hz Steps "B" "A" 19.9995 15.0000 1500 1600 16.0000 19.9996 1599 19,9997 "B" 15.9900 15.0100 20.0095 1501 16.0085 20.0085 1585 1586 16.0186 20.0086 "E" ∳ 1684 v 20.0184 17.0084 20.0185 20.0186 "C" "D" 20.0284 Increasing In 100 Hz Steps 32.0084 32.0085 "E" 32.0086 32.0184

Table 2. Programming Sequence for Two-Loop Synthesizer of Figure 11

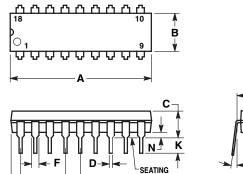

#### **OUTLINE DIMENSIONS**

**P DIP 18 = VP** (ML145145VP) CASE 707-02

#### NOTES

- POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25 (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO

- SEATING PLANE AND EACH OTHER.

DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL

- 3. DIMENSION B DOES NOT INCLUDE MOLD

|     | MILLIM   | IETERS | INC       | HES   |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 22.22    | 23.24  | 0.875     | 0.915 |

| В   | 6.10     | 6.60   | 0.240     | 0.260 |

| С   | 3.56     | 4.57   | 0.140     | 0.180 |

| D   | 0.36     | 0.56   | 0.014     | 0.022 |

| F   | 1.27     | 1.78   | 0.050     | 0.070 |

| G   | 2.54     | BSC    | 0.100     | BSC   |

| Н   | 1.02     | 1.52   | 0.040     | 0.060 |

| J   | 0.20     | 0.30   | 0.008     | 0.012 |

| K   | 2.92     | 3.43   | 0.115     | 0.135 |

| L   | 7.62 BSC |        | 0.300 BSC |       |

| M   | 0°       | 15°    | 0°        | 15°   |

| N   | 0.51     | 1 02   | 0.020     | 0.040 |

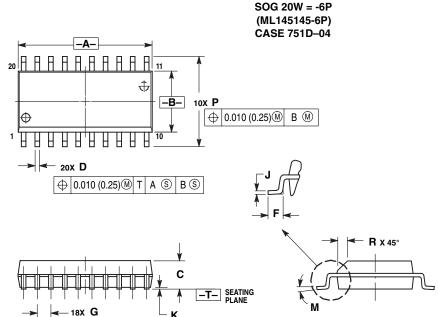

#### NOTES:

- OLES.

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MELE DESTRUCCIONE.

- MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.150

- (0.006) PER SIDE.

- (0.005) FER SIDE.

5. DIMENSION D DOES NOT INCLUDE

DAMBAR PROTRUSION. ALLOW ABLE

DAMBAR PROTRUSION SHALL BE 0.13

(0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 12.65  | 12.95  | 0.499     | 0.510 |  |

| В   | 7.40   | 7.60   | 0.292     | 0.299 |  |

| С   | 2.35   | 2.65   | 0.093     | 0.104 |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.50   | 0.90   | 0.020     | 0.035 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.25   | 0.32   | 0.010     | 0.012 |  |

| K   | 0.10   | 0.25   | 0.004     | 0.009 |  |

| M   | 0°     | 7°     | 0°        | 7°    |  |

| Р   | 10.05  | 10.55  | 0.395     | 0.415 |  |

| R   | 0.25   | 0.75   | 0.010     | 0.029 |  |

|     |        |        |           |       |  |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.