## **INTEGRATED CIRCUITS**

# DATA SHEET

74HC2G32; 74HCT2G32 Dual 2-input OR gate

Product specification Supersedes data of 2002 Jul 17 2003 Oct 30

### **Dual 2-input OR gate**

### 74HC2G32; 74HCT2G32

#### **FEATURES**

- Wide supply voltage range from 2.0 to 6.0 V

- · Symmetrical output impedance

- · High noise immunity

- · Low power dissipation

- · Balanced propagation delays

- Very small 8 pins package

- · Output capability: standard

- ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V.

#### **DESCRIPTION**

The 74HC2G/HCT2G32 is a high-speed Si-gate CMOS device.

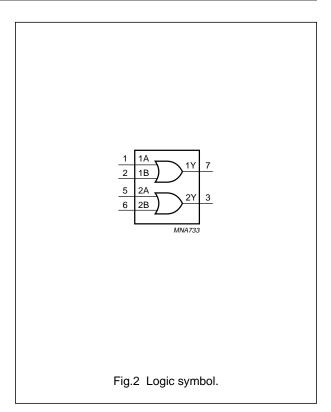

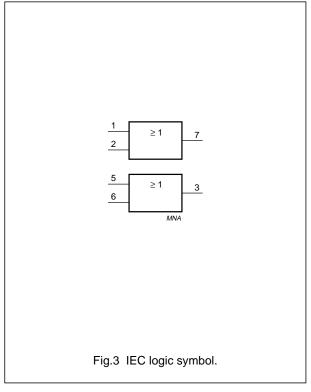

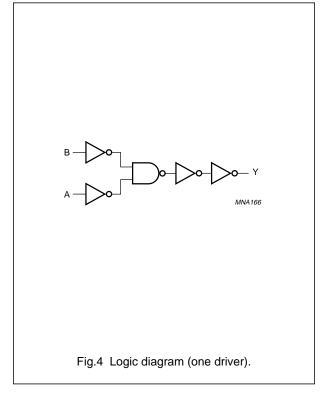

The 74HC2G/HCT2G32 provides the dual 2-input OR function.

#### **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb} = 25 \, ^{\circ}C$ ;  $t_r = t_f \le 6.0 \, \text{ns}$ .

| SYMBOL                             | PARAMETER                              | CONDITIONS                                    | TYP    | UNIT    |      |

|------------------------------------|----------------------------------------|-----------------------------------------------|--------|---------|------|

|                                    | FARAIVIETER                            | CONDITIONS                                    | HC2G32 | HCT2G32 | UNIT |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA, nB to nY         | $C_L = 50 \text{ pF}; V_{CC} = 4.5 \text{ V}$ | 9      | 13      | ns   |

| Cı                                 | input capacitance                      |                                               | 1.5    | 1.5     | pF   |

| C <sub>PD</sub>                    | power dissipation capacitance per gate | notes 1 and 2                                 | 10     | 11      | pF   |

#### Notes

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

$$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \sum (C_L \times V_{CC}^2 \times f_o)$$

where:

f<sub>i</sub> = input frequency in MHz;

$f_o = output frequency in MHz;$

C<sub>L</sub> = output load capacitance in pF;

$V_{CC}$  = supply voltage in Volts;

N = total load switching outputs;

$\sum (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs.}$

2. For 74HC2G32: the condition is  $V_I = GND$  to  $V_{CC}$ .

For 74HCT2G32: the condition is  $V_I$  = GND to  $V_{CC}$  – 1.5 V.

# Dual 2-input OR gate

74HC2G32; 74HCT2G32

### **FUNCTION TABLE**

See note 1.

| INF   | INPUT |    |  |

|-------|-------|----|--|

| nA nB |       | nY |  |

| L     | L     | L  |  |

| L     | Н     | Н  |  |

| Н     | L     | Н  |  |

| Н     | Н     | Н  |  |

#### Note

H = HIGH voltage level;

L = LOW voltage level.

### **ORDERING INFORMATION**

|             |                      | PACKAGE |         |          |          |         |  |  |  |  |

|-------------|----------------------|---------|---------|----------|----------|---------|--|--|--|--|

| TYPE NUMBER | TEMPERATURE<br>RANGE | PINS    | PACKAGE | MATERIAL | CODE     | MARKING |  |  |  |  |

| 74HC2G32DP  | -40 to +125 °C       | 8       | TSSOP8  | plastic  | SOT505-2 | H32     |  |  |  |  |

| 74HCT2G32DP | -40 to +125 °C       | 8       | TSSOP8  | plastic  | SOT505-2 | T32     |  |  |  |  |

| 74HC2G32DC  | -40 to +125 °C       | 8       | VSSOP8  | plastic  | SOT765-1 | H32     |  |  |  |  |

| 74HCT2G32DC | -40 to +125 °C       | 8       | VSSOP8  | plastic  | SOT765-1 | T32     |  |  |  |  |

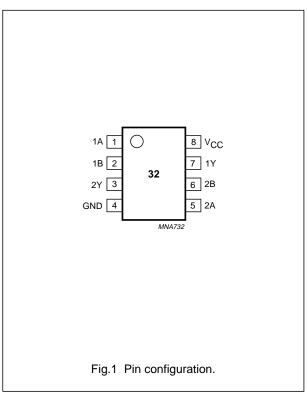

### **PINNING**

| PIN | SYMBOL          | DESCRIPTION    |

|-----|-----------------|----------------|

| 1   | 1A              | data input 1A  |

| 2   | 1B              | data input 1B  |

| 3   | 2Y              | data output 2Y |

| 4   | GND             | ground (0 V)   |

| 5   | 2A              | data input 2A  |

| 6   | 2B              | data input 2B  |

| 7   | 1Y              | data output 1Y |

| 8   | V <sub>CC</sub> | supply voltage |

# Dual 2-input OR gate

# 74HC2G32; 74HCT2G32

# Dual 2-input OR gate

74HC2G32; 74HCT2G32

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL                          | PARAMETER                     | CONDITIONS                               | 74HC2G32 |      |                 | 74HCT2G32 |      |                 | UNIT |

|---------------------------------|-------------------------------|------------------------------------------|----------|------|-----------------|-----------|------|-----------------|------|

| STIMBOL                         | PARAMETER                     | CONDITIONS                               | MIN.     | TYP. | MAX.            | MIN.      | TYP. | MAX.            | UNII |

| V <sub>CC</sub>                 | supply voltage                |                                          | 2.0      | 5.0  | 6.0             | 4.5       | 5.0  | 5.5             | V    |

| V <sub>I</sub>                  | input voltage                 |                                          | 0        | _    | V <sub>CC</sub> | 0         | _    | V <sub>CC</sub> | V    |

| Vo                              | output voltage                |                                          | 0        | _    | V <sub>CC</sub> | 0         | _    | V <sub>CC</sub> | V    |

| T <sub>amb</sub>                | operating ambient temperature | see DC and AC characteristics per device | -40      | +25  | +125            | -40       | +25  | +125            | °C   |

| t <sub>r</sub> , t <sub>f</sub> | input rise and fall times     | V <sub>CC</sub> = 2.0 V                  | _        | _    | 1000            | _         | _    | _               | ns   |

|                                 |                               | V <sub>CC</sub> = 4.5 V                  | _        | 6.0  | 500             | _         | 6.0  | 500             | ns   |

|                                 |                               | V <sub>CC</sub> = 6.0 V                  | _        | _    | 400             | _         | _    | _               | ns   |

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134); voltages are referenced to GND (ground = 0 V).

| SYMBOL           | PARAMETER                      | CONDITIONS                                                              | MIN. | MAX. | UNIT |

|------------------|--------------------------------|-------------------------------------------------------------------------|------|------|------|

| V <sub>CC</sub>  | supply voltage                 |                                                                         | -0.5 | +7.0 | V    |

| I <sub>IK</sub>  | input diode current            | $V_I < -0.5 \text{ V or } V_I > V_{CC} + 0.5 \text{ V}; \text{ note 1}$ | _    | ±20  | mA   |

| I <sub>OK</sub>  | output diode current           | $V_O < -0.5 \text{ V or } V_O > V_{CC} + 0.5 \text{ V}; \text{ note 1}$ | _    | ±20  | mA   |

| Io               | output source or sink current  | -0.5 V < V <sub>O</sub> < V <sub>CC</sub> + 0.5 V; note 1               | _    | 25   | mA   |

| I <sub>CC</sub>  | V <sub>CC</sub> or GND current | note 1                                                                  | _    | 50   | mA   |

| T <sub>stg</sub> | storage temperature            |                                                                         | -65  | +150 | °C   |

| P <sub>D</sub>   | power dissipation per package  | for temperature range from -40 to +125 °C; note 2                       | _    | 300  | mW   |

### Notes

- 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

- 2. Above 110  $^{\circ}\text{C}$  the value of  $P_D$  derates linearly with 8 mW/K.

# Dual 2-input OR gate

74HC2G32; 74HCT2G32

### **DC CHARACTERISTICS**

### **Type 74HC2G32**

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| 0)/4501                  | PARAMETER                 | TEST CONDIT                         | TIONS               | MIN.  | T)(D | MAY  |      |

|--------------------------|---------------------------|-------------------------------------|---------------------|-------|------|------|------|

| SYMBOL                   |                           | OTHER                               | V <sub>CC</sub> (V) | WIIN. | TYP. | MAX. | UNIT |

| T <sub>amb</sub> = 25 °C |                           |                                     |                     |       |      | •    |      |

| V <sub>IH</sub>          | HIGH-level input voltage  |                                     | 2.0                 | 1.5   | 1.2  | _    | V    |

|                          |                           |                                     | 4.5                 | 3.15  | 2.4  | _    | V    |

|                          |                           |                                     | 6.0                 | 4.2   | 3.2  | _    | V    |

| V <sub>IL</sub>          | LOW-level input           |                                     | 2.0                 | _     | 0.8  | 0.5  | V    |

|                          | voltage                   |                                     | 4.5                 | _     | 2.1  | 1.35 | V    |

|                          |                           |                                     | 6.0                 | _     | 2.8  | 1.8  | V    |

| V <sub>OH</sub>          | HIGH-level output voltage | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |      |      |

|                          |                           | $I_{O} = -20 \mu A$                 | 2.0                 | 1.9   | 2.0  | _    | V    |

|                          |                           | $I_{O} = -20 \mu A$                 | 4.5                 | 4.4   | 4.5  | _    | V    |

|                          |                           | $I_{O} = -20 \mu A$                 | 6.0                 | 5.9   | 6.0  | _    | V    |

|                          |                           | $I_{O} = -4.0 \text{ mA}$           | 4.5                 | 4.18  | 4.32 | _    | V    |

|                          |                           | $I_{O} = -5.2 \text{ mA}$           | 6.0                 | 5.68  | 5.81 | _    | V    |

| V <sub>OL</sub>          | LOW-level output          | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |      |      |

|                          | voltage                   | $I_{O} = 20 \mu A$                  | 2.0                 | _     | 0    | 0.1  | V    |

|                          |                           | $I_{O} = 20 \mu A$                  | 4.5                 | _     | 0    | 0.1  | V    |

|                          |                           | $I_{O} = 20 \mu A$                  | 6.0                 | _     | 0    | 0.1  | V    |

|                          |                           | $I_{O} = 4.0 \text{ mA}$            | 4.5                 | _     | 0.15 | 0.26 | V    |

|                          |                           | $I_{O} = 5.2 \text{ mA}$            | 6.0                 | _     | 0.16 | 0.26 | V    |

| ILI                      | input leakage current     | $V_I = V_{CC}$ or GND               | 6.0                 | _     | _    | ±0.1 | μΑ   |

| I <sub>CC</sub>          | quiescent supply current  | $V_I = V_{CC}$ or GND;<br>$I_O = 0$ | 6.0                 | _     | _    | 1.0  | μΑ   |

# Dual 2-input OR gate

# 74HC2G32; 74HCT2G32

| OVMDOL                    | DADAMETED                | TEST CONDIT                         | TIONS               | BAIN! | TVD  | NA A V |      |

|---------------------------|--------------------------|-------------------------------------|---------------------|-------|------|--------|------|

| SYMBOL                    | PARAMETER                | OTHER                               | V <sub>CC</sub> (V) | MIN.  | TYP. | MAX.   | UNIT |

| T <sub>amb</sub> = -40 to | o +85 °C                 |                                     |                     |       | •    | •      | •    |

| V <sub>IH</sub>           | HIGH-level input voltage |                                     | 2.0                 | 1.5   | _    | _      | V    |

|                           |                          |                                     | 4.5                 | 3.15  | _    | _      | V    |

|                           |                          |                                     | 6.0                 | 4.2   | _    | _      | V    |

| V <sub>IL</sub>           | LOW-level input          |                                     | 2.0                 | _     | _    | 0.5    | V    |

|                           | voltage                  |                                     | 4.5                 | _     | _    | 1.35   | V    |

|                           |                          |                                     | 6.0                 | -     | _    | 1.8    | V    |

| V <sub>OH</sub>           | HIGH-level output        | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |        |      |

|                           | voltage                  | $I_{O} = -20  \mu A$                | 2.0                 | 1.9   | _    | _      | V    |

|                           |                          | $I_{O} = -20  \mu A$                | 4.5                 | 4.4   | _    | _      | V    |

|                           |                          | $I_{O} = -20  \mu A$                | 6.0                 | 5.9   | _    | _      | V    |

|                           |                          | $I_{O} = -4.0 \text{ mA}$           | 4.5                 | 4.13  | _    | _      | V    |

|                           |                          | $I_{O} = -5.2 \text{ mA}$           | 6.0                 | 5.63  | _    | _      | V    |

| $V_{OL}$                  | LOW-level output         | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |        |      |

|                           | voltage                  | $I_0 = 20 \mu A$                    | 2.0                 | _     | _    | 0.1    | V    |

|                           |                          | $I_0 = 20 \mu A$                    | 4.5                 | _     | _    | 0.1    | V    |

|                           |                          | $I_0 = 20 \mu A$                    | 6.0                 | _     | _    | 0.1    | V    |

|                           |                          | $I_0 = 4.0 \text{ mA}$              | 4.5                 | _     | _    | 0.33   | V    |

|                           |                          | $I_0 = 5.2 \text{ mA}$              | 6.0                 | _     | _    | 0.33   | V    |

| ILI                       | input leakage current    | $V_I = V_{CC}$ or GND               | 6.0                 | _     | _    | ±1.0   | μΑ   |

| I <sub>CC</sub>           | quiescent supply current | $V_I = V_{CC}$ or GND;<br>$I_O = 0$ | 6.0                 | _     | -    | 10     | μΑ   |

# Dual 2-input OR gate

# 74HC2G32; 74HCT2G32

| OVMDOL                    | DADAMETED                | TEST CONDIT                         | TIONS               | BAIN! | TVD  | NA A V |      |

|---------------------------|--------------------------|-------------------------------------|---------------------|-------|------|--------|------|

| SYMBOL                    | PARAMETER                | OTHER                               | V <sub>CC</sub> (V) | MIN.  | TYP. | MAX.   | UNIT |

| T <sub>amb</sub> = -40 to | o +125 °C                |                                     |                     |       | •    | •      | •    |

| V <sub>IH</sub>           | HIGH-level input voltage |                                     | 2.0                 | 1.5   | _    | _      | V    |

|                           |                          |                                     | 4.5                 | 3.15  | _    | _      | V    |

|                           |                          |                                     | 6.0                 | 4.2   | _    | _      | V    |

| V <sub>IL</sub>           | LOW-level input          |                                     | 2.0                 | _     | _    | 0.5    | V    |

|                           | voltage                  |                                     | 4.5                 | _     | _    | 1.35   | V    |

|                           |                          |                                     | 6.0                 | -     | _    | 1.8    | V    |

| V <sub>OH</sub>           | HIGH-level output        | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |        |      |

|                           | voltage                  | $I_{O} = -20  \mu A$                | 2.0                 | 1.9   | _    | _      | V    |

|                           |                          | $I_{O} = -20  \mu A$                | 4.5                 | 4.4   | _    | _      | V    |

|                           |                          | $I_{O} = -20  \mu A$                | 6.0                 | 5.9   | _    | _      | V    |

|                           |                          | $I_{O} = -4.0 \text{ mA}$           | 4.5                 | 3.7   | _    | _      | V    |

|                           |                          | $I_{O} = -5.2 \text{ mA}$           | 6.0                 | 5.2   | _    | _      | V    |

| $V_{OL}$                  | LOW-level output         | $V_I = V_{IH}$ or $V_{IL}$          |                     |       |      |        |      |

|                           | voltage                  | $I_0 = 20 \mu A$                    | 2.0                 | _     | _    | 0.1    | V    |

|                           |                          | $I_0 = 20 \mu A$                    | 4.5                 | _     | _    | 0.1    | V    |

|                           |                          | $I_0 = 20 \mu A$                    | 6.0                 | _     | _    | 0.1    | V    |

|                           |                          | $I_{O} = 4.0 \text{ mA}$            | 4.5                 | _     | _    | 0.4    | V    |

|                           |                          | $I_0 = 5.2 \text{ mA}$              | 6.0                 | _     | _    | 0.4    | V    |

| ILI                       | input leakage current    | $V_I = V_{CC}$ or GND               | 6.0                 | _     | _    | ±1.0   | μΑ   |

| I <sub>CC</sub>           | quiescent supply current | $V_I = V_{CC}$ or GND;<br>$I_O = 0$ | 6.0                 | _     | -    | 20     | μΑ   |

# Dual 2-input OR gate

74HC2G32; 74HCT2G32

Type 74HCT2G32

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| CVMDOL                    | DADAMETED                           | TEST CONDITIONS                         |                     | MINI | TYP.  | MAY  | UNIT |

|---------------------------|-------------------------------------|-----------------------------------------|---------------------|------|-------|------|------|

| SYMBOL                    | PARAMETER                           | OTHER                                   | V <sub>CC</sub> (V) | MIN. | 1117. | MAX. | UNII |

| T <sub>amb</sub> = 25 °C  | ;                                   |                                         |                     |      | •     | _    | •    |

| V <sub>IH</sub>           | HIGH-level input voltage            |                                         | 4.5 to 5.5          | 2.0  | 1.6   | _    | V    |

| V <sub>IL</sub>           | LOW-level input voltage             |                                         | 4.5 to 5.5          | _    | 1.2   | 0.8  | V    |

| $V_{OH}$                  | HIGH-level output                   | $V_I = V_{IH}$ or $V_{IL}$              |                     |      |       |      |      |

|                           | voltage                             | $I_{O} = -20 \mu\text{A}$               | 4.5                 | 4.4  | 4.5   | _    | V    |

|                           |                                     | $I_{O} = -4.0 \text{ mA}$               | 4.5                 | 4.18 | 4.32  | _    | V    |

| V <sub>OL</sub>           | LOW-level output                    | $V_I = V_{IH}$ or $V_{IL}$              |                     |      |       |      |      |

|                           | voltage                             | I <sub>O</sub> = 20 μA                  | 4.5                 | _    | 0     | 0.1  | V    |

|                           |                                     | $I_{O} = 4.0 \text{ mA}$                | 4.5                 | _    | 0.15  | 0.26 | V    |

| ILI                       | input leakage current               | $V_I = V_{CC}$ or GND                   | 5.5                 | _    | _     | ±0.1 | μΑ   |

| I <sub>CC</sub>           | quiescent supply current            | $V_I = V_{CC}$ or GND;<br>$I_O = 0$     | 5.5                 | _    | -     | 1.0  | μΑ   |

| Δl <sub>CC</sub>          | additional supply current per input | $V_I = V_{CC} - 2.1 \text{ V}; I_O = 0$ | 4.5 to 5.5          | _    | _     | 300  | μА   |

| T <sub>amb</sub> = -40 to | o +85 °C                            | •                                       |                     |      | •     |      | •    |

| V <sub>IH</sub>           | HIGH-level input voltage            |                                         | 4.5 to 5.5          | 2.0  | -     | _    | V    |

| V <sub>IL</sub>           | LOW-level input voltage             |                                         | 4.5 to 5.5          | -    | _     | 0.8  | V    |

| V <sub>OH</sub>           | HIGH-level output                   | $V_I = V_{IH}$ or $V_{IL}$              |                     |      |       |      |      |

|                           | voltage                             | $I_{O} = -20 \mu\text{A}$               | 4.5                 | 4.4  | -     | _    | V    |

|                           |                                     | $I_{O} = -4.0 \text{ mA}$               | 4.5                 | 4.13 | _     | _    | V    |

| V <sub>OL</sub>           | LOW-level output                    | $V_I = V_{IH}$ or $V_{IL}$              |                     |      |       |      |      |

|                           | voltage                             | I <sub>O</sub> = 20 μA                  | 4.5                 | _    | _     | 0.1  | V    |

|                           |                                     | I <sub>O</sub> = 4.0 mA                 | 4.5                 | _    | _     | 0.33 | V    |

| I <sub>LI</sub>           | input leakage current               | $V_I = V_{CC}$ or GND                   | 5.5                 | _    | _     | ±1.0 | μΑ   |

| I <sub>cc</sub>           | quiescent supply current            | $V_I = V_{CC}$ or GND;<br>$I_O = 0$     | 5.5                 | -    | -     | 10   | μА   |

| Δl <sub>CC</sub>          | additional supply current per input | $V_I = V_{CC} - 2.1 \text{ V}; I_O = 0$ | 4.5 to 5.5          | _    | -     | 375  | μΑ   |

# Dual 2-input OR gate

# 74HC2G32; 74HCT2G32

| CVMDOL                    | DADAMETED                           | TEST CONDIT                                                                | IONS                | BAINI      | TYP. | MAY  | UNIT   |

|---------------------------|-------------------------------------|----------------------------------------------------------------------------|---------------------|------------|------|------|--------|

| SYMBOL                    | PARAMETER                           | OTHER                                                                      | V <sub>CC</sub> (V) | MIN.       | ITP. | MAX. | ONIT   |

| T <sub>amb</sub> = -40 to | ) +125 °C                           |                                                                            |                     | •          | •    | •    |        |

| V <sub>IH</sub>           | HIGH-level input voltage            |                                                                            | 4.5 to 5.5          | 2.0        | -    | -    | V      |

| V <sub>IL</sub>           | LOW-level input voltage             |                                                                            | 4.5 to 5.5          | -          | -    | 0.8  | V      |

| V <sub>OH</sub>           | HIGH-level output voltage           | $V_I = V_{IH}$ or $V_{IL}$<br>$I_O = -20 \mu A$<br>$I_O = -4.0 \text{ mA}$ | 4.5<br>4.5          | 4.4<br>3.7 | _    | -    | V<br>V |

| V <sub>OL</sub>           | LOW-level output voltage            | $V_I = V_{IH} \text{ or } V_{IL}$ $I_O = 20 \mu A$ $I_O = 4.0 \text{ mA}$  | 4.5<br>4.5          | -          | -    | 0.1  | V<br>V |

| ILI                       | input leakage current               | $V_I = V_{CC}$ or GND                                                      | 5.5                 | _          | -    | ±1.0 | μΑ     |

| I <sub>CC</sub>           | quiescent supply current            | $V_I = V_{CC}$ or GND;<br>$I_O = 0$                                        | 5.5                 | -          | _    | 20   | μΑ     |

| Δl <sub>CC</sub>          | additional supply current per input | $V_1 = V_{CC} - 2.1 \text{ V}; I_O = 0$                                    | 4.5 to 5.5          | -          | -    | 410  | μΑ     |

# Dual 2-input OR gate

74HC2G32; 74HCT2G32

### **AC CHARACTERISTICS**

### **Type 74HC2G32**

GND = 0 V;  $t_r = t_f \le 6.0$  ns;  $C_L = 50$  pF.

| CVMDOL                             | DADAMETED              | TEST CONDI       | TIONS               | MIN.    | TYP. | MAX. | LINUT |

|------------------------------------|------------------------|------------------|---------------------|---------|------|------|-------|

| SYMBOL                             | PARAMETER              | WAVEFORMS        | V <sub>CC</sub> (V) | IVIIIN. | 117. | WAX. | UNIT  |

| T <sub>amb</sub> = 25 °C           |                        |                  |                     |         | •    |      | •     |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,  | see Figs 5 and 6 | 2.0                 | _       | 24   | 75   | ns    |

|                                    | nB to nY               |                  | 4.5                 | _       | 9    | 15   | ns    |

|                                    |                        |                  | 6.0                 | _       | 7    | 13   | ns    |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time | see Figs 5 and 6 | 2.0                 | _       | 18   | 75   | ns    |

|                                    |                        |                  | 4.5                 | _       | 6    | 15   | ns    |

|                                    |                        |                  | 6.0                 | _       | 5    | 13   | ns    |

| $T_{amb} = -40 \text{ to}$         | +85 °C                 |                  |                     |         |      |      |       |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,  | see Figs 5 and 6 | 2.0                 | _       | _    | 95   | ns    |

|                                    | nB to nY               |                  | 4.5                 | _       | _    | 19   | ns    |

|                                    |                        |                  | 6.0                 | _       | _    | 16   | ns    |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time | see Figs 5 and 6 | 2.0                 | _       | _    | 95   | ns    |

|                                    |                        |                  | 4.5                 | _       | _    | 19   | ns    |

|                                    |                        |                  | 6.0                 | _       | _    | 16   | ns    |

| $T_{amb} = -40 \text{ to}$         | +125 °C                |                  | •                   |         | •    |      |       |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,  | see Figs 5 and 6 | 2.0                 | _       | _    | 110  | ns    |

|                                    | nB to nY               |                  | 4.5                 | _       | _    | 22   | ns    |

|                                    |                        |                  | 6.0                 | _       | _    | 20   | ns    |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time | see Figs 5 and 6 | 2.0                 | _       | -    | 125  | ns    |

|                                    |                        |                  | 4.5                 | _       | -    | 25   | ns    |

|                                    |                        |                  | 6.0                 | _       | _    | 20   | ns    |

## Dual 2-input OR gate

## 74HC2G32; 74HCT2G32

### Type 74HCT2G32

GND = 0 V;  $t_r = t_f \le 6.0$  ns;  $C_L = 50$  pF.

| CVMDOL                             | DADAMETED                         | TEST CONDIT      | TIONS               | BAINI | TYP.  | MAY  | LINUT |  |  |  |  |

|------------------------------------|-----------------------------------|------------------|---------------------|-------|-------|------|-------|--|--|--|--|

| SYMBOL                             | PARAMETER                         | WAVEFORMS        | V <sub>CC</sub> (V) | MIN.  | I TP. | MAX. | UNIT  |  |  |  |  |

| T <sub>amb</sub> = 25 °C           |                                   |                  | •                   | •     | •     | •    | •     |  |  |  |  |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,<br>nB to nY | see Figs 5 and 6 | 4.5                 | -     | 13    | 24   | ns    |  |  |  |  |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time            | see Figs 5 and 6 | 4.5                 | _     | 6     | 15   | ns    |  |  |  |  |

| T <sub>amb</sub> = -40 to          | T <sub>amb</sub> = −40 to +85 °C  |                  |                     |       |       |      |       |  |  |  |  |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,<br>nB to nY | see Figs 5 and 6 | 4.5                 | -     | -     | 30   | ns    |  |  |  |  |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time            | see Figs 5 and 6 | 4.5                 | _     | -     | 19   | ns    |  |  |  |  |

| T <sub>amb</sub> = -40 to +125 °C  |                                   |                  |                     |       |       |      |       |  |  |  |  |

| t <sub>PHL</sub> /t <sub>PLH</sub> | propagation delay nA,<br>nB to nY | see Figs 5 and 6 | 4.5                 | _     | -     | 36   | ns    |  |  |  |  |

| t <sub>THL</sub> /t <sub>TLH</sub> | output transition time            | see Figs 5 and 6 | 4.5                 | _     | _     | 22   | ns    |  |  |  |  |

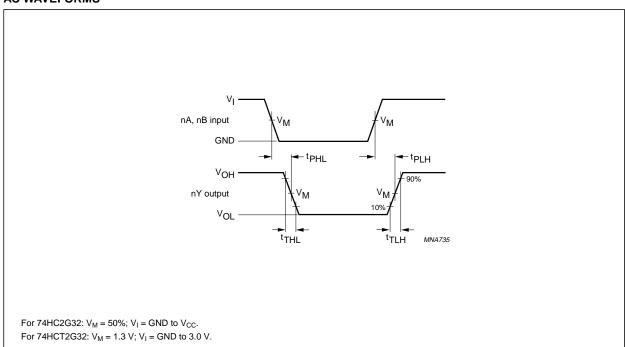

### **AC WAVEFORMS**

Fig.5 The input (nA, nB) to output (nY) propagation delays and transition times.

# Dual 2-input OR gate

# 74HC2G32; 74HCT2G32

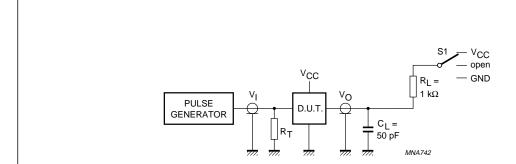

| TEST                               | S1              |

|------------------------------------|-----------------|

| t <sub>PLH</sub> /t <sub>PHL</sub> | open            |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | V <sub>CC</sub> |

| t <sub>PHZ</sub> /t <sub>PZH</sub> | GND             |

Definitions for test circuit:

C<sub>L</sub> = load capacitance including jig and probe capacitance.

$R_T$  = termination resistance should be equal to the output impedance  $Z_0$  of the pulse generator.

Fig.6 Load circuitry for switching times.

# Dual 2-input OR gate

## 74HC2G32; 74HCT2G32

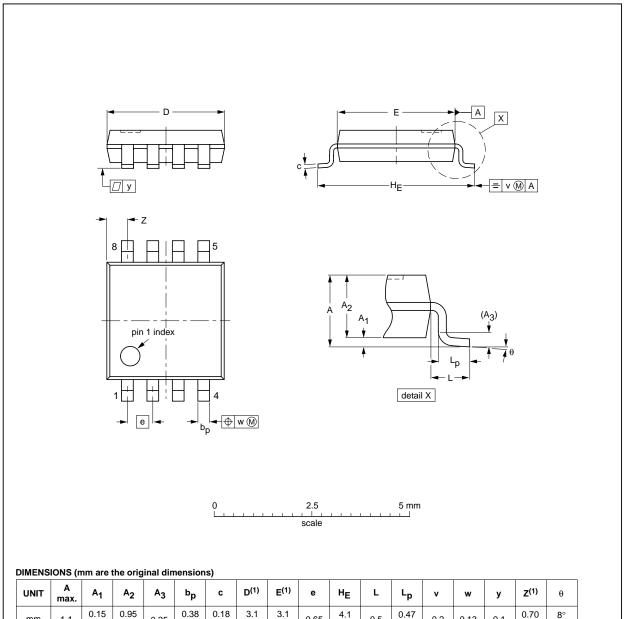

### **PACKAGE OUTLINES**

TSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm; lead length 0.5 mm SOT505-2

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L   | Lp           | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|------|------------|-----|--------------|-----|------|-----|------------------|----------|

| mm   | 1.1       | 0.15<br>0.00   | 0.95<br>0.75   | 0.25           | 0.38<br>0.22 | 0.18<br>0.08 | 3.1<br>2.9       | 3.1<br>2.9       | 0.65 | 4.1<br>3.9 | 0.5 | 0.47<br>0.33 | 0.2 | 0.13 | 0.1 | 0.70<br>0.35     | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |     | REFER | EUROPEAN | ISSUE DATE |            |            |  |

|----------|-----|-------|----------|------------|------------|------------|--|

| VERSION  | IEC | JEDEC | JEITA    |            | PROJECTION | ISSUE DATE |  |

| SOT505-2 |     |       |          |            |            | 02-01-16   |  |

2003 Oct 30 14

# Dual 2-input OR gate

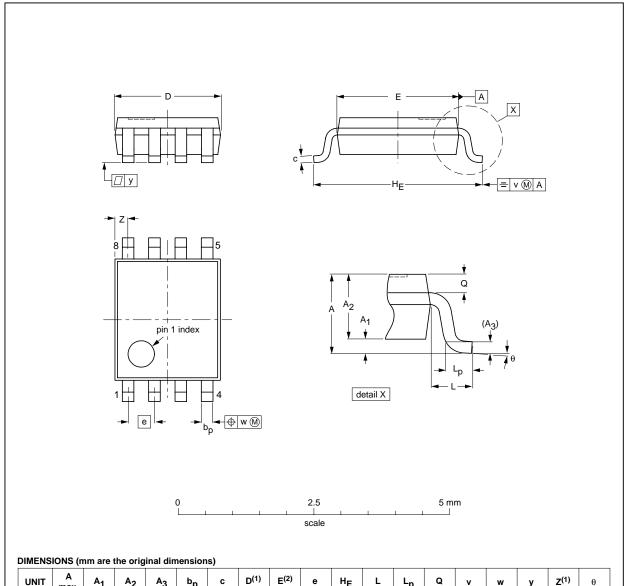

# 74HC2G32; 74HCT2G32

### VSSOP8: plastic very thin shrink small outline package; 8 leads; body width 2.3 mm

SOT765-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | С            | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L   | Lp           | Q            | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|-----|------------|-----|--------------|--------------|-----|------|-----|------------------|----------|

| mm   | 1         | 0.15<br>0.00   | 0.85<br>0.60   | 0.12 | 0.27<br>0.17 | 0.23<br>0.08 | 2.1<br>1.9       | 2.4<br>2.2       | 0.5 | 3.2<br>3.0 | 0.4 | 0.40<br>0.15 | 0.21<br>0.19 | 0.2 | 0.13 | 0.1 | 0.4<br>0.1       | 8°<br>0° |

- Plastic or metal protrusions of 0.15 mm maximum per side are not included.

Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |           | EUROPEAN | ISSUE DATE |            |            |  |

|----------|-----------|----------|------------|------------|------------|--|

| VERSION  | IEC JEDEC |          | JEITA      | PROJECTION | ISSUE DATE |  |

| SOT765-1 |           | MO-187   |            |            | 02-06-07   |  |

2003 Oct 30 15

### Dual 2-input OR gate

### 74HC2G32; 74HCT2G32

#### SOLDERING

#### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended.

#### Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 220 °C for thick/large packages, and below 235 °C for small/thin packages.

#### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

### Dual 2-input OR gate

74HC2G32; 74HCT2G32

#### Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE <sup>(1)</sup>                                                   | SOLDERING METHOD                  |                       |  |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------|-----------------------|--|--|--|--|

| PACKAGE                                                                  | WAVE                              | REFLOW <sup>(2)</sup> |  |  |  |  |

| BGA, LBGA, LFBGA, SQFP, TFBGA, VFBGA                                     | not suitable                      | suitable              |  |  |  |  |

| DHVQFN, HBCC, HBGA, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, HVSON, SMS | not suitable <sup>(3)</sup>       | suitable              |  |  |  |  |

| PLCC <sup>(4)</sup> , SO, SOJ                                            | suitable                          | suitable              |  |  |  |  |

| LQFP, QFP, TQFP                                                          | not recommended <sup>(4)(5)</sup> | suitable              |  |  |  |  |

| SSOP, TSSOP, VSO, VSSOP                                                  | not recommended <sup>(6)</sup>    | suitable              |  |  |  |  |

#### **Notes**

- For more detailed information on the BGA packages refer to the "(LF)BGA Application Note" (AN01026); order a copy from your Philips Semiconductors sales office.

- 2. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 3. These packages are not suitable for wave soldering. On versions with the heatsink on the bottom side, the solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the heatsink on the top side, the solder might be deposited on the heatsink surface.

- 4. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 5. Wave soldering is suitable for LQFP, TQFP and QFP packages with a pitch (e) larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 6. Wave soldering is suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

### Dual 2-input OR gate

74HC2G32; 74HCT2G32

#### **DATA SHEET STATUS**

| LEVEL | DATA SHEET<br>STATUS <sup>(1)</sup> | PRODUCT<br>STATUS <sup>(2)(3)</sup> | DEFINITION                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                      | Development                         | This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                    |

| II    | Preliminary data                    | Qualification                       | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                        | Production                          | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

#### Notes

- 1. Please consult the most recently issued data sheet before initiating or completing a design.

- 2. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

- 3. For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### **DEFINITIONS**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **DISCLAIMERS**

Life support applications — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

# Philips Semiconductors – a worldwide company

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

© Koninklijke Philips Electronics N.V. 2003

SCA75

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

613508/02/pp19

Date of release: 2003 Oct 30

Document order number: 9397 750 10566

Let's make things better.

Philips Semiconductors