January 2003 Revised January 2003

# 100LVELT22 3.3V Dual LVTTL/LVCMOS to Differential LVPECL Translator

# **General Description**

The 100LVELT22 is a LVTTL/LVCMOS to differential LVPECL translator operating from a single  $\pm 3.3$ V supply.

Both outputs of a differential pair should be terminated in  $50\Omega$  to  $V_{CC}$  - 2.0V even if only one output is being used. If an output pair is unused both outputs can be left open (un-terminated).

The 100 series is temperature compensated.

## **Features**

- Typical propagation delay of 350 ps

- <100 ps skew between outputs

- Max I<sub>CC</sub> of 28 mA at 25°C

- When TTL input is left Open Q output defaults HIGH

- Fairchild MSOP-8 package is a drop-in replacement to ON TSSOP-8

- Flow through pinout

- Meets or exceeds JEDEC specification EIA/JESD78 IC latch-up test

- Moisture Sensitivity Level 1

- ESD Performance:

Human Body Model > 2000V Machine Model > 200V

# **Ordering Code:**

|                               |         | Product  |                                                                             |

|-------------------------------|---------|----------|-----------------------------------------------------------------------------|

| Order Number                  | Package | Code     | Package Description                                                         |

|                               | Number  | Top Mark |                                                                             |

| 100LVELT22M                   | M08A    | KVT22    | 8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| 100LVELT22M8<br>(Preliminary) | MA08D   | KR22     | 8-Lead Molded Small Outline Package (MSOP), JEDEC MO-187, 3.0mm Wide        |

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

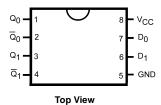

# **Connection Diagram**

**Pin Descriptions**

| Pin Name                        | Description                 |  |  |  |  |  |  |

|---------------------------------|-----------------------------|--|--|--|--|--|--|

| $Q_n, \overline{Q}_n$           | LVPECL Differential Outputs |  |  |  |  |  |  |

| D <sub>0</sub> , D <sub>1</sub> | LVTTL/LVCMOS Inputs         |  |  |  |  |  |  |

| V <sub>CC</sub>                 | Positive Supply             |  |  |  |  |  |  |

| GND                             | Ground                      |  |  |  |  |  |  |

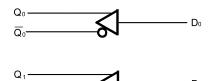

# **Logic Diagram**

© 2003 Fairchild Semiconductor Corporation

DS500777

www.fairchildsemi.com

# **Absolute Maximum Ratings**(Note 1)

$\label{eq:supply Voltage VCC} \mbox{Supply Voltage (V$_{CC}$)} \qquad 0.0V \mbox{ to +7.0V} \\ \mbox{Input Voltage (V$_{I}$) $V$_{I} $\le $V$_{CC}$} \qquad 0.0V \mbox{ to +7.0V} \\ \mbox{}$

DC Output Current (I<sub>OUT</sub>)

# Recommended Operating Conditions

Power Supply Operating  $V_{CC} = 3.0V \text{ to } 3.8V$  LVTTL/LVCMOS Input Voltage  $0.0V \text{ to } V_{CC}$  Free Air Operating Temperature (T<sub>A</sub>)  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# LVPECL DC Electrical Characteristics $V_{CC} = 3.3V$ ; GND = 0.0V (Note 2)

| Symbol          | Parameter                    | -40°C |     |      | 25°C |     |      | 85°C |     |      | Units  |

|-----------------|------------------------------|-------|-----|------|------|-----|------|------|-----|------|--------|

| Syllibol        | raiametei                    | Min   | Тур | Max  | Min  | Тур | Max  | Min  | Тур | Max  | Ullits |

| I <sub>CC</sub> | Power Supply Current         |       |     | 28   |      |     | 28   |      |     | 29   | mA     |

| V <sub>OH</sub> | Output HIGH Voltage (Note 3) | 2215  |     | 2420 | 2275 |     | 2420 | 2275 |     | 2420 | mV     |

| V <sub>OL</sub> | Output LOW Voltage (Note 3)  | 1470  |     | 1745 | 1490 |     | 1680 | 1490 |     | 1680 | mV     |

Note 2: Output parameters vary 1 to 1 with  $V_{CC}$ .  $V_{CC}$  can vary  $\pm 0.15 V$ .

Note 3: Outputs are terminated through a  $50\Omega$  resistor to  $V_{CC}-2.0V.$

Note: Devices are designed to meet the DC specifications after thermal equilibrium has been established. Circuit is tested with air flow greater than 500LFPM maintained.

# LVTTL/LVCMOS DC Electrical Characteristics $V_{CC} = 3.3V$ ; GND = 0.0V (Note 4)

| Symbol          | Parameter           | T <sub>A</sub> = | = –40°C to 8 | 5°C  | Units | Condition                            |  |  |  |

|-----------------|---------------------|------------------|--------------|------|-------|--------------------------------------|--|--|--|

| - Cyllibol      | i didiliotoi        | Min              | Тур          | Max  | Omio  |                                      |  |  |  |

| I <sub>IH</sub> | Input HIGH Current  |                  |              | 20   | μА    | $V_{IN} = 2.7V$<br>$V_{IN} = V_{CC}$ |  |  |  |

|                 |                     |                  |              | 100  | μΛ    | $V_{IN} = V_{CC}$                    |  |  |  |

| I <sub>IL</sub> | Input LOW Current   |                  |              | -200 | μΑ    | V <sub>IN</sub> = 0.5V               |  |  |  |

| V <sub>IK</sub> | Clamp Diode Voltage |                  |              | -1.2 | V     | I <sub>IN</sub> = -18 mA             |  |  |  |

| V <sub>IH</sub> | Input HIGH Voltage  | 2.0              |              |      | V     |                                      |  |  |  |

| V <sub>IL</sub> | Input LOW Voltage   |                  |              | 0.8  | V     |                                      |  |  |  |

Note 4: V<sub>CC</sub> can vary ±0.15V.

Note: Devices are designed to meet the DC specifications after thermal equilibrium has been established. Circuit is tested with air flow greater than 500LFPM maintained.

# AC Electrical Characteristics V<sub>CC</sub> = 3.3V; GND = 0.0V (Note 5)

| Symbol                              | Parameter                       | -40°C |     |     | 25°C |     |     | 85°C |     |     | Units | Figure   |

|-------------------------------------|---------------------------------|-------|-----|-----|------|-----|-----|------|-----|-----|-------|----------|

| Symbol                              | Farameter                       | Min   | Тур | Max | Min  | Тур | Max | Min  | Тур | Max | Units | Number   |

| f <sub>MAX</sub>                    | Maximum Toggle Frequency        |       | TBD |     |      | TBD |     |      | TBD |     | MHz   |          |

| t <sub>JITTER</sub>                 | Cycle-to-Cycle Jitter           |       | TBD |     |      | TBD |     |      | TBD |     | ps    |          |

| t <sub>PLH</sub> / t <sub>PHL</sub> | Propagation Delay (Note 6)      | 200   | 350 | 600 | 200  | 350 | 600 | 200  | 350 | 600 | ps    | Figure 1 |

| t <sub>SKEW</sub>                   | Skew Output-to-Output           |       | 30  | 100 |      | 30  | 100 |      | 30  | 100 | ps    |          |

|                                     | Part-to-Part                    |       |     | 400 |      |     | 400 |      |     | 400 | ρs    |          |

| t <sub>r</sub> , t <sub>f</sub>     | Output Rise Time Q (20% to 80%) | 200   |     | 550 | 200  |     | 500 | 200  |     | 500 | ns    | Figure 2 |

Note 5: V<sub>CC</sub> can vary ±0.15V.

Note 6: Specifications for standard LVTTL input signal (see Figure 1).

# **Switching Waveforms** t<sub>PHL</sub> → Input $t_r/t_f = 3 \text{ns} 10\%$ to 90% FIGURE 1. LVTTL to Differential LVPECL Propagation Delay FIGURE 2. Differential Output Edge Rates

www.fairchildsemi.com

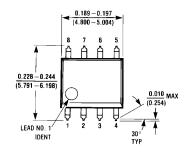

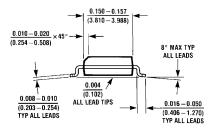

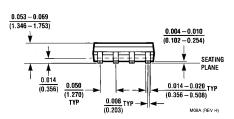

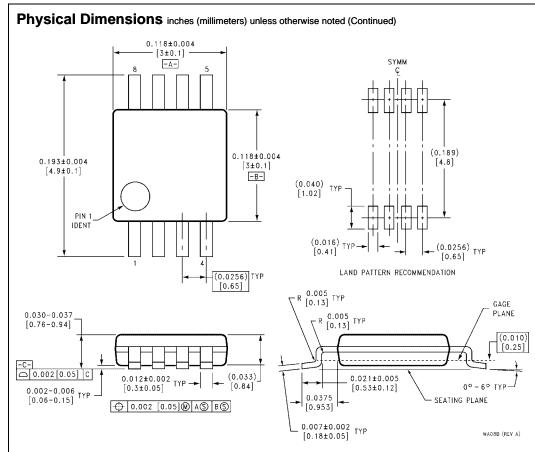

# Physical Dimensions inches (millimeters) unless otherwise noted

8-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M08A

8-Lead Molded Small Outline Package (MSOP), JEDEC MO-187, 3.0mm Wide Package Number MA08D

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

5

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

www.fairchildsemi.com