# PI90LV03/PI90LVB03

# SOTiny<sup>™</sup> LVDS Repeater

### Features

- · Complies with ANSI/TIA/EIA-644-A LVDS standard

- LVDS receiver inputs accept LVPECL signals

- Low jitter 660 Mbps fully differential data path

- Bus-Terminal ESD exceeds 2kV

- Single +3.3V supply voltage operation

- Receiver Differential Input Voltage Threshold < ±100mV

- Receiver open-circuit failsafe

- Low-Voltage Differential Signaling with typical Output Voltages of 350mV into:

- 100Ω Load (PI90LV03)

- $-50\Omega$  Load (PI90LVB03)

- Typical Propagation Delay Times of 1.5ns

- Typical Power Dissipation of 20mW @ 200 MHz

- Outputs are High Impedance with  $V_{CC} < 1.5V$

- Industrial Temperature Range: -40°C to 85°C

- Packaging:

- 6-pin space-saving SOT-23 (T)

### **Function Table**

| Inputs                                              | Outputs                   |

|-----------------------------------------------------|---------------------------|

| $V_{ID} = V_A - V_B$                                | $V_{\rm Y}$ - $V_{\rm Z}$ |

| $V_{ID} > 50 mV$                                    | Н                         |

| $50 \mathrm{mV} < \mathrm{V_{ID}} < 50 \mathrm{mV}$ | Х                         |

| $V_{ID} \le -50 mV$                                 | L                         |

| Open                                                | Н                         |

Notes:

1. H = high level; L = low level; X = indeterminate

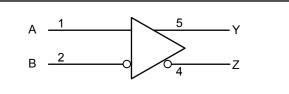

### **Block Diagram**

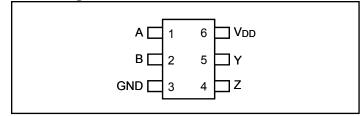

### **Pin Configuration**

## Description

PI90LV03 and PI90LVB03 are single LVDS Repeaters that use low-voltage differential signaling (LVDS) to support data rates up to 660 Mbps. The PI90LVB03 features high-drive output. Both products are designed for applications requiring high-speed, lowpower consumption, low-noise generation, and a small package.

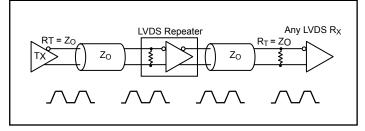

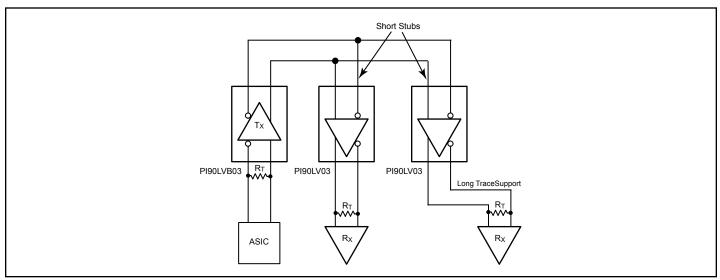

The LVDS Repeaters take an LVDS input signal and provide an LVDS output to address various interface logic requirements such as signal isolation, repeater, stub length, and Optical Transceiver Modules. In many large systems, signals are distributed across backplanes, and the distance between the transmission line and the unterminated receivers are one of the limiting factors for system speed. The buffers can be used to reduce the 'stub length' by strategic device placement along the trace length. They can improve system performance by allowing the receiver to be placed very close to the main transmission line or very close to the connector on the card. Longer traces to the LVDS receiver can then be placed after the buffer.

The buffer's wide input dynamic range enables them to receive differential signals from LVPECL and LVDS sources. The devices can be used as compact high-speed serial translators between LVPECL and LVDS data lines. The differential translation provides a simple way to mix and match Optical Transceiver ICs from various vendors without redesigning the interfaces.

## Applications

The PI90LV03 and PI90LVB03 provide differential translation between LVDS and PECL devices for high-speed, point-to-point interface and telecom applications:

- -ATM

- SONET/SDH

- Switches

- Routers

- Add-Drop Multiplexers

### **High-Speed Differential Cable Repeater Application**

### Absolute Maximum Ratings Over Operating Free-Air Temperature (unless otherwise noted)<sup>(2)</sup>

| Supply Voltage Range, V <sub>CC</sub> <sup>(1)</sup>         | ).5V to 4V            |

|--------------------------------------------------------------|-----------------------|

| Voltage Range (A, B, or R <sub>OUT</sub> )0.5 to V           | / <sub>CC</sub> +0.5V |

| ESD rating (HBIN, 1.5kΩ, 100pF)                              | ······ ≥2KV           |

| Storage Temperature Range65°C                                | C to 150°C            |

| Lead Temperature 1.6 mm (1/16 inch) from case for 10 seconds | 250°C                 |

|                                                              |                       |

#### Notes:

- 1. All voltage values, except differential I/O bus voltages, are with respect to ground terminal.

- Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to Absolute-Maximum-Rated conditions for extended periods may affect device reliability.

Figure 2. Backplance Stub-Hider Application

### **Dissipation Rating Table**

| Package          | T <sub>A</sub> ≤25°C Power Rating | <b>Derating Factor Above T<sub>A</sub> = 25°C</b> | T <sub>A</sub> = 85°C Power Rating |

|------------------|-----------------------------------|---------------------------------------------------|------------------------------------|

| 6-pin SOT-23 (T) | 385mW                             | 3.1mW/°C                                          | 200mW                              |

#### Notes:

1. This is the inverse of the junction-to-ambient thermal vsistance when board-mounted (low-K) and with no air flow.

# **Recommended Operating Conditions**

| Symbol          | Paramters                                 | Min. | Тур. | Max.                              | Units |

|-----------------|-------------------------------------------|------|------|-----------------------------------|-------|

| V <sub>CC</sub> | Supply Voltage                            | 3.0  | 3.3  | 3.6                               |       |

| V <sub>ID</sub> | Magnitude of differential Voltage         | 0.1  |      | 0.6                               | V     |

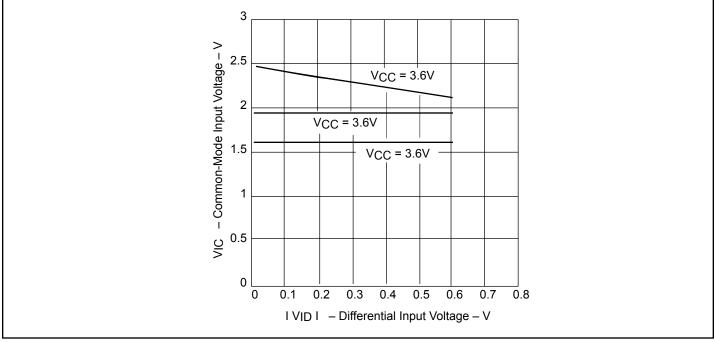

| V <sub>IC</sub> | Common-Mode Intput Voltage <sup>(6)</sup> | 0    |      | $2.0 - \frac{ V_{\text{ID}} }{2}$ | Y     |

| T <sub>A</sub>  | Operating Free-air Temperature            | -40  |      | 85                                | °C    |

# Common-Mode Input Voltage vs. Differenital Input Voltage

Figure 3.  $V_{IC}$  vs.  $V_{ID}$  and  $V_{CC}$

#### Note:

1. All typical values are at 25°C and with a 3.3V supply.

| Symbol                        | Parameter                                                                   | Test Condition                                                 | 1                               | Min.  | Typ. <sup>(1)</sup> | Max.  | Units |

|-------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------|-------|---------------------|-------|-------|

| V <sub>ITH+</sub>             | Positive-going differential input voltage threshold                         | See Grunne 2 and 4 and table 1                                 |                                 |       |                     | 50    | mV    |

| V <sub>ITH-</sub>             | Negative-going differential input voltage threshold                         | See figures 5 and 4 and ta                                     | See figures 3 and 4 and table 1 |       |                     |       | mV    |

| T.                            | Input Current (A or B inputs)                                               | V <sub>I</sub> - 0V                                            |                                 |       |                     | ±20   |       |

| II                            | input Current (A or B inputs)                                               | $V_{\rm I} = 2.4 V \text{ or } V_{\rm CC} - 0.8$               |                                 | -1.2  |                     |       | μA    |

| I <sub>ID</sub>               | High-level input current ( $I_{IA}$ - $I_{IB}$ )                            | $V_{IA} = 0V, V_{IB} = 0.1V$<br>$V_{IA} = 2.4V, V_{IB} = 2.3V$ |                                 |       |                     | ±2    | μΑ    |

| V <sub>OD</sub>               | Differential output voltage magnitude                                       | $R_{\rm L} = 100\Omega ({\rm LV03});$                          |                                 | 247   | 350                 | 454   |       |

| $\Delta   V_{OD}  $           | Change in differential output voltage magnitude                             | $R_L = 50\Omega (LVB03);$<br>See Figure 4                      |                                 | -50   |                     | 50    | mV    |

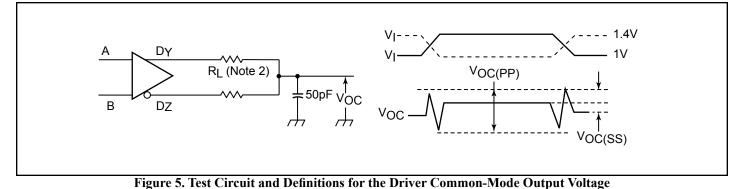

| V <sub>OC(SS)</sub>           | Steady-State common-mode output voltage                                     | See Figure 5                                                   |                                 | 1.125 |                     | 1.375 | V     |

| $\Delta V_{OC(SS)}$           | Change in Steady-State common-mode out-<br>put voltage between logic states |                                                                |                                 | -50   |                     | 50    | mV    |

| V <sub>OC(PP)</sub>           | Peak-to-peak common-mode output voltage                                     |                                                                |                                 |       | 25                  | 100   |       |

|                               |                                                                             | $V_I = 0V$ or $V_{CC}$ No load                                 |                                 |       | 7                   | 9     |       |

| I <sub>CC</sub>               | Supply Current                                                              | $V_{\rm I} = 0$ V or $V_{\rm CC}$ , $R_{\rm L} = 100$          | Ω (LV03)                        |       | 9.5                 | 12.5  |       |

|                               |                                                                             | $V_{\rm I} = 0$ V or $V_{\rm CC}$ , $R_{\rm L} = 500$          | 2 (LVB03)                       |       | 18                  | 25    |       |

|                               |                                                                             | $V_{OY}$ or $V_{OZ} = 0V$                                      | LV03                            |       | 3                   | 10    | mA    |

| I <sub>OS</sub> Short-circuit |                                                                             |                                                                | LVB03                           |       | 6                   | 20    |       |

|                               | Short-circuit output current                                                | $V_{OD} = 0V$                                                  | LV03                            |       |                     | 10    |       |

|                               |                                                                             |                                                                | LVB03                           |       |                     | 20    |       |

| I <sub>O(OFF)</sub>           | Power-off output current                                                    | $V_{\rm CC} = 0V, V_{\rm O} = 3.6V$                            |                                 |       |                     | ±1    | μΑ    |

| CI                            | Input load capacitance                                                      |                                                                |                                 |       | 3                   |       | pF    |

# Electrical Characteristics over Recommended Operating Conditions (unless otherwise noted).

### Receiver Switching Characteristics over Recommended Operating Conditions (unless otherwise noted)

| Symbol             | Parameter                                    | Test Conditions                         | Min. | Тур. | Max. | Units |

|--------------------|----------------------------------------------|-----------------------------------------|------|------|------|-------|

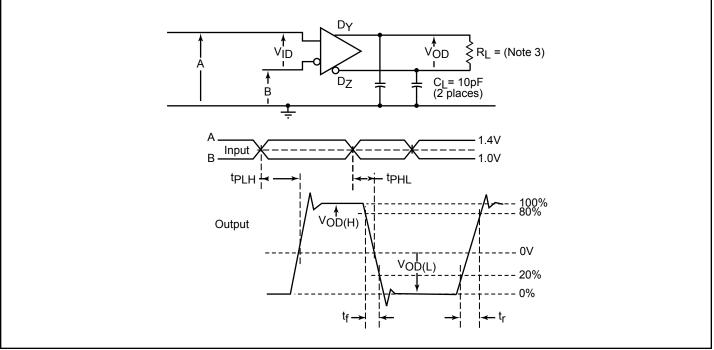

| t <sub>PLH</sub>   | Propagation delay, low to high level outputs |                                         |      | 1.4  | 6    |       |

| t <sub>PHL</sub>   | Propagation delay, high to low level outputs | 1                                       |      | 1.4  | 6    |       |

| t <sub>R</sub>     | Output signal rise time                      | LV03 $R_L = 100\Omega$ ,                |      | 0.5  | 1    | ns    |

| t <sub>F</sub>     | Output signal fall time                      | LVB03 $R_L = 50\Omega;$<br>$C_L = 10pF$ |      | 0.5  | 1    |       |

| t <sub>sk(p)</sub> | Pulse skew ( $  t_{PHL} - t_{PLH}   )^{(2)}$ | See Figure 6                            |      | 50   |      | ps    |

| t <sub>skpp</sub>  | Part-to-part skew                            |                                         |      | 1.5  |      | ns    |

| f <sub>max</sub>   | Maximum throughtput data rate <sup>(3)</sup> |                                         |      | 660  |      | mbps  |

Notes:

1. All typical values are at 25°C and with a 3.3V supply

2.  $t_{sk(p)}$  is the magnitude of the time difference between the high-to-low and low-to-high propagation delay times at an output.

3.  $f_{max}$  generator input conditions: 50% duty cycle, 200mV, Output criteteria: 45% to 55% duty cycle,  $V_{OD} \ge 250mV$

## **Parameter Measurement Information**

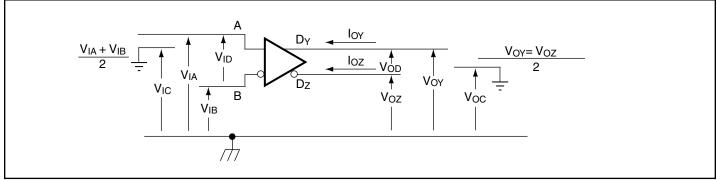

**Figure 4. Voltage Definitions**

### Table 1. Receiver Minimum and Maximum Input Threshold Test Voltages

| Applied V | oltages (V)     | Resulting Differenital Input Votlages (mV) | Resulting Common-Mode Input Voltages (V) |

|-----------|-----------------|--------------------------------------------|------------------------------------------|

| VIA       | V <sub>IB</sub> | V <sub>ID</sub>                            | V <sub>IC</sub>                          |

| 1.25      | 1.20            | 50                                         | 1.2                                      |

| 1.15      | 1.20            | -50                                        | 1.2                                      |

| 2.4       | 2.35            | 50                                         | 2.35                                     |

| 2.3       | 2.35            | -50                                        | 2.35                                     |

| 0.05      | 0               | 50                                         | 0.05                                     |

| 0         | 0.05            | -50                                        | 0.05                                     |

| 1.5       | 0.9             | 600                                        | 1.2                                      |

| 0.9       | 1.5             | -600                                       | 1.2                                      |

| 2.4       | 1.8             | 600                                        | 2.1                                      |

| 1.8       | 2.4             | -600                                       | 2.1                                      |

| 0.6       | 0               | 600                                        | 0.3                                      |

| 0         | 0.6             | -600                                       | 0.3                                      |

#### Notes:

- 1. All input pulses are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$ ns, Pulse Repetition Rate (PPR) = 0.5 Mpps, pulse width = 500 ±10ns.  $C_L$  includes instrumentation and fixture capacitance within 0.06m of the D.U.T. The test measurement of  $V_{OC(PP)}$  is made on test equipment with a –3dB bandwidth of at least 300MHz.

- 2.  $R_L = 49.9\Omega \pm 1\%$  for PI90LV03 or 24.9 $\Omega \pm 1\%$  for PI90LVB03.

- 3. To verify output max signaling rate , the output signal transition time  $(t_r/t_f)$  should not exceed 0.76ns.

#### **Figure 6. Test Circuit and Definitions**

#### Notes:

- $1. \quad \text{All input pulses are supplied by a generator having the following characteristics: } t_r \text{ or } t_f \leq 1 \text{ns}, \text{Pulse Repetition Rate}$

- (PPR) = 50 Mpps, pulse width = 10 ±0.2ns. C<sub>L</sub> includes instrumentation and fixture capacitance within 0.06m of the D.U.T.

- 2. This point is 1.4V with  $V_{CC} = 3.3V$  or 1.2V with  $V_{CC} = 2.7V$ .

- 3.  $R_L = 100\Omega \pm 1\%$  for PI90LV03 or  $50\Omega \pm 1\%$  for PI90LVB03.

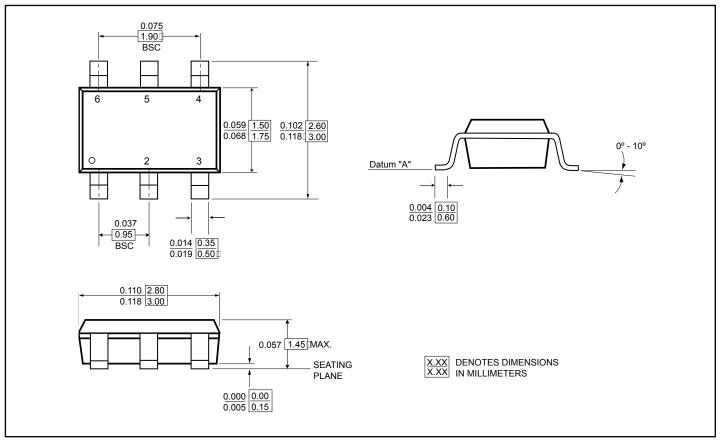

# Packaging Mechanical: 6-Pin SOT (T)

# **Ordering Information**

| Ordering Code | Package Code | Package Description           | Top Marking |

|---------------|--------------|-------------------------------|-------------|

| PI90LV03TX    | Т            | 6-pin SOT-23                  | L9          |

| PI90LV03TEX   | Т            | Pb-free & Green, 6-pin SOT-23 | LC          |

| PI90LVB03TX   | Т            | 6-pin SOT-23                  | LA          |

| PI90LVB03TEX  | Т            | Pb-free & Green, 6-pin SOT-23 | LD          |

Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. X = Tape and reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com