## STLVDS31B

## High speed differential line drivers

### **Features**

- Meets or exceeds the requirements of ANSI TIA/EIA-644 standard

- Low voltage differential signaling with typical output voltage of 350 mV and a 100  $\Omega$  load

- Typical output voltage rise and fall times of 750 ps (400 Mbps)

- Typical propagation delay times of 1.7 ns

- Operates from a single 3.3 V supply

- Power dissipation 25 mW typical per driver at 200 MHz

- $\blacksquare$  Driver at high impedance when disabled or with  $V_{CC}=0\ V$

- Pin compatible with the AM26LS31, SN65LVDS31

- Low voltage TTL (LVTTL) logic input levels

## **Description**

The STLVDS31B is a quad differential line drivers that implements the electrical characteristics of low voltage differential signaling (LVDS). This signaling technique lowers the output voltage levels of 5 V differential standard levels (such as TIA/EIA-422B) to reduce the power, increase the switching speeds and allows operations with a 3.3 V supply rail. Any of the four current mode drivers will deliver a minimum differential output voltage magnitude of 247 mV into a 100  $\Omega$  load when enabled.

The intended application of this device and signalling technique is for point-to-point baseband data transmission over controlled impedancemedia approximately 100  $\Omega$ . The

transmission media may be printed circuit board traces, backplanes or cables. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and noise coupling to the environment.

The STLVDS31B is characterized for operation from - 55 °C to 125 °C.

Table 1. Device summary

| Order code  | Temperature range | Package                 | Packaging           |

|-------------|-------------------|-------------------------|---------------------|

| STLVDS31BTR | - 40 to 85 °C     | TSSOP16 (tape and reel) | 2500 parts per reel |

July 2009 Doc ID 8338 Rev 6 1/15

Contents STLVDS31B

## **Contents**

| 1 | Pin configuration 3                 |

|---|-------------------------------------|

| 2 | Maximum ratings 5                   |

| 3 | Electrical characteristics 6        |

| 4 | Typical characteristics 8           |

| 5 | Typical performance characteristics |

| 6 | Package mechanical data11           |

| 7 | Revision history                    |

STLVDS31B Pin configuration

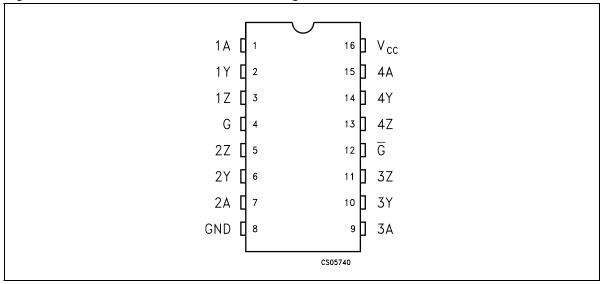

# 1 Pin configuration

Figure 1. Pin connections and functional diagram

Table 2. Pin description

| Pin n°       | Symbol          | Name and function |

|--------------|-----------------|-------------------|

| 1, 7, 9, 15  | 1A to 4A        | Driver inputs     |

| 2, 6, 10, 14 | 1Y to 4Y        | Driver outputs    |

| 3, 5, 11, 13 | 1Z to 4Z        | Driver outputs    |

| 4            | G               | Enable            |

| 12           | G               | Enable            |

| 8            | GND             | Ground            |

| 16           | V <sub>CC</sub> | Supply voltage    |

Pin configuration STLVDS31B

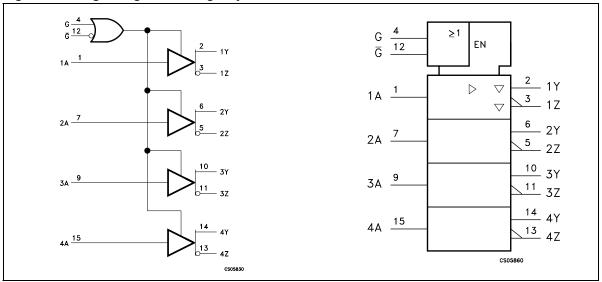

Figure 2. Logic diagram and logic symbol

Table 3. Truth table for receiver

| $V_{ID} = V_A - V_B$                | R |

|-------------------------------------|---|

| V <sub>ID</sub> ≥ 100 mV            | Н |

| - 100 mV < V <sub>ID</sub> < 100 mV | ? |

| $V_{ID} \le -100 \text{ mV}$        | L |

| OPEN                                | Н |

Table 4. Truth table

| Input | Ena | bles | Out | puts |

|-------|-----|------|-----|------|

| А     | G   | G    | Υ   | z    |

| Н     | Н   | Х    | Н   | L    |

| L     | Н   | Х    | L   | Н    |

| Н     | Х   | L    | Н   | L    |

| L     | Х   | L    | L   | Н    |

| Х     | L   | Н    | Z   | Z    |

| OPEN  | Н   | Х    | L   | Н    |

| OPEN  | Х   | L    | L   | Н    |

L = Low level, H = High Level, X = Don't care, Z = High Impedance

4/15 Doc ID 8338 Rev 6

STLVDS31B Maximum ratings

# 2 Maximum ratings

Table 5. Absolute maximum ratings

| Symbol           | Parameter                     | Value                           | Unit |

|------------------|-------------------------------|---------------------------------|------|

| V <sub>CC</sub>  | Supply voltage <sup>(1)</sup> | -0.5 to 4.6                     | V    |

| VI               | DC input voltage              | -0.5 to (V <sub>CC</sub> + 0.5) | V    |

| T <sub>STG</sub> | Storage temperature range     | -65 to +150                     | °C   |

<sup>1.</sup> All voltages except differential I/O bus voltage, are with respect to the network ground terminal.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

Table 6. Recommended operating conditions

| Symbol           | Parameter                   | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------|------|------|------|------|

| V <sub>CC</sub>  | Supply voltage              | 3.0  | 3.3  | 3.6  | V    |

| V <sub>IH</sub>  | HIGH level input voltage    | 2.0  |      |      | V    |

| V <sub>ILI</sub> | LOW level input voltage     |      |      | 0.8  | V    |

| T <sub>A</sub>   | Operating temperature range | -40  |      | 85   | °C   |

Electrical characteristics STLVDS31B

## 3 Electrical characteristics

Over recommended operating conditions unless otherwise noted. All typical values are at T\_A = 25  $^{\circ}C,$  and V\_CC = 3.3 V.

Table 7. Electrical characteristics

| Symbol              | Parameter                                                             | Test condition                                    | Min.  | Тур. | Max.  | Unit |

|---------------------|-----------------------------------------------------------------------|---------------------------------------------------|-------|------|-------|------|

| V <sub>OD</sub>     | Differential output voltage                                           |                                                   | 247   | 350  | 454   | mV   |

| $\Delta V_{OD}$     | Change in differential output voltage between logic state             | $R_L = 100\Omega$ , Figure 2                      | -50   |      | 50    | mV   |

| $\Delta V_{OC(SS)}$ | Change in steady-state common mode output voltage between logic state | Figure 3                                          | 1.125 | 1.2  | 1.375 | ٧    |

| V <sub>OC(SS)</sub> | Steady-state common mode output voltage                               | Figure 3                                          | -50   |      | 50    | mV   |

| V <sub>OC(PP)</sub> | Peak to peak common mode output voltage                               |                                                   |       | 80   | 150   | mV   |

|                     |                                                                       | V <sub>IN</sub> = 0.8V or 2V, Enabled, No Load    |       | 11.5 | 20    | mA   |

| $I_{CC}$            | Supply current                                                        | $V_{IN} = 0.8V$ or 2V, Enabled, $R_L = 100\Omega$ |       | 25   | 35    | mA   |

|                     |                                                                       | V <sub>IN</sub> = 0 or V <sub>CC</sub> , Disabled |       | 0.3  | 1     | mA   |

| I <sub>IH</sub>     | High level input current                                              | V <sub>IH</sub> = 2V                              |       | 4    | 20    | μΑ   |

| I <sub>IL</sub>     | Low level input current                                               | V <sub>IL</sub> = 0.8V                            |       | 0.6  | 10    | μΑ   |

| 1                   | Short circuit output current                                          | $V_{O(Y)}$ or $V_{O(Z)} = 0V$                     |       | 6.1  | - 24  | mA   |

| I <sub>SC</sub>     | Short circuit output current                                          | V <sub>OD</sub> = 0                               |       |      | ± 12  | mA   |

| I <sub>OZ</sub>     | High impedance output current                                         | V <sub>O</sub> = 0 or 2.4V                        |       |      | ± 1   | μΑ   |

| I <sub>CS</sub>     | Cold spare leakage current                                            | $V_{I} = 3.6V, V_{DD} = 0V$                       |       |      | ± 20  | μΑ   |

| I <sub>OFF</sub>    | Power OFF output current                                              | $V_{CC} = 0, V_{O} = 2.4V$                        |       |      | ± 1   | μΑ   |

| C <sub>IN</sub>     | Input capacitance                                                     |                                                   |       | 3    |       | pF   |

6/15 Doc ID 8338 Rev 6

Over recommended operating conditions unless otherwise noted. All typical values are at  $T_A$  = 25  $^{\circ}C,$  and  $V_{CC}$  = 3.3 V.

Table 8. Switching characteristics (1)

| Symbol             | Parameter                                                   | Test condition                | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------------------------------------------|-------------------------------|------|------|------|------|

| t <sub>PLH</sub>   | Propagation delay time, low to high output                  |                               | 0.5  | 1.4  | 2    | ns   |

| t <sub>PHL</sub>   | Propagation delay time, high to low output                  | $R_1 = 100\Omega, C_1 = 10pF$ | 1    | 1.7  | 2.5  | ns   |

| t <sub>r</sub>     | Differential output signal rise time                        | Figure 2                      | 0.4  | 0.5  | 0.6  | ns   |

| t <sub>f</sub>     | Differential output signal fall time                        |                               | 0.4  | 0.5  | 0.6  | ns   |

| t <sub>sk(P)</sub> | Pulse skew (It <sub>THL</sub> = t <sub>TLH</sub> I)         |                               |      | 0.3  | 0.6  | ns   |

| t <sub>sk(O)</sub> | Channel to channel output skew (2)                          |                               |      | 0    | 0.3  | ns   |

| t <sub>PZH</sub>   | Propagation delay time, high impedance to high level output |                               |      | 5.4  | 15   | ns   |

| t <sub>PZL</sub>   | Propagation delay time, high impedance to low level output  | Figure 4                      |      | 2.5  | 15   | ns   |

| t <sub>PHZ</sub>   | Propagation delay time, high level to high impedance output | Trigule 4                     |      | 8.1  | 15   | ns   |

| t <sub>PLZ</sub>   | Propagation delay time, low level to high impedance output  |                               |      | 7.3  | 15   | ns   |

<sup>1.</sup> RS-232 IN to TTL-CMOS OUT (from 50 % to 50 %).

<sup>2.</sup>  $t_{sk(O)}$  is the maximum delay time difference between drivers on the same device.

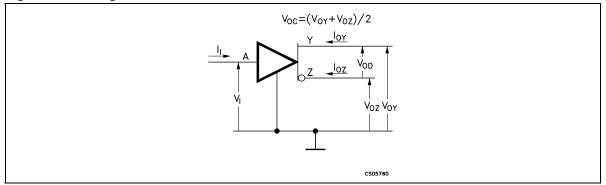

# 4 Typical characteristics

Figure 3. Voltage and current definitions

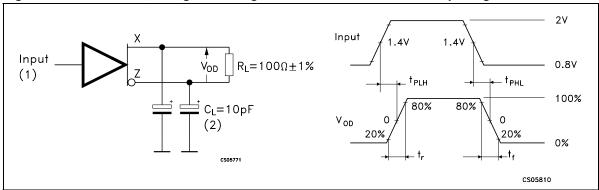

Figure 4. Test circuit, timing and voltage definitions for differential output signal

- 1. All input pulse are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width =  $10 \pm 0.2$  ns.

- 2. C<sub>L</sub> includes instrumentation and fixture capacitance within 6 mm. of the D.U.T.

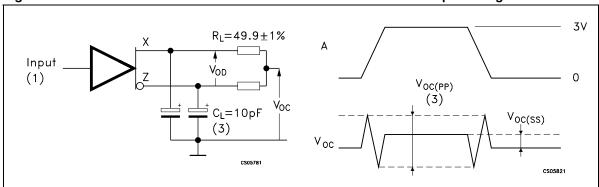

Figure 5. Test circuit and definitions for the driver common mode output voltage

- 1. All input pulse are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 50 Mpps, pulse width =  $10 \pm 0.2$  ns.

- 2.  $C_L$  includes instrumentation and fixture capacitance within 6mm of the D.U.T

- 3. The measurement of  $V_{OC(PP)}$  is made on test equipment with a -3 dB bandwidth of at least 300 MHz.

**\_\_\_\_\_**

8/15 Doc ID 8338 Rev 6

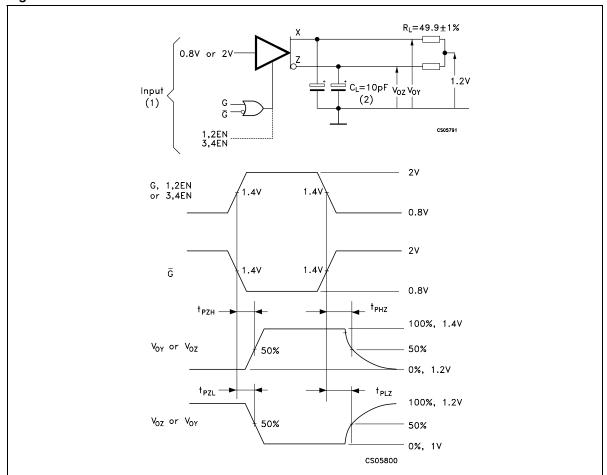

Figure 6. Enable and disable time test circuit and waveform

- 1. All input pulse are supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 1$  ns, pulse repetition rate (PRR) = 0.5 Mpps, pulse width =  $500 \pm 10$  ms.

- 2.  $\,$  C $_{L}$  includes instrumentation and fixture capacitance within 6 mm. of the D.U.T.

# 5 Typical performance characteristics

Unless otherwise specified  $T_J = 25$  °C

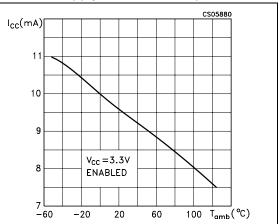

Figure 7. Supply current vs. temperature

0.28 0.27 0.26 0.25 V<sub>CC</sub> = 3.3V DISABLED 0.24 -60 -20 20 60 100 T<sub>amb</sub>(°C)

Figure 8. Supply current vs. temperature

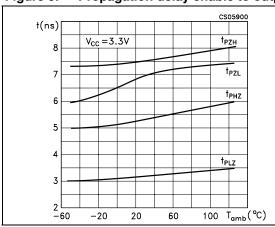

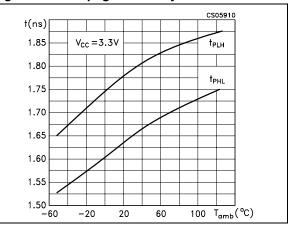

Figure 9. Propagation delay enable to output Figure 10. Propagation delay time

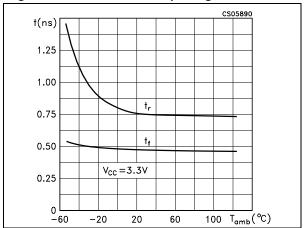

Figure 11. Differential output signal

10/15 Doc ID 8338 Rev 6

47

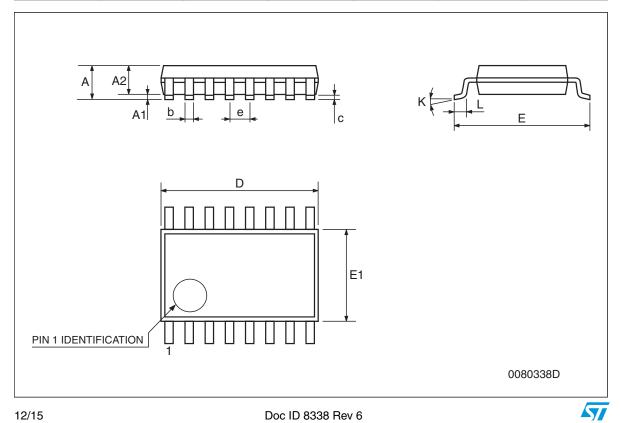

# 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

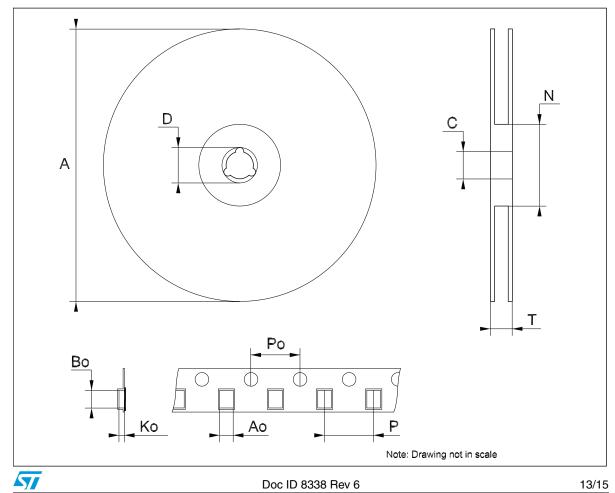

### TSSOP16 mechanical data

| Dim.   |      | mm.      |      |       |            |        |

|--------|------|----------|------|-------|------------|--------|

| Dilli. | Min. | Тур.     | Max. | Min.  | Тур.       | Max.   |

| А      |      |          | 1.2  |       |            | 0.047  |

| A1     | 0.05 |          | 0.15 | 0.002 | 0.004      | 0.006  |

| A2     | 0.8  | 1        | 1.05 | 0.031 | 0.039      | 0.041  |

| b      | 0.19 |          | 0.30 | 0.007 |            | 0.012  |

| С      | 0.09 |          | 0.20 | 0.004 |            | 0.0079 |

| D      | 4.9  | 5        | 5.1  | 0.193 | 0.197      | 0.201  |

| Е      | 6.2  | 6.4      | 6.6  | 0.244 | 0.252      | 0.260  |

| E1     | 4.3  | 4.4      | 4.48 | 0.169 | 0.173      | 0.176  |

| е      |      | 0.65 BSC |      |       | 0.0256 BSC |        |

| К      | 0°   |          | 8°   | 0°    |            | 8°     |

| L      | 0.45 | 0.60     | 0.75 | 0.018 | 0.024      | 0.030  |

| Tape & reel | TSSOP16 | mechanical | data |

|-------------|---------|------------|------|

|-------------|---------|------------|------|

| Di   | mm.  |      |      | inch. |      |        |

|------|------|------|------|-------|------|--------|

| Dim. | Min. | Тур. | Max. | Min.  | Тур. | Max.   |

| А    |      |      | 330  |       |      | 12.992 |

| С    | 12.8 |      | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |      |      | 0.795 |      |        |

| N    | 60   |      |      | 2.362 |      |        |

| Т    |      |      | 22.4 |       |      | 0.882  |

| Ao   | 6.7  |      | 6.9  | 0.264 |      | 0.272  |

| Во   | 5.3  |      | 5.5  | 0.209 |      | 0.217  |

| Ko   | 1.6  |      | 1.8  | 0.063 |      | 0.071  |

| Ро   | 3.9  |      | 4.1  | 0.153 |      | 0.161  |

| Р    | 7.9  |      | 8.1  | 0.311 |      | 0.319  |

Revision history STLVDS31B

# 7 Revision history

Table 9. Document revision history

| Date        | Revision | Changes                       |

|-------------|----------|-------------------------------|

| 28-Mar-2006 | 5        | Order codes updated.          |

| 15-Jul-2009 | 6        | Modified: Features on page 1. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 8338 Rev 6

15/15