#### Features

- Fibre Channel compliant

- IBM ESCON<sup>™</sup> compliant

- OLC Compatible system interface

- 8B/10B-coded or 10-bit unencoded

- 160- to 330-Mbps data rate

- No external PLL components

- Dual ECL 100K serial inputs

- Low power: 650 mW

- Compatible with fiberoptic modules, coaxial cable, and twisted pair media

- Built-In Self-Test

- 28-pin SOIC/PLCC

#### **Functional Description**

The CY7B9331 HOTLink OLC Receiver is a point-to-point communications building block that receives data over high-speed serial links (fiber, coax, and twisted pair) at 160 to

# HOTLink<sup>™</sup> OLC Receiver

330 Mbits/second. The HOTLink OLC Receiver system interface has been tailored to match OLC (Optical Link Card) timing and functionality.

The HOTLink receiver accepts the serial bit stream at its differential line receiver inputs and, using a completely integrated PLL clock synchronizer, recovers the timing information necessary for data reconstruction.

The bit stream is deserialized, decoded, and checked for transmission errors. The recovered byte is presented in parallel to the receiving host along with a byte rate clock.

The 8B/10B encoder/decoder can be disabled in systems that already encode or scramble the transmitted data. A Built-In Self-Test pattern generator and checker allows testing of the transmitter, receiver, and the connecting link as a part of a system diagnostic check.

The CY7B9331 HOTLink Receiver is a companion part to the CY7B923 HOTLink Transmitter. The HOTLink chip set provides a complete physical interface solution. For further information on HOTLink Transceiver and Receiver functions see the CY7B923/933 datasheet.

ESCON is a registered trademark of IBM.

April 1994

408-943-2600

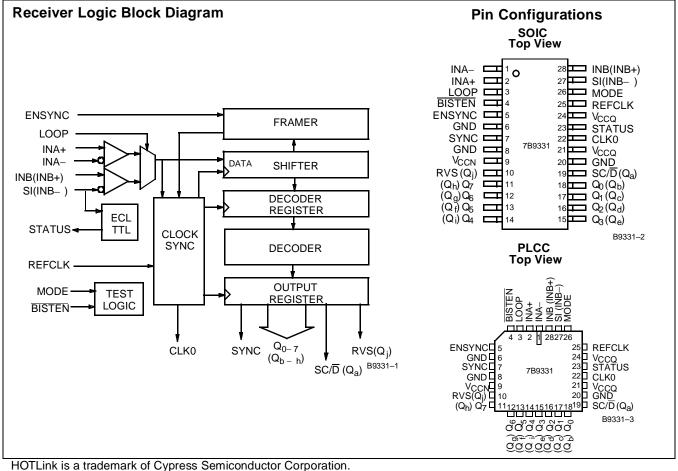

#### CY7B9331 HOTLink Receiver Pin Description

| Name                                       | I/O                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q <sub>0 -7</sub><br>(Q <sub>b - h</sub> ) | TTL Out              | $Q_{0-7}$ Parallel Data Output. $Q_{0-7}$ contain the most recently received data. These outputs change synchronously with Clk0. When MODE is HIGH, $Q_{0, 1,7}$ become $Q_{b, c,h}$ respectively.                                                                                                                                                                                                                                                                                                                                                                   |

| SC/D(Q <sub>a</sub> )                      | TTL Out              | Special Character/Data Select. SC/ $\overline{D}$ indicates the context of received data. HIGH indicates a Control (Special Character) code, LOW indicates a Data character. When MODE is HIGH, SC/ $\overline{D}$ acts as $Q_a$ output.                                                                                                                                                                                                                                                                                                                             |

| RVS (Q <sub>j</sub> )                      | TTL Out              | Received Violation Symbol. A HIGH on RVS indicates that a code rule violation has been detected in the received data stream. A LOW shows that no error has been detected. In BIST mode, a LOW on RVS indicates correct operation of the transmitter, receiver, and link on a byte-by-byte basis. When MODE is HIGH, RVS acts as $Q_j$ output.                                                                                                                                                                                                                        |

| SYNC                                       | TTL Out              | In Encoded mode, SYNC asserted HIGH indicates that new data has been received and is ready to be delivered. SYNC asserted LOW shows that the received data is the Null character (normally inserted by the transmitter as a pad between data inputs). In Bypass mode, SYNC stays LOW except to indicate a K28.5 character when the framer is enabled (ENSYNC HIGH). In BIST mode, SYNC will remain HIGH for all but the last byte of a test loop and will pulse LOW one byte time per BIST loop.                                                                     |

| CLK0                                       | TTL Out              | Recovered Byte Clock. This byte rate clock output is phase and frequency aligned to the incoming serial data stream. SYNC, $Q_{0-7}$ , SC/ $\overline{D}$ , and RVS all switch synchronously with the rising edge of this output.                                                                                                                                                                                                                                                                                                                                    |

| LOOP                                       | ECL in               | Serial Data Input Select. This ECL 100K (+5V referenced) input selects INB or INA as the active data input. If LOOP is HIGH, INB is connected to the shifter and signals connected to INB will be decoded. If LOOP is LOW INA is selected.                                                                                                                                                                                                                                                                                                                           |

| INA±                                       | Diff In              | Serial Data Input A. The differential signal at the receiver end of the communication link may be connected to the differential input pairs INA $\pm$ or INB $\pm$ . Either the INA pair or the INB pair can be used as the main data input and the other can be used as a loopback channel or as an alternative data input selected by the state of LOOP.                                                                                                                                                                                                           |

| INB<br>(INB+)                              | ECL in<br>(Diff In ) | Serial Data Input B. This pin is either a single-ended ECL data receiver (INB) or half of the INB of the differential pair. If STATUS is wired to $V_{CC}$ , then INB $\pm$ can be used as differential line receiver inter-changeably with INA $\pm$ . If STATUS is normally connected and loaded, INB becomes a single-ended ECL 100K (+5V referenced) serial data input. INB is used as the test clock while in Test mode.                                                                                                                                        |

| SI<br>(INB–)                               | ECL in<br>(Diff In)  | Status Input. This pin is either a single-ended ECL status monitor input (SI) or half of the INB of the differential pair. If STATUS is wired to $V_{CC}$ , then INB $\pm$ can be used as differential line receiver inter-changeably with INA $\pm$ . If STATUS is normally connected and loaded, SI becomes a single-ended ECL 100K (+5V referenced) status monitor input.                                                                                                                                                                                         |

| STATUS                                     | TTL Out              | Status Out. Status is the inverted TTL-translated output of SI. It is typically used to translate the Carrier Detect output from a fiberoptic receiver. When this pin is normally connected and loaded (without any external pull-up resistor), STATUS will assume the negative logical level of SI and INB will become a single-ended ECL serial data input. If the status monitor translation is not desired, then STATUS may be wired to $V_{CC}$ and the INB± pair may be used as a differential serial data input.                                              |

| ENSYNC                                     | TTL In               | Reframe Enable. ENSYNC controls the Framer logic in the receiver. When ENSYNC is held HIGH, each SYNC (K28.5) symbol detected in the shifter will frame the data that follows. When ENSYNC is held LOW, the reframing logic is disabled. The incoming data stream is then continuously deserialized and decoded using byte boundaries set by the internal byte counter. Bit errors in the data stream will not cause alias SYNC characters to reframe the data erroneously.                                                                                          |

| REFCLK                                     | TTL In               | Reference Clock. REFCLK is the clock frequency reference for the clock/data synchronizing PLL.<br>REFCLK sets the approximate center frequency for the internal PLL to track the incoming bit stream.<br>REFCLK must be connected to a crystal-controlled time base that runs within the frequency limits of<br>the Tx/Rx pair, and the frequency must be the same as the transmitter CKW frequency (within<br>CKW±0.1%).                                                                                                                                            |

| MODE                                       | 3-Level In           | Decoder Mode Select. The level on the MODE pin determines the decoding method to be used. When wired to GND (Encoded Mode), MODE selects 8B/10B decoding. When wired to V <sub>CC</sub> (Bypass MODE), registered shifter contents bypass the decoder and are sent to Q <sub>a-j</sub> directly. When left floating (internal resistors hold the MODE pin at V <sub>CC</sub> /2) the internal bit clock generator is disabled and INB becomes the bit rate test clock to be used for factory test. In typical applications, MODE is wired to V <sub>CC</sub> or GND. |

PRELIMINARY

#### CY7B9331 HOTLink Receiver Pin Description (continued)

| Name             | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BISTEN           | TTL In | Built-In Self-Test Enable. When BISTEN is LOW the receiver awaits a D0.0 (sent once per BIST character and begins a continuous test sequence that tests the functionality of the transmitter, receiver, and the link connecting them. In BIST mode the status of the test can be monitored w Sync and RVS outputs. In normal use BISTEN is held HIGH or wired to $V_{CC}$ . |  |

| V <sub>CCN</sub> |        | Power for output drivers.                                                                                                                                                                                                                                                                                                                                                   |  |

| V <sub>CCQ</sub> |        | Power for internal circuitry.                                                                                                                                                                                                                                                                                                                                               |  |

| GND              |        | Ground                                                                                                                                                                                                                                                                                                                                                                      |  |

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | –65°C to +150°C |

|------------------------------------|-----------------|

| Ambient Temperature with           |                 |

| Power Applied                      | 55°C to +125°C  |

| Supply Voltage to Ground Potential | 0.5V to +7.0V   |

| DC Input Voltage                   | –0.5V to +7.0V  |

| Output Current into TTL Outputs (LOW) 3                      | 0 mA  |

|--------------------------------------------------------------|-------|

| Output Current into ECL outputs (HIGH)5                      | 0 mA  |

| Static Discharge Voltage>2<br>(per MIL-STD-883, Method 3015) | :001V |

| Latch-Up Current>20                                          | 0 mA  |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub> |

|------------|---------------------|-----------------|

| Commercial | 0°C to +70°C        | 5V ± 10%        |

## **Electrical Characteristics**

| Parameter                       | Description                                                 | Test Conditions                         | Min.                   | Max.                   | Unit |

|---------------------------------|-------------------------------------------------------------|-----------------------------------------|------------------------|------------------------|------|

| Receiver T                      | TL-Compatible Pins: Q <sub>0-7</sub> , SC/ <del>D</del> , F | RVS, Sync, Clk0, REFCLK, EnSync, Ē      | BISTEN, Status         | 1                      | 1    |

| V <sub>OHT</sub>                | Output HIGH Voltage                                         | I <sub>OH</sub> = - 2 mA                | 2.4                    |                        | V    |

| V <sub>OLT</sub>                | Output LOW Voltage                                          | I <sub>OL</sub> = 4 mA                  |                        | 0.45                   | V    |

| I <sub>OST</sub>                | Output Short Circuit Current                                | V <sub>OUT</sub> =0V <sup>[1]</sup>     | -15                    | -90                    | mA   |

| V <sub>IHT</sub>                | Input HIGH Voltage                                          |                                         | 2.0                    | V <sub>CC</sub>        | V    |

| V <sub>ILT</sub>                | Input LOW Voltage                                           |                                         | -0.5                   | 0.8                    | V    |

| I <sub>IHT</sub>                | Input HIGH Current                                          | $V_{IN} = V_{CC}$                       | -10                    | +10                    | μΑ   |

| I <sub>ILT</sub>                | Input LOW Current                                           | $V_{IN} = 0.0V$                         |                        | -500                   | μΑ   |

| Receiver E                      | CL-Compatible Input Pins: Loop,                             | SI, INB                                 |                        | I                      |      |

| V <sub>IHE</sub>                | Input HIGH Voltage                                          |                                         | V <sub>CC</sub> -1.165 | V <sub>CC</sub>        | V    |

| V <sub>ILE</sub>                | Input LOW Voltage                                           |                                         | 2.0                    | V <sub>CC</sub> -1.475 | V    |

| I <sub>IHE</sub> <sup>[2]</sup> | Input HIGH Current                                          | V <sub>IN</sub> = V <sub>IHE</sub> Max. |                        | +500                   | μΑ   |

| $I_{ILE}^{[2]}$                 | Input LOW Current                                           | V <sub>IN</sub> = V <sub>ILL</sub> Min. | +0.5                   |                        | μA   |

| Differential                    | Line Receiver Input Pins: INA+, I                           | INA-, INB+, INB-                        |                        |                        |      |

| V <sub>DIFF</sub>               | Input Differential Voltage<br> (IN+) – (IN– )               |                                         | 50                     | 1200                   | mV   |

| V <sub>IHH</sub>                | Highest Input HIGH Voltage                                  |                                         |                        | V <sub>CC</sub>        | V    |

| V <sub>ILL</sub>                | Lowest Input LOW Voltage                                    |                                         | 2.0                    |                        | V    |

| I <sub>IHH</sub>                | Input HIGH Current                                          | V <sub>IN</sub> = V <sub>IHH</sub> Max. |                        | 750                    | μΑ   |

| I <sub>ILL</sub> [3]            | Input LOW Current                                           | V <sub>IN</sub> = V <sub>ILL</sub> Min. | -200                   |                        | μA   |

#### Notes:

Tested one output at a time, output shorted for less than one second, less than 10% duty cycle.

Applies to Loop only.

Input currents are always positive at all voltages above V<sub>CC</sub>/2.

#### Electrical Characteristics (continued)

| Parameter                       | Description                   | Test Conditions | Min. | Max. | Unit |

|---------------------------------|-------------------------------|-----------------|------|------|------|

| Miscellaneous                   |                               |                 | Тур. | Max. |      |

| I <sub>CCR</sub> <sup>[4]</sup> | Receiver Power Supply Current | Freq. = Max     | 130  | 150  | mA   |

## Capacitance<sup>[5]</sup>

| Parameter       | Description       | Test Conditions                                                 | Max. | Unit |

|-----------------|-------------------|-----------------------------------------------------------------|------|------|

| C <sub>IN</sub> | Input Capacitance | $T_A = 25^{\circ}C, f_0 = 1 \text{ MHz}, V_{CC} = 5.0 \text{V}$ | 10   | pF   |

Notes:

Maximum I<sub>CCR</sub> is measured with V<sub>CC</sub>=Max., RF=LOW, and outputs unloaded. Typical I<sub>CCR</sub> is measured with V<sub>CC</sub>=5.0V, T<sub>A</sub>=25°C, RF=LOW, BISTEN=LOW, and outputs unloaded. Tested initially and after any design or process changes that may affect these parameters. 4.

5.

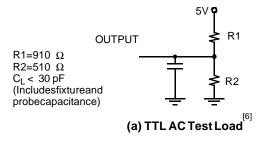

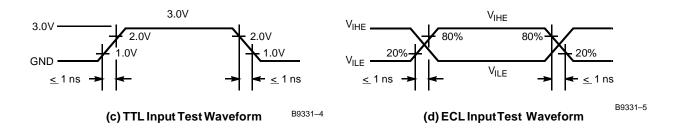

#### AC Test Loads and Waveforms

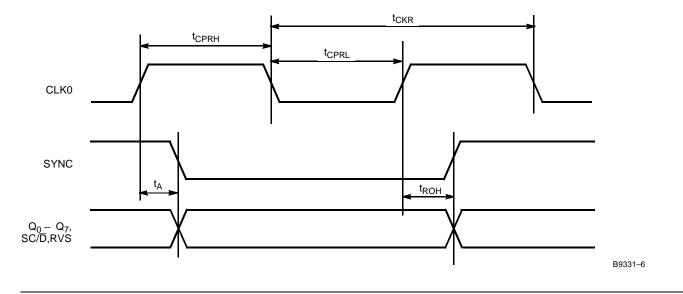

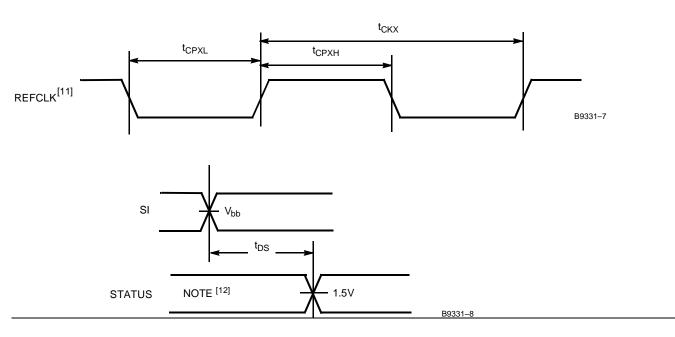

#### Receiver Switching Characteristics Over the Operating Range

|                   |                                                                                | 7B9331             |                    |      |

|-------------------|--------------------------------------------------------------------------------|--------------------|--------------------|------|

| Parameter         | Description                                                                    | Min.               | Max.               | Unit |

| t <sub>CKR</sub>  | Read Clock Period (No Serial Data Input), REFCLK as Reference <sup>[7]</sup>   | -1                 | +1                 | %    |

| t <sub>B</sub>    | Bit Time <sup>[8]</sup>                                                        | 3.03               | 6.25               | ns   |

| t <sub>CPRH</sub> | Read Clock Pulse HIGH                                                          | 5t <sub>B</sub> -3 |                    | ns   |

| t <sub>CPRL</sub> | Read Clock Pulse LOW                                                           | 5t <sub>B</sub> –3 |                    | ns   |

| t <sub>A</sub>    | Data Access Time <sup>[9, 10]</sup>                                            | 2t <sub>B</sub> -3 | 2t <sub>B</sub> +4 | ns   |

| t <sub>ROH</sub>  | Data Hold Time <sup>[9,10]</sup>                                               | 2t <sub>B</sub> -3 |                    | ns   |

| t <sub>CKX</sub>  | REFCLK Clock Period Referenced to CKW of Transmitter (CY7B923) <sup>[11]</sup> | -0.1               | +0.1               | %    |

| t <sub>CPXH</sub> | REFCLK Clock Pulse HIGH                                                        | 6.5                |                    | ns   |

| t <sub>CPXL</sub> | REFCLK Clock Pulse LOW                                                         | 6.5                |                    | ns   |

| t <sub>DS</sub>   | Propagation Delay SI to Status (note ECL and TTL thresholds) <sup>[12]</sup>   |                    | 20                 | ns   |

#### Switching Waveforms for the CY7B9331 HOTLink Receiver

#### Notes:

- Tested initially and after any design or process changes that may affect these parameters, but not 100% tested. The period of t<sub>CKR</sub> will match the period of the transmitter (CY7B923) CKW when the receiver is receiving serial data. When data is interrupted, Clk0 may drift to one of the range limits above. 6. 7.

- 8.

- 9

- 10.

- drift to one of the range limits above. Receiver t<sub>B</sub> is calculated as t<sub>CIN0</sub>/10 if no data is being received, or t<sub>CKW</sub>/10 if data is being received. Data includes Q<sub>0.7</sub>, SC/D, RVS, and Sync. t<sub>A</sub> and t<sub>ROH</sub> specifications are only valid if all outputs (Clk0, Sync, Q<sub>0.7</sub>, SC/D, and RVS) are loaded with similar DC and AC loads. REFCLK has no phase or frequency relationship with Clk0 and only acts as a centering reference to reduce clock synchronization time. REFCLK must be within 0.1% of the transmitter CKW frequency, necessitating a ±500-PPM crystal. The ECL switching threshold is the midpoint between the ECL— V<sub>OH</sub>, and V<sub>OL</sub> specification (approximately V<sub>CC</sub> 1.35V). The TTL switching threshold is 1.5V. 11. 12.

- 1.5V.

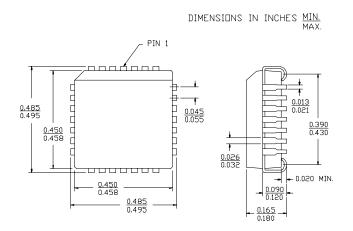

# **Ordering Information**

| Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|-----------------|-------------------------------------|--------------------|

| CY7B9331–JC   | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

| CY7B9331-SC   | S21             | 28-Lead (300-Mil) SOIC              |                    |

Document #: 38-00359

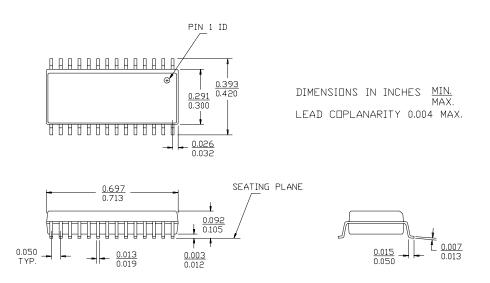

#### **Package Diagrams**

#### 28-Lead Plastic Leaded Chip Carrier J64

#### 28-Lead (300-Mil) Molded SOIC S21

© Cypress Semiconductor Corporation, 1994. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.