# Low Voltage 1:5 Differential LVDS Clock Fanout Buffer

DATA SHEET

The MC100ES8014 is a HSTL differential clock fanout buffer. Designed for the most demanding clock distribution systems, the MC100ES8014 supports various applications that require the distribution of precisely aligned differential clock signals. Using SiGe technology and a fully differential architecture, the device offers very low skew outputs and superior digital signal characteristics. Target applications for this clock driver are in high performance clock distribution in computing, networking and telecommunication systems.

The MC100ES8014 is designed for low skew clock distribution systems and supports clock frequencies up to 400MHz. The device accepts two clock sources. The CLK0 input accepts HSTL compatible signals and CLK1 accepts PECL compatible signals. The selected input signal is distributed to 5 identical, differential HSTL compatible outputs.

# Features

- 1:5 differential clock fanout buffer

- 50 ps maximum device skew

- SiGe Technology

- Supports DC to 400 MHz operation

- 1.5V HSTL compatible differential clock outputs

- PECL and HSTL compatible differential clock inputs

- 3.3V power supply for device core, 1.5V or 1.8V HSTL output supply

- Supports industrial temperature range

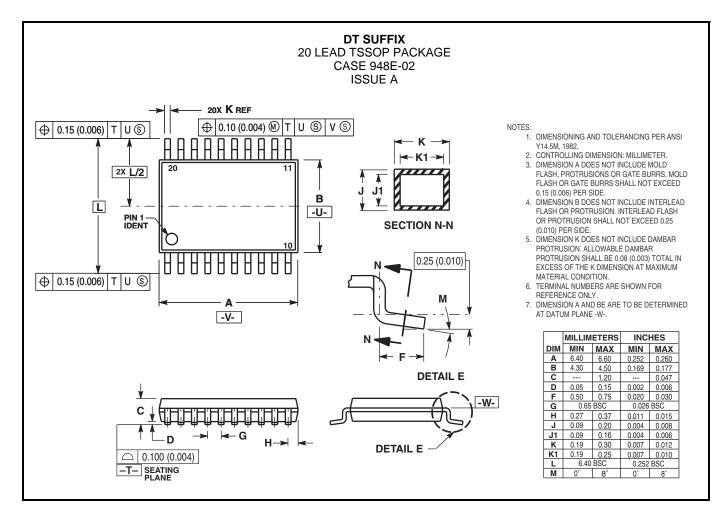

- Standard 20 lead TSSOP package

0 LEAD TSSOP PACKAG CASE 948E

# **ORDERING INFORMATION**

| Device          | Package  |

|-----------------|----------|

| MC100ES8014DT   | TSSOP-20 |

| MC100ES8014DTR2 | TSSOP-20 |

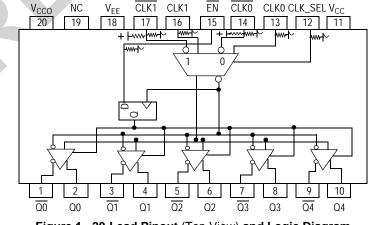

Figure 1. 20-Lead Pinout (Top View) and Logic Diagram

IDT<sup>™</sup> Low Voltage 1:5 Differential LVDS Clock Fanout Buffer

MC100ES8014

# Table 1. Pin Description

| Pin              | Function                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK0, CLK0       | HSTL Data Inputs                                                                                                                                           |

| CLK1, CLK1       | PECL Data Inputs                                                                                                                                           |

| Q[0:4], Q[0:4]   | HSTL Data Outputs                                                                                                                                          |

| CLK_SEL          | LVCMOS Active Clock Select Input                                                                                                                           |

| EN               | LVCMOS Sync Enable                                                                                                                                         |

| V <sub>CC</sub>  | Positive Supply of device core (3.3V)                                                                                                                      |

| V <sub>CCO</sub> | Positive power supply of the HSTL outputs. All VCCO pins must be connected to the positive<br>power supply (1.5V or 1.8V) for correct DC and AC operation. |

| V <sub>EE</sub>  | Negative Supply                                                                                                                                            |

| nc               | no connect                                                                                                                                                 |

# Table 2. Function Table

| Control | Default | 0                                                                                                                                                           | 1                                                                                                                                                               |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_SEL | 0       | CLK0, CLK0 (HSTL) is the active differential clock input                                                                                                    | CLK1, CLK1 (PECL) is the active differential clock input                                                                                                        |

| EN      | 0       | Q[0:4], $\overline{Q[0:4]}$ are active. Deassertion of $\overline{EN}$ can be asynchronous to the reference clock without generation of output runt pulses. | $Q[0:4] = L, \overline{Q[0:4]} = H$ (outputs disabled). Assertion of<br>EN can be asynchronous to the reference clock without generation of output runt pulses. |

# **Table 3. General Specifications**

| Characteristics                                        | Value                              |     |

|--------------------------------------------------------|------------------------------------|-----|

| Internal Input Pulldown Resistor                       | TBD                                |     |

| Internal Input Pullup Resistor                         | TBD                                |     |

| ESD Protection                                         | Human Body Model<br>Machine Model  | TBD |

| $\theta_{JA}$ Thermal Resistance (Junction to Ambient) | 0 LFPM, 8 SOIC<br>500 LFPM, 8 SOIC | TBD |

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

# Table 4. Absolute Maximum Ratings<sup>1</sup>

| Symbol              | Parameter                   | Conditions                            | Rating                                         | Unit     |

|---------------------|-----------------------------|---------------------------------------|------------------------------------------------|----------|

| V <sub>SUPPLY</sub> | Power Supply Voltage        | Difference between $V_{CC} \& V_{EE}$ | 3.9                                            | V        |

| V <sub>IN</sub>     | Input Voltage               | $V_{CC} - V_{EE} \le 3.6V$            | V <sub>CC</sub> + 0.3<br>V <sub>EE</sub> - 0.3 | V<br>V   |

| I <sub>OUT</sub>    | Output Current              | Continuous<br>Surge                   | 50<br>100                                      | mA<br>mA |

| T <sub>A</sub>      | Operating Temperature Range |                                       | -40 to +85                                     | °C       |

| T <sub>STG</sub>    | Storage Temperature Range   |                                       | -65 to +150                                    | °C       |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

IDT<sup>™</sup> Low Voltage 1:5 Differential LVDS Clock Fanout Buffer

| Symbol              | Characteristic                                                           | Min                     | Тур        | Max                     | Unit | Condition                            |

|---------------------|--------------------------------------------------------------------------|-------------------------|------------|-------------------------|------|--------------------------------------|

| HSTL differe        | ntial input signals (CLK0, CLK0)                                         |                         |            |                         |      | ·                                    |

| V <sub>DIF</sub>    | Differential input voltage <sup>2</sup>                                  | 0.2                     |            |                         | V    |                                      |

| V <sub>X, IN</sub>  | Differential cross point voltage <sup>3</sup>                            | 0.25                    | 0.68 - 0.9 | V <sub>CC</sub> – 1.3   | V    |                                      |

| V <sub>IH</sub>     | Input high voltage                                                       | V <sub>X</sub> + 0.1    |            |                         | V    |                                      |

| V <sub>IL</sub>     | Input low voltage                                                        |                         |            | V <sub>X</sub> -0.1     | V    |                                      |

| I <sub>IN</sub>     | Input current                                                            |                         |            | ±150                    | mA   | $V_{IN} = V_X \pm 0.1V$              |

| PECL differe        | ntial input signals (CLK1, CLK1)                                         |                         |            |                         |      | ·                                    |

| V <sub>PP</sub>     | Differential input voltage <sup>4</sup>                                  | 0.15                    |            | 1.0                     | V    | Differential Operation               |

| V <sub>CMR</sub>    | Differential cross point voltage <sup>5</sup>                            | 1.0                     |            | V <sub>CC</sub> -0.6    | V    | Differential Operation               |

| V <sub>IH</sub>     | Input high voltage                                                       | V <sub>CC</sub> – 1.165 |            | V <sub>CC</sub> -0.880  | V    |                                      |

| V <sub>IL</sub>     | Input low voltage                                                        | V <sub>CC</sub> – 1.810 |            | V <sub>CC</sub> – 1.475 | V    |                                      |

| I <sub>IN</sub>     | Input current                                                            |                         |            | ±150                    | mA   | $V_{IN} = V_{IH} \text{ or } V_{IN}$ |

| LVCMOS cor          | ntrol inputs EN, CLK_SEL                                                 |                         |            |                         |      | ·                                    |

| V <sub>IL</sub>     | Input low voltage                                                        |                         |            | 0.8                     | V    |                                      |

| V <sub>IH</sub>     | Input high voltage                                                       | 2.0                     |            |                         | V    |                                      |

| I <sub>IN</sub>     | Input current                                                            |                         |            | ±150                    | mA   | $V_{IN} = V_{IH} \text{ or } V_{IN}$ |

| HSTL clock of       | outputs (Q[0:4], Q[0:4])                                                 |                         |            |                         |      | ·                                    |

| V <sub>X, OUT</sub> | Output differential crosspoint                                           | 0.68                    | 0.75       | 0.9                     | V    |                                      |

| V <sub>OH</sub>     | Output high voltage                                                      | 1                       |            |                         | V    |                                      |

| V <sub>OL</sub>     | Ouput low voltage                                                        |                         |            | 0.4                     | V    |                                      |

| Supply Curre        | nt                                                                       |                         |            |                         |      |                                      |

| I <sub>CC</sub>     | Maximum Quiescent Supply Current without<br>output termination current   |                         | TBD        | TBD                     | mA   | V <sub>CC</sub> pin (core)           |

| I <sub>CCO</sub>    | Maximum Quiescent Supply Current, outputs terminated 50 $\Omega$ to V_TT |                         | TBD        | TBD                     | mA   | V <sub>CCO</sub> pin (outputs)       |

# Table 5. DC Characteristics $(V_{CC} = 3.3V \pm 5\%; T_J = 0^{\circ}C \text{ to } 110^{\circ}C)^1$

1. DC characteristics are design targets and pending characterization.

2. V<sub>DIF</sub> (DC) is the minimum differential HSTL input voltage swing required for device functionality.

3. V<sub>X</sub> (DC) is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the V<sub>X</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

4. V<sub>PP</sub> (DC) is the minimum differential input voltage swing required to maintain device functionality.

5. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

| Symbol                          | Characteristic                                         | Min                    | Тур     | Max                    | Unit | Condition                |

|---------------------------------|--------------------------------------------------------|------------------------|---------|------------------------|------|--------------------------|

| HSTL/LVDS                       | S differential input signals (CLK0, CLK0)              |                        |         |                        |      |                          |

| V <sub>DIF</sub>                | Differential input voltage (peak-to-peak) <sup>3</sup> | 0.4                    |         |                        | V    |                          |

| V <sub>X, IN</sub>              | Differential cross point voltage <sup>4</sup>          | 0.68                   |         | 0.9                    | V    |                          |

| f <sub>CLK</sub>                | Input Frequency                                        |                        | 0 - 400 | TBD                    | MHz  | Differential             |

| t <sub>PD</sub>                 | Propagation Delay                                      |                        |         | TBD                    | ps   | Differential             |

| PECL differ                     | ential input signals (CLK1, CLK1)                      | •                      |         |                        |      |                          |

| V <sub>PP</sub>                 | Differential input voltage (peak-to-peak) <sup>5</sup> | 0.2                    |         | 1.0                    | V    |                          |

| V <sub>CMR</sub>                | Differential cross point voltage <sup>6</sup>          | 1                      |         | V <sub>CC</sub> - 0.6  | V    |                          |

| f <sub>CLK</sub>                | Input Frequency                                        |                        | 0 – 400 |                        | MHz  | Differential             |

| t <sub>PD</sub>                 | Propagation Delay                                      |                        |         | TBD                    | ps   | Differential             |

| HSTL clock                      | outputs (Q[0:4], Q[0:4])                               |                        |         |                        |      |                          |

| V <sub>X, OUT</sub>             | Output differential crosspoint                         | 0.68                   | 0.75    | 0.9                    | V    |                          |

| V <sub>OH</sub>                 | Output high voltage                                    |                        |         |                        | V    |                          |

| V <sub>OL</sub>                 | Ouput low voltage                                      |                        |         | 0.5                    | V    |                          |

| V <sub>O(P-P)</sub>             | Differential output voltage (peak-to-peak)             | 0.5                    |         |                        | V    |                          |

| t <sub>SK(O)</sub>              | Output-to-output skew                                  |                        | *       | 50                     | ps   | Differential             |

| t <sub>SK(PP)</sub>             | Output-to-output skew (part-to-part)                   |                        |         | TBD                    | ps   | Differential             |

| t <sub>JIT(CC)</sub>            | Output cycle-to-cycle jitter                           |                        |         | TBD                    |      |                          |

| DC <sub>O</sub>                 | Output duty cycle                                      | TBD                    | 50      | TBD                    | %    | DC <sub>fref</sub> = 50% |

| t <sub>r</sub> / t <sub>f</sub> | Output Rise/Fall Times                                 | 0.05                   |         | TBD                    | ns   | 20% to 80%               |

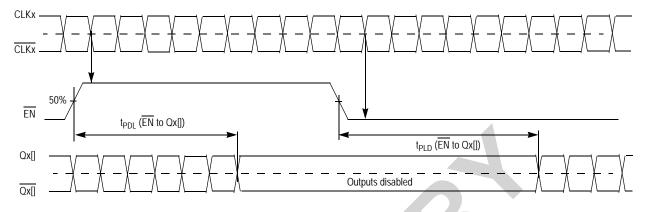

| t <sub>PDL</sub>                | Output disable time <sup>7</sup>                       | 2.5*T +t <sub>PD</sub> |         | 3.5*T +t <sub>PD</sub> | ns   | T = CLK period           |

| t <sub>PLD</sub>                | Output enable time <sup>8</sup>                        | 3*T +t <sub>PD</sub>   |         | 4*T +t <sub>PD</sub>   | ns   | T = CLK period           |

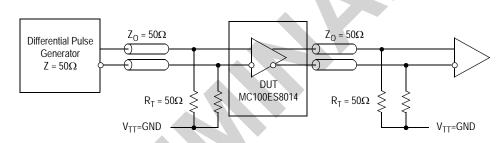

# Table 6. AC Characteristics (V<sub>CC</sub> = $3.3V\pm5\%$ ; T<sub>J</sub> = 0°C to 110°C)<sup>1 2</sup>

1. AC characteristics are design targets and pending characterization.

2. AC characteristics apply for parallel output termination of 50  $\!\Omega$  to V\_{TT.}

3. V<sub>DIF</sub> (AC) is the minimum differential HSTL input voltage swing required to maintain AC characteristics including tpd and device-to-device skew.

4. V<sub>X</sub> (AC) is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the V<sub>X</sub> (AC) range and the input swing lies within the V<sub>DIF</sub> (AC) specification. Violation of V<sub>X</sub> (AC) or V<sub>DIF</sub>(AC) impacts the device propagation delay, device and part-to-part skew.

5. V<sub>PP</sub> (AC) is the minimum differential PECL input voltage swing required to maintain AC characteristics including tpd and device-to-device skew.

V<sub>CMR</sub> (AC) is the crosspoint of the differential PECL input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub>(AC) impacts the device propagation delay, device and part-to-part skew.

7. Propagation delay EN deassertion to differential output disabled (differential low: true output low, complementary output high).

8. Propagation delay  $\overline{EN}$  assertion to output enabled (active).

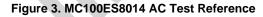

Figure 2. MC100ES8014 AC Test Reference

Figure 4. MC100ES8014 AC Reference Measurement Waveform (HSTL Input)

Figure 5. MC100ES8014 AC Reference Measurement Waveform (PECL Input)

IDT<sup>™</sup> Low Voltage 1:5 Differential LVDS Clock Fanout Buffer

IDT<sup>™</sup> Low Voltage 1:5 Differential LVDS Clock Fanout Buffer

# PACKAGE DIMENSIONS

# Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

# For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

# For Tech Support

netcom@idt.com 480-763-2056

# **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Acelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA