# Low Voltage 1:2 Differential HSTL Clock Fanout Buffer

MC100ES8011H

The MC100ES8011H is a low voltage 1:2 Differential HSTL fanout buffer. Designed for the most demanding clock distribution systems, the MC100ES8011H supports various applications that require the distribution of precisely aligned differential clock signals. Using SiGe technology and a fully differential architecture, the device offers very low skew outputs and superior digital signal characteristics. Target applications for this clock driver are in high performance clock distribution in computing, networking and telecommunication systems.

### Features

- 1:2 differential clock fanout buffer

- 20 ps maximum device skew

- SiGe Technology

- Supports DC to 625 MHz operation

- HSTL compatible differential clock outputs

- HSTL compatible differential clock inputs

- 3.3V power supply

- Supports industrial temperature range

- Standard 8 lead SOIC package

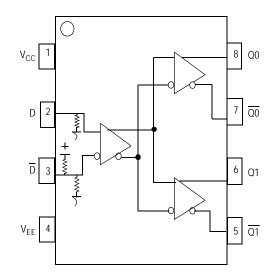

Figure 1. 8-Lead Pinout (Top View) and Logic Diagram

| ORDERING INFORMATION |

|----------------------|

|----------------------|

| Device          | Package |

|-----------------|---------|

| MC100ES8011HD   | SO-8    |

| MC100ES8011HDR2 | SO-8    |

| PIN DESCRIPTION |                   |  |  |  |

|-----------------|-------------------|--|--|--|

| Pin             | Pin Function      |  |  |  |

| D, D            | HSTL Data Inputs  |  |  |  |

| Qn, Qn          | HSTL Data Outputs |  |  |  |

| V <sub>CC</sub> | Positive Supply   |  |  |  |

| V <sub>EE</sub> | Negative Supply   |  |  |  |

IDT<sup>™</sup> Low Voltage 1:2 Differential HSTL Clock Fanout Buffer

### Table 1. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol              | Parameter                   | Conditions                                           | Rating                                         | Unit     |  |

|---------------------|-----------------------------|------------------------------------------------------|------------------------------------------------|----------|--|

| V <sub>SUPPLY</sub> | Power Supply Voltage        | Difference between V <sub>CC</sub> & V <sub>EE</sub> | 3.9                                            | V        |  |

| V <sub>IN</sub>     | Input Voltage               | $V_{CC} - V_{EE} \le 3.6V$                           | V <sub>CC</sub> + 0.3<br>V <sub>EE</sub> - 0.3 | V<br>V   |  |

| I <sub>OUT</sub>    | Output Current              | Continuous<br>Surge                                  | 50<br>100                                      | mA<br>mA |  |

| T <sub>A</sub>      | Operating Temperature Range |                                                      | -40 to +85                                     | °C       |  |

| T <sub>STG</sub>    | Storage Temperature Range   |                                                      | -65 to +150                                    | °C       |  |

1. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

Table 2. DC Characteristics (V<sub>CC</sub> =  $3.3 \text{ V} \pm 5\%$ ; T<sub>J</sub> = 0°C to  $110^{\circ}$ C)<sup>(1)</sup>

| Symbol          | Characteristic                                                      | Min  | Тур        | Max                   | Unit | Condition                  |

|-----------------|---------------------------------------------------------------------|------|------------|-----------------------|------|----------------------------|

| HSTL differe    | ential input signals (D, $\overline{D}$ )                           |      |            |                       |      | •                          |

| $V_{DIF}$       | Differential Input Voltage <sup>(2)</sup>                           | 0.2  |            |                       | V    |                            |

| $V_{X, IN}$     | Differential Cross Point Voltage <sup>(3)</sup>                     | 0.25 | 0.68 - 0.9 | V <sub>CC</sub> – 1.3 | V    |                            |

| I <sub>IN</sub> | Input Current                                                       |      |            | ±150                  | mA   | $V_{IN} = V_X \pm 0.1V$    |

| HSTL clock      | outputs (Q[0:1], Q[0:1])                                            |      |            |                       | •    |                            |

| $V_{X,  OUT}$   | Output Differential Crosspoint                                      | 0.68 | 0.75       | 0.9                   | V    |                            |

| V <sub>OH</sub> | Output High Voltage                                                 | 1    |            |                       | V    |                            |

| V <sub>OL</sub> | Ouput Low Voltage                                                   |      |            | 0.4                   | V    |                            |

| Supply Curr     | ent                                                                 |      |            |                       |      |                            |

| I <sub>CC</sub> | Maximum Quiescent Supply Current without output termination current |      | 80         | 105                   | mA   | V <sub>CC</sub> pin (core) |

1. DC characteristics are design targets and pending characterization.

2. V<sub>DIF</sub> (DC) is the minimum differential HSTL input voltage swing required for device functionality.

3.  $V_X(DC)$  is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the V<sub>X</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

Downloaded from Elcodis.com electronic components distributor

| Symbol                          | Characteristic                                           | Min  | Тур  | Max  | Unit | Condition    |

|---------------------------------|----------------------------------------------------------|------|------|------|------|--------------|

| HSTL differ                     | ential input signals (D, $\overline{D}$ )                |      |      |      | •    |              |

| $V_{DIF}$                       | Differential Input Voltage (peak-to-peak) <sup>(3)</sup> | 0.4  |      |      | V    |              |

| $V_{X, IN}$                     | Differential Cross Point Voltage <sup>(4)</sup>          | 0.68 |      | 0.9  | V    |              |

| f <sub>CLK</sub>                | Input Frequency                                          |      |      | 625  | MHz  | Differential |

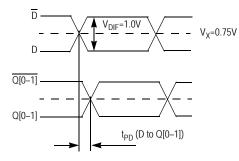

| t <sub>PD</sub>                 | Propagation Delay D to Q[0:1}                            | 700  | 920  | 1200 | ps   | Differential |

| HSTL clock                      | outputs (Q[0:1], Q[0:1])                                 |      |      |      | •    |              |

| $V_{X,  OUT}$                   | Output Differential Crosspoint                           | 0.68 | 0.75 | 0.9  | V    |              |

| V <sub>OH</sub>                 | Output High Voltage                                      | 1    |      |      | V    |              |

| V <sub>OL</sub>                 | Ouput Low Voltage                                        |      |      | 0.5  | V    |              |

| V <sub>O(P-P)</sub>             | Differential Output Voltage (peak-to-peak)               | 0.5  |      |      | V    |              |

| t <sub>SK(O)</sub>              | Output-to-Output Skew                                    |      |      | 20   | ps   | Differential |

| t <sub>SK(PP)</sub>             | Output-to-Output Skew (part-to-part)                     |      |      | 500  | ps   | Differential |

| t <sub>SK(P)</sub>              | Output Pulse Skew                                        |      |      | 100  | ps   |              |

| t <sub>JIT(CC)</sub>            | Output Cycle-to-Cycle Jitter                             |      |      | 1    | ps   |              |

| t <sub>r</sub> / t <sub>f</sub> | Output Rise/Fall Times                                   | 150  |      | 800  | ps   | 20% to 80%   |

### Table 3. AC Characteristics (V<sub>CC</sub> = $3.3 \text{ V} \pm 5\%$ ; T<sub>J</sub> = 0°C to $110^{\circ}$ C)<sup>(1)</sup> (2)

1. AC characteristics are design targets and pending characterization.

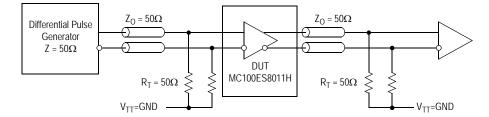

2. AC characteristics apply for parallel output termination of  $50\Omega$  to V<sub>TT.</sub> 3. V<sub>DIF</sub> (AC) is the minimum differential HSTL input voltage swing required to maintain AC characteristics including t<sub>PD</sub> and device-to-device skew.

4. V<sub>X</sub> (AC) is the crosspoint of the differential HSTL input signal. Functional operation is obtained when the crosspoint is within the V<sub>X</sub> (AC) range and the input swing lies within the V<sub>DIF</sub> (AC) specification. Violation of V<sub>X</sub> (AC) or V<sub>DIF</sub> (AC) impacts the device propagation delay, device and part-to-part skew.

Figure 2. MC100ES8011H AC Test Reference

Figure 3. MC100ES8011H AC Reference Measurement Waveform (HSTL Input)

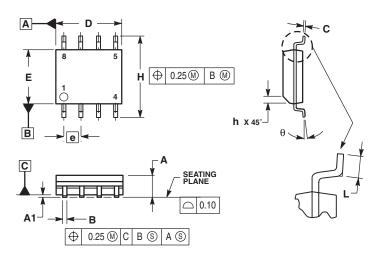

### PACKAGE DIMENSIONS

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. DIMENSIONS ARE IN MILLIMETER. 3. DIMENSION AND E DO NOT INCLUDE MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. 5. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 1.35        | 1.75 |  |  |

| A1  | 0.10        | 0.25 |  |  |

| В   | 0.35        | 0.49 |  |  |

| С   | 0.19        | 0.25 |  |  |

| D   | 4.80        | 5.00 |  |  |

| Е   | 3.80        | 4.00 |  |  |

| е   | 1.27        | BSC  |  |  |

| Н   | 5.80        | 6.20 |  |  |

| h   | 0.25        | 0.50 |  |  |

| L   | 0.40        | 1.25 |  |  |

| θ   | 0°          | 7°   |  |  |

**D SUFFIX 8-LEAD SOIC PACKAGE** CASE 751-06

## Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

### For Tech Support

netcom@idt.com 480-763-2056

### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Acelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA