# Clock Generator for PowerQUICC III

**MPC9865**

The MPC9865 is a PLL based clock generator specifically designed for Freescale Microprocessor and Microcontroller applications including the PowerPC and PowerQUICC. This device generates a microprocessor input clock. The microprocessor clock is selectable in output frequency to any of the commonly used microprocessor input and bus frequencies. The device offers eight low skew clock outputs in two banks, each configurable to support different clock frequencies. The extended temperature range of the MPC9865 supports telecommunication and networking requirements.

#### **Features**

- · 8 LVCMOS outputs for processor and other circuitry

- Crystal oscillator or external reference input

- 25 or 33 MHz Input reference frequency

- Selectable output frequencies include = 200, 166, 133,125, 111, 100, 83, 66, 50, 33, or 16 MHz

- · Buffered reference clock output (2 copies)

- · Low cycle-to-cycle and period jitter

- 100-lead PBGA package

- 100-lead Pb-free package available

- 3.3 V supply with 3.3 V or 2.5 V LVCMOS output supplies

- · Supports computing, networking, telecommunications applications

- Ambient temperature range -40°C to +85°C

#### MICROPROCESSOR CLOCK GENERATOR

VF SUFFIX VM SUFFIX (PB-FREE) 100 MAPBGA PACKAGE CASE 1462-01

# **Functional Description**

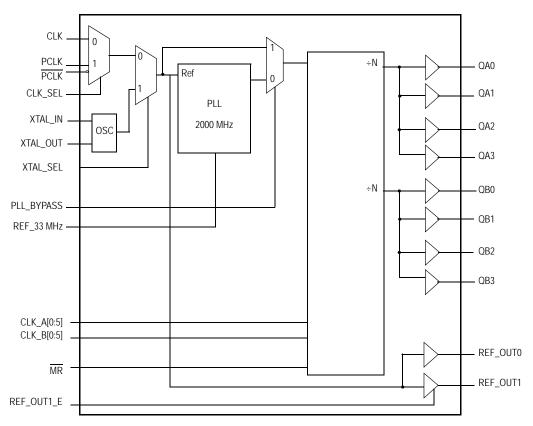

The MPC9865 uses either a 25 or 33 MHz reference frequency to generate 8 LVCMOS output clocks, of which, the frequency is selectable from 16 MHz to 200 MHz. The reference is applied to the input of a PLL and multiplied to 2 GHz. Output dividers, divide this frequency by 10, 12, 15, 16, 18, 20, 24, 30, 40, 60, or 120 to produce output frequencies of 200, 166, 133, 125, 111, 100, 83, 66, 50, 33, or 16 MHz. The single-ended LVCMOS outputs provide 8 low skew outputs for use in driving a microprocessor or microcontroller clock input as well as other system components. The input reference, either crystal or external input is also buffered to a separate dual outputs that my be used as the clock source for a Ethernet PHY if desired.

The reference clock may be provided by either an external clock input of 25 or 33 MHz. An internal oscillator requiring a 25 MHz crystal for frequency control may also be used. The external clock source my be applied to either of two clock inputs and selected via the CLK\_SEL control input. Both single ended LVCMOS and differential LVPECL inputs are available. The crystal oscillator or external clock input is selected via the input pin of XTAL\_SEL. Other than the crystal, no external components are required for crystal oscillator operation. The REF\_33 MHz configuration pin is used to select between a 33 and 25 MHz input frequency.

The MPC9865 is packaged in a 100 lead MAPBGA package to optimize both performance and board density.

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

Figure 1. MPC9865 Logic Diagram

**Table 1. Pin Configurations**

| Pin                                            | 1/0    | Туре   | Function                                                               | Supply            | Active/State |

|------------------------------------------------|--------|--------|------------------------------------------------------------------------|-------------------|--------------|

| CLK                                            | Input  | LVCMOS | PLL Reference Clock Input (pull-down)                                  | $V_{DD}$          |              |

| PCLK, PCLK                                     | Input  | LVPECL | PLL reference clock input (PCLK — pull-down)                           | V <sub>DD</sub>   | _            |

| QA0, QA1,<br>QA2, QA3<br>QB0, QB1,<br>QB2, QB3 | Output | LVCMOS | Clock Outputs                                                          | V <sub>DDOA</sub> | _            |

| REF_OUT0<br>REF_OUT1                           | Output | LVCMOS | Reference Output (25 MHz or 33 MHz)                                    | V <sub>DD</sub>   | _            |

| XTAL_IN                                        | Input  | LVCMOS | Crystal Oscillator Input Pin                                           | $V_{DD}$          | _            |

| XTAL_OUT                                       | Output | LVCMOS | Crystal Oscillator Output Pin                                          | $V_{DD}$          | _            |

| CLK_SEL                                        | Input  | LVCMOS | Select between CLK and PCLK input (pull-down)                          | $V_{DD}$          | High         |

| XTAL_SEL                                       | Input  | LVCMOS | Select between External Input and Crystal Oscillator Input (pull-down) | V <sub>DD</sub>   | High         |

| REF_33 MHz                                     | Input  | LVCMOS | Selects 33 MHz input (pull-down)                                       | $V_{DD}$          | High         |

| REF_OUT1_E                                     | Input  | LVCMOS | Enables REF_OUT1 output (pull-down)                                    | $V_{DD}$          | High         |

| MR                                             | Input  | LVCMOS | Master Reset (pull-up)                                                 | $V_{DD}$          | Low          |

| PLL_BYPASS                                     | Input  | LVCMOS | Select PLL or static test mode (pull-down)                             | $V_{DD}$          | High         |

| CLK_A[0:5] <sup>(1)</sup>                      | Input  | LVCMOS | Configures Bank A clock output frequency (pull-up)                     | $V_{DD}$          | _            |

| CLK_B[0:5] <sup>(2)</sup>                      | Input  | LVCMOS | Configures Bank B clock output frequency (pull-up)                     | $V_{DD}$          | _            |

| $V_{DD}$                                       | _      | _      | 3.3 V Supply                                                           | _                 | _            |

| $V_{DDA}$                                      | _      | _      | Analog Supply                                                          | _                 | _            |

| $V_{\text{DDOA}}$                              | _      | _      | Output Supply — Bank A                                                 | _                 | _            |

| $V_{DDOB}$                                     | _      | _      | Output Supply — Bank B                                                 | _                 | _            |

| GND                                            | _      | _      | Ground                                                                 | _                 | _            |

<sup>1.</sup> PowerPC bit ordering (bit 0 = msb, bit 5 = lsb).

**Table 2. Function Table**

| Control    | Default                               | 0                 | 1                        |

|------------|---------------------------------------|-------------------|--------------------------|

| CLK_SEL    | 0                                     | CLK               | PCLK                     |

| XTAL_SEL   | 0                                     | CLKx              | XTAL                     |

| PLL_BYPASS | 0                                     | Normal            | Bypass                   |

| REF_OUT1_E | 0                                     | Disables REF_OUT1 | Enables REF_OUT1         |

| REF_33 MHz | REF_33 MHz 0 Selects 25 MHz Reference |                   | Selects 33 MHz Reference |

| MR         | 1                                     | Reset             | Normal                   |

CLK\_A and CLK\_B control output frequencies. See **Table 3** for specific device configuration.

<sup>2.</sup> PowerPC bit ordering (bit 0 = msb, bit 5 = lsb).

Table 3. Output Configurations (Banks A & B)

| CLK_x[0:5] <sup>(1)</sup> | CLK_x[0]<br>(msb) | CLK_x[1] | CLK_x[2] | CLK_x[3] | CLK_x[4] | CLK_x[5]<br>(Isb) | N                | Frequency<br>(MHz) |

|---------------------------|-------------------|----------|----------|----------|----------|-------------------|------------------|--------------------|

| 111111                    | 1                 | 1        | 1        | 1        | 1        | 1                 | 126              | 15.87              |

| 111100                    | 1                 | 1        | 1        | 1        | 0        | 0                 | 120              | 16.67              |

| 101000                    | 1                 | 0        | 1        | 0        | 0        | 0                 | 80               | 25.00              |

| 011110                    | 0                 | 1        | 1        | 1        | 1        | 0                 | 60               | 33.33              |

| 010100                    | 0                 | 1        | 0        | 1        | 0        | 0                 | 40               | 50.00              |

| 010000                    | 0                 | 1        | 0        | 0        | 0        | 0                 | 32               | 62.5               |

| 001111                    | 0                 | 0        | 1        | 1        | 1        | 1                 | 30               | 66.67              |

| 001100                    | 0                 | 0        | 1        | 1        | 0        | 0                 | 24               | 83.33              |

| 001010                    | 0                 | 0        | 1        | 0        | 1        | 0                 | 20               | 100.00             |

| 001001                    | 0                 | 0        | 1        | 0        | 0        | 1                 | 18               | 111.11             |

| 001000                    | 0                 | 0        | 1        | 0        | 0        | 0                 | 16               | 125.00             |

| 000111                    | 0                 | 0        | 0        | 1        | 1        | 1                 | 15               | 133.33             |

| 000110                    | 0                 | 0        | 0        | 1        | 1        | 0                 | 12               | 166.67             |

| 000101                    | 0                 | 0        | 0        | 1        | 0        | 1                 | 10               | 200.00             |

| 000100                    | 0                 | 0        | 0        | 1        | 0        | 0                 | 8 <sup>(2)</sup> | 250                |

<sup>1.</sup> PowerPC bit ordering (bit 0 = msb, bit 5 = lsb).

<sup>2.</sup> Minimum value for N.

#### OPERATION INFORMATION

#### **Output Frequency Configuration**

The MPC9865 was designed to provide the commonly used frequencies in PowerQUICC, PowerPC and other microprocessor systems. **Table 3** lists the configuration values that will generate those common frequencies. The MPC9865 can generate numerous other frequencies that may be useful in specific applications. The output frequency  $(f_{out})$  of either Bank A or Bank B may be calculated by the following equation.

$$f_{out} = 2000 / N$$

where f<sub>out</sub> is in MHz and N = 2 \* CLK\_x[0:5]

This calculation is valid for all values of N from 8 to 126. Note that N = 15 is a modified case of the configuration inputs

$CLK_x[0:5]$ . To achieve N = 15  $CLK_x[0:5]$  is configured to 00111 or 7.

#### **Crystal Input Operation**

TBD

#### Power-Up and MR Operation

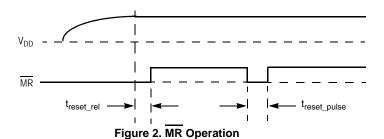

Figure 2 defines the release time and the minimum pulse length for  $\overline{\text{MR}}$  pin. The  $\overline{\text{MR}}$  release time is based upon the power supply being stable and within  $V_{DD}$  specifications. See Table 9 for actual parameter values. The MPC9865 may be configured after release of reset and the outputs will be stable for use after lock indication is obtained.

#### **Power Supply Bypassing**

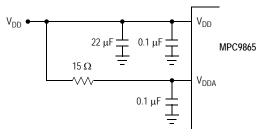

The MPC9865 is a mixed analog/digital product. The architecture of the MPC9865 supports low noise signal operation at high frequencies. In order to maintain its superior signal quality, all V<sub>DD</sub> pins should be bypassed by high-frequency ceramic capacitors connected to GND. If the spectral frequencies of the internally generated switching noise on the supply pins cross the series resonant point of an individual bypass capacitor, its overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the noise bandwidth.

Figure 3. V<sub>CC</sub> Power Supply Bypass

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

#### **Power Consumption Calculation**

For unloaded outputs the power consumption of the MPC9855 can be calculated as follows.

$$P = V_{DD} * I_{DDBASE} + n_A * (V_{DDOA} ** 2 * C_{PD} * f_A)$$

$$+ n_B * (V_{DDOB} ** 2 * C_{PD} * f_B)$$

V<sub>DD</sub> = core supply voltage

$I_{DDBASE}$  = base supply current

$n_A$  = number of A bank outputs (= 4)

n<sub>B</sub> = number of B bank outputs (= 4)

$V_{DDOA}$  = voltage supply on bank A outputs  $V_{DDOB}$  = voltage supply on bank B outputs

C<sub>PD</sub> = power dissipation capacitance

f<sub>A</sub> = frequency of bank A outputs

f<sub>B</sub> = frequency of bank B outputs

Table 4. Absolute Maximum Ratings<sup>(1)</sup>

| Symbol            | Characteristics                                 | Min  | Max                   | Unit | Condition |

|-------------------|-------------------------------------------------|------|-----------------------|------|-----------|

| V <sub>DD</sub>   | Supply Voltage (core)                           | -0.3 | 3.8                   | V    |           |

| V <sub>DDA</sub>  | Supply Voltage (Analog Supply Voltage)          | -0.3 | $V_{DD}$              | V    |           |

| V <sub>DDOx</sub> | Supply Voltage (LVCMOS output for Bank A and B) | -0.3 | $V_{DD}$              | V    |           |

| V <sub>IN</sub>   | DC Input Voltage                                | -0.3 | V <sub>DD</sub> +0.3  | V    |           |

| V <sub>OUT</sub>  | DC Output Voltage <sup>(2)</sup>                | -0.3 | V <sub>DDx</sub> +0.3 | V    |           |

| I <sub>IN</sub>   | DC Input Current                                |      | ±20                   | mA   |           |

| I <sub>OUT</sub>  | DC Output Current                               |      | ±50                   | mA   |           |

| T <sub>S</sub>    | Storage Temperature                             | -65  | 125                   | °C   |           |

<sup>1.</sup> Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

#### **Table 5. General Specifications**

| Symbol          | Characteristics                          | Min | Тур                 | Max | Unit | Condition    |

|-----------------|------------------------------------------|-----|---------------------|-----|------|--------------|

| $V_{TT}$        | Output Termination Voltage               |     | V <sub>DD</sub> ÷ 2 |     | V    |              |

| C <sub>IN</sub> | Input Capacitance                        |     | 4                   |     | pF   | Inputs       |

| C <sub>PD</sub> | Power Dissipation Capacitance            |     | 10                  |     | pF   | Per Output   |

| $\theta_{JA}$   | Thermal Resistance (Junction-to-Ambient) |     | 54.5                |     | °C/W | Air flow = 0 |

| T <sub>A</sub>  | Ambient Temperature                      | -40 |                     | 85  | °C   |              |

# Table 6. DC Characteristics ( $T_A = -40$ °C to 85°C)

| Symbol              | Characteristics                                                                                          | Min | Тур | Max | Unit | Condition                                  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--------------------------------------------|--|--|--|--|

| Supply Cur          | Supply Current for $V_{DD}$ = 3.3 V $\pm$ 5%, $V_{DDOA}$ = 3.3 V $\pm$ 5 and $V_{DDOB}$ = 3.3 V $\pm$ 5% |     |     |     |      |                                            |  |  |  |  |

| I <sub>DDBASE</sub> | Base Supply Current (Core)                                                                               |     | TBD | TBD | mA   | V <sub>DD</sub> + V <sub>DDA</sub><br>pins |  |  |  |  |

| I <sub>DDA</sub>    | Maximum Quiescent Supply Current (Analog Supply)                                                         |     |     | TBD | mA   | V <sub>DDIN</sub> pins                     |  |  |  |  |

<sup>2.</sup>  $V_{\text{DDx}}$  references power supply pin associated with specific output pin.

Table 7. LVPECL DC Characteristics  $(T_A = -40^{\circ}C \text{ to } 85^{\circ}C)^{(1)}$

| Symbol           | Characteristics                                                                                           | Min      | Тур | Max | Unit                  | Condition |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------|----------|-----|-----|-----------------------|-----------|--|--|--|--|

| Differentia      | Differential LVPECL Clock Inputs (CLK1, $\overline{\text{CLK1}}$ ) for $V_{\text{DD}}$ = 3.3 V $\pm$ 0.5% |          |     |     |                       |           |  |  |  |  |

| $V_{PP}$         | Differential Voltage <sup>(2)</sup> (peak-to-peak)                                                        | (LVPECL) | 250 |     |                       | mV        |  |  |  |  |

| V <sub>CMR</sub> | Differential Input Crosspoint Voltage <sup>(3)</sup>                                                      | (LVPECL) | 1.0 |     | V <sub>DD</sub> – 0.6 | V         |  |  |  |  |

- 1. AC characteristics are design targets and pending characterization.

- 2. V<sub>PP</sub> is the minimum differential input voltage swing required to maintain AC characteristics including t<sub>PD</sub> and device-to-device skew.

- 3. V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> (AC) range and the input swing lies within the V<sub>PP</sub> (AC) specification. Violation of V<sub>CMR</sub> (AC) or V<sub>PP</sub> (AC) impacts the device propagation delay, device and part-to-part skew.

Table 8. LVCMOS I/O DC Characteristics ( $T_A = -40$ °C to 85°C)

| Symbol           | Characteristics                                                                                                       | Min      | Тур     | Max                   | Unit | Condition                 |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|----------|---------|-----------------------|------|---------------------------|--|--|--|

| LVCMOS f         | or V <sub>DD</sub> = 3.3 V ± 5%                                                                                       |          |         |                       |      |                           |  |  |  |

| V <sub>IH</sub>  | Input High Voltage                                                                                                    | 2.0      |         | V <sub>DD</sub> + 0.3 | V    | LVCMOS                    |  |  |  |

| V <sub>IL</sub>  | Input Low Voltage                                                                                                     |          |         | 0.8                   | V    | LVCMOS                    |  |  |  |

| I <sub>IN</sub>  | Input Current <sup>(1)</sup>                                                                                          |          |         | ± 200                 | μА   | $V_{IN} = V_{DDL}$ or GND |  |  |  |

| LVCMOS           | LVCMOS for V <sub>DD</sub> = 3.3 V $\pm$ 5%, V <sub>DDOA</sub> = 3.3 V $\pm$ 5 and V <sub>DDOB</sub> = 3.3 V $\pm$ 5% |          |         |                       |      |                           |  |  |  |

| V <sub>OH</sub>  | Output High Voltage                                                                                                   | 2.4      |         |                       | V    | I <sub>OH</sub> = -24 mA  |  |  |  |

| V <sub>OL</sub>  | Output Low Voltage                                                                                                    |          |         | 0.5                   | V    | I <sub>OL</sub> = 24 mA   |  |  |  |

| Z <sub>OUT</sub> | Output Impedance                                                                                                      |          | 14 – 17 |                       | Ω    |                           |  |  |  |

| LVCMOS f         | or $V_{DD}$ = 3.3 V $\pm$ 5%, $V_{DDOA}$ = 2.5 V $\pm$ 5% and $V_{DDOB}$ = 2.5                                        | 5 V ± 5% |         |                       |      |                           |  |  |  |

| V <sub>OH</sub>  | Output High Voltage                                                                                                   | 1.9      |         |                       | V    | $I_{OH} = -15 \text{ mA}$ |  |  |  |

| V <sub>OL</sub>  | Output Low Voltage                                                                                                    |          |         | 0.4                   | V    | I <sub>OL</sub> = 15 mA   |  |  |  |

| Z <sub>OUT</sub> | Output Impedance                                                                                                      |          | 18 – 22 |                       | Ω    |                           |  |  |  |

<sup>1.</sup> Inputs have pull-down resistors affecting the input current.

| Table 9. AC Characteristics ( $V_{DD} = 3.3 \text{ V} + 5\%$ | $V_{DDOAB} = 3.3 \text{ V} \pm 5\%, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})^{(1)}$ (2)          |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1451C 3. AC Characteristics (VI)I) = 0.5 V ± 070             | $(V_1)(V_1)(V_2)(V_1)(V_2)(V_1)(V_2)(V_1)(V_2)(V_1)(V_2)(V_2)(V_1)(V_2)(V_2)(V_2)(V_2)(V_2)(V_2)(V_2)(V_2$ |

| Symbol                          | Characteristics                                                                                                                                          | Min            | Тур            | Max        | Unit                     | Condition                                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------|--------------------------|----------------------------------------------------------|

| Input and Out                   | put Timing Specification                                                                                                                                 |                | •              | •          | •                        | •                                                        |

| f <sub>ref</sub>                | Input Reference Frequency (25 MHz input) Input Reference Frequency (33 MHz input) XTAL Input Input Reference Frequency in PLL Bypass Mode <sup>(3)</sup> |                | 25<br>33<br>25 | 250        | MHz<br>MHz<br>MHz<br>MHz | PLL bypass                                               |

| $f_{VCO}$                       | VCO Frequency Range                                                                                                                                      |                | 2000           |            | MHz                      |                                                          |

| f <sub>MCX</sub>                | Output Frequency  Bank A output Bank B output                                                                                                            | 15.87<br>15.87 |                | 200<br>200 | MHz<br>MHz               | PLL locked                                               |

| f <sub>refPW</sub>              | Reference Input Pulse Width                                                                                                                              | 2              |                |            | ns                       |                                                          |

| f <sub>refCcc</sub>             | Input Frequency Accuracy                                                                                                                                 |                |                | 100        | ppm                      |                                                          |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                                                    | 150            |                | 500        | ps                       | 20% to 80%                                               |

| DC                              | Output Duty Cycle                                                                                                                                        | 45             | 50             | 55         | %                        | Bank A and B                                             |

| PLL Specifica                   | tions                                                                                                                                                    |                |                |            |                          |                                                          |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                                                    |                |                | 10         | ms                       |                                                          |

| t <sub>reset_ref</sub>          | MR Hold Time on Power Up                                                                                                                                 | 10             |                |            | ns                       |                                                          |

| t <sub>reset_pulse</sub>        | MR Hold Time                                                                                                                                             | 10             |                |            | ns                       |                                                          |

| Skew and Jitte                  | er Specifications                                                                                                                                        |                |                |            | •                        |                                                          |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (within a bank)                                                                                                                    |                |                | 50         | ps                       |                                                          |

| t <sub>sk(O)</sub>              | Output-to-Output Skew (across banks A and B)                                                                                                             |                |                | 100        | ps                       | $V_{DDOA} = 3.3 \text{ V}$<br>$V_{DDOB} = 3.3 \text{ V}$ |

| t <sub>JIT(CC)</sub>            | Cycle-to-Cycle Jitter                                                                                                                                    |                |                | 150        | ps                       | Bank A and B                                             |

| t <sub>JIT(PER)</sub>           | Period Jitter                                                                                                                                            |                |                | 150        | ps                       | Bank A and B                                             |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                                                                                                                    |                |                | TBD        | ns                       | 20% to 80%                                               |

- 1. AC characteristics are design targets and pending characterization.

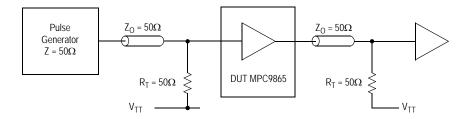

- 2. AC characteristics apply for parallel output termination of  $50\Omega$  to  $V_{TT}.$

- 3. In bypass mode, the MPC9865 divides the input reference clock.

Figure 4. MPC9865 AC Test Reference (LVCMOS Outputs)

Table 10. MPC9865 Pin Diagram (Top View)

|   | 1          | 2          | 3        | 4        | 5        | 6        | 7          | 8        | 9               | 10         |

|---|------------|------------|----------|----------|----------|----------|------------|----------|-----------------|------------|

| Α | $V_{DDOA}$ | $V_{DDOA}$ | CLKA[1]  | CLKA[3]  | CLKA[5]  | $V_{DD}$ | QA1        | QA2      | $V_{DDOA}$      | $V_{DDOA}$ |

| В | $V_{DDOA}$ | $V_{DDOA}$ | CLKA[0]  | CLKA[2]  | CLKA[4]  | QA0      | $V_{DDOA}$ | QA3      | $V_{DDOA}$      | $V_{DDOA}$ |

| С | RSVD       | RSVD       | $V_{DD}$ | $V_{DD}$ | $V_{DD}$ | $V_{DD}$ | $V_{DD}$   | $V_{DD}$ | $V_{DD}$        | REF_OUT[0] |

| D | $V_{DDA}$  | $V_{DDA}$  | $V_{DD}$ | GND      | GND      | GND      | GND        | $V_{DD}$ | RSVD            | REF_OUT[1] |

| Е | XTAL_SEL   | CLK        | $V_{DD}$ | GND      | GND      | GND      | GND        | $V_{DD}$ | V <sub>DD</sub> | GND        |

| F | PCLK       | PCLK       | $V_{DD}$ | GND      | GND      | GND      | GND        | $V_{DD}$ | RSVD            | RSVD       |

| G | CLK_SEL    | REF_33MHz  | $V_{DD}$ | GND      | GND      | GND      | GND        | $V_{DD}$ | PLL_BYPASS      | MR         |

| н | XTAL_IN    | XTAL_OUT   | $V_{DD}$ | $V_{DD}$ | $V_{DD}$ | $V_{DD}$ | $V_{DD}$   | $V_{DD}$ | RSVD            | REF_OUT1E  |

| J | $V_{DDOB}$ | $V_{DDOB}$ | CLKB[0]  | CLKB[2]  | CLKB[4]  | QB0      | $V_{DDOB}$ | QB3      | $V_{DDOB}$      | $V_{DDOB}$ |

| ĸ | $V_{DDOB}$ | $V_{DDOB}$ | CLKB[1]  | CLKB[3]  | CLKB[5]  | $V_{DD}$ | QB1        | QB2      | $V_{DDOB}$      | $V_{DDOB}$ |

Table 11. MPC9865 Pin List

| Signal            | 100 Pin<br>MAPBGA | Signal    | 100 Pin<br>MAPBGA | Signal   | 100 Pin<br>MAPBGA | Signal     | 100 Pin<br>MAPBGA | Signal     | 100 Pin<br>MAPBGA |

|-------------------|-------------------|-----------|-------------------|----------|-------------------|------------|-------------------|------------|-------------------|

| V <sub>DDOA</sub> | A1                | RSVD      | C1                | XTAL_SEL | E1                | CLK_SEL    | G1                | $V_{DDOB}$ | J1                |

| V <sub>DDOA</sub> | A2                | RSVD      | C2                | CLK      | E2                | REF_33MHz  | G2                | $V_{DDOB}$ | J2                |

| CLKA[1]           | А3                | $V_{DD}$  | C3                | $V_{DD}$ | E3                | $V_{DD}$   | G3                | CLKB[0]    | J3                |

| CLKA[3]           | A4                | $V_{DD}$  | C4                | GND      | E4                | GND        | G4                | CLKB[2]    | J4                |

| CLKA[5]           | A5                | $V_{DD}$  | C5                | GND      | E5                | GND        | G5                | CLKB[4]    | J5                |

| $V_{DD}$          | A6                | $V_{DD}$  | C6                | GND      | E6                | GND        | G6                | QB0        | J6                |

| QA1               | A7                | $V_{DD}$  | C7                | GND      | E7                | GND        | G7                | $V_{DDOB}$ | J7                |

| QA2               | A8                | $V_{DD}$  | C8                | $V_{DD}$ | E8                | $V_{DD}$   | G8                | QB3        | J8                |

| V <sub>DDOA</sub> | A9                | $V_{DD}$  | C9                | $V_{DD}$ | E9                | PLL_BYPASS | G9                | $V_{DDOB}$ | J9                |

| V <sub>DDOA</sub> | A10               | REF_OUT0  | C10               | GND      | E10               | MR         | G10               | $V_{DDOB}$ | J10               |

| V <sub>DDOA</sub> | B1                | $V_{DDA}$ | D1                | PCLK     | F1                | XTAL_IN    | H1                | $V_{DDOB}$ | K1                |

| V <sub>DDOA</sub> | B2                | $V_{DDA}$ | D2                | PCLK     | F2                | XTAL_OUT   | H2                | $V_{DDOB}$ | K2                |

| CLKA[0]           | В3                | $V_{DD}$  | D3                | $V_{DD}$ | F3                | $V_{DD}$   | H3                | CLKB[1]    | К3                |

| CLKA[2]           | B4                | GND       | D4                | GND      | F4                | $V_{DD}$   | H4                | CLKB[3]    | K4                |

| CLKA[4]           | B5                | GND       | D5                | GND      | F5                | $V_{DD}$   | H5                | CLKB[5]    | K5                |

| QA0               | B6                | GND       | D6                | GND      | F6                | $V_{DD}$   | H6                | $V_{DD}$   | K6                |

| V <sub>DDOA</sub> | B7                | GND       | D7                | GND      | F7                | $V_{DD}$   | H7                | QB1        | K7                |

| QA3               | B8                | $V_{DD}$  | D8                | $V_{DD}$ | F8                | $V_{DD}$   | H8                | QB2        | K8                |

| V <sub>DDOA</sub> | В9                | RSVD      | D9                | RSVD     | F9                | RSVD       | H9                | $V_{DDOB}$ | K9                |

| $V_{DDOA}$        | B10               | REF_OUT1  | D10               | RSVD     | F10               | REF_OUT1_E | H10               | $V_{DDOB}$ | K10               |

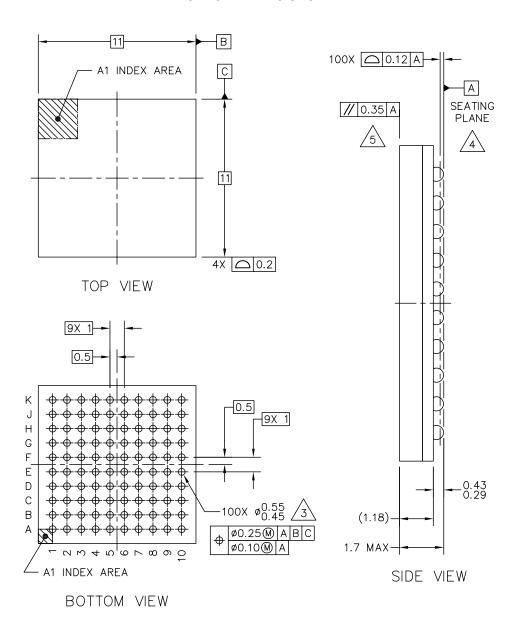

#### **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.             | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: PBGA, LOW PROFILE, 100 I/O, 11 X 11 PKG, 1 MM PITCH (MAP) |           | DOCUMENT NO  | : 98ASA10565D    | REV: A      |

|                                                                  |           | CASE NUMBER  | : 1462-01        | 26 MAY 2005 |

|                                                                  |           | STANDARD: JE | DEC MO-192 DAC-1 |             |

PAGE 1 OF 2

VA SUFFIX VM SUFFIX (PB-FREE) 100 MAPBGA PACKAGE CASE 1462-01 ISSUE A

#### **PACKAGE DIMENSIONS**

#### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO   | OT TO SCALE |

|------------------------------------------------------|--------------------|--------------------|-------------|

| TITLE: PBGA, LOW PROFIL                              | _E, DOCUMENT       | NO: 98ASA10565D    | REV: A      |

| 100 I/O, 11 X 11 P                                   |                    | BER: 1462-01       | 26 MAY 2005 |

| 1 MM PITCH (MAF                                      | STANDARD:          | JEDEC MO-192 DAC-1 |             |

PAGE 2 OF 2

VA SUFFIX VM SUFFIX (PB-FREE) 100 MAPBGA PACKAGE CASE 1462-01 ISSUE A

IDT™ Clock Generator for PowerQUICC III

MPC9865

# Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

For Sales

800-345-7015 408-284-8200

Fax: 408-284-2775

For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA