# PC8477B (SuperFDC™) Advanced Floppy Disk Controller

# **General Description**

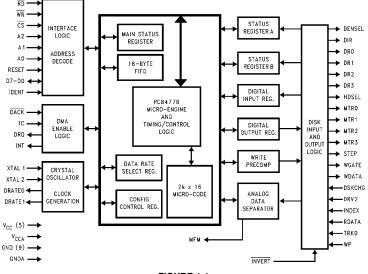

The PC8477B CMOS advanced floppy disk controller is an enhanced version of National's DP8473 floppy controller. The PC8477B is software compatible with the DP8473 and NEC  $\mu$ PD765 floppy disk controllers. In addition, it is pin and software compatible with the Intel 82077AA floppy controller. The PC8477B, a 24 MHz crystal, a device chip select, and a resistor package are all that is needed for a complete PC-AT®, PS/2® or EISA floppy controller solution.

The PC8477B includes advanced features such as a 16 byte FIFO (Burst and Non-Burst modes), support of Perpendicular Recording Mode disk drives, PS/2 diagnostic registers for Model 30 and Models 50/60/80, standard CMOS disk I/O, and additional commands to control these new features. The 16 byte FIFO will increase system performance at higher data rates and with multi-tasking bus structures. This controller is designed to fit into all PC-AT, EISA, and PS/2 designs, as well as other advanced applications.

### **Features**

- Pin and software compatible with Intel 82077AA FDC

- Software compatible with NSC's DP8473

- 16 byte FIFO (default disabled)

- Burst and Non-Burst modes

- Programmable threshold

- Perpendicular Mode Recording drive support

- High performance internal analog data separator (no external filter components required)

- Low power CMOS with manual power down mode

- Automatic power down mode, for complete software transparency

- Integrates all PC-AT, and PS/2 logic

- On chip Oscillator

- PC compatible FDC address decode

- PS/2 Model 30 and Model 50/60/80 diagnostic registers

- DMA control circuitry

- High current CMOS disk interface outputs

- Data Rate and Digital Output registers

- 12 mA μP bus interface buffers

- Data Rate Support: 250/300 kb/s, 500 kb/s, and 1 Mb/s

- Write precompensation software programmable

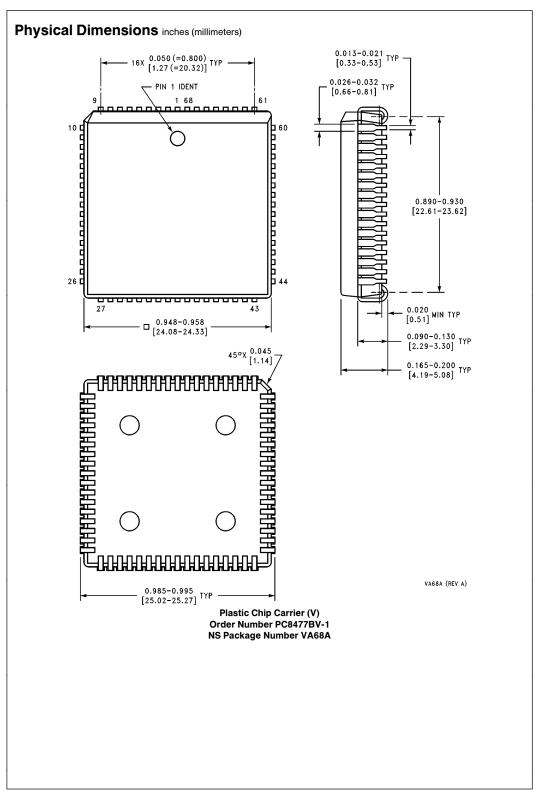

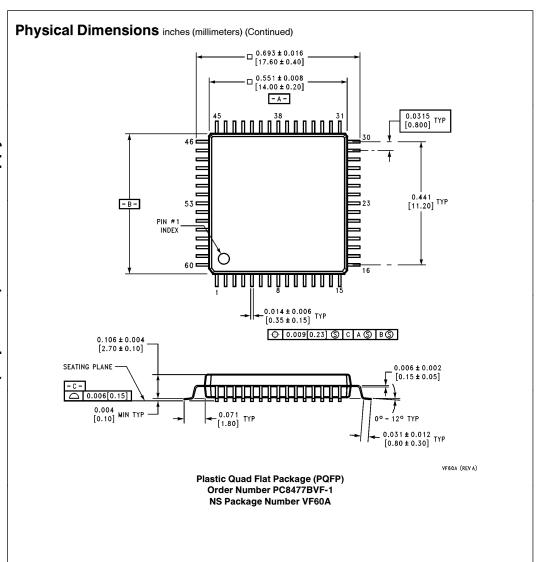

- 68 pin PLCC package

- 60 pin PQFP package Ideal for space limited applications

# **Functional Block Diagram**

FIGURE 1-1

SuperFDCT<sup>M</sup> is a trademark of National Semiconductor Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

IBM®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corp.

© 1995 National Semiconductor Corporation TL/F/1133

RRD-B30M75/Printed in U. S. A.

TL/F/11332-3

# **Table of Contents**

# 1.0 INTRODUCTION 2.0 PIN DESCRIPTION

## 3.0 REGISTER DESCRIPTION

3.1 Status Register A (SRA)

3.1.1 SRA—PS/2 Mode

3.1.2 SRA-Model 30 Mode

3.2 Status Register B (SRB)

3.2.1 SRB-PS/2 Mode

3.2.2 SRB-Model 30 Mode

3.3 Digital Output Register (DOR)

3.4 Tape Drive Register (TDR)

3.5 Main Status Register (MSR)

3.6 Data Rate Select Register (DSR)

3.7 Data Register (FIFO)

3.8 Digital Input Register (DIR)

3.8.1 DIR-PC-AT Mode

3.8.2 DIR-PS/2 Mode

3.8.3 DIR-Model 30 Mode

3.9 Configuration Control Register (CCR)

3.9.1 CCR-PC-AT and PS/2 Modes

3.9.2 CCR-Model 30 Mode

3.10 Result Phase Status Registers

3.10.1 Status Register 0 (ST0)

3.10.2 Status Register 1 (ST1)

3.10.3 Status Register 2 (ST2)

3.10.4 Status Register 3 (ST3)

## 4.0 COMMAND SET DESCRIPTION

4.1 Command Set Summary

4.2 Command Description

4.2.1 Configure Command

4.2.2 Dumpreg Command

4.2.3 Format Command

4.2.4 Invalid Command

4.2.5 Lock Command

4.2.6 Mode Command

4.2.7 NSC Command

4.2.8 Perpendicular Mode Command

4.2.9 Read Data Command

4.2.10 Read Deleted Data Command

4.2.11 Read ID Command

4.2.12 Read A Track Command

4.2.13 Recalibrate Command

4.2.14 Relative Seek Command

4.2.15 Scan Commands

4.2.16 Seek Command

4.2.17 Sense Drive Status Command

4.2.18 Sense Interrupt Command

4.2.19 Set Track Command

4.2.20 Specify Command

4.2.21 Verify Command

4.2.22 Version Command

4.2.23 Write Data Command

4.2.24 Write Deleted Data Command

#### **5.0 FUNCTIONAL DESCRIPTION**

5.1 Microprocessor Interface

5.2 Modes of Operation

5.3 Controller Phases

5.3.1 Command Phase

5.3.2 Execution Phase

5.3.2.1 DMA Mode—FIFO Disabled

5.3.2.2 DMA Mode—FIFO Enabled

5.3.2.3 Interrupt Mode—FIFO Disabled

5.3.2.4 Interrupt Mode—FIFO Enabled

5.3.2.5 Software Polling

5.3.3 Result Phase

5.3.4 Idle Phase

5.3.5 Drive Polling Phase

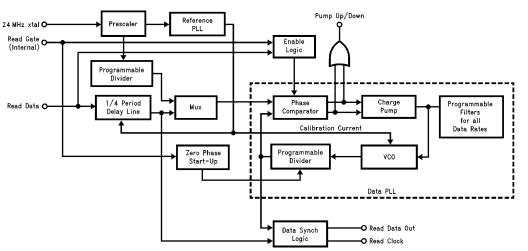

5.4 Data Separator

5.5 Crystal Oscillator

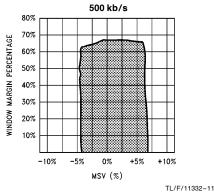

5.6 Dynamic Window Margin Performance

5.7 Perpendicular Recording Mode

5.8 Data Rate Selection

5.9 Write Precompensation

5.10 Low Power Mode Logic

5.11 Reset Operation

# 6.0 DEVICE DESCRIPTION

6.1 DC Electrical Characteristics

6.2 AC Electrical Characteristics

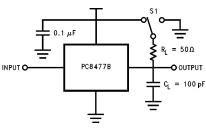

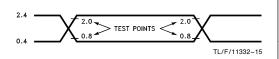

6.2.1 AC Test Conditions

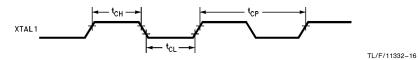

6.2.2 Clock Timing

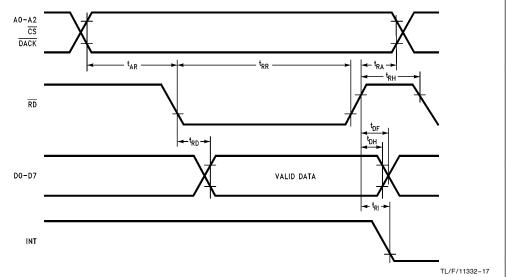

6.2.3 Microprocessor Read Timing

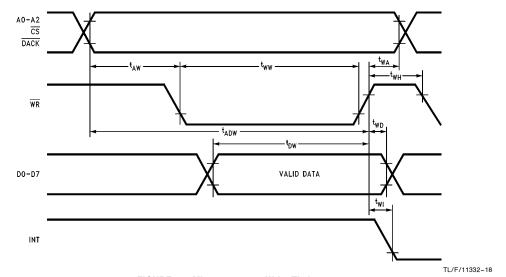

6.2.4 Microprocessor Write Timing

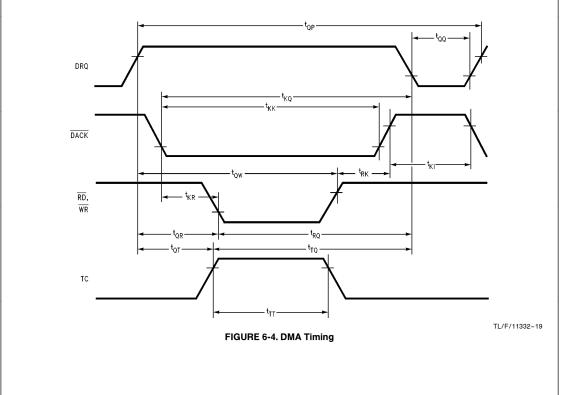

6.2.5 DMA Timing

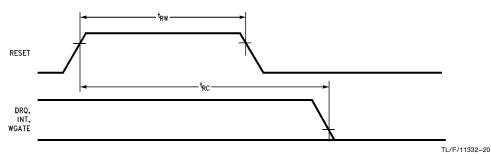

6.2.6 Reset Timing

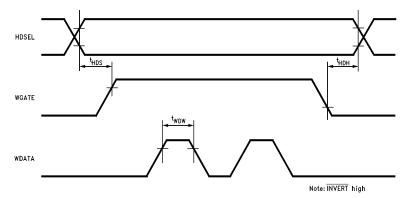

6.2.7 Write Data Timing

6.2.8 Drive Control Timing

6.2.9 Read Data Timing

## 7.0 REFERENCE SECTION

7.1 Mnemonic Definitions for PC8477B Commands

7.2 PC8477B Enhancements vs. 82077AA

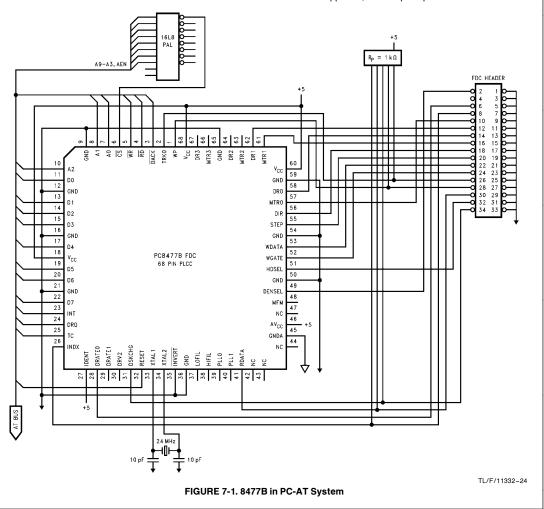

7.3 PC8477B Interface in a PC-AT

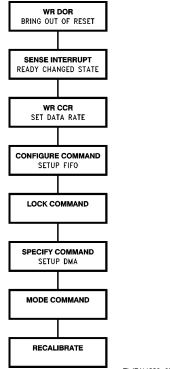

7.4 Software Initialization Sequence

7.5 PC8477B/PC8477A differences

7.6 Revision History

| List of Figures                                                  |

|------------------------------------------------------------------|

| PC8477B Functional Block Diagram                                 |

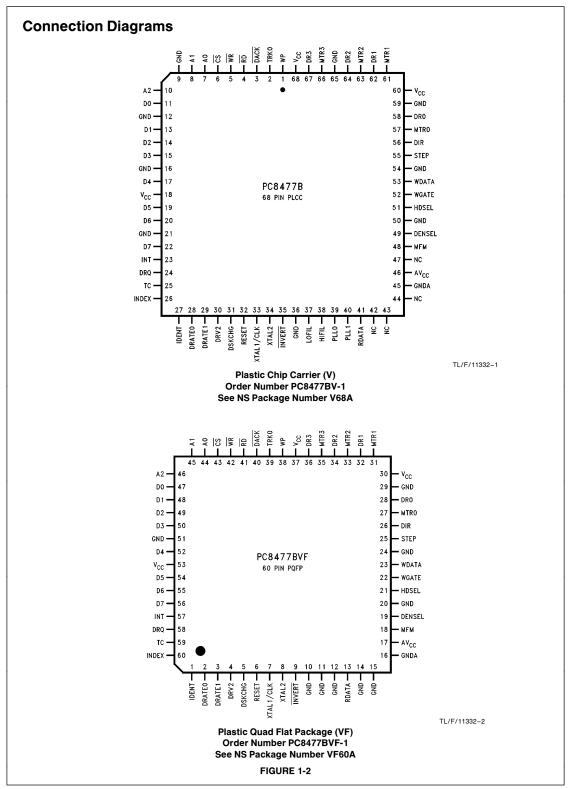

| PC8477B Pin Diagram for 68 Pin PLCC and 60 Pin PQFP              |

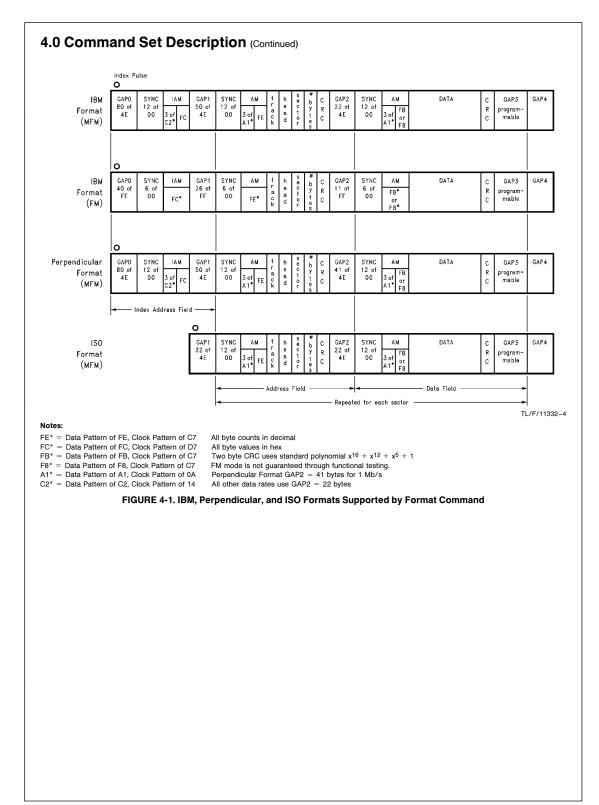

| IBM®, Perpendicular, and ISO Formats Supported by Format Command |

| PC8477B Data Separator Block Diagram5-1                          |

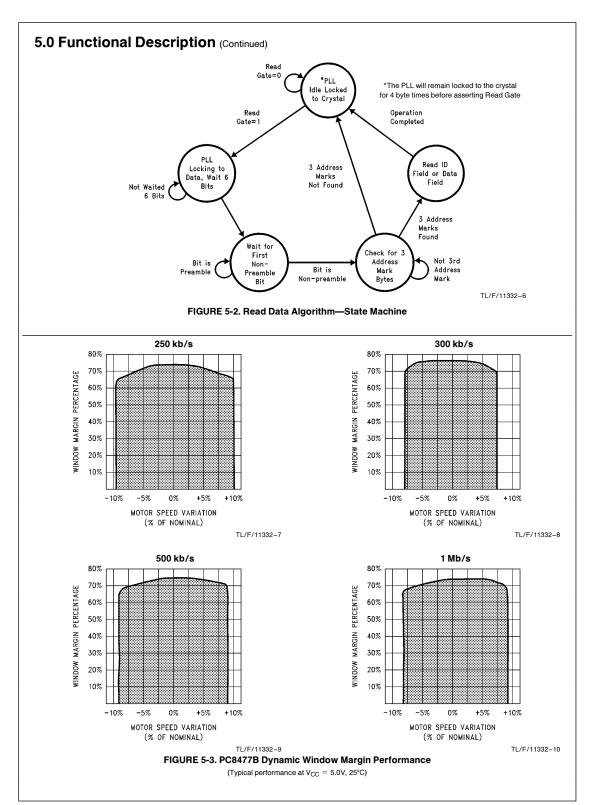

| Read Data Algorithm—State Diagram5-2                             |

| PC8477B Dynamic Window Margin Performance5-3                     |

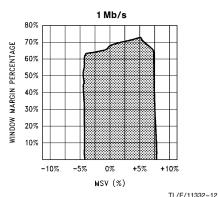

| PC8477B Dynamic Window Margin Performance with ±3% ISV           |

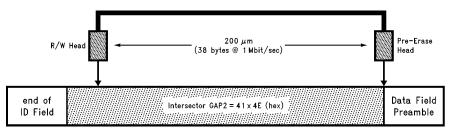

| Perpendicular Recording Drive R/W Head and Pre-Erase Head        |

| Clock Timing                                                     |

| Microprocessor Read Timing                                       |

| Microprocessor Write Timing                                      |

| DMA Timing                                                       |

| Reset Timing                                                     |

| Write Data Timing                                                |

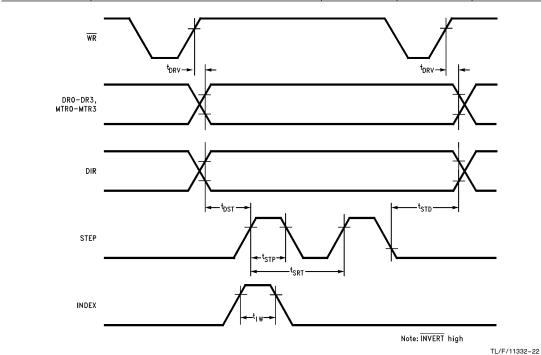

| Drive Control Timing                                             |

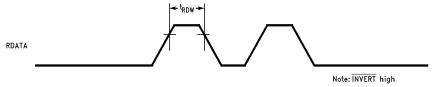

| Read Data Timing                                                 |

| PC8477B in a PC-AT System                                        |

| PC84777B Initialization                                          |

|                                                                  |

|                                                                  |

| List of Tables                                                   |

| Register Description and Addresses                               |

| Drive Enable Values                                              |

| Tape Drive Assignment Values                                     |

| Write Precompensation Delays                                     |

| Default Precompensation Delays                                   |

| Data Rate Select Encoding                                        |

| Typical Format Gap Length Values4-1                              |

| DENSEL Encoding4-2                                               |

| DENSEL Default Encoding4-3                                       |

| Effects of WGATE and GAP4-4                                      |

| Sector Size Selection                                            |

| SK Effect of Read Data Command                                   |

| Result Phase Termination Values with No Error4-7                 |

| SK Effect on Read Deleted Data Command4-8                        |

| Maximum Recalibrate Step Pulses Based on R255 and ETR            |

| Scan Command Termination Values                                  |

| Status Register 0 Termination Codes                              |

| Set Track Register Address                                       |

| Step Rate (SRT) Values         4-13                              |

| Motor Off Time (MFT) Values                                      |

| Motor On Time (MNT) Values                                       |

| Verify Command Result Phase Table4-16                            |

| Nominal t <sub>ICP</sub> , t <sub>DRP</sub> Values               |

| Minimum t <sub>WDW</sub> Values                                  |

| PC8477B-82077 Parameter Comparison                               |

| Density Encoding                                                 |

|                                                                  |

|                                                                  |

|                                                                  |

|                                                                  |

# 1.0 Introduction

The PC8477B advanced floppy disk controller is suitable for all PC-AT, EISA, PS/2, and general purpose applications. The operational mode (PC-AT, PS/2, and Model 30) of the PC8477B is determined by hardware strapping of the IDENT and MFM pins. DP8473 and Intel 82077AA software compatibility is provided. Key features include the 16 byte FIFO, PS/2 diagnostic register support, the perpendicular recording mode, CMOS disk interface, and a high performance analog data separator.

The PC8477B supports the standard PC data rates of 250, 300, 500 kb/s, and 1 Mb/s in MFM encoded data mode, but is no longer guaranteed through functional testing to support the older FM encoded data mode. References to the older FM mode remain in this document to clarify the true functional operation of the device.

The 1 Mb/s data rate is used by new high performance tape and floppy drives emerging in the PC market today. The new floppy drives utilize high density media which requires the PC8477B supported perpendicular recording mode format. When used with the 1 Mb/s data rate this new format allows the use of 4 Mb floppy drives which format ED media to 2.88 MB data capacity.

The high performance internal analog data separator needs no external components. It improves on the window margin performance standards of the DP8473, and is compatible with the strict data separator requirements of floppy and floppy-tape drives.

The PC8477B contains write precompensation and circuitry that will default to 125 ns for 250, 300, and 500 kb/s, 41.67 ns at 1 Mb/s. These values can be overridden through software to disable write precompensation or to provide levels of precompensation up to 250 ns. The PC8477B has internal 12 mA data bus buffers which allow direct connection to the system bus. The internal 48 mA totem-pole disk interface buffers are compatible with both CMOS drive inputs and  $150\Omega$  resistor terminated disk drive inputs.

The PC8477B is available in a 68 pin Plastic Leaded Chip Carrier (PLCC) package, and in a 60 pin Plastic Quad Flat Package (PQFP).

| Symbol                                 | PLCC<br>Pin                                   | PQFP<br>Pin                                    | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------|-----------------------------------------------|------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0<br>A1<br>A2                         | 7<br>8<br>10                                  | 44<br>45<br>46                                 | I   | Address. These address lines from the microprocessor determine which internal FDC register is accessed. See TABLE 3-1 in the Register Description section. A0–A2 are don't cares during a DMA transfer.                                                                                                                                                                                                                                                                          |

| AVCC                                   | 46                                            | 17                                             |     | Analog Supply. This pin is the 5V supply for the analog data separator.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CS                                     | 6                                             | 43                                             | ı   | Chip Select. Active low input from address decoder used to enable the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ inputs during register I/O. Should be held inactive during DMA transfers.                                                                                                                                                                                                                                                                                |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6 | 11<br>13<br>14<br>15<br>17<br>19<br>20<br>22  | 47<br>48<br>49<br>50<br>52<br>54<br>55         | 1/0 | <b>Data.</b> Bi-directional data lines to the microprocessor. D0 is the LSB and D7 is the MSB. These signals all have 12 mA buffered outputs.                                                                                                                                                                                                                                                                                                                                    |

| DACK                                   | 3                                             | 40                                             | ı   | DMA Acknowledge. Active low input to acknowledge the DMA request and enable the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ inputs during a DMA transfer. $\overline{\text{DACK}}$ should be held inactive high during normal reaction write accesses when $\overline{\text{CS}}$ is active. When in PC-AT or Model 30 mode, this signal is enabled by bit D3 of the DOR. When in PS/2 mode, $\overline{\text{DAK}}$ is always enabled, and bit D3 of the DOR is reserved. |

| DENSEL                                 | 49                                            | 19                                             | 0   | Density Select. Indicates when a high density data rate (500 kb/s or 1 Mb/s) or a low density data rate (250 or 300 kb/s) has been selected. DENSEL is active high for high density (5.25" drives) when IDENT is high, and active low for high density (3.5" drives) when IDENT is low. DENSEL is also programmable via the Mode command (see Section 4.2.6).                                                                                                                    |

| DIR                                    | 56                                            | 26                                             | 0   | <b>Direction.</b> This output determines the direction of the head movement (active = step in, inactive = step out) during a seek operation. During read or writes, DIR will be inactive.                                                                                                                                                                                                                                                                                        |

| DR0<br>DR1<br>DR2<br>DR3               | 58<br>62<br>64<br>67                          | 28<br>32<br>34<br>36                           | 0   | <b>Drive Select 0–3.</b> These are the decoded drive select outputs that are controlled by Digital Output Register bits D0, D1. The Drive Select outputs are gated by DOR bits 4–7.                                                                                                                                                                                                                                                                                              |

| DRATE0<br>DRATE1                       | 28<br>29                                      | 2                                              | 0   | <b>Data Rate 0,1.</b> These outputs reflect the currently selected data rate, (bits 0 and 1 in the CCR or the DSR, whichever was written to last). These pins are totem-pole buffered outputs (6 mA sink, 4 mA source).                                                                                                                                                                                                                                                          |

| DRQ                                    | 24                                            | 58                                             | 0   | <b>DMA Request.</b> Active high output to signal the DMA controller that a data transfer is needed. When in PC-AT or Model 30 mode, this signal is enabled by bit D3 of the DOR. When in PS/2 mode, DRQ is always enabled, and bit D3 of the DOR is reserved.                                                                                                                                                                                                                    |

| DRV2                                   | 30                                            | 4                                              | ı   | <b>Drive2.</b> This input indicates whether a second disk drive has been installed. The state of this pin is available from Status Register A in PS/2 mode.                                                                                                                                                                                                                                                                                                                      |

| DSKCHG                                 | 31                                            | 5                                              | I   | <b>Disk Change.</b> The input indicates if the drive door has been opened. The state of this pin is available from the Digital Input register. This pin can also be configured as the RGATE data separator diagnostic input via the Mode command (see Section 4.2.6).                                                                                                                                                                                                            |

| GND                                    | 9, 12,<br>16, 21,<br>36, 50,<br>54, 59,<br>65 | 10, 11,<br>12, 14,<br>15, 20,<br>24, 29,<br>51 |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GNDA                                   | 45                                            | 16                                             |     | Analog Ground. This is the analog ground for the data separator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Symbol | PLCC<br>Pin | PQFP<br>Pin | 1/0      |                                                                       | Function                                                                                                                                                                                                                                                                                                                                    |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

|--------|-------------|-------------|----------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

| HDSEL  | 51          | 21          | 0        |                                                                       | <b>Head Select.</b> This output determines which side of the disk drive is accessed. Active selects side 1, inactive selects side 0.                                                                                                                                                                                                        |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| HIFIL  | 38          | (Note 1)    |          | _                                                                     | connect. No external c<br>it will have no effect or                                                                                                                                                                                                                                                                                         |                                                                                           | An external capacitor can be performance.                                                                                                                                                                                             |                                       |  |  |  |

| IDENT  | 27          | 1           | ı        |                                                                       | chip reset, the IDENT<br>ding to the following ta                                                                                                                                                                                                                                                                                           | •                                                                                         | ampled to determine the mode of                                                                                                                                                                                                       | -                                     |  |  |  |

|        |             |             |          |                                                                       | IDENT                                                                                                                                                                                                                                                                                                                                       | MFM                                                                                       | Mode                                                                                                                                                                                                                                  |                                       |  |  |  |

|        |             | '           |          |                                                                       | 1                                                                                                                                                                                                                                                                                                                                           | 1 or NC                                                                                   | PC-AT Mode                                                                                                                                                                                                                            |                                       |  |  |  |

|        | 1           | '           |          |                                                                       | 1                                                                                                                                                                                                                                                                                                                                           | 0                                                                                         | Illegal                                                                                                                                                                                                                               |                                       |  |  |  |

| ļ      | 1           | '           | '        |                                                                       | 0                                                                                                                                                                                                                                                                                                                                           | 1 or NC                                                                                   | PS/2 Mode                                                                                                                                                                                                                             |                                       |  |  |  |

|        | 1           | '           |          |                                                                       | 0                                                                                                                                                                                                                                                                                                                                           | 0                                                                                         | Model 30 Mode                                                                                                                                                                                                                         |                                       |  |  |  |

|        |             |             |          | are disabled (TR                                                      | RI-STATE®).                                                                                                                                                                                                                                                                                                                                 |                                                                                           | active high. Status Registers A and                                                                                                                                                                                                   |                                       |  |  |  |

|        |             |             |          | and B are enable                                                      |                                                                                                                                                                                                                                                                                                                                             | t in the DOH is valid.                                                                    | TC is active high. Status Register                                                                                                                                                                                                    | SA                                    |  |  |  |

| ,      |             |             |          |                                                                       | he DMA enable bit in t<br>led. TC is active low. S                                                                                                                                                                                                                                                                                          |                                                                                           | re, and the DRQ and INT signals vid B are enabled.                                                                                                                                                                                    | will                                  |  |  |  |

|        |             | '           |          |                                                                       | After chip reset, the state of IDENT determines the polarity of the DENSEL output.                                                                                                                                                                                                                                                          |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

|        | 1           | '           |          |                                                                       | When IDENT is a logic "1", DENSEL is active high for 500 kb/s and 1 Mb/s data rates.                                                                                                                                                                                                                                                        |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

|        | 1           | '           |          |                                                                       | When IDENT is a logic "0", DENSEL is active low for 500 kb/s and 1 Mb/s data rates.                                                                                                                                                                                                                                                         |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

|        |             | <b></b> '   | <u> </u> | ,                                                                     | See Mode command for further explanation of DENSEL.)                                                                                                                                                                                                                                                                                        |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| INDEX  | 26          | 60          | I        | -                                                                     | ndex. This input signals the beginning of a track.                                                                                                                                                                                                                                                                                          |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| INT    | 23          | 57          | 0        | commands. Also<br>in PC-AT or Mod                                     | Interrupt. Active high output to signal the completion of the execution phase for certain commands. Also used to signal when a data transfer is ready during a Non-DMA operation. When in PC-AT or Model 30 mode, this signal is enabled by bit D3 of the DOR. When in PS/2 mode, INT is always enabled, and bit D3 of the DOR is reserved. |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| INVERT | 35          | 9           | -        | buffers and inve                                                      | erting Schmitt input rec<br>nigh, the disk interface                                                                                                                                                                                                                                                                                        | eivers are enabled, a                                                                     | When tied low, the internal disk o<br>and the disk interface signals are a<br>gh, and external receivers and ou                                                                                                                       | active                                |  |  |  |

| LOFIL  | 37          | (Note 1)    |          |                                                                       | connect. No external c<br>it will have no effect or                                                                                                                                                                                                                                                                                         |                                                                                           | An external capacitor can be performance.                                                                                                                                                                                             |                                       |  |  |  |

| MFM    | 48          | 18          | 1/0      | mode (MFM high 10 k $\Omega$ resistor w high), MFM show when RESET is | h), or the Model 30 mo<br>vill select between the<br>uld be left pulled high i<br>inactive. MFM = high                                                                                                                                                                                                                                      | ode (MFM low). An in<br>two PS/2 modes. W<br>nternally. MFM refle<br>, FM = low. Defaults | , this pin is sampled to select the I<br>ternal pull-up or external pull-dow<br>hen the PC-AT mode is desired (II<br>cts the current data encoding form<br>is to low after a chip reset. This sig<br>ostic output via the Mode comman | /n<br>DEN <sup>-</sup><br>nat<br>ınal |  |  |  |

| MTR0   | 57          | 27          | 0        | Motor Select 0                                                        | -3 These are the mot                                                                                                                                                                                                                                                                                                                        | or enable lines for dr                                                                    | rives 0-3, and are controlled by bi                                                                                                                                                                                                   | its D                                 |  |  |  |

| MTR1   | 61          | 31          | `        | D4 of the Digital                                                     |                                                                                                                                                                                                                                                                                                                                             | 01 0114010                                                                                | 1, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4, 4,                                                                                                                                                                                             |                                       |  |  |  |

| MTR2   | 63          | 33          |          | D                                                                     | Output tog                                                                                                                                                                                                                                                                                                                                  |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| MTR3   | 66          | 35          |          |                                                                       |                                                                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| NC     | 42          | (Note 1)    |          | No Connect. Th                                                        | nese pins must be left                                                                                                                                                                                                                                                                                                                      | unconnected.                                                                              |                                                                                                                                                                                                                                       |                                       |  |  |  |

|        | 43          |             |          |                                                                       | 1000 p                                                                                                                                                                                                                                                                                                                                      |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| ļ      | 44          | '           |          |                                                                       |                                                                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

| ļ      | 47          | '           |          | 1                                                                     |                                                                                                                                                                                                                                                                                                                                             |                                                                                           |                                                                                                                                                                                                                                       |                                       |  |  |  |

# 2.0 Pin Description (Continued)

| Symbol          | PLCC<br>Pin    | PQFP<br>Pin    | 1/0 | Function                                                                                                                                                                                                                                                                                                     |

|-----------------|----------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL0<br>PLL1    | 39<br>40       | (Note 1)       |     | Phase Locked Loop 0,1. No connects. These pins can be tied high or low with no affect on the data separator performance.                                                                                                                                                                                     |

| RD              | 4              | 41             | 1   | Read. Active low input to signal a read from the controller to the microprocessor.                                                                                                                                                                                                                           |

| RDATA           | 41             | 13             | I   | Read Data. This input is the raw serial data read from the disk drive.                                                                                                                                                                                                                                       |

| RESET           | 32             | 6              | I   | Reset. Active high input that resets the controller to the idle state, and resets all disk interface outputs to their inactive states. The DOR, DSR, CCR, Mode command, Configure command, and Lock command parameters are cleared to their default values. The Specify command parameters are not affected. |

| STEP            | 55             | 25             | 0   | <b>Step.</b> This output signal issues pulses to the disk drive at a software programmable rate to move the head during a seek operation.                                                                                                                                                                    |

| TC              | 25             | 59             | .   | <b>Terminal Count.</b> Control signal from the DMA controller to indicate the termination of a DMA transfer. TC is accepted only when DACK is active. TC is active high in PC-AT and Model 30 modes, and active low in PS/2 mode.                                                                            |

| TRK0            | 2              | 39             | I   | <b>Track 0.</b> This input indicates to the controller that the head of the selected disk drive is at track zero.                                                                                                                                                                                            |

| V <sub>CC</sub> | 18<br>60<br>68 | 30<br>37<br>53 |     | <b>Voltage.</b> This is the $+5V$ supply voltage for the digital circuitry.                                                                                                                                                                                                                                  |

| WDATA           | 53             | 23             | 0   | Write Data. This output is the write precompensated serial data that is written to the selected disk drive. Precompensation is software selectable.                                                                                                                                                          |

| WGATE           | 52             | 22             | 0   | Write Gate. This output signal enables the write circuitry of the selected disk drive.  WGATE has been designed to prevent glitches during power up and power down. This prevents writing to the disk when power is cycled.                                                                                  |

| WP              | 1              | 38             | ı   | Write Protect. This input indicates that the disk in the selected drive is write protected.                                                                                                                                                                                                                  |

| WR              | 5              | 42             | I   | Write. Active low input to signal a write from the microprocessor to the controller.                                                                                                                                                                                                                         |

| XTAL1/CLK       | 33             | 7              | I   | Crystal1/Clock. One side of an external 24 MHz crystal is attached here. If a crystal is not used, a TTL or CMOS compatible clock is connected to this pin.                                                                                                                                                  |

| XTAL2           | 34             | 8              | I   | Crystal2. One side of an external 24 MHz crystal is attached here. This pin is left unconnected if an external clock is used.                                                                                                                                                                                |

Note 1: When converting the 68 pin PLCC to a 60 pin PQFP, eight pins were removed. The following signals were affected in this conversion process:

- 2. NC (No Connect) signals on pins 44 and 47 of the 68 pin PLCC were removed for the 60 pin PQFP.

- 3. HIFIL (pin 38) and LOFIL (pin 37) of the 68 pin PLCC were removed for the 60 pin PQFP.

- 4. PLL0 (pin 39) and PLL1 (pin 40) of the 68 PLCC were converted to GND (ground) signals on the PQFP (pins 11 and 12 respectively).

- 5. The GND (ground) signals on pins 9, 12, 21, and 65 of the 68 pin PLCC are not available for the 60 pin PQFP. These signals are tied to ground internally.

<sup>1.</sup> NC (No Connect) signals on pins 42 and 43 of the 68 pin PLCC were converted to GND (Ground) signals on pins 14 and 15 of the 60 pin PQFP, respectively.

# 3.0 Register Description

The following PC8477B registers are mapped into the addresses shown below, with the base address range being provided by the  $\overline{\text{CS}}$  pin. For PC-AT or PS/2 applications, the diskette controller primary address range is 3F0 to 3F7 (hex), and the secondary address range is 370 to 377 (hex). The PC8477B supports three different register modes: the

PC-AT mode, PS/2 mode (Models 50/60/80), and the Model 30 mode (Model 30). See Section 5.1 for more details on how each register mode is enabled. When applicable, the register definition for each mode of operation will be given. If no special notes are made, then the register is valid for all three register modes.

**TABLE 3-1. Register Description and Addresses**

| A2 | A1 | A0 | IDENT | R/W | Register                          |      |  |

|----|----|----|-------|-----|-----------------------------------|------|--|

| 0  | 0  | 0  | 0     | R   | Status Register A                 | SRA  |  |

| 0  | 0  | 1  | 0     | R   | Status Register B                 | SRB  |  |

| 0  | 1  | 0  | X     | R/W | Digital Output Register           | DOR  |  |

| 0  | 1  | 1  | X     | R/W | Tape Drive Register               | TDR  |  |

| 1  | 0  | 0  | X     | R   | Main Status Register              | MSR  |  |

| 1  | 0  | 0  | X     | W   | Data Rate Select Register         | DSR  |  |

| 1  | 0  | 1  | X     | R/W | Data Register (FIFO)              | FIFO |  |

| 1  | 1  | 0  | X     | Х   | None (Bus TRI-STATE)              |      |  |

| 1  | 1  | 1  | X     | R   | Digital Input Register            | DIR  |  |

| 1  | 1  | 1  | X     | W   | Configuration Control Register CO |      |  |

Note: SRA and SRB are enabled by IDENT = 0 during a chip reset only.

#### 3.1 STATUS REGISTER A (SRA) Read Only

This is a read only diagnostic register that is part of the PS/2 floppy controller register set, and is enabled when in the PS/2 or Model 30 mode. This register monitors the state of the INT pin and some of the disk interface signals. The state of these bits is independent of the  $\overline{\text{INVERT}}$  pin. The SRA can be read at any time when in PS/2 mode. In the PC-AT mode, D7–D0 are TRI-STATE during a  $\mu P$  read.

#### 3.1.1 SRA-PS/2 Mode

|               | D7          | D6   | D5   | D4   | D3    | D2   | D1  | D0  |

|---------------|-------------|------|------|------|-------|------|-----|-----|

| DESC          | INT<br>PEND | DRV2 | STEP | TRK0 | HDSEL | ĪNDX | WP  | DIR |

| RESET<br>COND | 0           | N/A  | 0    | N/A  | 0     | N/A  | N/A | 0   |

- **D7** Interrupt Pending: This active high bit reflects the state of the INT pin.

- D6 2nd Drive Installed: Active low status of the DRV2 disk interface input, indicating if a second drive has been installed.

- **Step:** Active high status of the STEP disk interface output.

- **Track 0:** Active low status of the TRK0 disk interface input.

- D3 Head Select: Active high status of the HDSEL disk interface output.

- D2 Index: Active low status of the INDEX disk interface input.

- **Write Protect:** Active low status of the WP disk interface input.

- **Direction:** Active high status of the DIR disk interface output.

#### 3.1.2 SRA— Model 30 Mode

|       | D7          | D6  | D5   | D4   | D3    | D2   | D1  | D0  |

|-------|-------------|-----|------|------|-------|------|-----|-----|

| DESC  | INT<br>PEND | DRQ | STEP | TRK0 | HDSEL | INDX | WP  | DIR |

| RESET | 0           | 0   | 0    | N/A  | 1     | N/A  | N/A | 1   |

- D7 Interrupt Pending: This active high bit reflects that state of the INT pin.

- D6 DMA Request: Active high status of the DRQ signal.

- D5 Step: Active high status of the latched STEP disk interface output. This bit is latched with the STEP output going active, and is cleared with a read from the DIR, or with a hardware or software reset.

- **Track 0:** Active high status of TRK0 disk interface input.

- D3 Head Select: Active low status of the HDSEL disk interface output.

- D2 Index: Active high status of the INDEX disk interface input.

- D1 Write Protect: Active high status of the WP disk interface input.

- Direction: Active low status of the DIR disk interface output.

# 3.2 STATUS REGISTER B (SRB) Read Only

This is a read only diagnostic register that is part of the PS/2 floppy controller register set, and is enabled when in the PS/2 or Model 30 mode. The state of these bits is independent of the  $\overline{\text{INVERT}}$  pin. The SRB can be read at any time when in PS/2 mode. In the PC-AT mode, D7–D0 are TRI-STATE during a  $\mu\text{P}$  read.

#### 3.2.1 SRB-PS/2 Mode

|       | D7  | D6  | D5  | D4    | D3    | D2    | D1   | D0   |

|-------|-----|-----|-----|-------|-------|-------|------|------|

| DESC  | 1   | 1   | DR0 | WDATA | RDATA | WGATE | MTR1 | MTRO |

| RESET | N/A | N/A | 0   | 0     | 0     | 0     | 0    | 0    |

D7 Reserved: Always 1.

D6 Reserved: Always 1.

Drive Select 0: Reflects the status of the Drive Select 0 bit in the DOR (address 2, bit 0). This bit is cleared after a hardware reset, not a software reset.

D4 Write Data: Every inactive edge transition of the WDATA disk interface output causes this bit to change states.

D3 Read Data: Every positive edge transition of the RDATA disk interface output causes this bit to change states.

**D2** Write Gate: Active high status of the WGATE disk interface output.

D1 Motor Enable 1: Active high status of the MTR1 disk interface output. Low after a hardware reset, unaffected by a software reset.

D0 Motor Enable 0: Active high status of the MTR0 disk interface output. Low after a hardware reset, unaffected by a software reset.

#### 3.2.2 SRB-Model 30 Mode

|       | D7   | D6  | D5  | D4    | D3    | D2    | D1  | D0  |

|-------|------|-----|-----|-------|-------|-------|-----|-----|

| DESC  | DRV2 | DR1 | DR0 | WDATA | RDATA | WGATE | DR3 | DR2 |

| RESET | N/A  | 1   | 1   | 0     | 0     | 0     | 1   | 1   |

**2nd Drive Installed**: Active low status of the DRV2 disk interface input.

Drive Select 1: Active low status of the DR1 disk interface output.

**Drive Select 0:** Active low status of the DR0 disk interface output.

D4 Write Data: Active high status of latched WDATA signal. This bit is latched by the inactive going edge of WDATA and is cleared by a read from the DIR. This bit is not gated by WGATE

D3 Read Data: Active high status of latched RDATA signal. This bit is latched by the inactive going edge of RDATA and is cleared by a read from the DIR.

D2 Write Gate: Active high status of latched WGATE signal. This bit is latched by the active going edge of WGATE and is cleared by a read from the DIR.

D1 Drive Select 3: Active low status of the DR3 disk interface output.

Do Drive Select 2: Active low status of the DR2 disk interface output.

#### 3.3 DIGITAL OUTPUT REGISTER (DOR) Read/Write

The DOR controls the drive select and motor enable disk interface outputs, enables the DMA logic, and contains a software reset bit. The contents of the DOR are set to 00 (hex) after a hardware reset, and are unaffected by a software reset. The DOR can be written to at any time.

#### DOR

|               | D7   | D6   | D5   | D4   | D3    | D2    | D1             | D0             |

|---------------|------|------|------|------|-------|-------|----------------|----------------|

| DESC          | MTR3 | MTR2 | MTR1 | MTR0 | DMAEN | RESET | DRIVE<br>SEL 1 | DRIVE<br>SEL 0 |

| RESET<br>COND | 0    | 0    | 0    | 0    | 0     | 0     | 0              | 0              |

D7 Motor Enable 3: This bit controls the MTR3 disk interface output. A 1 in this bit causes the MTR3 pin to go active. The actual level of MTR3 depends on the state of the INVERT pin.

**Motor Enable 2:** Same function as D7 except for MTR2

**D5 Motor Enable 1:** Same function as D7 except for MTR1.

**D4 Motor Enable 0:** Same function as D7 except for MTR0.

DMA Enable: This bit has two modes of operation. PC-AT mode or Model 30 mode: Writing a 1 to this bit will enable the DRQ, DAK, INT and TC pins. Writing a 0 to this bit will TRI-STATE DRQ and INT, and disable DAK and TC. This bit is a 0 after a reset when in these modes. PS/2 mode: This bit is reserved, and the DRQ, DAK, INT and TC pins will always be enabled. During a reset, the DRQ, DAK, and INT lines will remain enabled, and D3 will be a

D2 Reset Controller: Writing a 0 to this bit resets the controller. It will remain in the reset condition until a 1 is written to this bit. A software reset does not affect the DSR, CCR, and other bits of the DOR. A software reset will affect the Configure and Mode command bits (see Section 4.0 Command Set Description). The minimum time that this bit must be low is 100 ns. Thus, toggling the Reset Controller bit during consecutive writes to the DOR is an acceptable method of issuing a software reset.

D1-D0 Drive Select: These two bits are binary encoded for the four drive selects DR0-DR3, so that only one drive select output is active at a time. The actual level of the drive select outputs is determined by the state of the INVERT pin.

It is common programming practice to enable both the motor enable and drive select outputs for a particular drive. Table 3-2 below shows the DOR values to enable each of the four drives.

TABLE 3-2. Drive Enable Values

| Drive | DOR Value |

|-------|-----------|

| 0     | 1C (Hex)  |

| 1     | 2D        |

| 2     | 4E        |

| 3     | 8F        |

## 3.4 DRIVE REGISTER (TDR) Read/Write

This register is used to assign a particular drive number with the tape drive support mode of the data separator. All other logical drives are assigned floppy drive support with the data separator. Any future reference to the assigned tape drive will invoke tape drive support. The TDR is unaffected by a software reset.

#### TDR

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1           | D0           |

|---------------|-----|-----|-----|-----|-----|-----|--------------|--------------|

| DESC          | х   | Х   | х   | Х   | х   | Х   | TAPE<br>SEL1 | TAPE<br>SEL0 |

| RESET<br>COND | N/A | N/A | N/A | N/A | N/A | N/A | 0            | 0            |

**D7-D2** Reserved: These bits are ignored when written to and are TRI-STATE when read.

D1-D0 Tape Select 1,0: These two bits assign a logical drive number to be a tape drive. Drive 0 is not available as a tape drive, and is reserved as the floppy disk boot drive. See Table 3-3 for the tape drive assignment values.

**TABLE 3-3. Tape Drive Assignment Values**

| TAPESEL1 | TAPESEL0 | DRIVE<br>SELECTED |

|----------|----------|-------------------|

| 0        | 0        | None              |

| 0        | 1        | 1                 |

| 1        | 0        | 2                 |

| 1        | 1        | 3                 |

## 3.5 MAIN STATUS REGISTER (MSR) Read Only

The read only Main Status Register indicates the current status of the disk controller. The Main Status Register is always available to be read. One of its functions is to control the flow of data to and from the Data Register (FIFO). The Main Status Register indicates when the disk controller is ready to send or receive data through the Data Register. It should be read before each byte is transferred to or from the Data Register except during a DMA transfer. No delay is required when reading this register after a data transfer.

After a hardware or software reset, or recovery from a power down state, the Main Status Register is immediately available to be read by the  $\mu P.$  It will contain a value of 00 hex until the oscillator circuit has stabilized, and the internal registers have been initialized. When the PC8477B is ready to receive a new command, it will report an 80 hex to the  $\mu P.$  The system software can poll the MSR until it is ready. The worst case time allowed for the MSR to report an 80 hex value (RQM set) is 2.5  $\mu s$  after reset or power up.

### MSR

|       | D7  | D6 | D5  | D4          | D3 | D2 | D1 | D0  |

|-------|-----|----|-----|-------------|----|----|----|-----|

| DESC  | RQM |    | l . | CMD<br>PROG |    |    |    | l . |

| RESET | 0   | 0  | 0   | 0           | 0  | 0  | 0  | 0   |

Request for Master: Indicates that the controller is ready to send or receive data from the  $\mu P$  through the FIFO. This bit is cleared immediately after a byte transfer and will become set again as soon as the disk controller is ready for the next byte. During a Non-DMA Execution phase, the RQM indicates the status of the interrupt pin.

D6 Data I/O (Direction): Indicates whether the controller is expecting a byte to be written to (0) or read from (1) the Data Register.

Non-DMA Execution: Indicates that the controller is in the Execution Phase of a byte transfer operation in the Non-DMA mode. Used for multiple byte transfers by the μP in the Execution Phase through interrupts or software polling.

D4 Command in Progress: This bit is set after the first byte of the Command Phase is written. This bit is cleared after the last byte of the Result Phase is read. If there is no Result Phase in a command, the bit is cleared after the last byte of the Command Phase is written.

D3 Drive 3 Busy: Set after the last byte of the Command Phase of a Seek or Recalibrate command is issued for drive 3. Cleared after reading the first byte in the Result Phase of the Sense Interrupt Command for this drive.

Drive 2 Busy: Same as above for drive 2.

D1 Drive 1 Busy: Same as above for drive 1.

D0 Drive 0 Busy: Same as above for drive 0.

## 3.6 DATA RATE SELECT REGISTER (DSR) Write Only

This write only register is used to program the data rate, amount of write precompensation, power down mode, and software reset. The data rate is programmed via the CCR, not the DSR, for PC-AT and PS/2 Model 30 and MicroChannel applications. Other applications can set the data rate in the DSR. The data rate of the floppy controller is determined by the most recent write to either the DSR or CCR. The DSR is unaffected by a software reset. A hardware reset will set the DSR to 02 (hex), which corresponds to the default precompensation setting and 250 kb/s.

### DSR

D6

D7

**D**5

|               | D7           | D6         | D5 | D4            | D3            | D2            | D1     | D0     |

|---------------|--------------|------------|----|---------------|---------------|---------------|--------|--------|

| DESC          | S/W<br>RESET | LOW<br>PWR | 0  | PRE-<br>COMP2 | PRE-<br>COMP1 | PRE-<br>COMP0 | DRATE1 | DRATE0 |

| RESET<br>COND |              | 0          | 0  | 0             | 0             | 0             | 1      | 0      |

D7 Software Reset: A 1 in this bit location will reset the part similar to the DOR RESET (D2) except that this software reset is self-clearing.

Low Power: A 1 to this bit will put the controller into the Manual Low Power mode. The oscillator and data separator circuits will be turned off. Manual Low Power can also be accessed via the Mode command. The chip will come out of low power after a software reset, or access to the Data Register or Main Status Register.

**D5** Undefined: Should be set to 0.

D4-D2 Precompensation Select: These three bits select the amount of write precompensation the floppy controller will use on the WDATA disk interface output. Table 3-4 shows the amount of precompensation used for each bit pattern. In most cases, the default values (Table 3-5) can be used; however, alternate values can be chosen for specific types of drives and media. Track 0 is the default starting track number for precompensation. The starting track number can be changed in the Configure command.

D1-D0 Data Rate Select 1,0: These bits determine the data rate for the floppy controller. See Table 3-6 for the corresponding data rate for each value of D1, D0. The data rate select bits are unaffected by a software reset, and are set to 250 kb/s after a hardware reset.

**TABLE 3-4. Write Precompensation Delays**

|          |   |          | · · · · · · · · · · · · · · · · · · · |

|----------|---|----------|---------------------------------------|

| PRI<br>4 |   | OMP<br>2 | Precompensation Delay                 |

| 1        | 1 | 1        | 0.0 ns                                |

| 0        | 0 | 1        | 41.7 ns                               |

| 0        | 1 | 0        | 83.3 ns                               |

| 0        | 1 | 1        | 125.0 ns                              |

| 1        | 0 | 0        | 166.7 ns                              |

| 1        | 0 | 1        | 208.3 ns                              |

| 1        | 1 | 0        | 250.0 ns                              |

| 0        | 0 | 0        | DEFAULT                               |

**TABLE 3-5. Default Precompensation Delays**

| Data Rate | Precompensation Delay |

|-----------|-----------------------|

| 1 Mb/s    | 41.7 ns               |

| 500 kb/s  | 125.0 ns              |

| 300 kb/s  | 125.0 ns              |

| 250 kb/s  | 125.0 ns              |

**TABLE 3-6. Data Rate Select Encoding**

| Data Rate | e Select | Data     | Data Rate |  |  |  |  |

|-----------|----------|----------|-----------|--|--|--|--|

| 1         | 1 2      |          | FM        |  |  |  |  |

| 1         | 1        | 1 Mb/s   | Illegal   |  |  |  |  |

| 0         | 0        | 500 kb/s | 250 kb/s  |  |  |  |  |

| 0         | 1        | 300 kb/s | 150 kb/s  |  |  |  |  |

| 1         | 0        | 250 kb/s | 125 kb/s  |  |  |  |  |

Note: FM mode is not guaranteed through functional testing.

# 3.7 DATA REGISTER (FIFO) Read/Write

The FIFO (read/write) is used to transfer all commands, data, and status between the  $\mu P$  and the PC8477B. During the Command Phase, the  $\mu P$  writes the command bytes into the FIFO after polling the RQM and DIO bits in the MSR. During the Result Phase, the  $\mu P$  reads the result bytes from the FIFO after polling the RQM and DIO bits in the MSR.

The enabling of the FIFO and setting of the FIFO threshold is done via the Configure command. If the FIFO is enabled,

only the Execution Phase byte transfers use the 16 byte FIFO. The FIFO is always disabled during the Command and Result Phases of a controller operation. If the FIFO is enabled, it will not be disabled after a software reset if the LOCK bit is set in the Lock Command. After a hardware reset, the FIFO is disabled to maintain compatibility with PC-AT systems.

The 16 byte FIFO can be used for DMA, Interrupt, or software polling type transfers during the execution of a read, write, format, or scan command. In addition, the FIFO can be put into a Burst or Non-Burst mode with the Mode command. In the Burst mode, DRQ or INT remains active until all of the bytes have been transferred to or from the FIFO. In the Non-Burst mode, DRQ or INT is deasserted for 350 ns to allow higher priority transfer requests to be serviced. The Mode command can also disable the FIFO for either reads or writes separately. The FIFO allows the system a larger latency without causing a disk overrun/underrun error. Typical uses of the FIFO would be at the 1 Mb/s data rate, or with multi-tasking operating systems. The default state of the FIFO is disabled, with a threshold of zero. The default state is entered after a hardware reset.

### Data Register (FIFO)

|               | D7 | D6         | D5 | D4   | D3   | D2 | D1 | D0 |  |

|---------------|----|------------|----|------|------|----|----|----|--|

| DESC          |    | Data [7:0] |    |      |      |    |    |    |  |

| RESET<br>COND |    |            |    | Byte | Mode |    |    |    |  |

During the Execution Phase of a command involving data transfer to/from the FIFO, the system must respond to a data transfer service request based on the following formula:

# **Maximum Allowable Data Transfer Service Time**

(THRESH + 1) imes 8 imes t<sub>DRP</sub> - (16 imes t<sub>ICP</sub>)

This formula is good for all data rates with the FIFO enabled or disabled. THRESH is a four bit value programmed in the Configure command, which sets the FIFO threshold. If the FIFO is disabled, THRESH is zero in the above formula. The last term of the formula,  $(16\times t_{\rm ICP})$  is an inherent delay due to the microcode overhead required by the PC8477B. This delay is also data rate dependent. See Table 6-1 for the  $t_{\rm DRP}$  and  $t_{\rm ICP}$  times.

The programmable FIFO threshold (THRESH) is useful in adjusting the floppy controller to the speed of the system. In other words, a slow system with a sluggish DMA transfer capability would use a high value of THRESH, giving the system more time to respond to a data transfer service request (DRQ for DMA mode or INT for Interrupt mode). Conversely, a fast system with quick response to a data transfer service request would use a low value of THRESH.

## 3.8 DIGITAL INPUT REGISTER (DIR) Read Only

This diagnostic register is used to detect the state of the DSKCHG disk interface input and some diagnostic signals. The function of this register depends on the register mode of operation. When in the PC-AT mode, the D6-D0 are TRI-STATE to avoid conflict with the fixed disk status register at the same address. The DIR is unaffected by a software reset.

#### 3.8.1 DIR-PC-AT Mode

|       | D7     | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| DESC  | DSKCHG | х   | x   | х   | Х   | x   | Х   | Х   |

| RESET | N/A    | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

D7 Disk Changed: Active high status of DSKCHG disk interface input, independent of INVERT

**D6-D0 Undefined:** TRI-STATE. Used by hard disk controller status register.

#### 3.8.2 DIR-PS/2 Mode

|               | D7     | D6  | D5  | D4  | D3  | D2     | D1     | D0          |

|---------------|--------|-----|-----|-----|-----|--------|--------|-------------|

| DESC          | DSKCHG | 1   | 1   | 1   | 1   | DRATE1 | DRATE0 | HIGH<br>DEN |

| RESET<br>COND | N/A    | N/A | N/A | N/A | N/A | N/A    | N/A    | 1           |

D7 Disk Changed: Active high status of DSKCHG disk interface input, independent of INVERT value.

D6-D3 Reserved: Always 1.

D2-D1 Data Rate Select 1,0: These bits indicate the status of the DRATE1-0 bits programmed through the DSR/CCR.

D0 High Density: This bit is low when the 1 Mb/s or 500 kb/s data rate is chosen, and high when the 300 kb/s or 250 kb/s data rate is chosen. This bit is independent of the IDENT or INVERT value.

## 3.8.3 DIR-Model 30 Mode

|               | D7     | D6 | D5 | D4 | D3    | D2    | D1     | D0     |

|---------------|--------|----|----|----|-------|-------|--------|--------|

| DESC          | DSKCHG | 0  | 0  | 0  | DMAEN | NOPRE | DRATE1 | DRATE0 |

| RESET<br>COND | N/A    | 0  | 0  | 0  | 0     | 0     | 1      | 0      |

D7 Disk Changed: Active low status of DSKCHG disk interface input, independent of INVERT value.

D6-D4 Reserved: Always 0.

D3 DMA Enable: Active high status of the DMAEN bit in the DOR.

**No Precompensation:** Active high status of the NOPRE bit in the CCR.

D1-D0 Data Rate Select 1,0: These bits indicate the status of the DRATE1-0 bits programmed through the DSR/CCR.

# 3.9 CONFIGURATION CONTROL REGISTER (CCR) Write Only

This is the write only data rate register commonly used in PC-AT applications. This register is not affected by a software reset, and is set to 250 kb/s after a hardware reset. The data rate of the floppy controller is determined by the last write to either the CCR or DSR

#### 3.9.1 CCR-PC-AT and PS/2 Modes

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1     | D0     |

|---------------|-----|-----|-----|-----|-----|-----|--------|--------|

| DESC          | 0   | 0   | 0   | 0   | 0   | 0   | DRATE1 | DRATE0 |

| RESET<br>COND | N/A | N/A | N/A | N/A | N/A | N/A | 1      | 0      |

D7-D2 Reserved: Should be set to 0.

D1-D0 Data Rate Select 1,0: These bits determine the data rate of the floppy controller. See Table 3-6 for the appropriate values.

#### 3.9.2 CCR-Model 30 Mode

|               | D7  | D6  | D5  | D4  | D3  | D2    | D1     | D0     |

|---------------|-----|-----|-----|-----|-----|-------|--------|--------|

| DESC          | 0   | 0   | 0   | 0   | 0   | NOPRE | DRATE1 | DRATE0 |

| RESET<br>COND | N/A | N/A | N/A | N/A | N/A | 0     | 1      | 0      |

D7-D3 Reserved: Should be set to 0.

No Precompensation: This bit can be set by software, but it has no functionality. It can be read by bit D2 of the DIR when in the Model 30 register mode. Unaffected by a software reset.

D1-D0 Data Rate Select 1,0: These bits determine the data rate of the floppy controller. See Table 3-6 for the appropriate values.

#### 3.10 RESULT PHASE STATUS REGISTERS

The Result Phase of a command contains bytes that hold status information. The format of these bytes are described below. Do not confuse these status bytes with the Main Status Register, which is a read only register that is always valid. The Result Phase status registers are read from the Data Register (FIFO) only during the Result Phase of certain commands (see Section 4.1 Command Set Summary). The status of each register bit is indicated when the bit is a 1.

# 3.10.1 Status Register 0 (ST0)

|       | D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0  |

|-------|----|----|----|----|----|-----|-----|-----|