# **LR38575**

#### **DESCRIPTION**

The LR38575 is a CMOS timing generator IC which generates timing pulses for driving 1 310 k-pixel CCD area sensor and processing pulses.

#### **FEATURES**

- Designed for 1/3.2-type 1 310 k-pixel CCD area sensor

- Frequency of driving horizontal CCD: 12.272725

MHz

- In monitoring mode, it can be obtained 30 fields/s

- Two still mode types :

3 fields period and 4 fields period

- External shutter control function with serial data input is possible

- +3.3 V and +4.5 V power supplies

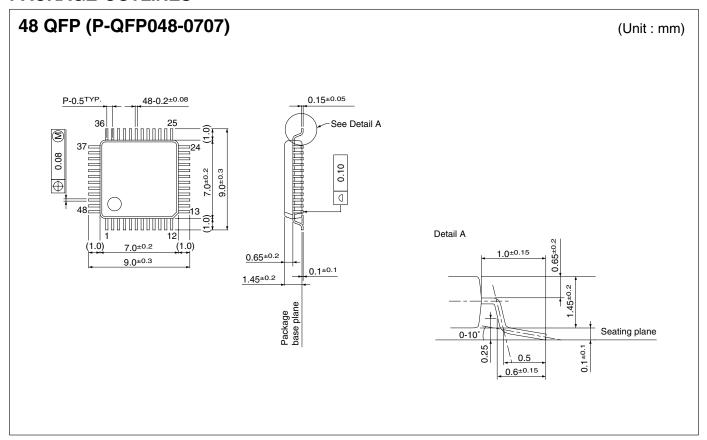

- Package : 48-pin QFP (P-QFP048-0707) 0.5 mm pin-pitch

# Timing Generator IC for 1 310 k-pixel CCD

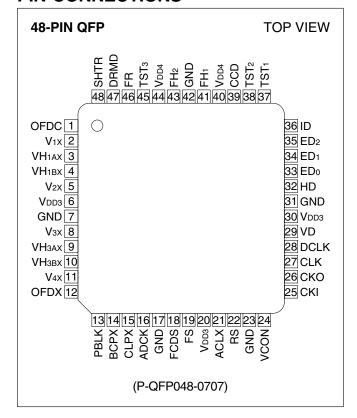

## **PIN CONNECTIONS**

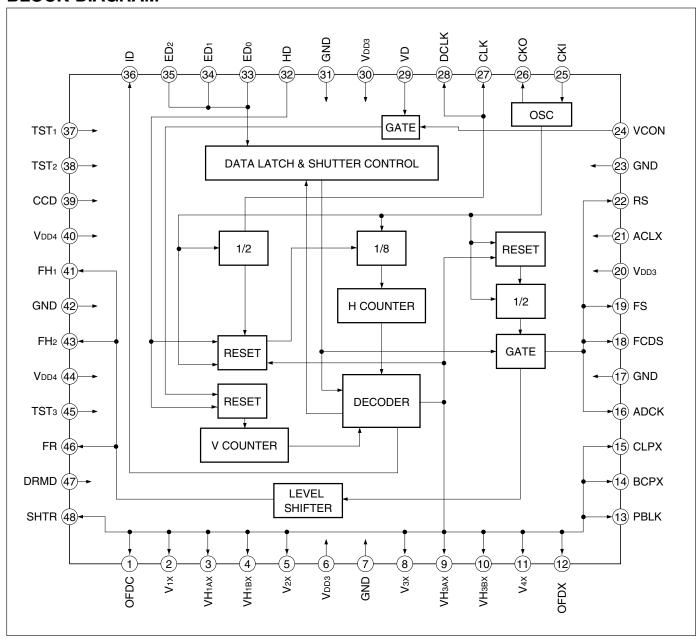

### **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

|         | 0. SYMBOL IO SYMBOL POLARITY PIN NAME DESCRIPTION |           |          |                                      |                                                         |  |  |  |  |

|---------|---------------------------------------------------|-----------|----------|--------------------------------------|---------------------------------------------------------|--|--|--|--|

| PIN NO. | SYMBOL                                            | IO SYMBOL | POLARITY | PIN NAME                             | DESCRIPTION                                             |  |  |  |  |

| 1       | OFDC                                              | О3        | Л        | Control pulse output for OFD voltage | A pulse to control OFD voltage.                         |  |  |  |  |

| 2       | Vav                                               | 02        | П        | Vertical transfer                    | A vertical transfer pulse for the CCD.                  |  |  |  |  |

| 2       | V <sub>1</sub> X                                  | O3        |          | pulse output 1                       | Connect to V <sub>1</sub> x pin of vertical driver IC.  |  |  |  |  |

|         |                                                   |           | T        | Readout pulse output 1A              | A pulse that transfers the charge of the photo-diode to |  |  |  |  |

| 3       | VH <sub>1</sub> AX                                | О3        |          |                                      | the vertical shift register.                            |  |  |  |  |

|         |                                                   |           |          |                                      | Connect to VH1AX pin of vertical driver IC.             |  |  |  |  |

|         |                                                   |           |          | Readout pulse                        | A pulse that transfers the charge of the photo-diode to |  |  |  |  |

| 4       | VH <sub>1</sub> BX                                | O3        |          | output 1B                            | the vertical shift register.                            |  |  |  |  |

|         |                                                   |           |          |                                      | Connect to VH <sub>1BX</sub> pin of vertical driver IC. |  |  |  |  |

| 5       | V <sub>2</sub> X                                  | O3        |          | Vertical transfer                    | A vertical transfer pulse for the CCD.                  |  |  |  |  |

|         | VZA                                               | 03        | ] _      | pulse output 2                       | Connect to V2x pin of vertical driver IC.               |  |  |  |  |

| 6       | VDD3                                              | _         | _        | Power supply                         | Supply of +3.3 V power.                                 |  |  |  |  |

| 7       | GND                                               | _         | _        | Ground                               | A grounding pin.                                        |  |  |  |  |

| 8       | V <sub>3</sub> x                                  | O3        | 7 .      | Vertical transfer                    | A vertical transfer pulse for the CCD.                  |  |  |  |  |

|         | VOA                                               | 0.5       | Ш        | pulse output 3                       | Connect to V <sub>3</sub> x pin of vertical driver IC.  |  |  |  |  |

|         | VНзах                                             | O3        | T        | Readout pulse output 3A              | A pulse that transfers the charge of the photo-diode to |  |  |  |  |

| 9       |                                                   |           |          |                                      | the vertical shift register.                            |  |  |  |  |

|         |                                                   |           |          |                                      | Connect to VH3AX pin of vertical driver IC.             |  |  |  |  |

|         |                                                   | O3        |          | Readout pulse output 3B              | A pulse that transfers the charge of the photo-diode to |  |  |  |  |

| 10      | VНзвх                                             |           | T        |                                      | the vertical shift register.                            |  |  |  |  |

|         |                                                   |           |          |                                      | Connect to VH3BX pin of vertical driver IC.             |  |  |  |  |

| 11      | V <sub>4</sub> X                                  | О3        |          | Vertical transfer                    | A vertical transfer pulse for the CCD.                  |  |  |  |  |

| L.,     | <b>V</b> 4/                                       |           |          | pulse output 4                       | Connect to V <sub>4</sub> x pin of vertical driver IC.  |  |  |  |  |

|         |                                                   | Х ОЗ      |          | OFD pulse output                     | A pulse that sweeps the charge of the photo-diode for   |  |  |  |  |

| 12      | OFDX                                              |           | I        |                                      | the electronic shutter. Connect to OFD pin of the CCD   |  |  |  |  |

| '-      |                                                   |           |          | or B paids satpar                    | through the vertical driver IC and DC offset circuit.   |  |  |  |  |

|         |                                                   |           |          |                                      | Held at H level in normal mode.                         |  |  |  |  |

|         |                                                   |           |          |                                      | A pulse for pre-blanking. This pulse is controlled by   |  |  |  |  |

|         |                                                   | О3        | T        |                                      | serial data BLKCNT.                                     |  |  |  |  |

|         | PBLK                                              |           |          |                                      | BLKCNT = H; This pulse stays low during the             |  |  |  |  |

|         |                                                   |           |          | Pre-blanking pulse                   | absence of effective pixels within the                  |  |  |  |  |

| 13      |                                                   |           |          | output                               | vertical blanking or during the                         |  |  |  |  |

|         |                                                   |           |          |                                      | sweepout signal.                                        |  |  |  |  |

|         |                                                   |           |          |                                      | BLKCNT = L; This pulse stays high during the            |  |  |  |  |

|         |                                                   |           |          |                                      | sweepout signal.                                        |  |  |  |  |

|         |                                                   |           |          |                                      | The output phase of PBLK is selected by serial data.    |  |  |  |  |

| PIN NO. | SYMBOL           | IO SYMBOL | POLARITY | PIN NAME            | DESCRIPTION                                                     |                                             |  |  |  |

|---------|------------------|-----------|----------|---------------------|-----------------------------------------------------------------|---------------------------------------------|--|--|--|

|         |                  |           |          |                     | A pulse to clamp the optical black signal.                      |                                             |  |  |  |

|         |                  |           |          |                     | This pulse is controlled by serial data BCPCNT;                 |                                             |  |  |  |

|         |                  |           |          |                     | BCPCNT = H; This pulse stays high during the                    |                                             |  |  |  |

| 1 4     | BCPX             | O3        | 7        | Optical black clamp | absence of effective pixels within the                          |                                             |  |  |  |

| 14      | БСРХ             | U3        |          | pulse output        | vertical blanking or during the                                 |                                             |  |  |  |

|         |                  |           |          |                     | sweepout signal.                                                |                                             |  |  |  |

|         |                  |           |          |                     | BCPCNT = L; This pulse stays high during the                    |                                             |  |  |  |

|         |                  |           |          |                     | sweepout signal.                                                |                                             |  |  |  |

| 15      | CLPX             | O3        | 7        | Clamp pulse output  | A pulse to clamp the dummy outputs of the CCD signal.           |                                             |  |  |  |

|         | OLFX             | 3         |          |                     | This pulse stays high during the sweepout period.               |                                             |  |  |  |

| 16      | ADCK             | O6MA3     | $\prod$  | AD alask cutout     | An output pin for AD converter. The output phase of             |                                             |  |  |  |

| 16      | ADCK             | OdiviA3   | ][]      | AD clock output     | ADCK is selected by serial data in 90° steps.                   |                                             |  |  |  |

| 17      | GND              | -         | 1        | Ground              | A grounding pin.                                                |                                             |  |  |  |

|         |                  |           |          | CDS pulse output 1  | A pulse to clamp the feed-through level for the CCD.            |                                             |  |  |  |

| 18      | FCDS             | O6MA3     |          |                     | The output phase and output polarity of FCDS are                |                                             |  |  |  |

|         |                  |           |          |                     | selected by serial data.                                        |                                             |  |  |  |

|         |                  | O6MA3     |          | CDS pulse output 2  | A pulse to sample-hold the signal for the CCD.                  |                                             |  |  |  |

| 19      | FS               |           |          |                     | The output phase and output polarity of FS are selected         |                                             |  |  |  |

|         |                  |           |          |                     | by serial data.                                                 |                                             |  |  |  |

| 20      | V <sub>DD3</sub> | ı         | I        | Power supply        | Supply of +3.3 V power.                                         |                                             |  |  |  |

|         |                  | ICU3      | 3 –      | All clear input     | An input pin for resetting all internal circuits at power-on.   |                                             |  |  |  |

| 21      | ACLX             |           |          |                     | Connect to VDD through the diode and GND through the            |                                             |  |  |  |

|         |                  |           |          |                     | capacitor.                                                      |                                             |  |  |  |

| 22      | RS               | O6MA3     |          | S/H pulse output    | A pulse to sample-hold the signal for the CDS circuit.          |                                             |  |  |  |

|         | 110              | OOIVIAO   |          | O/11 puise output   | The output polarity of RS is selected by serial data.           |                                             |  |  |  |

| 23      | GND              | _         | 1        | Ground              | A grounding pin.                                                |                                             |  |  |  |

|         |                  |           |          |                     | An input pin to control internal vertical clock for long        |                                             |  |  |  |

|         | VCON             | ICU3      | -        |                     | shutter speed.                                                  |                                             |  |  |  |

|         |                  |           |          |                     | H level or open : VD                                            |                                             |  |  |  |

| 24      |                  |           |          | VD control input    | L level : VD is masked by the pulse which                       |                                             |  |  |  |

|         |                  |           |          |                     | is latched at the rising edge of VD.                            |                                             |  |  |  |

|         |                  |           |          |                     | It's necessary to be set SMD = high and number of the           |                                             |  |  |  |

|         |                  |           |          |                     | fields data $n \ge 2$ in serial data control at VCON operation. |                                             |  |  |  |

| 25      | 25 CKI OSC       |           | 3   _    | Clock input         | An input pin for reference clock oscillation.                   |                                             |  |  |  |

|         |                  |           |          |                     | The frequency is 24.54545 MHz.                                  |                                             |  |  |  |

| 26      | СКО              | OSCO3     | -        | Clock output        | An output pin for reference clock oscillation.                  |                                             |  |  |  |

|         |                  |           |          |                     | The output is the inverse of CKI (pin 25).                      |                                             |  |  |  |

| 27      | CLK              | C O6MA3   | O6MA3    | ПГ                  | Clock output                                                    | An output pin to generate HD and VD pulses. |  |  |  |

|         | J                |           | ] []     | C.Ook Output        | The frequency is 12.272725 MHz.                                 |                                             |  |  |  |

| PIN NO. | SYMBOL           | IO SYMBOL  | POLARITY  | PIN NAME DESCRIPTION      |                                                              |  |                     |                                          |  |

|---------|------------------|------------|-----------|---------------------------|--------------------------------------------------------------|--|---------------------|------------------------------------------|--|

|         |                  |            |           |                           | An output pin for DSP IC. The frequency is 12.272725 MHz.    |  |                     |                                          |  |

| 28      | DCLK             | O6MA3      |           | Clock output              | The output phase of DCLK is selected by serial data in       |  |                     |                                          |  |

|         |                  |            |           | 90° steps.                |                                                              |  |                     |                                          |  |

| 20      | 20 \             | 100        | _         | Vertical reference        | An input pin for reference of vertical pulse.                |  |                     |                                          |  |

| 29      | VD               | IC3        |           | pulse input               | Connect to VD pin of DSP IC.                                 |  |                     |                                          |  |

| 30      | V <sub>DD3</sub> | _          | ı         | Power supply              | Supply of +3.3 V power.                                      |  |                     |                                          |  |

| 31      | GND              | _          | _         | Ground                    | A grounding pin.                                             |  |                     |                                          |  |

| 32      | HD               | IC3        |           | Horizontal drive          | An input pin for reference of horizontal pulse.              |  |                     |                                          |  |

| 32      | טוו              | 103        | Ш         | pulse input               | Connect to HD pin of DSP IC.                                 |  |                     |                                          |  |

| 33      | ED <sub>0</sub>  | ICSU3      | _         | Strobe pulse input        | An input pin for the strobe pulse, to control the functions  |  |                     |                                          |  |

| 33      | LD0              | 10303      |           | Strobe pulse input        | of LR38575. For details, see "Serial Data Control".          |  |                     |                                          |  |

|         |                  |            |           | Shift register clock      | An input pin for the clock of the shift register, to control |  |                     |                                          |  |

| 34      | ED1              | ICSU3      | _         |                           | the functions of LR38575. For details, see "Serial Data      |  |                     |                                          |  |

|         |                  |            |           | input                     | Control".                                                    |  |                     |                                          |  |

|         |                  | ICSU3      |           | Shift register data input | An input pin for the data of the shift register, to control  |  |                     |                                          |  |

| 35      | ED2              |            | _         |                           | the functions of LR38575. For details, see "Serial Data      |  |                     |                                          |  |

|         |                  |            |           |                           | Control".                                                    |  |                     |                                          |  |

| 36      | ID               | O3         | Л         | Line index pulse          | The pulse is used in color separator.                        |  |                     |                                          |  |

|         |                  | 03         |           | output                    | The signal switches between high and low at every line.      |  |                     |                                          |  |

| 37      | TST <sub>1</sub> | ICD4       | _         | Test pin 1                | A test pin. Set open or to L level in normal mode.           |  |                     |                                          |  |

| 38      | TST2             | ICD4       | _         | Test pin 2                | A test pin. Set open or to L level in normal mode.           |  |                     |                                          |  |

|         |                  | ICU4       | _         | CCD selection input       | An input pin to select CCD. It should be used with           |  |                     |                                          |  |

| 39      | CCD              |            |           |                           | MODE input which is in the serial data.                      |  |                     |                                          |  |

|         |                  |            |           |                           | Fix to H level or open.                                      |  |                     |                                          |  |

| 40      | VDD4             | _          | _         | Power supply              | Supply of +3.3 to +4.5 V power.                              |  |                     |                                          |  |

| 41      | FH <sub>1</sub>  | O6MA43     | O6M443    | O6MA43                    | O6MA43                                                       |  | Horizontal transfer | A horizontal transfer pulse for the CCD. |  |

|         |                  | 0011111110 | ] []      | pulse output 1            | Connect to $\phi$ H1 pin of the CCD.                         |  |                     |                                          |  |

| 42      | GND              | _          | _         | Ground                    | A grounding pin.                                             |  |                     |                                          |  |

| 43      | FH <sub>2</sub>  | 2 O6MA43   | Ha O6MA43 | EH2 O6MA43                | H2 O6MA43                                                    |  | Horizontal transfer | A horizontal transfer pulse for the CCD. |  |

|         | 1112             |            |           | pulse output 2            | Connect to $\phi$ H₂ pin of the CCD.                         |  |                     |                                          |  |

| 44      | VDD4             | _          | _         | Power supply              | Supply of +3.3 to +4.5 V power.                              |  |                     |                                          |  |

| 45      | TST3             | ICD4       | _         | Test pin 3                | A test pin. Set open or to L level in normal mode.           |  |                     |                                          |  |

| 46      | FR               | O6MA43     |           | Reset pulse output        | A pulse to reset the charge of output circuit.               |  |                     |                                          |  |

|         |                  |            |           |                           | The output phase of FR is selected by serial data.           |  |                     |                                          |  |

|         | DRMD             | ICU3       | _         | Drive mode selection      | An input pin to select the period of still mode.             |  |                     |                                          |  |

| 47      |                  |            |           | input                     | L level : 3 fields period                                    |  |                     |                                          |  |

|         |                  |            | _         | input                     | H level or open : 4 fields period                            |  |                     |                                          |  |

| 48      | SHTR             | O3         |           | Trigger output            | A trigger pulse for effective signal period.                 |  |                     |                                          |  |

IC3 : Input pin (CMOS level)

ICU3 : Input pin (CMOS level with pull-up resistor)

ICSU3 : Input pin (CMOS schmitt-trigger level with pull-up resistor)

ICSU3 : Output pin (output high level is VDD3.)

ICSU3 : OeMA43 : Output pin (output high level is VDD4.)

ICU4 : Input pin (CMOS level with pull-up resistor) OSCI3 : Input pin for oscillation ICD4 : Input pin (CMOS level with pull-down resistor) OSCO3 : Output pin for oscillation

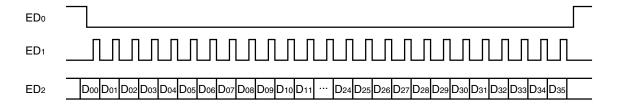

# Serial Data Control SERIAL DATA INPUT TIMING

ED2 is shifted at the rising edge of ED1, and is latched at the rising edge of ED0.

PWSA is effective at the rising edge of EDo, but others are effective at the horizontal line in which VH1AX to VH3BX are active.

ED<sub>0</sub> should be at low level during data inputs of ED<sub>1</sub> and ED<sub>2</sub>.

Since all internal data are set to low level by ACLX, EDo to ED2 should be input for proper operations. Since all internal data except PWSA are set to low level by PWSA, EDo to ED2 should be input for proper operations.

### **SERIAL DATA INPUTS**

| DATA    | NAME            | FUNCTION                                    | DATA = L      | DATA = L DATA = H |       |

|---------|-----------------|---------------------------------------------|---------------|-------------------|-------|

| D00-D06 | SD0-SD6         | Step of high speed shutter                  | _             |                   | All L |

| D07     | SD7             |                                             |               |                   |       |

| D08     | SD8             | Number of exposed fields                    | _             | All L             |       |

| D09     | SD <sub>9</sub> |                                             |               |                   |       |

| D10     | SMD             | Electronic shutter mode control             | -             | _                 | L     |

| D11     | INMD            | Integration mode control                    | Monitoring    | Still             | L     |

| D12     | PWSA            | Power save control                          | Normal        | Power save        | _     |

| D13     | PLCH            | Polarity control of FCDS, FS and RS pulses  | Negative      | Positive          | L     |

| D14     | MODE            | Monitoring mode selection with CCD (pin 39) | No use        | No use RJ24J3XX   |       |

| D15     | BCPCNT          | BCP control                                 | Discontinuous | Continuous        | L     |

| D16     | ML <sub>1</sub> |                                             |               | All L             |       |

| D17     | ML2             |                                             | _             | All L             |       |

| D18     | MR <sub>1</sub> |                                             |               |                   |       |

| D19     | MR <sub>2</sub> |                                             | -             | All L             |       |

| D20     | MRз             |                                             |               |                   |       |

| D21     | MC <sub>1</sub> |                                             |               |                   |       |

| D22     | MC <sub>2</sub> |                                             | -             | All L             |       |

| D23     | МСз             |                                             |               |                   |       |

| D24     | MS <sub>1</sub> | Phase control                               |               |                   |       |

| D25     | MS <sub>2</sub> | Friase control                              | -             | _                 | All L |

| D26     | MSз             |                                             |               |                   |       |

| D27     | MD <sub>1</sub> |                                             |               | All L             |       |

| D28     | MD2             |                                             | _             |                   |       |

| D29     | МДз             |                                             |               |                   |       |

| D30     | MA <sub>1</sub> |                                             |               | All L             |       |

| D31     | MA <sub>2</sub> |                                             |               | All L             |       |

| D32     | MP1             |                                             |               | All L             |       |

| D33     | MP2             |                                             |               | All L             |       |

| D34     | BLKCNT          | PBLK control                                | Discontinuous | Continuous        | L     |

| D35     | VHCONT          | VH1AX to VH3BX control Normal Stay H        |               | L                 |       |

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL     | RATING                 | UNIT |  |  |  |  |

|-----------------------|------------|------------------------|------|--|--|--|--|

| Supply voltage        | VDD3, VDD4 | -0.3 to +6.0           | V    |  |  |  |  |

| Input voltage         | Vıз        | -0.3 to VDD3 + 0.3     | V    |  |  |  |  |

| Input voltage         | VI4        | VI4 -0.3 to VDD4 + 0.3 |      |  |  |  |  |

| Output valtage        | Voз        | -0.3 to VDD3 + 0.3     | V    |  |  |  |  |

| Output voltage        | VO4        | -0.3 to VDD4 + 0.3     | V    |  |  |  |  |

| Operating temperature | Topr       | -20 to +70             | °C   |  |  |  |  |

| Storage temperature   | Tstg       | -55 to +150            | °C   |  |  |  |  |

### **ELECTRICAL CHARACTERISTICS**

**DC Characteristics** (VDD3 = 3.0 V to VDD4, VDD4 = VDD3 to 5.5 V, VDD4 ≥ VDD3, TOPR = -20 to +70°C)

| PARAMETER             | SYMBOL            | CONDITIONS     | MIN.       | TYP. | MAX.     | UNIT | NOTE       |  |

|-----------------------|-------------------|----------------|------------|------|----------|------|------------|--|

| Input "Low" voltage   | VIL3-1            |                |            |      | 0.2VDD3  | V    | 1 0        |  |

| Input "High" voltage  | VIH3-1            |                | 0.8VDD3    |      |          | V    | 1, 2       |  |

| Input "Low" voltage   | VIL3-2            |                | 0.2VDD3    |      |          | V    |            |  |

| Input "High" voltage  | VIH3-2            | Schmitt-buffer |            |      | 0.75VDD3 | V    | 3          |  |

| Hysteresis voltage    | $V_{T+} - V_{T-}$ |                | 0.08VDD3   |      |          | V    |            |  |

| Input "Low" voltage   | VIL4              |                |            |      | 0.2VDD4  | V    | 4.5        |  |

| Input "High" voltage  | VIH4              |                | 0.8VDD4    |      |          | V    | 4, 5       |  |

| Input "Low" current   | IIL3-1            | Vı = 0 V       |            |      | 1.0      | μA   | 1          |  |

| Input "High" current  | IIH3-1            | VI = VDD3      |            |      | 1.0      | μΑ   | ] <b>'</b> |  |

| Input "Low" current   | IIL3-2            | Vı = 0 V       | 2.0        |      | 60       | μΑ   | 0.0        |  |

| Input "High" current  | IIH3-2            | VI = VDD3      |            |      | 2.0      | μΑ   | 2, 3       |  |

| Input "Low" current   |                   | Vı = 0 V       | 2.0        |      | 60       | μA   | 4          |  |

| Input "High" current  | IIH4-1            | VI = VDD4      |            |      | 2.0      | μA   | 4          |  |

| Input "Low" current   | IIL4-2            | Vı = 0 V       |            |      | 2.0      | μA   | 5          |  |

| Input "High" current  | IIH4-2            | VI = VDD4      | 2.0        |      | 60       | μA   | 5          |  |

| Output "Low" voltage  | VOL3-1            | IoL = 2 mA     |            |      | 0.4      | V    | 6          |  |

| Output "High" voltage | VOH3-1            | IOH = -1  mA   | VDD3 - 0.5 |      |          | V    | 0          |  |

| Output "Low" voltage  | VOL3-2            | IoL = 2 mA     |            |      | 0.4      | V    | 7          |  |

| Output "High" voltage | VOH3-2            | Iон = −2 mA    | VDD3 - 0.5 |      |          | V    | ′          |  |

| Output "Low" voltage  | VOL3-3            | IoL = 3 mA     |            |      | 0.4      | V    | 8          |  |

| Output "High" voltage | Vонз-з            | Iон = −3 mA    | VDD3 - 0.5 |      |          | ٧    | 0          |  |

| Output "Low" voltage  | Vol4              | IoL = 9 mA     |            |      | 0.4      | V    | 0          |  |

| Output "High" voltage | Vон4              | Iон = −9 mA    | VDD4 - 0.5 |      |          | V    | 9          |  |

#### **NOTES:**

- 1. Applied to inputs (IC3, OSCI3).

- 2. Applied to input (ICU3).

- 3. Applied to input (ICSU3).

- 4. Applied to input (ICU4).

- 5. Applied to input (ICD4).

- 6. Applied to output (O3).

- Applied to output (OSCO3). (Output (OSCO3) measures on condition that input (OSCI3) level is 0 V or VDD3.)

- 8. Applied to output (O6MA3).

- 9. Applied to output (O6MA43).

## **PACKAGE OUTLINES**