# BIPOLAR ANALOG INTEGRATED CIRCUIT $\mu$ PC4061

# J-FET INPUT LOW-POWER OPERATIONAL AMPLIFIER

#### **DESCRIPTION**

The  $\mu$ PC4061 is a J-FET input low-power operational amplifier featuring low supply voltage operation from  $\pm 2$  V. Supply current is ten times smaller than  $\mu$ PC4081 type J-FET input op-amp. With very low input bias current characteristics, the  $\mu$ PC4061 is an excellent choice for hand-held measurement equipment and other low-power application circuits.

#### **FEATURES**

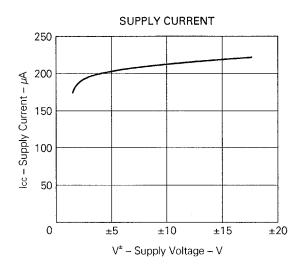

- Low supply current: 220 μA (TYP.)

- Very low input bias and offset currents

- Offset voltage null capability

- High input impedance...J-FET Input Stage

- Low supply voltage operation

- Output short circuit protection

- Internal frequency compensation

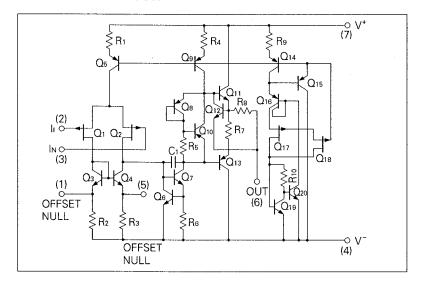

#### **EQUIVALENT CIRCUIT**

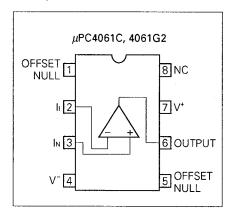

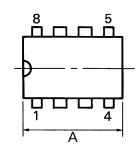

# CONNECTION DIAGRAM (Top View)

### ORDERING INFORMATION

| PART NUMBER       | PACKAGE                     | QUALITY GRADE |  |

|-------------------|-----------------------------|---------------|--|

| μ <b>PC4061</b> C | 8 PIN PLASTIC DIP (300 mil) | Standard      |  |

| μPC4061G2         | 8 PIN PLASTIC SOP (225 mil) | Standard      |  |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specifications of quality grade on the devices and its recommended applications.

# ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C)

| PARAMETER                                                  |                     | SYMBOL  | μPC4061                                    | UNIT |

|------------------------------------------------------------|---------------------|---------|--------------------------------------------|------|

| Voltage between V <sup>+</sup> and V <sup>-</sup> (Note 1) |                     | V+ - V- | -0.3 to +36                                | V    |

| Differential Input Voltage                                 |                     | ViD     | ±30                                        | V    |

| Input Voltage (Note 2)                                     |                     | Vı      | V <sup>-</sup> -0.3 to V <sup>+</sup> +0.3 | V    |

| Output Voltage (Note 3)                                    |                     | Vo      | V <sup>-</sup> -0.3 to V <sup>+</sup> +0.3 | V    |

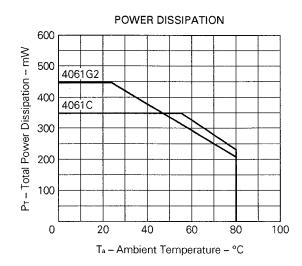

| Power Dissipation                                          | C Package (Note 4)  | Рт      | 350                                        | mW   |

|                                                            | G2 Package (Note 5) | FI      | 440                                        | mW   |

| Output Short Circuit Duration (Note 6)                     |                     |         | Indefinite                                 | sec  |

| Operating Temperature Range                                |                     | Topt    | −20 to +80                                 | °C   |

| Storage Temperature Range                                  |                     | Tstg    | -55 to +125                                | °C   |

- Note 1. Reverse connection of supply voltage can cause destruction.

- Note 2. The input voltage should be allowed to input without damage or destruction. Even during the transition period of supply voltage, power on/off etc., this specification should be kept. The normal operation will establish when the both inputs are within the Common Mode Input Voltage Range of electrical characteristics.

- Note 3. This specification is the voltage which should be allowed to supply to the output terminal from external without damage or destructive. Even during the transition period of supply voltage, power on/off etc., this specification should be kept. The output voltage of normal operation will be the Output Voltage Swing of electrical characteristics.

- Note 4. Thermal derating factor is -5.0 mV / °C when ambient temperature is higher than 55 °C.

- Note 5. Thermal derating factor is -4.4 mV / °C when ambient temperature is higher than 25 °C.

- Note 6. Pay careful attention to the total power dissipation not to exceed the absolute maximum ratings, Note 4 and Note 5.

#### RECOMMENDED OPERATING CONDITIONS

| CHARACTERISTIC            | SYMBOL    | MIN. | TYP. | MAX. | UNIT |

|---------------------------|-----------|------|------|------|------|

| Supply Voltage            | V±        | ± 2  |      | ± 16 | V    |

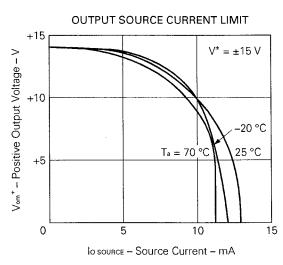

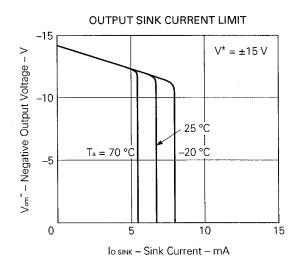

| Output Current (SOURCE)   | lo source |      |      | 5    | mA   |

| Output Current (SINK)     | lo sink   |      |      | 3.5  | mA   |

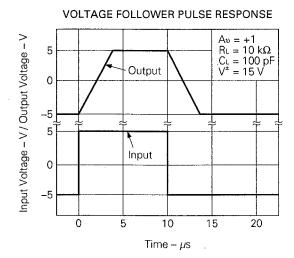

| Capacitive Load (Av = +1) | CL        |      |      | 100  | pF   |

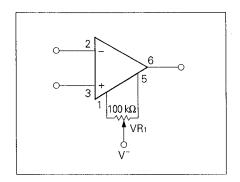

# **OFFSET VOLTAGE NULL CIRCUIT**

# ELECTRICAL CHARACTERISTICS (Ta = 25 °C, $V^{\pm}$ = $\pm 15$ V)

| CHARACTERISTIC                         | SYMBOL     | MIN. | TYP.           | MAX. | UNIT               | CONDITION                                    |

|----------------------------------------|------------|------|----------------|------|--------------------|----------------------------------------------|

| Input Offset Voltage                   | Vio        |      | ±2             | ±10  | mV                 | Rs $\leq$ 50 $\Omega$                        |

| Input Offset Current (Note 7)          | lio        | _    | ±5             | ±50  | pА                 |                                              |

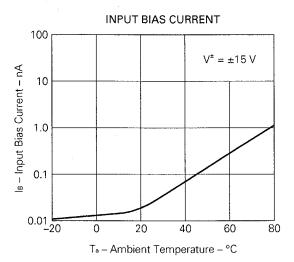

| Input Bias Current (Note 7)            | lв         |      | 10             | 100  | pА                 |                                              |

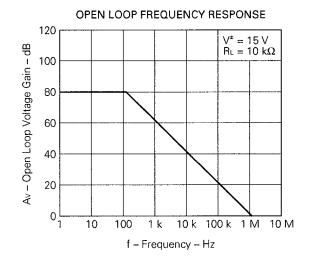

| Large Signal Voltage Gain              | Αυ         | 3    | 9              |      | V/mV               | RL $\geq$ 10 k $\Omega$ , Vo = $\pm$ 10 V    |

| Supply Current                         | lcc        |      | 220            | 250  | μΑ                 | Io = 0 A                                     |

| Common Mode Rejection Ratio            | CMR        | 70   | 90             |      | dB                 |                                              |

| Supply Voltage Rejection Ratio         | SVR        | 70   | 90             |      | dB                 |                                              |

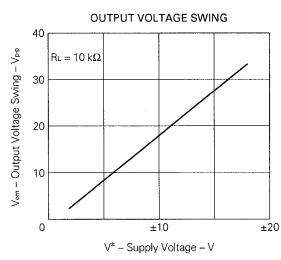

| Output Voltage Swing                   | Vom        | ±12  | +14.0<br>-13.6 |      | V                  | $RL \ge 10 \text{ k}\Omega$                  |

| Common Model Input Voltage Range       | Vicм       | ±12  | +15<br>-13     |      | ٧                  |                                              |

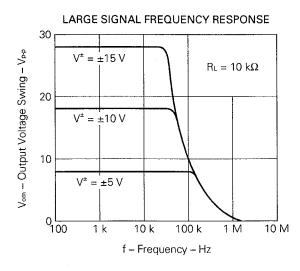

| Slew Rate                              | SR         |      | 3              |      | V/μs               | Av = 1                                       |

| Unity Gain Frequency                   | funity     |      | 1              |      | MHz                |                                              |

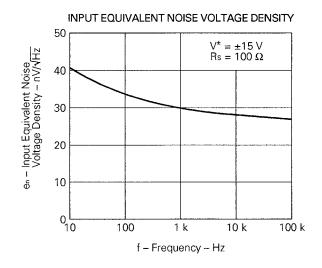

| Input Equivalent Noise Voltage Density | <b>e</b> n |      | 30             |      | nV/√ <del>Hz</del> | Rs = 100 $\Omega$ , f = 1 kHz                |

| Input Offset Voltage                   | Vio        |      | ,              | ±15  | mV                 | Rs $\leq$ 50 $\Omega$ , Ta = -20 to +70 °C   |

| Average Vio Temperature Drift          | ⊿ V10/⊿ T  |      | ±10            |      | μV/°C              | T <sub>a</sub> = -20 to +70 °C               |

| Input Offset Current (Note 7)          | lio        |      |                | ±2   | nA                 | $T_a = -20 \text{ to } +70 ^{\circ}\text{C}$ |

| Input Bias Current (Note 7)            | lв         |      |                | 3.5  | nA                 | T <sub>a</sub> = -20 to +70 °C               |

Note 7. Input bias currents flow into IC. Because each currents are gate leak current of P-channel J-FET on input stage.

And that are temperature sensitive. Short time measuring method is recommendable to maintain the junction temperature close to the ambient temperature.

# TYPICAL PERFORMANCE CHARACTERISTICS (Ta = 25 °C, TYP.)

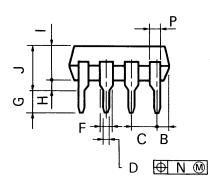

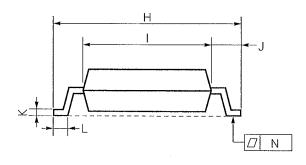

# 8PIN PLASTIC DIP (300 mil)

P8C-100-300B,C

# **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES        |

|------|-----------------------|---------------|

| Α    | 10.16 MAX.            | 0.400 MAX.    |

| В    | 1.27 MAX.             | 0.050 MAX.    |

| С    | 2.54 (T.P.)           | 0.100 (T.P.)  |

| D    | 0.50 <sup>±0.10</sup> | 0.020 + 0.004 |

| F    | 1.4 MIN.              | 0.055 MIN.    |

| G    | 3.2 <sup>±0.3</sup>   | 0.126 ±0.012  |

| Н    | 0.51 MIN.             | 0.020 MIN.    |

| 1    | 4.31 MAX.             | 0.170 MAX.    |

| J    | 5.08 MAX.             | 0.200 MAX.    |

| К    | 7.62 (T.P.)           | 0.300 (T.P.)  |

| L    | 6.4                   | 0.252         |

| М    | 0.25 +0.10            | 0.010 -0.003  |

| N    | 0.25                  | 0.01          |

| Р    | 0.9 MIN.              | 0.035 MIN.    |

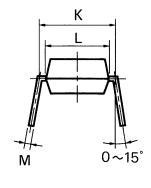

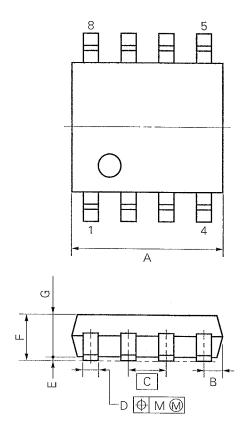

# 8 PIN PLASTIC SOP (225 mil)

# NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

S8GM-50-225B-2

| ITEM | MILLIMETERS                            | INCHES       |

|------|----------------------------------------|--------------|

| Α    | 5.37 MAX.                              | 0.212 MAX.   |

| В    | 0.78 MAX.                              | 0.031 MAX.   |

| С    | 1.27 (T.P.)                            | 0.050 (T.P.) |

| D    | 0.40+0.10                              | 0.016+0.004  |

| E    | 0.1±0.1                                | 0.004±0.004  |

| F    | 1.8 MAX.                               | 0.071MAX.    |

| G    | 1.49                                   | 0.059        |

| Н    | 6.5±0.3                                | 0.256±0.012  |

| ı    | 4.4                                    | 0.173        |

| J    | 1.1                                    | 0.043        |

| K    | 0.15 <sup>+0.10</sup> <sub>-0.05</sub> | 0.006+0.004  |

| L    | 0.6±0.2                                | 0.024+0.008  |

| М    | 0.12                                   | 0.005        |

| N    | 0.15                                   | 0.006        |

# RECOMMENDED SOLDERING CONDITIONS

The following conditions (see table below) must be met when soldering this product.

Please consult with our sales offices in case other soldering process is used, or in case soldering is done under different conditions.

### TYPES OF SURFACE MOUNT DEVICE

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (IEI-1207).

[  $\mu$ PC4061G2 ]

| Soldering<br>method    | Soldering conditions                                                                                                                                               | Recommended condition symbol |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Infrared ray reflow    | Peak package's surface temperature: 230 °C or below,<br>Reflow time: 30 seconds or below (210 °C or higher),<br>Number of reflow process: 1, Exposure limit*: None | IR30-001                     |

| VPS                    | Peak package's surface temperature: 215 °C or below,<br>Reflow time: 40 seconds or below (200 °C or higher),<br>Number of reflow process: 1, Exposure limit*: None | VP15-00-1                    |

| Wave soldering         | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below<br>Number of flow process: 1, Exposure limit*: None                                         | WS15-00-1                    |

| Partial heating method | Terminal temperature: 300 °C or below,<br>Flow time: 10 seconds or below,<br>Exposure limit*: None                                                                 |                              |

<sup>\*:</sup> Exposure limit before soldering after dry-pack package is opened. Storage conditions: 25 °C and relative humidity at 65 % or less.

Note: Do not apply more than a single process at once, except for "Partial heating method."

## TYPES OF THROUGH HOLE DEVICE

[ $\mu$ PC4061C]

| Soldering<br>method | Soldering conditions                                                   | Recommended condition symbol |  |

|---------------------|------------------------------------------------------------------------|------------------------------|--|

| Wave soldering      | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below |                              |  |

[MEMO]