# FW802A Low-Power PHY *IEEE*\* 1394A-2000 Two-Cable Transceiver/Arbiter Device

## **Distinguishing Features**

- Compliant with IEEE Standard 1394a-2000, IEEE Standard for a High Performance Serial Bus Amendment 1.

- Low-power consumption during powerdown or microlow-power sleep mode.

- Supports extended BIAS\_HANDSHAKE time for enhanced interoperability with camcorders.

- While unpowered and connected to the bus, will not drive TPBIAS on a connected port even if receiving incoming bias voltage on that port.

- Does not require external filter capacitors for PLL.

- Does not require a separate 5 V supply for 5 V link controller interoperability.

- Interoperable across 1394 cable with 1394 physical layers (PHY) using 5 V supplies.

- Interoperable with 1394 link-layer controllers using 5 V supplies.

- 1394a-2000 compliant common mode noise filter on incoming TPBIAS.

- Powerdown features to conserve energy in batterypowered applications include:

- Device powerdown pin.

- Link interface disable using LPS.

- Inactive ports power down.

- Automatic microlow-power sleep mode during suspend.

- Interface to link-layer controller supports Annex J electrical isolation as well as bus-keeper isolation.

# Features

- Provides two fully compliant cable ports at 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s.

- Fully supports OHCI requirements.

- Supports arbitrated short bus reset to improve utilization of the bus.

- Supports ack-accelerated arbitration and fly-by concatenation.

- Supports connection debounce.

- Supports multispeed packet concatenation.

- Supports PHY pinging and remote PHY access packets.

- Fully supports suspend/resume.

- Supports PHY-link interface initialization and reset.

- Supports 1394a-2000 register set.

- Supports LPS/link-on as a part of PHY-link interface.

- Supports provisions of IEEE 1394-1995 Standard for a High Performance Serial Bus.

- Fully interoperable with *FireWire*<sup>†</sup> implementation of *IEEE* 1394-1995.

- Reports cable power fail interrupt when voltage at CPS pin falls below 7.5 V.

- Separate cable bias and driver termination voltage supply for each port.

- Meets Intel<sup>‡</sup> Mobile Power Guideline 2000.

## **Other Features**

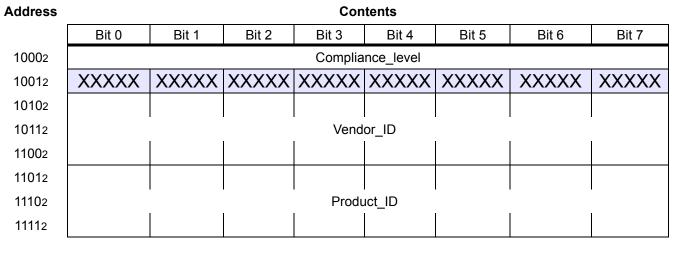

- 64-pin TQFP package.

- Single 3.3 V supply operation.

- Data interface to link-layer controller provided through 2/4/8 parallel lines at 50 Mbits/s.

- 25 MHz crystal oscillator and PLL provide transmit/ receive data at 100 Mbits/s, 200 Mbits/s, and 400 Mbits/s, and link-layer controller clock at 50 MHz.

- Node power-class information signaling for system power management.

- Multiple separate package signals provided for analog and digital supplies and grounds.

- \* *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

- *† FireWire* is a registered trademark of Apple Computer, Inc.

- ‡ Intel is a registered trademark of Intel Corporation.

Page

## **Table of Contents**

#### Contents

| Distinguishing Features                      | 1 |

|----------------------------------------------|---|

| Features                                     | 1 |

| Other Features                               | 1 |

| Description                                  |   |

| Signal Information                           |   |

| Application Information                      |   |

| Crystal Selection Considerations             |   |

| 1394 Application Support Contact Information |   |

| Absolute Maximum Ratings                     |   |

| Electrical Characteristics                   |   |

| Timing Characteristics                       |   |

| Timing Waveforms                             |   |

| Internal Register Configuration              |   |

| Outline Diagrams                             |   |

| Ordering Information                         |   |

# List of Figures

### Figures

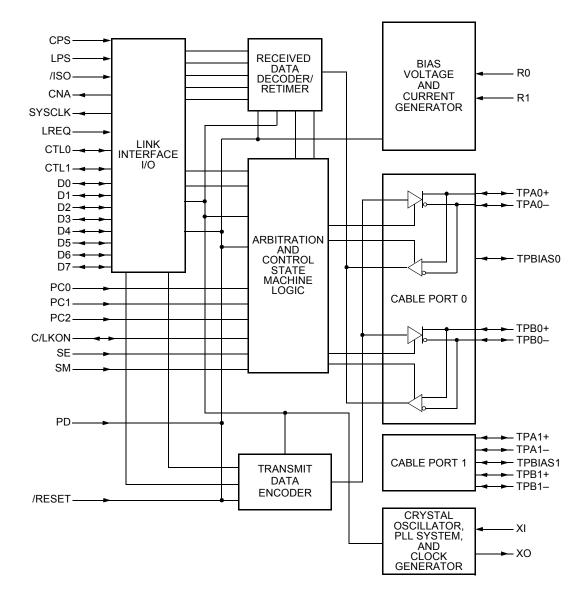

| Figure 1. Block Diagram                                           | 5  |

|-------------------------------------------------------------------|----|

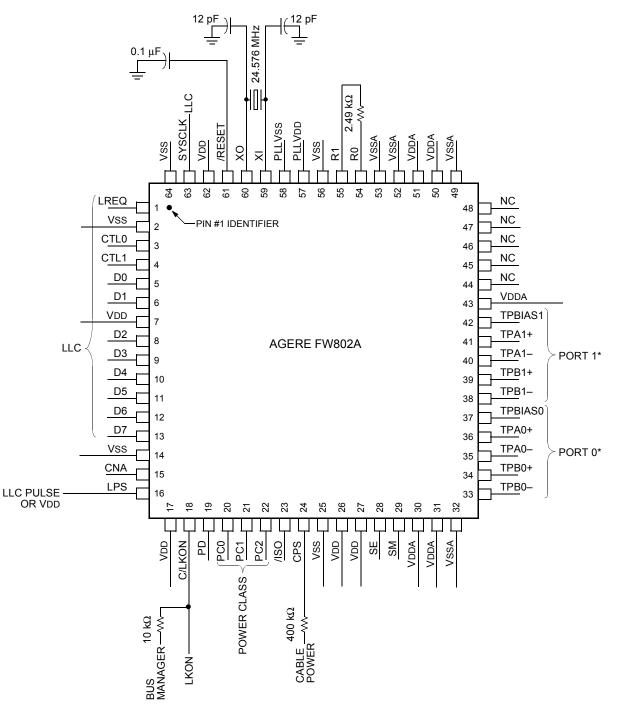

| Figure 2. Pin Assignments                                         |    |

| Figure 3. Typical External Component Connections                  |    |

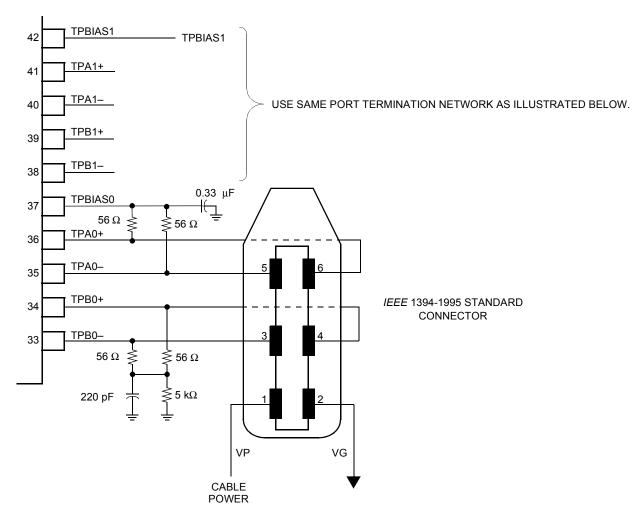

| Figure 4. Typical Port Termination Network                        | 11 |

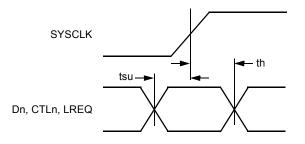

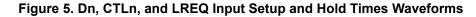

| Figure 5. Dn, CTLn, and LREQ Input Setup and Hold Times Waveforms | 17 |

| Figure 6. Dn, CTLn Output Delay Relative to SYSCLK Waveforms      | 17 |

# **List of Tables**

### Tables

### Page

| Table 1. Signal Descriptions                              | 7    |

|-----------------------------------------------------------|------|

| Table 2. Absolute Maximum Ratings                         |      |

| Table 3. Analog Characteristics                           |      |

| Table 4. Driver Characteristics                           | 14   |

| Table 5. Device Characteristics                           | 15   |

| Table 6. Switching Characteristics                        | 16   |

| Table 7. Clock Characteristics                            | 16   |

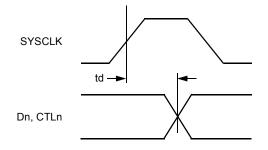

| Table 8. PHY Register Map for the Cable Environment       | 18   |

| Table 9. PHY Register Fields for the Cable Environment    | . 18 |

| Table 10. PHY Register Page 0: Port Status Page           | . 20 |

| Table 11. PHY Register Port Status Page Fields            | . 21 |

| Table 12. PHY Register Page 1: Vendor Identification Page | . 22 |

| Table 13. PHY Register Vendor Identification Page Fields  | 22   |

|                                                           |      |

#### Page

## Description

The Agere Systems Inc. FW802A device provides the analog physical layer functions needed to implement a two-port node in a cable-based *IEEE* 1394-1995 and *IEEE* 1394a-2000 network.

Each cable port incorporates two differential line transceivers. The transceivers include circuitry to monitor the line conditions as needed for determining connection status, for initialization and arbitration, and for packet reception and transmission. The PHY is designed to interface with a link-layer controller (LLC).

The PHY requires either an external 24.576 MHz crystal or crystal oscillator. The internal oscillator drives an internal phase-locked loop (PLL), which generates the required 400 MHz reference signal. The 400 MHz reference signal is internally divided to provide the 49.152 MHz, 98.304 MHz, and 196.608 MHz clock signals that control transmission of the outbound encoded strobe and data information. The 49.152 MHz clock signal is also supplied to the associated LLC for synchronization of the two chips and is used for resynchronization of the received data. The powerdown function, when enabled by the PD signal high, stops operation of the PLL and disables all circuitry except the cable-not-active signal circuitry.

The PHY supports an isolation barrier between itself and its LLC. When /ISO is tied high, the link interface outputs behave normally. When /ISO is tied low, internal differentiating logic is enabled, and the outputs become short pulses, which can be coupled through a capacitor or transformer as described in the *IEEE* 1394-1995 Annex J. To operate with bus-keeper isolation, the /ISO pin of the FW802A must be tied high.

Data bits to be transmitted through the cable ports are received from the LLC on two, four, or eight data lines (D[0:7]), and are latched internally in the PHY in synchronization with the 49.152 MHz system clock. These bits are combined serially, encoded, and transmitted at 98.304 Mbits/s, 196.608 Mbits/s, or 393.216 Mbits/s as the outbound data-strobe information stream. During transmission, the encoded data information is transmitted differentially on the TPA and TPB cable pair(s).

During packet reception, the TPA and TPB transmitters of the receiving cable port are disabled, and the receivers for that port are enabled. The encoded data information is received on the TPA and TPB cable pair. The received data-strobe information is decoded to recover the receive clock signal and the serial data bits. The serial data bits are split into two, four, or eight parallel streams, resynchronized to the local system clock, and sent to the associated LLC. The received data is also transmitted (repeated) out of the other active (connected) cable ports.

Both the TPA and TPB cable interfaces incorporate differential comparators to monitor the line states during initialization and arbitration. The outputs of these comparators are used by the internal logic to determine the arbitration status. The TPA channel monitors the incoming cable common-mode voltage. The value of this common-mode voltage is used during arbitration to set the speed of the next packet transmission. In addition, the TPB channel monitors the incoming cable common-mode voltage for the presence of the remotely supplied twisted-pair bias voltage. This monitor is called bias-detect.

The TPBIAS circuit monitors the value of incoming TPA pair common-mode voltage when local TPBIAS is inactive. Because this circuit has an internal current source and the connected node has a current sink, the monitored value indicates the cable connection status. This monitor is called connect-detect.

Both the TPB bias-detect monitor and TPBIAS connect-detect monitor are used in suspend/resume signaling and cable connection detection.

The PHY provides a 1.86 V nominal bias voltage for driver load termination. This bias voltage, when seen through a cable by a remote receiver, indicates the presence of an active connection. The value of this bias voltage has been chosen to allow interoperability between transceiver chips operating from 5 V or 3 V nominal supplies. This bias voltage source should be stabilized by using an external filter capacitor of approximately 0.33  $\mu$ F.

The transmitter circuitry, the receiver circuitry, and the twisted-pair bias voltage circuity are all disabled with a powerdown condition. The powerdown condition occurs when the PD input is high. The port transmitter circuitry, the receiver circuitry, and the TPBIAS output are also disabled when the port is disabled, suspended, or disconnected.

The line drivers in the PHY operate in a highimpedance current mode and are designed to work with external 112  $\Omega$  line-termination resistor networks. One network is provided at each end of each twistedpair cable. Each network is composed of a pair of series-connected 56  $\Omega$  resistors. The midpoint of the pair of resistors that is directly connected to the twisted-pair A (TPA) signals is connected to the PBIAS voltage signal. The midpoint of the pair of

Agere Systems Inc.

## Description (continued)

resistors that is directly connected to the twisted-pair B (TPB) signals is coupled to ground through a parallel RC network with recommended resistor and capacitor values of 5 k $\Omega$  and 220 pF, respectively.

The value of the external resistors are specified to meet the standard specifications when connected in parallel with the internal receiver circuits.

The driver output current, along with other internal operating currents, is set by an external resistor. This resistor is connected between the R0 and R1 signals and has a value of 2.49 k $\Omega \pm 1\%$ .

The FW802A supports suspend/resume as defined in the *IEEE* 1394a-2000 specification. The suspend mechanism allows an FW802A port to be put into a suspended state. In this state, a port is unable to transmit or receive data packets, however, it remains capable of detecting connection status changes and detecting incoming TPBias. When all ports of the FW802A are suspended, all circuits except the bias voltage reference generator, and bias detection circuits are powered down, resulting in significant power savings. The use of suspend/resume is recommended.

Four signals are used as inputs to set four configuration status bits in the self-identification (self-ID) packet. These signals are hardwired high or low as a function of the equipment design. PC[0:2] are the three signals that indicate either the need for power from the cable or the ability to supply power to the cable. The fourth signal, C/LKON, as an input, indicates whether a node is a contender for bus manager. When the C/LKON signal is asserted, it means the node is a contender for bus manager. When the signal is not asserted, it means that the node is not a contender. The C bit corresponds to bit 20 in the self-ID packet, PC0 corresponds to bit 21, PC1 corresponds to bit 22, and PC2 corresponds to bit 23 (see Table 4-29 of the IEEE 1394-1995 standard for additional details).

A powerdown signal (PD) is provided to allow a powerdown mode where most of the PHY circuits are powered down to conserve energy in battery-powered applications. The internal logic in FW802A is reset as long as the powerdown signal is asserted. A cable status signal, CNA, provides a high output when none of the twisted-pair cable ports are receiving incoming bias voltage. This output is not debounced. The CNA output can be used to determine when to power the PHY down or up. In the powerdown mode, all circuitry is disabled except the CNA circuitry. It should be noted that when the device is powered down, it does not act in a repeater mode.

When the power supply of the PHY is removed while the twisted-pair cables are connected, the PHY transmitter and receiver circuitry has been designed to present a high impedance to the cable in order to not load the TPBIAS signal voltage on the other end of the cable.

For reliable operation, the TPBn signals must be terminated using the normal termination network regardless of whether a cable is connected to a port or not connected to a port. For those applications, when FW802A is used with one of the ports not brought out to a connector, those unused ports may be left unconnected without normal termination. When a port does not have a cable connected, internal connectdetect circuitry will keep the port in a disconnected state.

**Note:** All gap counts on all nodes of a 1394 bus must be identical. This may be accomplished by using PHY configuration packets (see Section 4.3.4.3 of *IEEE* 1394-1995 standard) or by using two bus resets, which resets the gap counts to the maximum level (3Fh).

The link power status (LPS) signal works with the C/LKON signal to manage the LLC power usage of the node. The LPS signal indicates that the LLC of the node is powered up or powered down. If LPS is inactive for more than 1.2  $\mu$ s and less than 25  $\mu$ s, PHY/link interface is reset. If LPS is inactive for greater than  $25 \,\mu$ s, the PHY will disable the PHY/link interface to save power. FW802A continues its repeater function. If the PHY then receives a link-on packet, the C/LKON signal is activated to output a 6.114 MHz signal, which can be used by the LLC to power itself up. Once the LLC is powered up, the LPS signal communicates this to the PHY and the PHY/link interface is enabled. C/LKON signal is turned off when LPS is active or when a bus reset occurs, provided the interrupt that caused C/LKON is not present.

When the PHY/link interface is in the disabled state, the FW802A will automatically enter a low-power mode, if all ports are inactive (disconnected, disabled, or suspended). In this low-power mode, the FW802A disables its PLL and also disables parts of reference circuitry depending on the state of the ports (some reference circuitry must remain active in order to detect incoming TP bias). The lowest power consumption (the microlow-power sleep mode) is attained when all ports are either disconnected or disabled with the ports interrupt enable bit cleared. The FW802A will exit the lowpower mode when the LPS input is asserted high or when a port event occurs that requires the FW802A

#### **Description** (continued)

to become active in order to respond to the event or to notify the LLC of the event (e.g., incoming bias or disconnection is detected on a suspended port, a new connection is detected on a nondisabled port, etc.). The SYSCLK output will become active (and the PHY/ link interface will be initialized and become operative) within 3 ms after LPS is asserted high, when the FW802A is in the low-power mode. Two of the signals are used to set up various test conditions used in manufacturing. These signals (SE and SM) should be connected to Vss for normal operation.

5-5459.f (F)

Figure 1. Block Diagram

## **Signal Information**

Note: Active-low signals are indicated by "/" at the beginning of signal names, within this document.

5-6236.b (F)

Figure 2. Pin Assignments

# Signal Information (continued)

### Table 1. Signal Descriptions

| Pin                              | Signal* | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18                               | C/LKON  | I/O  | <b>Bus Manager Capable Input and Link-On Output.</b> On hardware reset, this pin is used to set the default value of the contender status indicated during self-ID. The bit value programming is done by tying the signal through a 10 k $\Omega$ resistor to VDD (high, bus manager capable) or to GND (low, not bus manager capable). Using either the pull-up or pull-down resistor allows the link-on output to override the input value when necessary.                                                                                                                                                                                              |

|                                  |         |      | After hardware reset, this pin is set as an output. If the LPS is inactive, C/LKON indicates one of the following events by asserting a 6.114 MHz signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  |         |      | <ol> <li>FW802A receives a link-on packet addressed to this node.</li> <li>Port_event register bit is 1.</li> <li>Any of the Timeout, Pwr_Fail, or Loop register bits are 1 and the<br/>Resume_int register bit is also 1. Once activated, the C/LKON output<br/>will continue active until the LPS becomes active. The PHY also deas-<br/>serts the C/LKON output when a bus reset occurs, if the C/LKON is<br/>active due solely to the reception of a link-on packet.</li> </ol>                                                                                                                                                                       |

|                                  |         |      | <b>Note:</b> If an interrupt condition exists which would otherwise cause the C/LKON output to be activated if the LPS were inactive, the C/LKON output will be activated when the LPS subsequently becomes inactive.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                               | CNA     | 0    | <b>Cable-Not-Active Output.</b> CNA is asserted high when none of the PHY ports are receiving an incoming bias voltage. This circuit remains active during the powerdown mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 24                               | CPS     | Ι    | <b>Cable Power Status.</b> CPS is normally connected to the cable power through a 400 k $\Omega$ resistor. This circuit drives an internal comparator that detects the presence of cable power. This information is maintained in one internal register and is available to the LLC by way of a register read (see Table 8, Register 0).                                                                                                                                                                                                                                                                                                                  |

| 3                                | CTL0    | I/O  | <b>Control I/O.</b> The CTLn signals are bidirectional communications control signals between the PHY and the LLC. These signals control the passage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4                                | CTL1    |      | of information between the two devices. Bus-keeper circuitry is built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5, 6, 8,<br>9, 10, 11,<br>12, 13 | D[0:7]  | I/O  | <b>Data I/O.</b> The Dn signals are bidirectional and pass data between the PHY and the LLC. Bus-keeper circuitry is built into these terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23                               | /ISO    | Ι    | Link Interface Isolation Disable Input (Active-Low). /ISO controls the operation of an internal pulse differentiating function used on the PHY-LLC interface signals, CTLn and Dn, when they operate as outputs. When /ISO is asserted low, the isolation barrier is implemented between PHY and its LLC (as described in Annex J of <i>IEEE</i> 1394-1995). /ISO is normally tied high to disable isolation differentiation. Bus-keepers are enabled when /ISO is high (inactive) on CTL, D, and LREQ. When /ISO is low (active), the bus-keepers are disabled. Please refer to Agere's application note AP98-074CMPR for more information on isolation. |

\* Active-low signals are indicated by "/" at the beginning of signal names, within this document.

# Signal Information (continued)

Table 1. Signal Descriptions (continued)

| Pin                   | Signal* | Туре       | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                    | LPS     | I          | <b>Link Power Status.</b> LPS is connected to either the VDD supplying the LLC or to a pulsed output that is active when the LLC is powered for the purpose of monitoring the LLC power status. If LPS is inactive for more than 1.2 $\mu$ s and less than 25 $\mu$ s, interface is reset. If LPS is inactive for greater than 25 $\mu$ s, the PHY will disable the PHY/Link interface to save power. FW802A continues its repeater function.  |

| 1                     | LREQ    | I          | <b>Link Request.</b> LREQ is an output from the LLC that requests the PHY to perform some service. Bus-keeper circuitry is built into this terminal.                                                                                                                                                                                                                                                                                           |

| 44, 45, 46,<br>47, 48 | NC      | _          | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20                    | PC0     | I          | Power-Class Indicators. On hardware reset, these inputs set the default                                                                                                                                                                                                                                                                                                                                                                        |

| 21                    | PC1     |            | value of the power class indicated during self-ID. These bits can be                                                                                                                                                                                                                                                                                                                                                                           |

| 22                    | PC2     |            | programmed by tying the signals to VDD (high) or to ground (low).                                                                                                                                                                                                                                                                                                                                                                              |

| 19                    | PD      | I          | <b>Powerdown.</b> When asserted high, PD turns off all internal circuitry except the bias-detect circuits that drive the CNA signal. Internal FW802A logic is kept in the reset state as long as PD is asserted. PD terminal is provided for backward compatibility. It is recommended that the FW802A be allowed to manage its own power consumption using suspend/resume in conjunction with LPS. C/LKON features are defined in 1394a-2000. |

| 57                    | PLLVDD  | _          | <b>Power for PLL Circuit.</b> PLLVDD supplies power to the PLL circuitry portion of the device.                                                                                                                                                                                                                                                                                                                                                |

| 58                    | PLLVss  | —          | Ground for PLL Circuit. PLLVss is tied to a low-impedance ground plane.                                                                                                                                                                                                                                                                                                                                                                        |

| 54                    | R0      | I          | <b>Current Setting Resistor.</b> An internal reference voltage is applied to a resistor connected between R0 and R1 to set the operating current and the cable driver output current. A low temperature-coefficient resistor                                                                                                                                                                                                                   |

| 55                    | R1      |            | (TCR) with a value of 2.49 k $\Omega \pm 1\%$ should be used to meet the <i>IEEE</i> 1394-1995 standard requirements for output voltage limits.                                                                                                                                                                                                                                                                                                |

| 61                    | /RESET  | I          | <b>Reset (Active-Low).</b> When /RESET is asserted low (active), the FW802A is reset. An internal pull-up resistor, which is connected to VDD, is provided, so only an external delay capacitor is required. This input is a standard logic buffer and can also be driven by an open-drain logic output buffer.                                                                                                                                |

| 28                    | SE      | I          | <b>Test Mode Control.</b> SE is used during the manufacturing test and should be tied to Vss.                                                                                                                                                                                                                                                                                                                                                  |

| 29                    | SM      | Ι          | <b>Test Mode Control.</b> SM is used during the manufacturing test and should be tied to Vss.                                                                                                                                                                                                                                                                                                                                                  |

| 63                    | SYSCLK  | 0          | <b>System Clock.</b> SYSCLK provides a 49.152 MHz clock signal, which is synchronized with the data transfers to the LLC.                                                                                                                                                                                                                                                                                                                      |

| 36                    | TPA0+   | Analog I/O | Portn, Port Cable Pair A. TPAn is the port A connection to the twisted-                                                                                                                                                                                                                                                                                                                                                                        |

| 41                    | TPA1+   |            | pair cable. Board traces from each pair of positive and negative differen-<br>tial signal pins should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                                                                                                                                   |

\* Active-low signals are indicated by "/" at the beginning of signal names, within this document.

# Signal Information (continued)

### Table 1. Signal Descriptions (continued)

| Pin                   | Signal* | Туре       | Name/Description                                                                                                                                                                                                                                                                                                                  |

|-----------------------|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35                    | TPA0-   | Analog I/O | Portn, Port Cable Pair A. TPAn is the port A connection to the twisted-                                                                                                                                                                                                                                                           |

| 40                    | TPA1-   |            | pair cable. Board traces from each pair of positive and negative differen-<br>tial signal pins should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                      |

| 34                    | TPB0+   | Analog I/O | Portn, Port Cable Pair B. TPBn is the port B connection to the twisted-                                                                                                                                                                                                                                                           |

| 39                    | TPB1+   |            | pair cable. Board traces from each pair of positive and negative differen-<br>tial signal pins should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                      |

| 33                    | TPB0-   | Analog I/O |                                                                                                                                                                                                                                                                                                                                   |

| 38                    | TPB1–   | -          | pair cable. Board traces from each pair of positive and negative differen-<br>tial signal pins should be kept matched and as short as possible to the<br>external load resistors and to the cable connector.                                                                                                                      |

| 37                    | TPBIAS0 | Analog I/O | Portn, Twisted-Pair Bias. TPBIAS provides the 1.86 V nominal bias                                                                                                                                                                                                                                                                 |

| 42                    | TPBIAS1 | -          | voltage needed for proper operation of the twisted-pair cable drivers and receivers and for sending a valid cable connection signal to the remote nodes.                                                                                                                                                                          |

| 7, 17,<br>26, 27, 62  | Vdd     | —          | <b>Digital Power.</b> VDD supplies power to the digital portion of the device.                                                                                                                                                                                                                                                    |

| 30, 31,<br>43, 50, 51 | Vdda    | —          | <b>Analog Circuit Power.</b> VDDA supplies power to the analog portion of the device.                                                                                                                                                                                                                                             |

| 2, 14,<br>25, 56, 64  | Vss     | —          | <b>Digital Ground.</b> All Vss signals should be tied to the low-impedance ground plane.                                                                                                                                                                                                                                          |

| 32, 49,<br>52, 53     | Vssa    | —          | <b>Analog Circuit Ground.</b> All VSSA signals should be tied together to a low-<br>impedance ground plane.                                                                                                                                                                                                                       |

| 59                    | XI      | —          | <b>Crystal Oscillator.</b> XI and XO connect to a 24.576 MHz parallel resonant fundamental mode crystal. Although, when a 24.576 MHz clock source is used, it can be connected to XI with XO left unconnected. The optimum                                                                                                        |

| 60                    | XO      |            | values for the external shunt capacitors are dependent on the specifica-<br>tions of the crystal used. It is suggested that two 12 pF shunt capacitors<br>be used for a crystal with a specified 7 pF loading capacitance. For more<br>details, see Crystal Selection Considerations in the Application Informa-<br>tion section. |

\* Active-low signals are indicated by "/" at the beginning of signal names, within this document.

### **Application Information**

5-6767 (F)

\* See Figure 4 for typical port termination network.

#### Figure 3. Typical External Component Connections

### Application Information (continued)

Figure 4. Typical Port Termination Network

# **1394 Application Support Contact Information**

E-mail: 1394support@agere.com

# **Crystal Selection Considerations**

The FW802A is designed to use an external 24.576 MHz crystal connected between the XI and XO terminals to provide the reference for an internal oscillator circuit. *IEEE* 1394a-2000 standard requires that FW802A have less than  $\pm$ 100 ppm total variation from the nominal data rate, which is directly influenced by the crystal. To achieve this, it is recommended that an oscillator with a nominal 50 ppm or less frequency tolerance be used.

The total frequency variation must be kept below  $\pm 100$  ppm from nominal with some allowance for error introduced by board and device variations. Trade offs between frequency tolerance and stability may be made as long as the total frequency variation is less than  $\pm 100$  ppm.

Agere Systems Inc.

5-6930 (F)

### Crystal Selection Considerations (continued)

### Load Capacitance

The frequency of oscillation is dependent upon the load capacitance specified for the crystal, in parallel resonant mode crystal circuits. Total load capacitance (CL) is a function of not only the discrete load capacitors, but also capacitances from the FW802A board traces and capacitances of the other FW802A connected components.

The values for load capacitors (C<sub>A</sub> and C<sub>B</sub>) should be calculated using this formula:

$C_A = C_B = (C_L - C_{stray}) \times 2$

Where:

$C_L$  = load capacitance specified by the crystal manufacturer  $C_{strav}$  = capacitance of the board and the FW802A, typically 2—3 pF

## **Board Layout**

The layout of the crystal portion of the PHY circuit is important for obtaining the correct frequency and minimizing noise introduced into the FW802A PLL. The crystal and two load capacitors should be considered as a unit during layout. They should be placed as close as possible to one another, while minimizing the loop area created by the combination of the three components. Minimizing the loop area minimizes the effect of the resonant current that flows in this resonant circuit. This layout unit (crystal and load capacitors) should then be placed as close as possible to the PHY XI and XO terminals to minimize trace lengths. Vias should not be used to route the XI and XO signals.

# **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

#### Table 2. Absolute Maximum Ratings

| Parameter                          | Symbol | Min  | Мах       | Unit |

|------------------------------------|--------|------|-----------|------|

| Supply Voltage Range               | Vdd    | 3.0  | 3.6       | V    |

| Input Voltage Range*               | VI     | -0.5 | VDD + 0.5 | V    |

| Output Voltage Range at Any Output | Vo     | -0.5 | Vdd + 0.5 | V    |

| Operating Free Air Temperature     | TA     | 0    | 70        | °C   |

| Storage Temperature Range          | Tstg   | -65  | 150       | °C   |

\* Except for 5 V tolerant I/O (CTL0, CTL1, D0—D7, and LREQ) where VI max = 5.5 V.

# **Electrical Characteristics**

### Table 3. Analog Characteristics

| Parameter                                 | Test Conditions                                 | Symbol        | Min      | Тур | Max   | Unit |

|-------------------------------------------|-------------------------------------------------|---------------|----------|-----|-------|------|

| Supply Voltage                            | Source power node                               | VDD—SP        | 3.0      | 3.3 | 3.6   | V    |

| Differential Input Voltage                | Cable inputs, 100 Mbits/s operation             | VID—100       | 142      | —   | 260   | mV   |

|                                           | Cable inputs, 200 Mbits/s operation             | VID-200       | 132      |     | 260   | mV   |

|                                           | Cable inputs, 400 Mbits/s operation             | VID-400       | 100      |     | 260   | mV   |

|                                           | Cable inputs, during arbitration                | VID—ARB       | 168      | _   | 265   | mV   |

| Common-mode Voltage                       | TPB cable inputs,                               | Vсм           | 1.165    | _   | 2.515 | V    |

| Source Power Mode                         | speed signaling off                             |               |          |     |       |      |

|                                           | TPB cable inputs,                               | VCM—SP—100    | 1.165    |     | 2.515 | V    |

|                                           | S100 speed signaling on                         |               | 0.005    |     | 0.545 | N    |

|                                           | TPB cable inputs,<br>S200 speed signaling on    | VCM—SP—200    | 0.935    |     | 2.515 | V    |

|                                           | TPB cable inputs,                               | VCM—SP—400    | 0.532    |     | 2.515 | V    |

|                                           | S400 speed signaling on                         | V CIVI-3P-400 | 0.552    |     | 2.515 | v    |

| Common-mode Voltage                       | TPB cable inputs,                               | Vсм           | 1.165    |     | 2.015 | V    |

| Nonsource Power Mode*                     | speed signaling off                             |               |          |     |       |      |

|                                           | TPB cable inputs,                               | VCM—NSP—100   | 1.165    |     | 2.015 | V    |

|                                           | S100 speed signaling on                         |               |          |     |       |      |

|                                           | TPB cable inputs,                               | VCM—NSP—200   | 0.935    | —   | 2.015 | V    |

|                                           | S200 speed signaling on                         |               |          |     |       |      |

|                                           | TPB cable inputs,                               | VCM—NSP—400   | 0.532    |     | 2.015 | V    |

|                                           | S400 speed signaling on                         |               |          |     |       |      |

| Receive Input Jitter                      | TPA, TPB cable inputs,                          | _             | -        |     | 1.08  | ns   |

|                                           | 100 Mbits/s operation                           |               |          |     | 0.5   |      |

|                                           | TPA, TPB cable inputs,<br>200 Mbits/s operation | _             | _        |     | 0.5   | ns   |

|                                           | TPA, TPB cable inputs,                          |               |          |     | 0.315 | ns   |

|                                           | 400 Mbits/s operation                           |               |          |     | 0.515 | 115  |

| Receive Input Skew                        | Between TPA and TPB cable inputs,               |               |          |     | 0.8   | ns   |

|                                           | 100 Mbits/s operation                           |               |          |     |       |      |

|                                           | Between TPA and TPB cable inputs,               | _             | _        |     | 0.55  | ns   |

|                                           | 200 Mbits/s operation                           |               |          |     |       |      |

|                                           | Between TPA and TPB cable inputs,               | —             | —        |     | 0.5   | ns   |

|                                           | 400 Mbits/s operation                           |               |          |     |       |      |

| Positive Arbitration                      | —                                               | Vth+          | 89       |     | 168   | mV   |

| Comparator Input                          |                                                 |               |          |     |       |      |

| Threshold Voltage<br>Negative Arbitration |                                                 |               | -168     |     | -89   | m)/  |

| Comparator Input                          | —                                               | Vth-          | -100     |     | -09   | mV   |

| Threshold Voltage                         |                                                 |               |          |     |       |      |

| Speed Signal Input                        | 200 Mbits/s                                     | VTH—S200      | 45       | —   | 139   | mV   |

| Threshold Voltage                         | 400 Mbits/s                                     | VTH—S400      | 266      | —   | 445   | mV   |

| Output Current                            | TPBIAS outputs                                  | lo            | 5        | —   | 2.5   | mA   |

| TPBIAS Output Voltage                     | At rated I/O current                            | Vo            | 1.665    | —   | 2.015 | V    |

| Current Source for                        | _                                               | ICD           | <u> </u> | —   | 76    | μA   |

| Connect Detect Circuit                    |                                                 |               |          |     |       |      |

\* For a node that does not source power (see Section 4.2.2.2 in IEEE 1394-1995 Standard).

Agere Systems Inc.

## Electrical Characteristics (continued)

#### **Table 4. Driver Characteristics**

| Parameter                                              | Test Conditions                                  | Symbol | Min   | Тур | Max   | Unit |

|--------------------------------------------------------|--------------------------------------------------|--------|-------|-----|-------|------|

| Differential Output Voltage                            | 56 Ω load                                        | Vod    | 172   | —   | 265   | mV   |

| Off-state Common-mode Voltage                          | Drivers disabled                                 | Voff   | _     | _   | 20    | mV   |

| Driver Differential Current,<br>TPA+, TPA–, TPB+, TPB– | Driver enabled,<br>speed signaling off*          | Idiff  | -1.05 | —   | 1.05  | mA   |

| Common-mode Speed Signaling<br>Current, TPB+, TPB–     | 200 Mbits/s speed signaling enabled <sup>†</sup> | ISP    | -2.53 | —   | -4.84 | mA   |

|                                                        | 400 Mbits/s speed signaling enabled <sup>†</sup> | ISP    | -8.1  | —   | -12.4 | mA   |

\* Limits are defined as the algebraic sum of TPA+ and TPA- driver currents. Limits also apply to TPB+ and TPB- as the algebraic sum of driver currents.

† Limits are defined as the absolute limit of each of TPB+ and TPB- driver currents.

# Electrical Characteristics (continued)

#### **Table 5. Device Characteristics**

| Parameter                                                                                     | Test Conditions         | Symbol                   | Min           | Тур                  | Мах         | Unit                 |

|-----------------------------------------------------------------------------------------------|-------------------------|--------------------------|---------------|----------------------|-------------|----------------------|

| Supply Current:<br>One Port Active<br>All Ports Active<br>Microlow-Power Sleep Mode<br>PD = 1 | VDD = 3.3 V             | IDD<br>IDD<br>IDD<br>IDD | <br>          | 54<br>74<br>50<br>50 | <br>        | mA<br>mA<br>μA<br>μA |

| High-level Output Voltage                                                                     | Іон max, Vdd = min      | Vон                      | Vdd - 0.4     | —                    | _           | V                    |

| Low-level Output Voltage                                                                      | IOL min, VDD = max      | Vol                      | —             | —                    | 0.4         | V                    |

| High-level Input Voltage                                                                      | CMOS inputs             | Vін                      | 0.7Vdd        | —                    | —           | V                    |

| Low-level Input Voltage                                                                       | CMOS inputs             | VIL                      | —             | —                    | 0.2VDD      | V                    |

| Pull-up Current,<br>/RESET Input                                                              | VI = 0 V                | lı                       | 11            | _                    | 32          | μA                   |

| Powerup Reset Time,<br>/RESET Input                                                           | VI = 0 V                | _                        | 2             | —                    |             | ms                   |

| Rising Input Threshold Voltage<br>/RESET Input                                                | _                       | VIRST                    | 1.1           | —                    | 1.4         | V                    |

| Output Current                                                                                | SYSCLK                  | Iol/Ioн<br>@ TTL         | -16           | —                    | 16          | mA                   |

|                                                                                               | Control, data           | Iol/Ioн<br>@ CMOS        | -12           | —                    | 12          | mA                   |

|                                                                                               | CNA                     | IOL/IOH                  | -16           | _                    | 16          | mA                   |

|                                                                                               | C/LKON                  | IOL/IOH                  | -2            | —                    | 2           | mA                   |

| Input Current,<br>LREQ, LPS, PD, SE, SM,<br>PC[0:2] Inputs                                    | VI = VDD or 0 V         | li                       |               | _                    | °±1         | μA                   |

| Off-state Output Current,<br>CTL[0:1], D[0:7], C/LKON I/Os                                    | Vo = VDD or 0 V         | loz                      | —             | —                    | °±5         | μA                   |

| Power Status Input Threshold<br>Voltage, CPS Input                                            | 400 k $\Omega$ resistor | Vтн                      | 7.5           | —                    | 8.5         | V                    |

| Rising Input Threshold Voltage*,<br>LREQ, CTLn, Dn                                            | _                       | VIT+                     | VDD/2 + 0.3   | —                    | VDD/2 + 0.8 | V                    |

| Falling Input Threshold Voltage*,<br>LREQ, CTLn, Dn                                           | _                       | Vit–                     | Vdd/2 - 0.8   | —                    | VDD/2 - 0.3 | V                    |

| Bus Holding Current,<br>LREQ, CTLn, Dn                                                        | VI = 1/2(VDD)           | —                        | 250           | —                    | 550         | μA                   |

| Rising Input Threshold Voltage<br>LPS                                                         | _                       | VLIH                     | _             | —                    | 0.24VDD + 1 | V                    |

| Falling Input Threshold Voltage<br>LPS                                                        | —                       | VLIL                     | 0.24VDD + 0.2 | —                    | —           | V                    |

\* Device is capable of both differentiated and undifferentiated operation.

# **Timing Characteristics**

#### **Table 6. Switching Characteristics**

| Symbol | Parameter                                   | Measured               | Test Conditions          | Min | Тур | Max  | Unit |

|--------|---------------------------------------------|------------------------|--------------------------|-----|-----|------|------|

|        | Jitter, Transmit                            | TPA, TPB               | —                        |     |     | 0.15 | ns   |

| —      | Transmit Skew                               | Between<br>TPA and TPB | _                        | _   | —   | ±0.1 | ns   |

| tr     | Rise Time, Transmit (TPA/TPB)               | 10% to 90%             | Rι = 56 Ω,<br>Cι = 10 pF | —   | —   | 1.2  | ns   |

| tf     | Fall Time, Transmit (TPA/TPB)               | 90% to 10%             | Rι = 56 Ω,<br>Cι = 10 pF | —   | —   | 1.2  | ns   |

| tsu    | Setup Time,<br>Dn, CTLn, LREQ↑↓ to SYSCLK↑  | 50% to 50%             | See Figure 5             | 6   | —   | —    | ns   |

| th     | Hold Time,<br>Dn, CTLn, LREQ↑↓ from SYSCLK↑ | 50% to 50%             | See Figure 5             | 0   | _   | _    | ns   |

| td     | Delay Time,<br>SYSCLK↑ to Dn, CTLn↑↓        | 50% to 50%             | See Figure 6             | 1   |     | 6    | ns   |

#### **Table 7. Clock Characteristics**

| Parameter                       | Symbol | Min     | Тур     | Max     | Unit |

|---------------------------------|--------|---------|---------|---------|------|

| External Clock Source Frequency | f      | 24.5735 | 24.5760 | 24.5785 | MHz  |

# **Timing Waveforms**

5-6017.a (F)

5-6018.a (F)

Figure 6. Dn, CTLn Output Delay Relative to SYSCLK Waveforms

Agere Systems Inc.

## **Internal Register Configuration**

The PHY register map is shown below in Table 8.

#### Table 8. PHY Register Map for the Cable Environment

| Address | Contents                |                                  |        |          |         |            |            |            |  |  |

|---------|-------------------------|----------------------------------|--------|----------|---------|------------|------------|------------|--|--|

|         | Bit 0                   | Bit 1                            | Bit 2  | Bit 3    | Bit 4   | Bit 5      | Bit 6      | Bit 7      |  |  |

| 00002   |                         |                                  | Physic | al_ID    |         |            | R          | PS         |  |  |

| 00012   | RHB IBR Gap_count       |                                  |        |          |         |            |            |            |  |  |

| 00102   | E                       | xtended (7)                      |        | XXXXX    |         | Tota       | l_ports    |            |  |  |

| 00112   | Max_speed XXXXX Delay   |                                  |        |          |         |            |            |            |  |  |

| 01002   | LCtrl                   | LCtrl Contender Jitter Pwr_class |        |          |         |            |            |            |  |  |

| 01012   | Resume_int              | ISBR                             | Loop   | Pwr_fail | Timeout | Port_event | Enab_accel | Enab_multi |  |  |

| 01102   | XXXXX                   | XXXXX                            | XXXXX  | XXXXX    | XXXXX   | XXXXX      | XXXXX      | XXXXX      |  |  |

| 01112   | F                       | Page_select XXXXX Port_select    |        |          |         |            |            |            |  |  |

| 10002   |                         | Register 0 Page_select           |        |          |         |            |            |            |  |  |

| •       | •                       |                                  |        |          |         |            |            |            |  |  |

| 11112   |                         | Register 7 Page_select           |        |          |         |            |            |            |  |  |

|         |                         |                                  |        |          |         |            |            |            |  |  |

|         | REQUIRED XXXXX RESERVED |                                  |        |          |         |            |            |            |  |  |

The meaning of the register fields within the PHY register map are defined by Table 9 below. Power reset values not specified are resolved by the operation of the PHY state machines subsequent to a power reset.

| Field       | Size | Туре | Power Reset<br>Value | Description                                                                                                                                                                                                                                                   |

|-------------|------|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical_ID | 6    | r    | 000000               | The address of this node determined during self-identification. A value of 63 indicates a malconfigured bus; the link will not transmit any packets.                                                                                                          |

| R           | 1    | r    | 0                    | When set to one, indicates that this node is the root.                                                                                                                                                                                                        |

| PS          | 1    | r    | —                    | Cable power active.                                                                                                                                                                                                                                           |

| RHB         | 1    | rw   | 0                    | Root hold-off bit. When set to one, the force_root variable is TRUE, which instructs the PHY to attempt to become the root during the next tree identify process.                                                                                             |

| IBR         | 1    | rw   | 0                    | Initiate bus reset. When set to one, instructs the PHY to set ibr TRUE and reset_time to RESET_TIME. These values in turn cause the PHY to initiate a bus reset without arbitration; the reset signal is asserted for 166 $\mu$ s. This bit is self-clearing. |

| Gap_count   | 6    | rw   | 3F16                 | Used to configure the arbitration timer setting in order to optimize gap times according to the topology of the bus. See Section 4.3.6 of <i>IEEE</i> Standard 1394-1995 for the encoding of this field.                                                      |

| Extended    | 3    | r    | 7                    | This field has a constant value of seven, which indicates the extended PHY register map.                                                                                                                                                                      |

# Internal Register Configuration (continued)

| Field       | Size | Туре | Power Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total_ports | 4    | r    | 2                 | The number of ports implemented by this PHY. This count reflects the number.                                                                                                                                                                                                                                                                                                                                                 |

| Max_speed   | 3    | r    | 0102              | Indicates the speed(s) this PHY supports:<br>0002 = 98.304 Mbits/s<br>0012 = 98.304 and 196.608 Mbits/s<br>0102 = 98.304, 196.608, and 393.216 Mbits/s<br>0112 = 98.304, 196.608, 393.216, and 786.43 Mbits/s<br>1002 = 98.304, 196.608, 393.216, 786.432, and<br>1,572.864 Mbits/s<br>1012 = 98.304, 196.608, 393.216, 786.432, 1,572.864, and<br>3,145.728 Mbits/s<br>All other values are reserved for future definition. |

| Delay       | 4    | r    | 0000              | Worst-case repeater delay, expressed as 144 + (delay * 20) ns.                                                                                                                                                                                                                                                                                                                                                               |

| LCtrl       | 1    | rw   | 1                 | <b>Link Active.</b> Cleared or set by software to control the value of the L bit transmitted in the node's self-ID packet 0, which will be the logical AND of this bit and LPS active.                                                                                                                                                                                                                                       |

| Contender   | 1    | rw   | See description.  | Cleared or set by software to control the value of the C bit transmitted in the self-ID packet. Powerup reset value is set by C/LKON pin.                                                                                                                                                                                                                                                                                    |

| Jitter      | 3    | r    | 000               | The difference between the fastest and slowest repeater data delay, expressed as (jitter + 1) * 20 ns.                                                                                                                                                                                                                                                                                                                       |

| Pwr_class   | 3    | rw   | See description.  | <b>Power-Class.</b> Controls the value of the pwr field transmitted in the self-ID packet. See Section 4.3.4.1 of <i>IEEE</i> Standard 1394-1995 for the encoding of this field. PC0, PC1, and PC2 pins set up power reset value.                                                                                                                                                                                            |

| Resume_int  | 1    | rw   | 0                 | <b>Resume Interrupt Enable.</b> When set to one, the PHY will set Port_event to one if resume operations commence for any port.                                                                                                                                                                                                                                                                                              |

| ISBR        | 1    | rw   | 0                 | Initiate Short (Arbitrated) Bus Reset. A write of one to this bit instructs the PHY to set ISBR true and reset_time to SHORT_RESET_TIME. These values in turn cause the PHY to arbitrate and issue a short bus reset. This bit is self-clearing.                                                                                                                                                                             |

| Loop        | 1    | rw   | 0                 | Loop Detect. A write of one to this bit clears it to zero.                                                                                                                                                                                                                                                                                                                                                                   |

| Pwr_fail    | 1    | rw   | 1                 | <b>Cable Power Failure Detect.</b> Set to one when the PS bit changes from one to zero. A write of one to this bit clears it to zero.                                                                                                                                                                                                                                                                                        |

| Timeout     | 1    | rw   | 0                 | Arbitration State Machine Timeout. A write of one to this bit clears it to zero (see MAX_ARB_STATE_TIME).                                                                                                                                                                                                                                                                                                                    |

| Port_event  | 1    | rw   | 0                 | <b>Port Event Detect.</b> The PHY sets this bit to one if any of connected, bias, disabled, or fault change for a port whose Int_enable bit is one. The PHY also sets this bit to one if resume operations commence for any port and Resume_int is one. A write of one to this bit clears it to zero.                                                                                                                        |

| Table 9. PHY Register Fields for the C | Cable Environment (continued) |

|----------------------------------------|-------------------------------|

|----------------------------------------|-------------------------------|

Agere Systems Inc.

### Internal Register Configuration (continued)

|             | •    |      |                      |                                                                                                                                                                                                                                                                          |

|-------------|------|------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field       | Size | Туре | Power Reset<br>Value | Description                                                                                                                                                                                                                                                              |

| Enab_accel  | 1    | rw   | 0                    | <b>Enable Arbitration Acceleration.</b> When set to one, the PHY will use the enhancements specified in clause 8.11 of 1394a-2000 specification. PHY behavior is unspecified if the value of Enab_accel is changed while a bus request is pending.                       |

| Enab_multi  | 1    | rw   | 0                    | Enable multispeed packet concatenation. When set to one, the link will signal the speed of all packets to the PHY.                                                                                                                                                       |

| Page_select | 3    | rw   | 000                  | Selects which of eight possible PHY register pages are accessible through the window at PHY register addresses 10002 through 11112, inclusive.                                                                                                                           |

| Port_select | 4    | rw   | 000                  | If the page selected by Page_select presents per-port information,<br>this field selects which port's registers are accessible through the<br>window at PHY register addresses 10002 through 11112, inclusive.<br>Ports are numbered monotonically starting at zero, p0. |

#### Table 9. PHY Register Fields for the Cable Environment (continued)

The port status page is used to access configuration and status information for each of the PHY's ports. The port is selected by writing zero to Page\_select and the desired port number to Port\_select in the PHY register at address 01112. The format of the port status page is illustrated by Table 10 below; reserved fields are shown shaded. The meanings of the register fields with the port status page are defined by Table 11.

#### Table 10. PHY Register Page 0: Port Status Page

| Address | Contents |              |       |            |       |           |       |          |  |  |

|---------|----------|--------------|-------|------------|-------|-----------|-------|----------|--|--|

|         | Bit 0    | Bit 1        | Bit 2 | Bit 3      | Bit 4 | Bit 5     | Bit 6 | Bit 7    |  |  |

| 10002   | ASI      | at           | BS    | stat       | Child | Connected | Bias  | Disabled |  |  |

| 10012   | Neg      | otiated_spee | ed    | Int_enable | Fault | XXXXX     | XXXXX | XXXXX    |  |  |

| 10102   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

| 10112   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

| 11002   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

| 11012   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

| 11102   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

| 11112   | XXXXX    | XXXXX        | XXXXX | XXXXX      | XXXXX | XXXXX     | XXXXX | XXXXX    |  |  |

REQUIRED

XXXXX RESERVED

# Internal Register Configuration (continued)

The meaning of the register fields with the port status page are defined by Table 11 below.

| Field            | Size | Туре | Power Reset<br>Value | Description                                                                                                                                                                                                                                                                             |

|------------------|------|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AStat            | 2    | r    | _                    | TPA line state for the port:<br>002 = invalid<br>012 = 1<br>102 = 0<br>112 = Z                                                                                                                                                                                                          |

| BStat            | 2    | r    |                      | TPB line state for the port (same encoding as AStat).                                                                                                                                                                                                                                   |

| Child            | 1    | r    | 0                    | If equal to one, the port is a child; otherwise, a parent. The meaning of this bit is undefined from the time a bus reset is detected until the PHY transitions to state T1: Child Hand-shake during the tree identify process (see Section 4.4.2.2 in <i>IEEE</i> Standard 1394-1995). |

| Connected        | 1    | r    | 0                    | If equal to one, the port is connected.                                                                                                                                                                                                                                                 |