PRODUCT SPECIFICATION

# **Z90102/103/104** 40-Pin Low-Cost Digital Television Controller

#### FEATURES

# 8-Bit CMOS Microcontroller for Consumer Television, Cable and Satellite Receiver Applications.

|        | ROM         | RAM*    |     |

|--------|-------------|---------|-----|

| Device | (KB)        | (Bytes) | I/O |

| Z90102 | 4           | 236     | 24  |

| Z90103 | 6           | 236     | 24  |

| Z90104 | 8           | 236     | 24  |

|        | al Duma a s |         |     |

Note: \*General-Purpose

- Lowest Cost DTC Family Member

- Low Power Consumption

- Fast Instruction Pointer 1.5 μs @ 4 MHz

- Two Standby Modes STOP and HALT

- Low Voltage Detection/Voltage Sensitive Reset

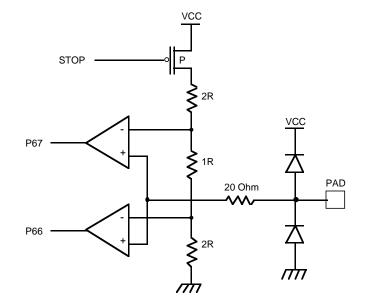

- Port 2 (8-Bit Programmable I/O) and Port 3 (2-Bit Input, 3-Bit Output) Register Mapped Ports

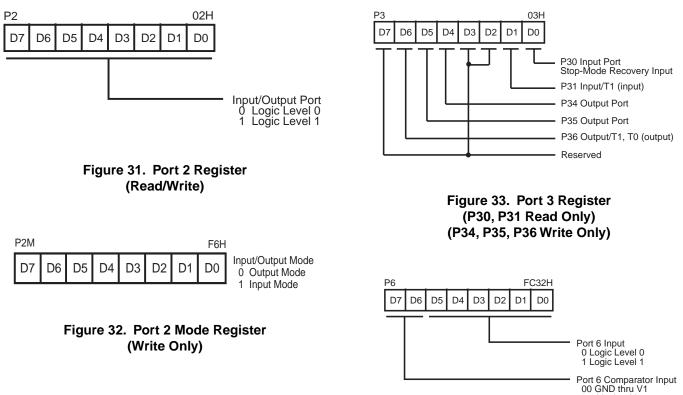

- Port 6 (6-Bit Input and Tristate Comparator AFC Input) Memory Mapped I/O Ports

- All Digital CMOS Levels Schmitt-Triggered

- Two Programmable 8-Bit Counter/Timers each with 6-Bit Programmable Prescaler.

- Six Vectored, Priority Interrupts from Six Different Sources

- Clock Speed up to 4 MHz

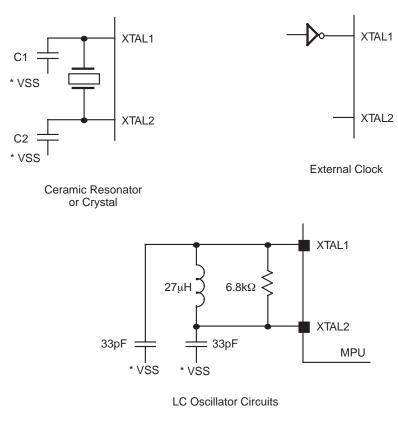

- On-Chip Oscillator that Accepts a Crystal, Ceramic Resonator, LC or External Clock Drive

- Permanently Enabled

Watch-Dog/Power-On Reset Timer

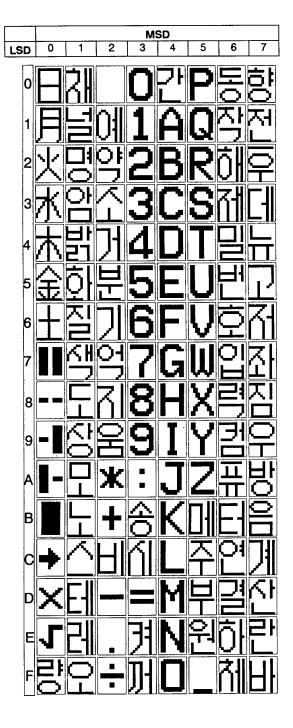

- 3K x 6-Bit Character Generator ROM

- 120 x 7-Bit Video RAM

- Mask Programmable 96-Character Set Display. The 90102 and 90103 6-Row x 20 Column Format, 12x15 Pixel Character Cell. The 90104 8-Row x 20 Column Format 12x15 Pixel Character Cell. The 90102, 90103 90104 Capable of supporting English, Korean, Thai, Chinese and Japanese High Resolution Characters.

- Fully Programmable Color Attributes Including Row Character, Row Background/Fringes, Frame Background/Position, Bar Graph Color Change, and Character Size.

- Programmable Display Position and Character Size Control

- One Pulse Width Modulator (14-Bit Resolution) for Voltage Synthesis Tuner Control.

- Three Pulse Width Modulator (8-Bit Resolution) for Picture Control

- Three Pulse Width Modulators (6-Bit Resolution) for Audio Control

#### **GENERAL DESCRIPTION**

The Z90102/3/4 40-pin Low-Cost Digital Television Controller are members of the  $Z8^{\mbox{\tiny B}}$ STOP Mode MCU singlechip family with 4, 6, and 8 KB of ROM and 236 bytes of RAM. The device is offered in a 40-pin package and is CMOS compatible. The DTC offers mask programmed ROM which enables the  $Z8^{\ensuremath{\mathbb{R}}}$  MCU to be used in a high volume production application device embedded with a custom program (customer supplied program) and combines

DS97TEL1902

#### **GENERAL DESCRIPTION** (Continued)

together with the Z86C27 and Z86127 to provide support for mid range and low end TV applications.

Zilog's DTC offers fast execution, efficient use of memory, sophisticated interrupts, input/output bit manipulation capabilities, and easy hardware/software system expansion along with low cost and low power consumption. The device provides an ideal performance and reliability solution for consumer and industrial television applications.

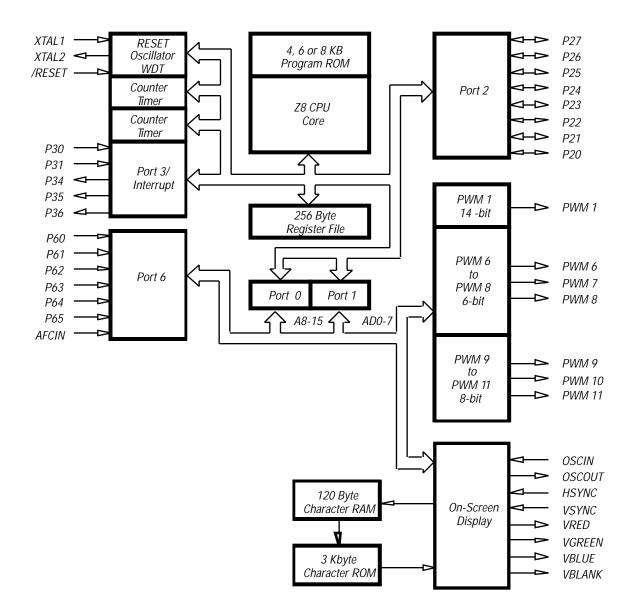

The Z90102/3/4 architecture is characterized by utilizing Zilog's advanced Superintegration<sup>™</sup> design methodology. The device has an 8-bit internal data path controlled by a Z8 microcontroller and On Screen Display (OSD) logic circuits and Pulse Width Modulators (PWM). On-chip peripherals include two register mapped I/O ports (Ports 2 and 3), interrupt control logic (one software, two external and three internal interrupts) and a standby mode recovery input port (Port 3, P30).

The OSD control circuits support 6 rows x 20 columns of characters. The character color is specified by row. One of the six rows is assigned to show two kinds of colors for bar type displays such as volume control. The OSD is capable of displaying either low resolution (5 x 7 dot pattern) or high resolution (11 x 15 dot pattern) characters.

A 14-bit PWM port provides enough voltage resolution for a voltage synthesizer tuning system. Three 6-bit PWM ports are used for controlling audio signal levels. Three 8bit PWM ports used to vary picture levels. For DTC applications demanding powerful I/O capabilities, the Z90102/3/4 fulfills this with 24 I/O pins dedicated to input and output. These lines are grouped into three ports, and are configurable under software control to provide timing, status signals, parallel I/O and an address/data bus for interfacing to external memory.

There are three basic address spaces available to support this wide range of configurations: Program Memory, Video RAM, and Register File. The Register File is composed of 236 bytes of general-purpose registers, two I/O Port registers, 15 control and status registers and three reserved registers.

To unburden the program from coping with the real-time problems such as counting/timing and data communication, the DTC offers two on-chip counter/timers with a large number of user selectable modes (Figure 1).

**Notes:** All signals with a preceding front slash, "/", are active Low. For example, B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

Figure 1. Functional Block Diagram

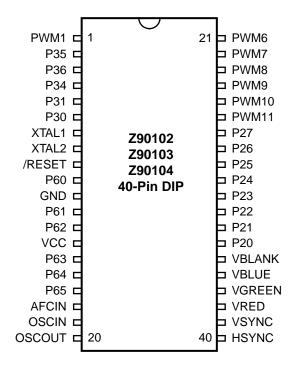

#### **PIN DESCRIPTION**

| 40-Pin     | D-Pin Name Function |                         | Direction |

|------------|---------------------|-------------------------|-----------|

| 1          | PWM1                | Pulse Width Modulator 1 | Output    |

| 2, 3       | P35-36              | Port 3, Pins 5, 6       | Output    |

| 4          | P34                 | Port 3, Pin 4           | Output    |

| 5          | P31                 | Port 3, Pin 1           | Input     |

| 6          | P30                 | Port 3, Pin 0           | Input     |

| 7          | XTAL1               | Crystal Oscillator      | Input     |

| 8          | XTAL2               | Crystal Oscillator      | Output    |

| 9          | /RESET              | System Reset            | Input     |

| 10         | P60                 | Port 6, Pin 0           | Input     |

| 11         | GND                 | Ground                  | Input     |

| 12         | P61                 | Port 6, Pin 1           | Input     |

| 13         | P62                 | Port 6, Pin 2           | Input     |

| 14         | V <sub>CC</sub>     | Power Supply            | Input     |

| 15, 16, 17 | P63-65              | Port 6, Pins 3, 4, 5    | Input     |

| 18         | AFC <sub>IN</sub>   | AFC Voltage Level       | Input     |

| 19         | OSCIN               | Video Dot Clock Osc     | Input     |

| 20         | OSC <sub>OUT</sub>  | Video Dot Clock Osc     | Output    |

| 21         | HSYNC               | Horizontal Sync Input   |           |

| 22         | VSYNC               | Vertical Sync           | Input     |

| 23         | Vred                | Video Red               | Output    |

#### Table 1. 40-Pin Mask-ROM Plastic DIP

#### Table 1. 40-Pin Mask-ROM Plastic DIP

| 40-Pin | Name   | Function                     | Direction |

|--------|--------|------------------------------|-----------|

| 24     | Vgreen | Video Green                  | Output    |

| 25     | Vblue  | Video Blue                   | Output    |

| 26     | Vblank | Video Blank                  | Output    |

| 27-34  | P20-27 | Port 2, Pins 0,1,2,3,4,5,6,7 | In/Output |

| 35     | PWM11  | Pulse Width Modulator 11     | Output    |

| 36     | PWM10  | Pulse Width Modulator 10     | Output    |

| 37     | PWM9   | Pulse Width Modulator 9      | Output    |

| 38     | PWM8   | Pulse Width Modulator 8      | Output    |

| 39     | PWM7   | Pulse Width Modulator 7      | Output    |

| 40     | PWM6   | Pulse Width Modulator 6      | Output    |

|        |        |                              |           |

#### **PIN DESCRIPTION**

**XTAL1, XTAL2.** (time-based input, output, respectively). These pins connect to the internal parallel-resonant clock crystal (4 MHz max) oscillator circuit with two capacitors to GND. XTAL1 is also used as an external clock input.

**SCLK System Clock.** SCLK is the internal system clock. It can be used to clock external glue logic.

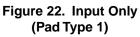

**HSYNC** (input, Schmitt triggered, CMOS level). Horizontal Sync is an input pin that accepts an externally generated Horizontal Sync signal of either negative or positive polarity.

**VSYNC** (input,Schmitt-triggered, CMOS level). Vertical Sync is an input pin that accepts an externally generated Vertical Sync signal of either negative or positive polarity.

**OSCIN, OSCOUT** (Video Oscillator input, output, respectively). Oscillator input and output pins for on-screen display circuits. These pins connect to an inductor and two capacitors to generate the character dot clock (typically around 6 MHz). The dot clock frequency determines the character pixel width and phase synchronized to HSYNC.

**Vblank Video Blank** (output). CMOS output, programmable polarity. Used as a superimpose control port to display characters from video RAM. The signal controls Y signal output of the CRT and turns off the incoming video display while the characters in video RAM are superimposed on the screen. The red, green, and blue outputs drive the three electron guns on the CRT directly, while the blank output turns off the Y signal.

**Vblue Video Blue** (output). CMOS Output of the Blue video signal (B-Y) and is programmable for either polarity.

**Vgreen Video Green** (output). CMOS Output of the Green video signal (G-Y) and is programmable for either polarity.

**Vred Video Red** (output). CMOS Output of the Red video signal (R-Y) and is programmable for either polarity.

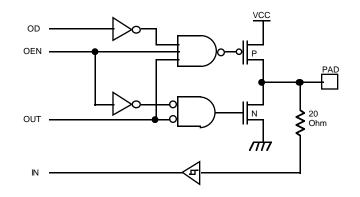

**Port 2** (P27-P20). Port 2 is an 8-bit port, CMOS-compatible, bit programmable for either input or output. Input buffers are Schmitt triggered. Bits programmed as outputs may be globally programmed as either push pull or opendrain (Figure 9).

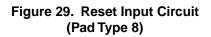

**Port 3** (P30, P31, P34-P36). Port 3, P30 input, is read directly. If appropriately enabled, a negative edge event is latched in IRQ3 to initiate an IRQ3 vectored interrupt. An application could place the device in STOP Mode when P30 goes Low (in the IRQ3 interrupt routine). P30 initiates a STOP Mode recovery when it subsequently goes to a High. Port 3, P31 are read directly. If appropriately enabled, a negative edge event is latched in IRQ2 to initiate an IRQ2 vectored interrupt. P31 High is signified as the TIN signal to Timer1. Port 3, P34 and P35 are general-purpose output lines. Port 3, P36 can be used as a general-purpose output or as an output for TOUT (from Timer1 or Timer2) or SCLK (Figure 10).

**Port 6** (P65-P60). Port 6 is a 6-bit, Schmitt triggered CMOS compatible, input port. The outputs of the AFC comparators internally feed into the Port 6, bit 6 and bit 7 inputs (Figure 11).

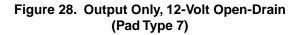

**AFCIN** (Comparator input port, memory mapped). The input signal is supplied to two comparators with VTH1=2/5  $V_{CC}$  and VTH2=3/5  $V_{CC}$  typical threshold voltage. The comparator outputs are internally connected to Port 6, bit 6 and bit 7. AFCIN is typically used to detect AFC voltage level to accommodate digital automatic fine tuning functions (Figure 12).

**Pulse Width Modulator 1** (PWM). PWM1 is typically used as the D/A converter for Voltage Synthesis Tuning systems. It is a push-pull output with 14-bit resolution.

**Pulse Width Modulator 6-8** (PWM). PWM8-PWM6 are Pulse Width Modulators with 6-bit resolution.

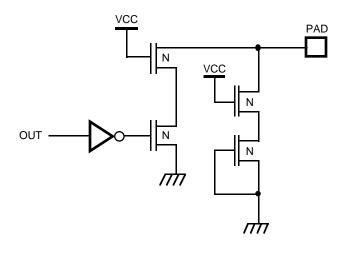

**Pulse Width Modulator 9, 10, 11** (PWM). Pulse Width Modulator circuits with 8-bit resolution. These PWMs are 12 volt, open-drain outputs.

**Pulse Width Modulator 1, 6, 7, 8** (PWM). Can be programmed as general-purpose outputs. PWM 1 is 5  $V_{OH}$  push-pull, and PWMs 6, 7, 8 are 12 volt open-drain outputs.

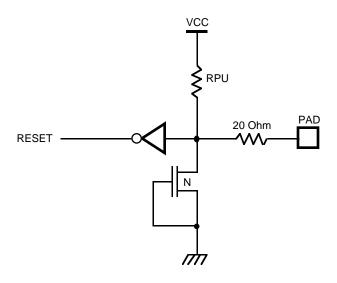

**/RESET** System Reset. Code is executed from memory address 000CH after the /RESET pin is set to a high level. The reset function is also carried out by detecting a  $V_{CC}$  transition state (automatic Power-On Reset) so that the external reset pin can be permanently tied to  $V_{CC}$ . A low level on /RESET forces a restart of the device.

## **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol          | Parameters               | Min  | Мах                  | Units | Notes     |

|-----------------|--------------------------|------|----------------------|-------|-----------|

| V <sub>CC</sub> | Power Supply<br>Voltage* | -0.3 | +7                   | V     |           |

| V <sub>I</sub>  | Input Voltage            | -0.3 | V <sub>CC</sub> +0.3 | V     |           |

| VI              | Input Voltage            | -0.3 | V <sub>CC</sub> +0.3 | V     | 1         |

| Vo              | Output Voltage           | -0.3 | 13.2                 | V     | 2, 3      |

| ОН              | Output Current High      |      | -10                  | mA    | 1 pin     |

| ОН              | Output Current High      |      | -100                 | mA    | All total |

| OL              | Output Current Low       |      | 20                   | mA    | 1 pin     |

| OL              | Output Current Low       |      | 200                  | mA    | All tota  |

| A               | Operating<br>Temperature | †    |                      |       |           |

| STG             | Storage<br>Temperature   | -65  | +150                 | С     |           |

Notes:

1. Port 2 open-drain

2. PWM open-drain outputs

3. Absolute maximum operating voltage 13.2V. Absolute maximum momentary (non-operating) voltage is 16.0V.

\* Voltage on all pins with respect to GND.

† See Ordering Information

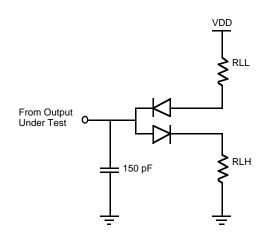

### STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 3).

Figure 3. Test Load Diagram

#### CAPACITANCE

$T_A = 25^{\circ}C$ ;  $V_{CC} = GND = 0V$ ; Freq =1.0 MHz; unmeasured pins to GND.

| Parameter               | Max | Units |

|-------------------------|-----|-------|

| Input capacitance       | 10  | pF    |

| Output capacitance      | 20  | pF    |

| I/O capacitance         | 25  | pF    |

| AFCIN input capacitance | 10  | pF    |

### **DC CHARACTERISTICS**

$T_A = 0^{\circ}C$  to +70°C;  $V_{CC} = +4.5V$  to +5.5V; FOSC = 4 MHz

|                    |                            | T <sub>A</sub> = 0°C te | o +70°C              | Typical |       |                                    |

|--------------------|----------------------------|-------------------------|----------------------|---------|-------|------------------------------------|

| Sym                | Parameter                  | Min                     | Мах                  | @ 25°C  | Units | Conditions                         |

| V <sub>IL</sub>    | Input Voltage Low          | 0                       | 0.2 V <sub>CC</sub>  | 1.48    | V     |                                    |

| V <sub>ILC</sub>   | Input XTAL/Osc In Low      |                         | 0.07 V <sub>CC</sub> | 0.98    | V     | External Clock<br>Generator Driven |

| V <sub>IH</sub>    | Input Voltage High         | 0.7 V <sub>CC</sub>     | V <sub>CC</sub>      | 3.0     | V     |                                    |

| V <sub>IHC</sub>   | Input XTAL/Osc In High     | 0.8 V <sub>CC</sub>     | V <sub>CC</sub>      | 3.2     | V     | External Clock<br>Generator Driven |

| V <sub>HY</sub>    | Schmitt Hysteresis         | 0.1 V <sub>CC</sub>     |                      | 0.8     | V     |                                    |

| V <sub>PU</sub>    | Maximum Pull-Up<br>Voltage |                         | 13.2                 |         | V     | 1, 2                               |

| V <sub>OL</sub>    | Output Voltage Low         |                         | 0.4                  | 0.16    | V     | I <sub>OL</sub> =1.00 mA           |

|                    |                            |                         | 0.4                  | 0.19    | V     | I <sub>OL</sub> =0.75 mA 1         |

| V <sub>00-01</sub> | AFC Level 01 In            |                         | 0.45 V <sub>CC</sub> | 1.9     | V     |                                    |

| V <sub>01-11</sub> | AFC Level 11 In            | 0.5 V <sub>CC</sub>     | 0.75 V <sub>CC</sub> | 3.12    | V     |                                    |

| V <sub>OH</sub>    | Output Voltage High        | V <sub>CC</sub> –0.4    |                      | 4.75    | V     | I <sub>OH</sub> =–0.75 mA          |

| I <sub>IR</sub>    | Reset Input Current        |                         | -80                  | -46     | μΑ    | V <sub>RL</sub> =0 <sub>V</sub>    |

| ΙΙ <sub>L</sub>    | Input Leakage              | -3.0                    | 3.0                  | 0.01    | μΑ    | 0V, V <sub>CC</sub>                |

| I <sub>OL</sub>    | Tristate Leakage           | -3.0                    | 3.0                  | 0.02    | μA    | 0V, V <sub>CC</sub>                |

| I <sub>CC</sub>    | Supply Current             |                         | 20                   | 13.2    | mA    | All inputs at rail &               |

| I <sub>CC1</sub>   |                            |                         | 6                    | 3.2     | mA    | outputs floating                   |

| I <sub>CC2</sub>   |                            |                         | 10                   | 2.0     | μA    |                                    |

Notes:

1. PWM open-drain

2. Recommended operating voltage 12V with maximum positive

tolerance 10%, i.e., 13.2V.

# **AC CHARACTERISTICS**

## **Timing Diagrams**

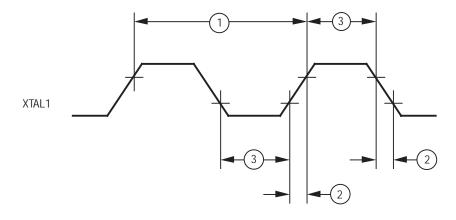

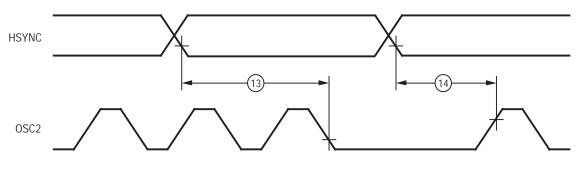

Figure 4. External Clock

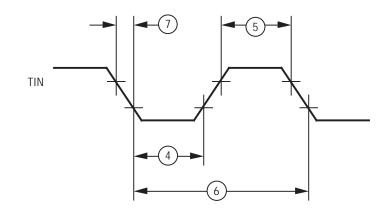

Figure 5. Counter Timer

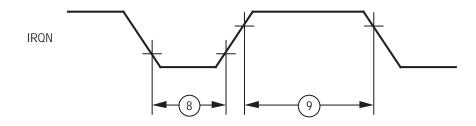

Figure 6. Interrupt Request

## **AC CHARACTERISTICS**

# $T_{A}$ = 0° C to +70° C; $V_{CC}$ = +4.5V to +5.5V; $F_{OSC}$ = 4 MHz

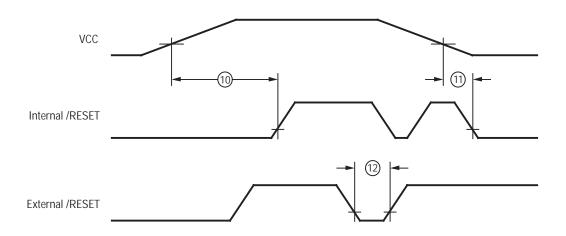

| No     | Symbol      | Parameter                   | Min  | Max  | Unit |

|--------|-------------|-----------------------------|------|------|------|

| 1      | ТрС         | Input Clock Period          | 250  | 1000 | ns   |

| 2      | TrC,TfC     | Clock Input Rise and Fall   |      | 15   | ns   |

| 3      | TwC         | Input Clock Width           | 125  |      | ns   |

| 4      | TwTinL      | Timer Input Low Width       | 70   |      | ns   |

| 5      | TwTinH      | Timer Input High Width      | 3ТрС |      |      |

| 6      | TpTin       | Timer Input Period          | 8TpC |      |      |

| 7      | TrTin,TfTin | Timer Input Rise and Fall   |      | 100  | ns   |

| 8a     | TwIL        | Int Req Input Low           | 70   |      | ns   |

| 8b     | TwIL        |                             | 3ТрС |      |      |

| 9      | TwIH        | Int Request Input High      | 3ТрС |      |      |

| 10     | TdPOR       | Power On Reset Delay        | 25   | 100  | ms   |

| 11     | TdLVIRES    | Low Voltage Detect to       | 200  |      | ns   |

|        |             | Internal RESET<br>Condition |      |      |      |

| 12     | TwRES       | Reset Minimum Width         | 5TpC |      |      |

| 13     | TdHsOI      | HSYNC Start to VOSC<br>Stop | 2TpV | 3TpV |      |

| 14     | TdHsOh      | HSYNC End to VOSC<br>Start  |      | 1TpV |      |

| 15     | TdWDT       | WDT Refresh Time            |      | 12   | ms   |

| Notes: |             |                             |      |      |      |

Notes:

Refer to DC Characteristics for details on switching levels.

#### FUNCTIONAL DESCRIPTION

The Z8 DTCincorporates special functions to enhance the Z8's versatility in consumer, industrial and television control applications.

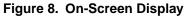

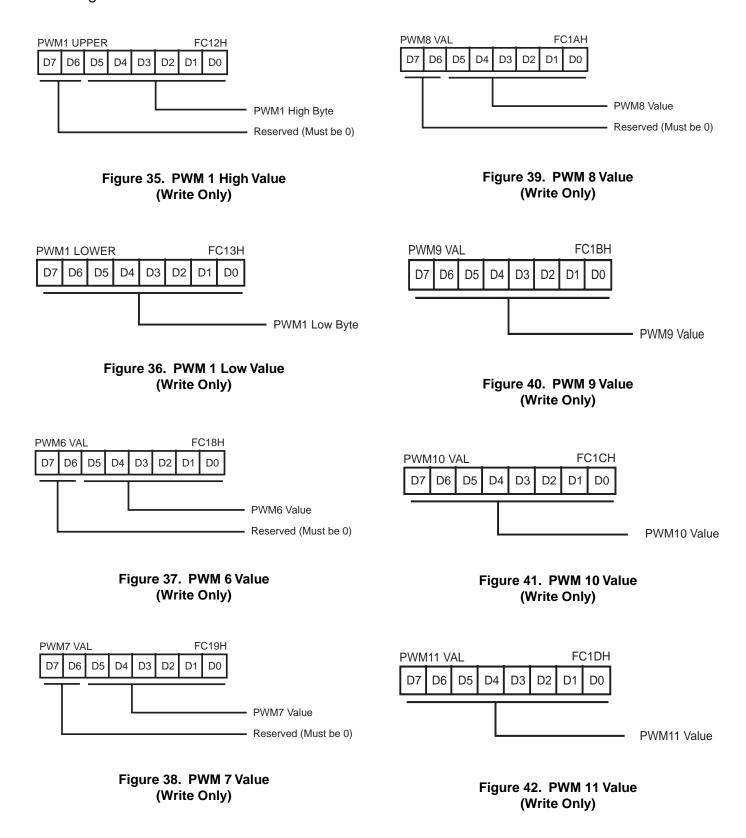

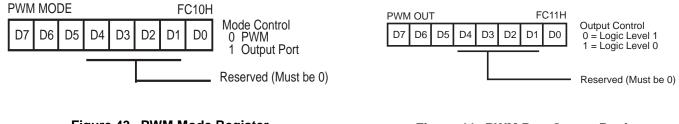

**Pulse Width Modulator** (PWM). The has seven PWM channels (Figure 9). There are three types of PWM circuits: PWM1 (one channel of 14-bit resolution) typically used for Voltage Synthesis Tuning, PWM8-PWM6 (three channels of 6-bit resolution) typically used for audio level control, and PWM9, 10, 11 (three channels of 8-bit resolution) typically used for picture level control. The PWM control registers are mapped into external memory and are accessed through LDE and LDEI instructions.

**PWM1.** It is a push-pull output.

**PWMs 6 through 11**. They have their maximum values (on times) when all 1s are loaded in their PWM Value registers (and minimum value for all 0s). PWM1 has a maximum value for all 0s and minimum value for all 1s.

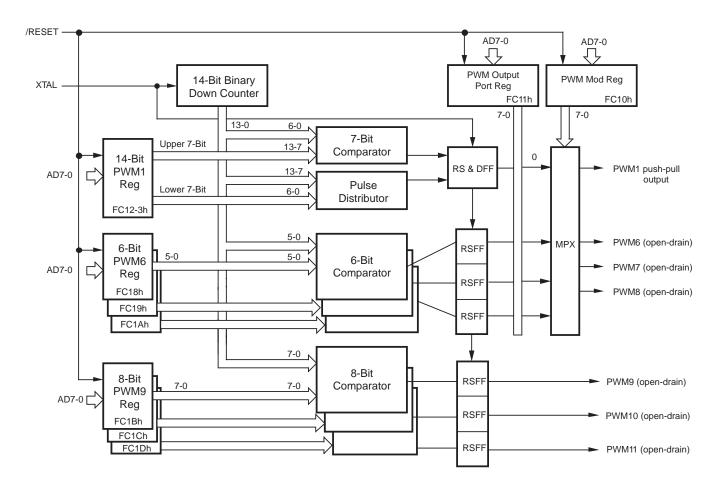

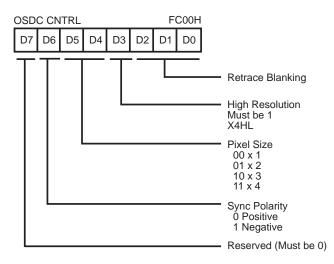

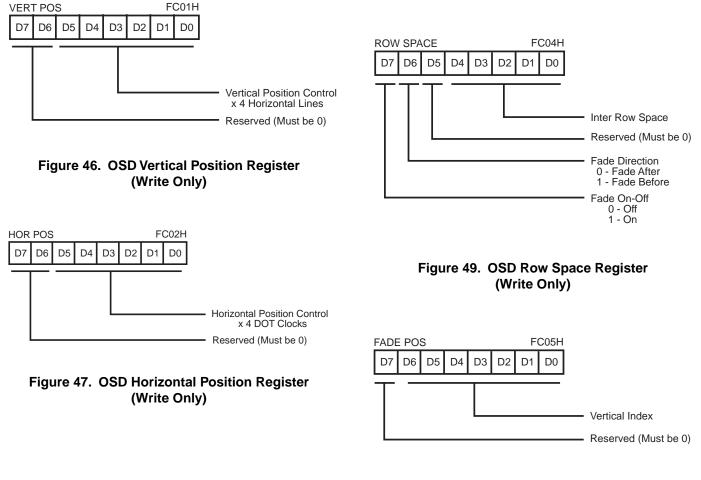

**On-Screen Display (OSD).** The OSD has a capability of displaying 6 rows x 20 columns of 96 kinds of characters for high resolution  $(11 \times 15 \text{ dots})$  patterns (Figures 10 and 11).

Figure 9. Pulse Width Modulator Block Diagram

Zilog

Figure 10. On-Screen Display Block Diagram

### **FUNCTIONAL DESCRIPTION** (Continued)

The OSD features are as follows:

- Character Color: Seven kinds of color are specified on a row basis.

- Character Pixel Size: Four character pixel sizes are selected for a high resolution (1HL, 2HL, 3HL, and 4HL) Horizontal Line (HL).

- Polarity Selections: Can select active low or high for horizontal/vertical sync input and RGB outputs.

- Display Position: Can display 64 vertical positions by 4HL units and 64 horizontal positions by a 4-dot clock.

- Inter Row Spacing: Inter row vertical line spacing is set from 2HL to 17HL.

- Fade In/Out Control: Fade position can be determined in vertical direction.

- Bar Line Type Display: One of the rows is selected to display an analog bar line every half column by setting second color with proper character set.

- Fringe Function: Fringe off/on and the color selected.

- Background Color: Eight kinds of color including black background color.

- ON/OFF Control: Character display, backgrounds are turned on and off.

- Number of Display Characters: 6 rows x 20 columns.

- Character Set: 96 (11 x 15 dots).

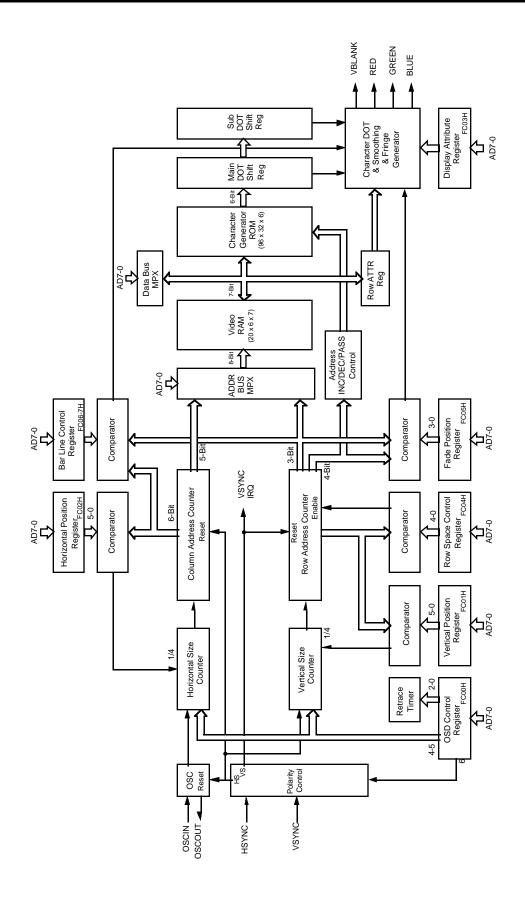

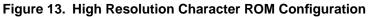

Character Generator ROM. The character generator ROM is organized as 3 KB of six bits. The ROM defines either 11 x 15 dot (high resolution)

Video RAM. The Video RAM is organized as 8-row arrays (21 x 7 bits each, Figure 11). The first location of each row array contains the attribute for that row. Row attributes include programmable character color, row background color and control for background off/on. The next 20 bytes contain row character data. Each character byte contains the ASCII code in order to select one of the 96 displayable

characters. LDE or LDEI instructions are required to access the Video RAM (Figure 11).

| Hex<br>Address |                                |

|----------------|--------------------------------|

| FD00           | Row 1 Attribute (ROW1_ATTR)    |

| FD01           | Row 1 Column 1 Character Data  |

| FD02           | Row 1 Column 2 Through         |

| FD13           | Column 19 Character Dăta       |

| FD14           | Row 1 Column 20 Character Data |

|                |                                |

| FD20           | Row 2 Attribute (ROW2_ATTR)    |

| FD21           | Row 2 Column 1 Character Data  |

| FD22           | Row 2 Column 2 Through         |

| FD33           | Column 19 Character Data       |

| FD34           | Row 2 Column 20 Character Data |

| FD40           |                                |

| FD40<br>FD54   | Row 3 Video RAM Buffer         |

|                |                                |

| FD60           | Row 4 Video RAM Buffer         |

| FD74           |                                |

| FD80           | Row 5 Video RAM Buffer         |

| FD94           |                                |

| FDA0           | Row 6 Video RAM Buffer         |

| FDB4           | KOM O VIGEO KAIVI BUITEL       |

|                | MSB (7 Bits Wide) LSB          |

Figure 11. Video RAM Configuration

| ( 7 Bits Wide)<br>Row 1 Attribute | ROW1<br>FD00H | ROW:<br>FD20H | ROW            | - ROW          | RUV   | ROW            |

|-----------------------------------|---------------|---------------|----------------|----------------|-------|----------------|

|                                   | L             |               |                | TDOUT          | FD80H | f FDA0H        |

| Row 1 Column 1 Character          | FD01H         | FD21H         | FD41H          |                |       | _              |

| Row 1 Column 2 Character          | FD02H         | FD22H         | FD42H          | FD61H          | FD81H | FDA1H          |

| Row 1 Column 3 Character          | FD03H         | FD23H         |                | FD62H          | FD82H |                |

| Row 1 Column 4 Character          | FD04H         | FD24H         | FD43H          | FD63H          | FD83H | FDA2H          |

| Row 1 Column 5 Character          | FD05H         | FD24H         | FD44H          | FD64H          | FD84H | FDA3H          |

| Row 1 Column 6 Character          | FD06H         | FD26H         | FD45H          | FD65H          | FD85H | FDA4H          |

| Row 1 Column 7 Character          | FD07H         | FD27H         | FD46H          | FD66H          | FD86H | FDA5H          |

| Row 1 Column 8 Character          | FD08H         | FD28H         | FD47H<br>FD48H | FD67H          | FD87H | FDA6H          |

| Row 1 Column 9 Character          | FD09H         | FD29H         | FD46H          | FD68H          | FD88H | FDA7H          |

| Row 1 Column 10 Character         | FD0AH         | FD2AH         | FD49H<br>FD4AH | FD69H          | FD89H | FDA8H          |

| Row 1 Column 11 Character         | <b>FD0BH</b>  | FD2BH         | FD4BH          | FD6AH          | FD8AH | FDA9H          |

| Row 1 Column 12 Character         | FD0CH         | FD2CH         | FD4CH          | FD6BH<br>FD6CH | FD8BH | FDAAH<br>FDABH |

| Row 1 Column 13 Character         | FD0DH         | FD2DH         | FD4DH          | FD6DH          | FD8CH | FDAGH          |

| Row 1 Column 14 Character         | <b>FD0EH</b>  | FD2EH         | FD4EH          | FD6EH          | FD8DH | FDADH          |

| Row 1 Column 15 Character         | FD0FH         | FD2FH         | FD4FH          | FD6FH          | FD8EH | FDAEH          |

| Row 1 Column 16 Character         | FD10H         | FD30H         | FD50H          | FD70H          | FD8FH | FDAFH          |

| Row 1 Column 17 Character         | FD11H         | FD31H         | FD51H          | FD71H          | FD90H | FDB0H          |

| Row 1 Column 18 Character         | FD12H         | FD32H         | FD52H          | FD72H          | FD91H | FDB1H          |

| Row 1 Column 19 Character         | FD13H         | FD33H         | FD53H          | FD73H          | FD92H | FDB2H          |

| Row 1 Column 20 Character         | FD14H         | FD34H         | FD54H          | FD74H          | FD93H | FDB3H          |

| MSB                               | L             | -             |                |                | FD94H | FDB4H          |

|                                   | LS            | В             |                |                |       |                |

Figure 12. Video RAM Map (Write/Read Registers)

#### **FUNCTIONAL DESCRIPTION** (Continued)

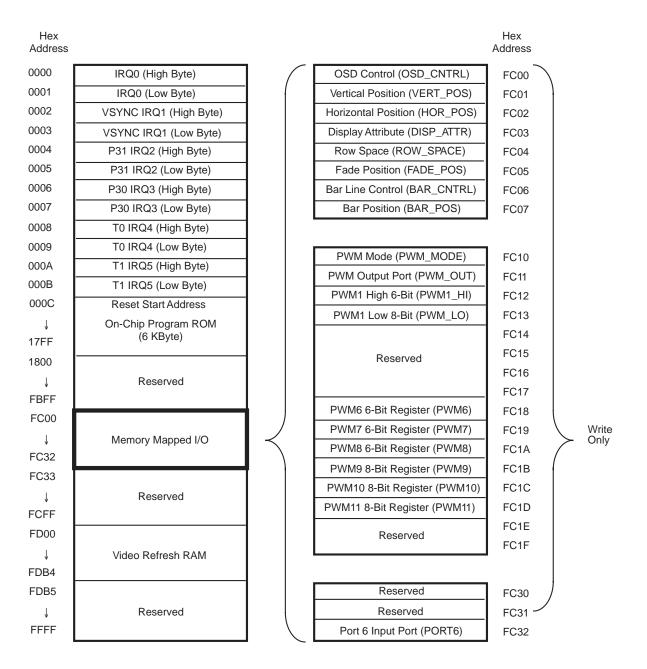

**Program Memory.** The program ROM size is 6 KB (Figure 14). The IRQ vector table is located in the lower address space. The vector address is fetched after the corresponding interrupt and program control is passed to the specified

vector address. IRQ1 vector is fixed to VSYNC interrupt request and occurs at the leading edge of the filtered VSYNC input. Program memory start at address 000CH after reset.

#### FUNCTIONAL DESCRIPTION (Continued)

**Memory Mapped Register.** All control registers and I/O ports (except Port 2 and Port 3) are assigned to program memory space. Address space FC00H contains OSD control registers, PWM output registers and Port 6 I/O registers. Two bits of the decoded AFCIN port are assigned to Port 6 input port. LDE and LDEI instructions are required to transfer data between the Register File and the Memory Mapped Registers.

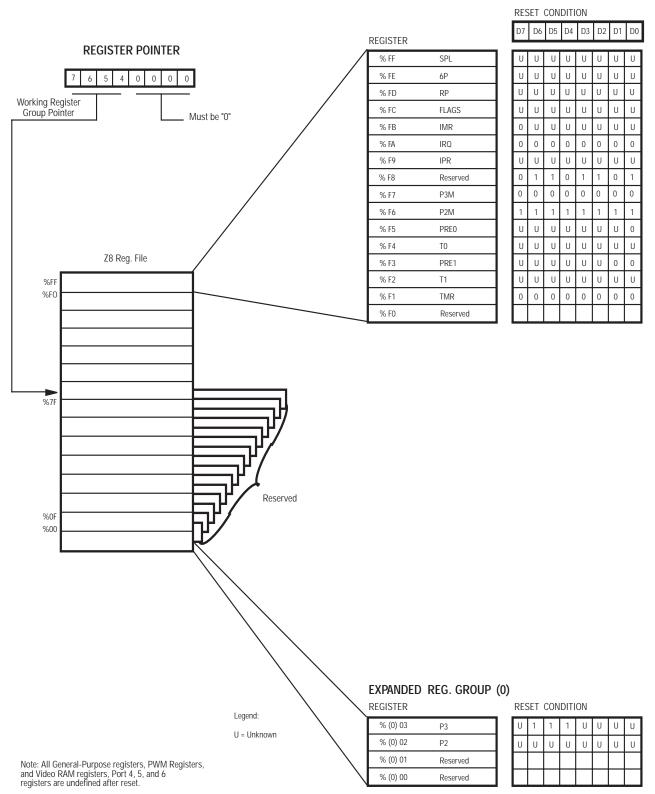

**Register File.** A total of 253 byte registers are implemented in the Z8 core. Address 00H, 01H and FOH are reserved. The register file consists of two I/O Port registers, 236 general-purpose registers and 15 control and status registers (Figure 19). The instructions can access registers directly or indirectly with an 8-bit address field. This also allows short 4-bit register addressing using the Register Pointer. In the 4-bit mode, the register file is divided into sixteen working-register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group (Figure 15).

Figure 15. Register File Configuration

**Note:** Register Bank E0-EF is only accessed through a working register and indirect addressing modes.

Figure 16. Register Pointer

#### Z8 STANDARD CONTROL REGISTERS

#### FUNCTIONAL DESCRIPTION (Continued)

**Stack.** Either the internal register file or the external data memory is used for the stack. An 8-bit Stack Pointer is used for the internal stack that resides within the 236 general-purpose registers.

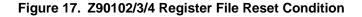

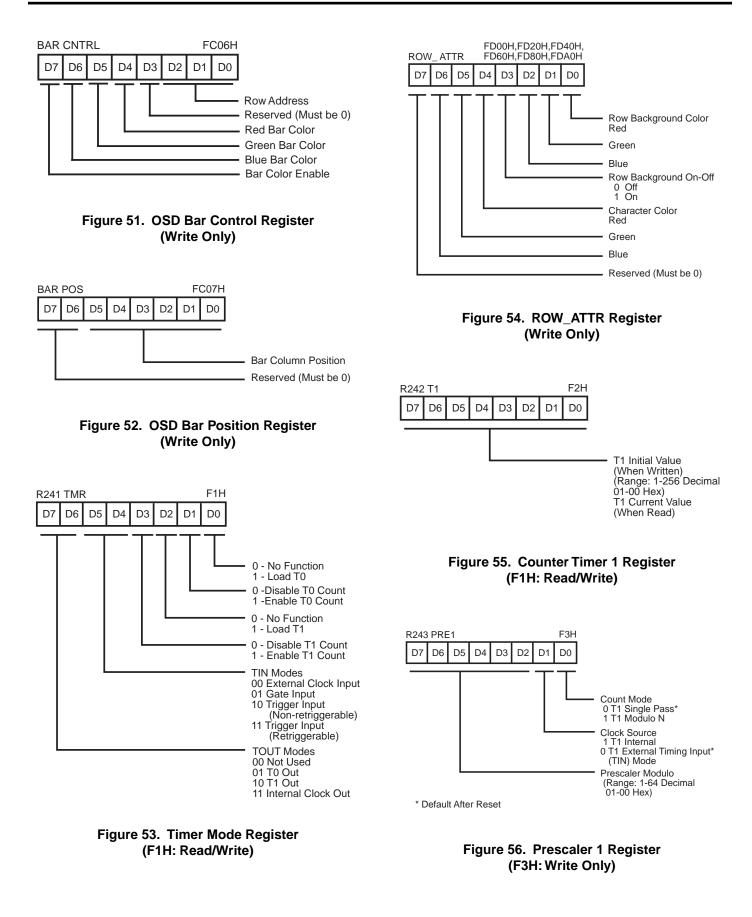

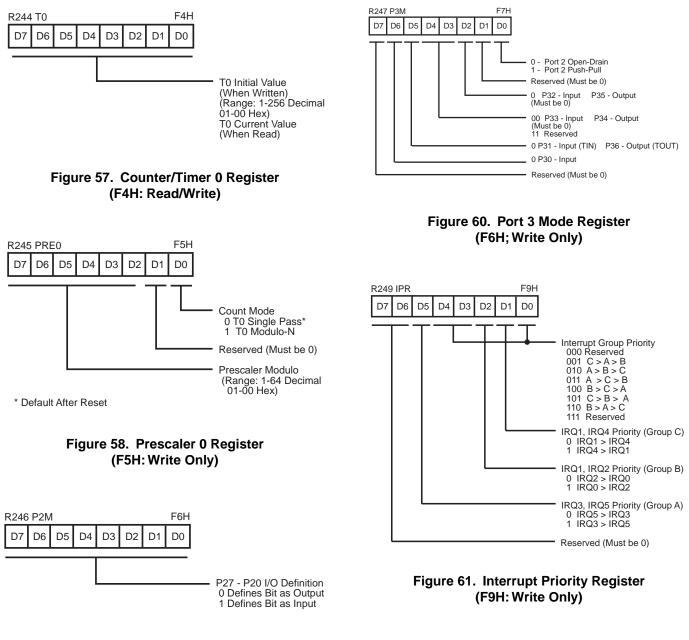

**Counter/Timers.** There are two 8-bit programmable counter/timers (T0-T1), each driven by its own 6-bit programmable prescaler (PRE0 and PRE1). The T1 prescaler can be driven by internal or external clock sources; howev-

er, the T0 prescaler is driven by the internal clock only (Figure 18).

The counter, but not the prescalers, are read at any time without disturbing their value or count mode. The clock source for T1 is user definable and is the internal microprocessor clock (XTAL clock/4), or an external signal input through Port 3, P31. The counter/timers are programmably cascaded by connecting the T0 output to the input of T1.

Figure 18. Counter/Timer Block Diagram

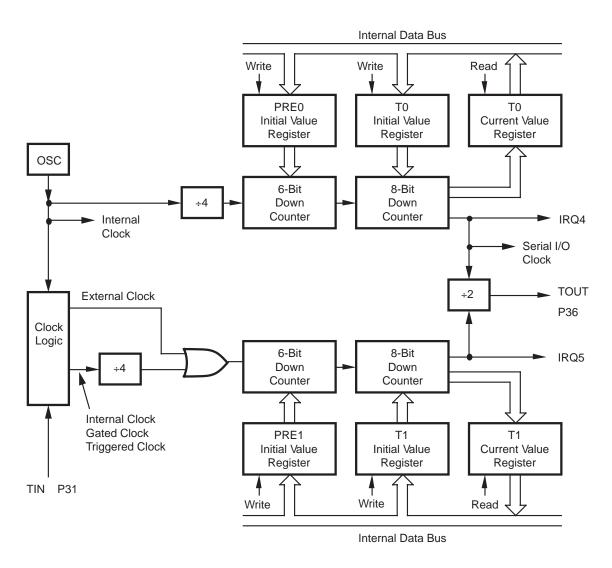

**Interrupts.** The DTC has six different interrupts from six different sources. These interrupts are maskable and prioritized (Figure 19). The six sources are divided as follows:

two sources are claimed by Port 3 (P30, P31), one by VSYNC, two by the counter/timers, and one is software triggered only.

Figure 19. Interrupt Block Diagram

#### FUNCTIONAL DESCRIPTION (Continued)

HALT Mode. The Z90102/3/4 is driven by two internal clocks, TCLK and SCLK. They both oscillate at the crystal frequency. TCLK provides the clock signal for the countertimers and the interrupt block. SCLK provides the clock signal for all other CPU blocks. HALT Mode turns off the internal CPU clock (SCLK), but not the XTAL oscillation. The counter/timers and external interrupts remain active. The device may be recovered by interrupts, either externally or internally generated. An interrupt request may be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after the HALT.

**STOP Mode.** The STOP instruction stops crystal oscillation, thereby stopping both SCLK and TCLK. The device ceases to operate. The STOP Mode can be released by two methods. The first method is to reset the device. A high input condition on Port 3 P30 is the second method. After releasing the STOP Mode by using either one of the two methods, program execution begins at location 000CH. To complete an instruction prior to entering the standby modes, a NOP instruction has to be placed before the HALT or STOP instructions. This is required because of instruction pipelining, i.e.:

| FF NOP  | ; clear the pipeline |

|---------|----------------------|

| 6F STOP | ; enter STOP Mode    |

|         | or                   |

| FF NOP  | ; clear the pipeline |

| 7F HALT | ; enter HALT Mode    |

**Notes:** In STOP Mode, XTAL2 pin has an internal pull-up on it and OSCOUT has an internal pull-down.

**Clock.** The Z90102/3/4 on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, ceramic resonator, or any suitable external clock source (XTAL1 = Input, XTAL2 = Output). The crystal is an AT cut, parallel resonant, 4 MHz max with a series resistance (RS) less than or equal to 100 Ohms.

The crystal source is connected across XTAL1 and XTAL2 using the crystal manufacturer's recommended capacitors (10 pF < CL < 300 pF, where C1=C2=CL) from each pin to device ground (Figure 20).

\* Must be connected to VSS pin and not system ground.

22

DS97TEL1902

**Watch-Dog Timer** (WDT). The Z90102/3/4 is equipped with a permanently enabled Watch-Dog Timer which must be refreshed every 12 ms. Failure to refresh the timer results in a reset of the device. The WDT is permanently enabled and is initially reset upon POR. Every subsequent WDT instruction resets the timer. The Watch-Dog Timer may or may not be enabled during the STOP Mode. The instruction WDT 4F (HEX) enables the timer during HALT.

If the WDH instruction is used, and if the HALT Mode is not released and the Watch-Dog Timer is not retriggered (by the WDT instruction) within 12 ms, a device reset occurs. The WDT instruction affects the Z (Zero) S (Sign), and V (Overflow) flags. WDT does not run during STOP Mode.

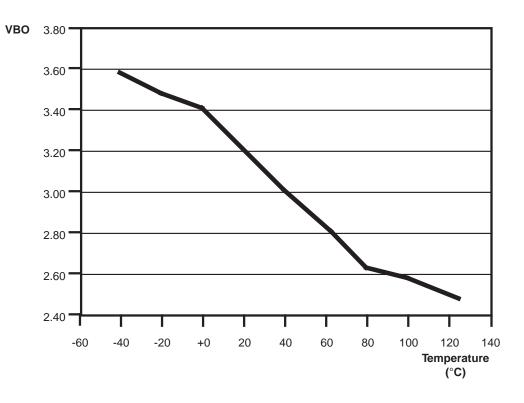

$V_{CC}$  Voltage Sensitive Reset (VSR). Reset is globally driven if  $V_{CC}$  is below the specified voltage (Figure 21).

Figure 21. Voltage Sensitive Reset vs Temperature

#### STANDARD CHARACTER SETS

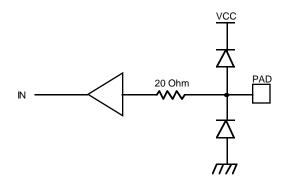

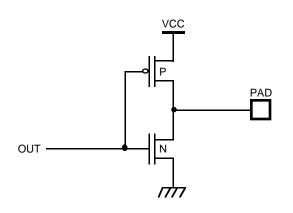

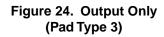

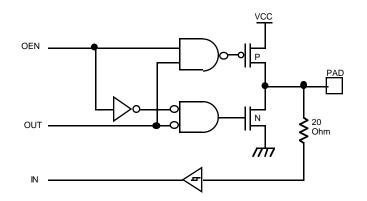

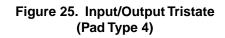

#### Input/Output Circuits

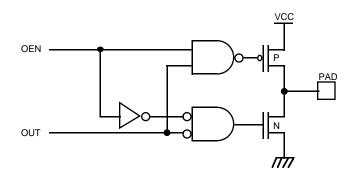

Figure 26. Input/Output, Tristate, Open-Drain

Figure 27. Output Only, Tristate

DS97TEL1902

#### SUMMARY (Continued)

Figure 30. AFC Input Circuit (Pad Type 9)

# Table 2. Mapping of Symbolic Pad Types to PinFunctions

| Pin Name             | Pad Type |  |  |

|----------------------|----------|--|--|

| XTAL1, OSCIN         | 1        |  |  |

| XTAL2, OSCOUT        | *        |  |  |

| /RESET               | 8        |  |  |

| P20-P27              | 5        |  |  |

| P30-P31              | 2        |  |  |

| P34-P36              | 3        |  |  |

| P60-P65              | 2        |  |  |

| AFCIN                | 9        |  |  |

| HSYNC, VSYNC         | 2        |  |  |

| VRED, VBLUE, VGREEN, | 3        |  |  |

| VBLANK               | 3        |  |  |

| PWM1                 | 3        |  |  |

| PWM [6 -11]          | 7        |  |  |

\*High gain start, low gain run amplifier circuit.

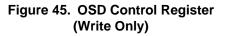

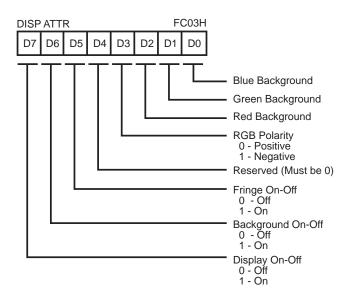

#### DTC CONTROL REGISTER DIAGRAMS Port Registers

0 1 V1 thru V2 11 V2 thru VCC

Figure 34. Port 6 Register (Read Only)

#### DTC CONTROL REGISTER DIAGRAMS PWM Registers

Figure 43. PWM Mode Register (Write Only)

Figure 44. PWM Port Output Register (Write Only)

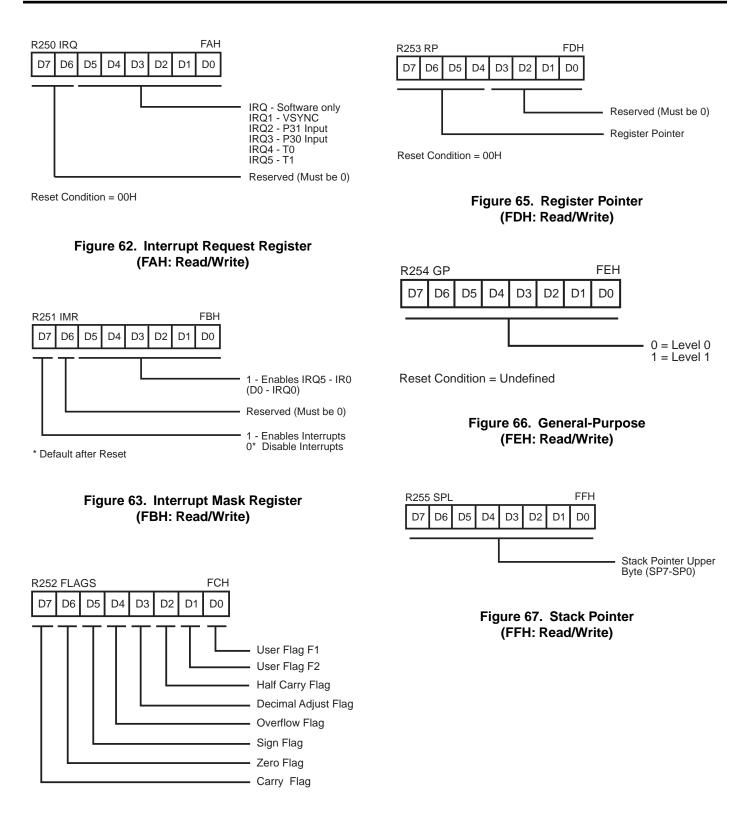

#### **Z8 REGISTER DIAGRAMS**

# Figure 48. OSD Display Attribute Register (Write Only)

Figure 50. OSD Fade Position Register (Write Only)

DS97TEL1902

#### **Z8 REGISTER DIAGRAMS** (Continued)

Figure 59. Port 2 Mode Register (F6H: Write Only)

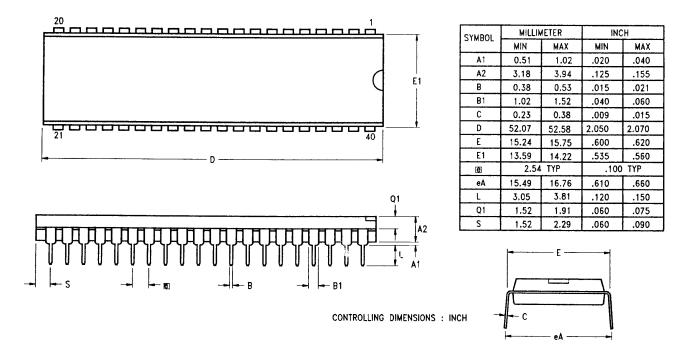

#### **PACKAGE INFORMATION**

Figure 68. 40-Pin DIP Package Diagram

34

# ORDERING INFORMATION

Z90102, Z90103, Z90104

#### 4 MHz 40-pin DIP

#### Z90102/3/404PSC

For fast results, contact your local Zilog sales office for assistance in ordering the part desired.

#### CODE

| Package                   | Speed                |

|---------------------------|----------------------|

| P = Plastic DIP           | 04 = 4 MHz           |

| Temperature               | Environmental        |

| $S = 0^{\circ}C$ to +70°C | C = Plastic Standard |

| Ex<br>Z | ample:<br>890103 | 04 P | S | с | is an 86227, 4 MHz, DIP, 0°C to +70°C, Plastic Standard Flow                            |

|---------|------------------|------|---|---|-----------------------------------------------------------------------------------------|

|         |                  |      |   |   | Environmental Flow<br>Temperature<br>Package<br>Speed<br>Product Number<br>Zilog Prefix |

36