### **SCAN25100**

# 2457.6, 1228.8, and 614.4 Mbps CPRI SerDes with Auto RE Sync and Precision Delay Calibration Measurement

### **General Description**

The SCAN25100 is a 2457.6, 1228.8, and 614.4 Mbps serializer/deseralizer (SerDes) for high-speed bidirectional serial data transmission over FR-4 printed circuit board backplanes, balanced cables, and optical fiber. The SCAN25100 integrates precision delay calibration measurement (DCM) circuitry that measures link delay components to better than  $\pm$  800 ps accuracy.

The SCAN25100 features independent transmit and receive PLLs, on-chip oscillator, and intelligent clock management circuitry to automatically perform remote radio head synchronization and reduce the cost and complexity of external clock networks.

The SCAN25100 is programmable though an MDIO interface as well as through pins, featuring configurable transmitter deemphasis, receiver equalization, speed rate selection, internal pattern generation/verification, and loop back modes. In addition to at-speed BIST, the SCAN25100 includes IEEE 1149.1 and 1149.6 testability.

Note: For a full datasheet of the SCAN25100 please contact your local National Semiconductor representitive.

#### **Features**

- Exceeds LV and HV CPRI voltage and jitter requirements

- 2457.6, 1228.8, and 614.4 Mbps operation

- Integrated delay calibration measurement (DCM) directly measures T14 and Toffset delays to ≤ ± 800 ps

- DCM also measures chip and other delays to ≤ ± 1200 ps accuracy

- Deterministic chip latency

- Automatic receiver lock and RE synchronization without reference clock or external crystal

- Independent transmit and receive PLLs for seamless RE synchronization

- Low noise recovered clock output

- Requires no jitter cleaning in single-hop applications

- >8 kV ESD on the CML IO, >7 kV on all other pins, >2 kV CDM

- Hot plug protection

- LOS, LOF, 8b/10b line code violation, comma, and receiver PLL lock reporting

- Programmable hyperframe length and start of hyperframe character

- Programmable transmit de-emphasis and receive equalization with on-chip termination

- Advanced testability features

- IEEE 1149.1 and 1149.6

- At-speed BIST pattern generator/verifier

- Multiple loopback modes

- 1.8V or 3.3V compatible parallel bus interface

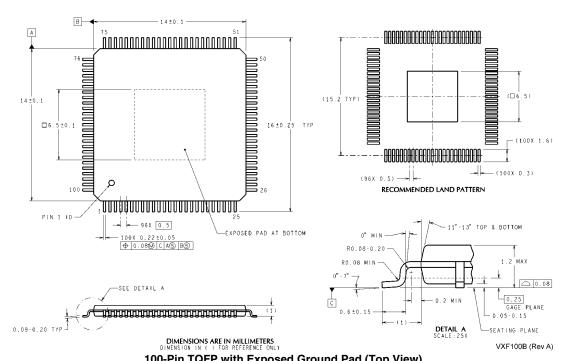

- 100-pin TQFP package with exposed dap

- Industrial –40 to +85° C temperature range

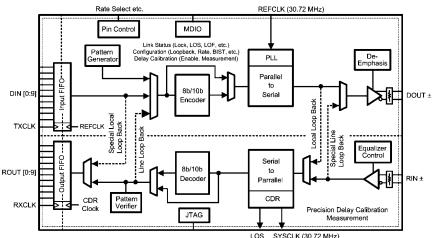

### **Block Diagram**

20183442

2

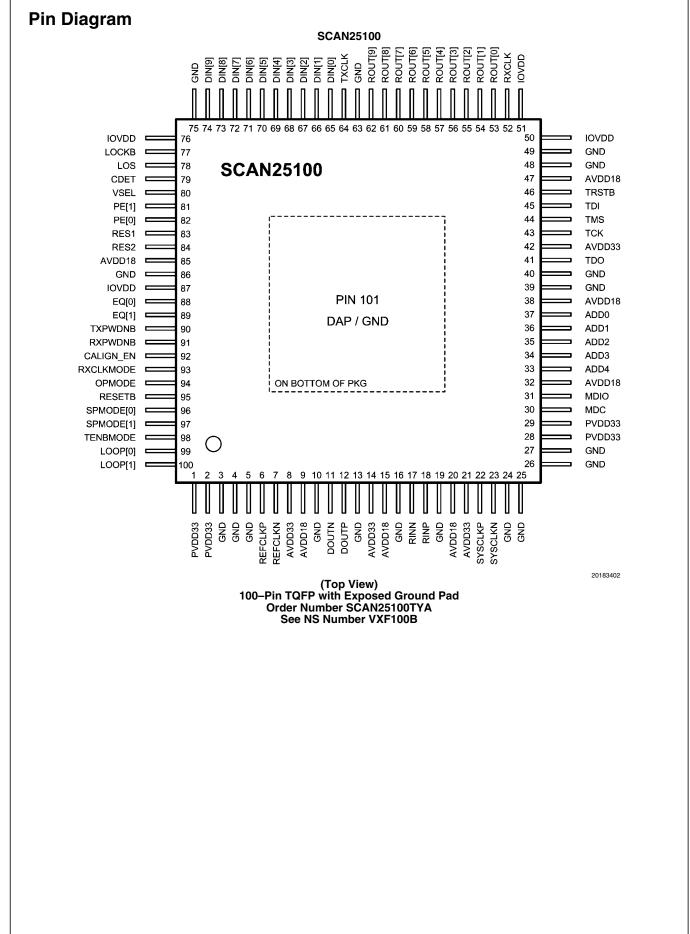

## **Pin Descriptions**

| Pin #    | Pin Name     | I/O, Type               | Description                                                                                    |

|----------|--------------|-------------------------|------------------------------------------------------------------------------------------------|

| HIGH SPE | ED DIFFERENT | TIAL I/O                |                                                                                                |

| 12       | DOUTP        | O, CML                  | Inverting and non-inverting high speed CML differential outputs of the serializer. On          |

| 11       | DOUTN        |                         | chip termination resistors connect from DO+ and DO- to an internal reference                   |

| 18       | RINP         | I, CML                  | Inverting and non-inverting high speed differential inputs of the deseralizer. On-chip         |

| 17       | RINN         | ,,                      | termination resistors connect from RI+ and RI- to an internal reference. On-chip               |

| • •      |              |                         | termination resistors are configured for AC-coupled applications.                              |

| DADALLE  | L DATA BUS   |                         | Tommation redictors are comigated for the coupled applications.                                |

|          | 1            | 1 1 1 1 7 7 7 1 1 0 1 1 | I <del>-</del>                                                                                 |

| 65       | DIN [0]      | I, LVTTL or 1.8V        | Transmit data word.                                                                            |

| 66       | DIN [1]      | LVCMOS Internal         |                                                                                                |

| 67       | DIN [2]      | pull down               | In 10-bit mode, the 10-bit code-group at DIN [0-9] is serialized with the internal 8b/         |

| 68       | DIN [3]      |                         | 10b encoder disabled. Bit 9 is the msb.                                                        |

| 69       | DIN [4]      |                         |                                                                                                |

| 70       | DIN [5]      |                         | The 8B/10B specification is defined in IEEE 802.3-2000 section 36.2.2                          |

| 71       | DIN [6]      |                         |                                                                                                |

| 72       | DIN [7]      |                         |                                                                                                |

| 73       | DIN [8]      |                         |                                                                                                |

| 74       | DIN [9]      |                         |                                                                                                |

| 53       | ROUT [0]     | O, LVTTL or 1.8V        | Deserialized receive data word.                                                                |

| 54       | ROUT [1]     | LVCMOS Internal         |                                                                                                |

| 55       | ROUT [2]     | pull down               | In 10-bit mode, ROUT [0-9] is the deserialized received data word in 10-bit code group         |

| 56       | ROUT [3]     | · '                     | Bit 9 is the msb.                                                                              |

| 57       | ROUT [4]     |                         | The 8B/10B specification is defined in IEEE 802.3-2000 section 36.2.2                          |

| 58       | ROUT [5]     |                         |                                                                                                |

| 59       | ROUT [6]     |                         |                                                                                                |

| 60       | ROUT [7]     |                         |                                                                                                |

| 61       | ROUT [8]     |                         |                                                                                                |

| 62       | ROUT [9]     |                         |                                                                                                |

| CLOCK SI |              |                         |                                                                                                |

|          |              | L LVDC or               | Investigation and non-investigated differential angularing reference plant. A law litter plant |

| 6<br>7   | REFCLKN      | I, LVDS or              | Inverting and non-inverting differential serializer reference clock. A low jitter clock        |

|          | REFCLKN      | LVPECL                  | source should be connected to REFCLKP & REFCLKN.                                               |

| 64       | TXCLK        | I, LVTTL or 1.8V        | Transmit clock. TXCLK must be synchronous to REFCLK to avoid FIFO under/                       |

|          |              | LVCMOS Internal         | overflow though it may differ in phase.                                                        |

|          |              | pull down               |                                                                                                |

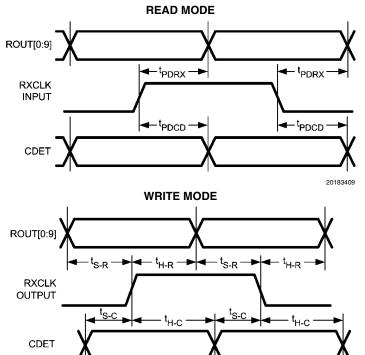

| 52       | RXCLK        | I/O, LVTTL or 1.8V      | Write mode: RXCLK is a recovered clock output pin.                                             |

|          |              | LVCMOS                  |                                                                                                |

|          |              |                         | Read mode: RXCLK is an input pin. ROUT [9:0] are latched out on RXCLK rising and               |

|          |              |                         | falling edges. RXCLK must be synchronous to the incoming serial data to avoid FIFC             |

|          |              |                         | over/underflow, though it may differ in phase. See RXCLKMODE pin description for               |

|          |              |                         | more details.                                                                                  |

| 22       | SYSCLKP      | O, LVDS                 | 30.72 MHz output clock. (OPMODE must be low.)                                                  |

| 23       | SYSCLKN      | 1                       | , , , , , , , , , , , , , , , , , , , ,                                                        |

| LINE STA |              | .1                      | ı                                                                                              |

| 78       | LOS          | O, LVTTL or 1.8V        | Receiver CPRI loss of signal (LOS) status (8-bit mode only).                                   |

| 70       | 1203         | LVCMOS                  | Theodiver Of the loss of signal (LOS) status (o-bit mode only).                                |

|          |              | LVCIVIOS                | O signal detected (new CDD) standard\                                                          |

|          |              |                         | 0 = signal detected (per CPRI standard)                                                        |

|          |              |                         | 1 = signal lost (per CPRI standard)                                                            |

|          |              |                         |                                                                                                |

|          |              |                         | See "LOS Detection" under "Functional Description" for more details.                           |

| 77       | LOCKB        | O, LVTTL or 1.8V        | Receiver PLL lock status                                                                       |

| • •      | 1            | LVCMOS                  | 0 = Receiver PLL locked                                                                        |

|          |              |                         | 1000.101.1 == 100.100                                                                          |

| Pin #   | Pin Name  | I/O, Type        |                                                                                          |                                       | Description                                            |  |  |  |  |

|---------|-----------|------------------|------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|--|--|--|--|

| 79      | CDET      | O, LVTTL or 1.8V | Comma Dete                                                                               | ct.                                   |                                                        |  |  |  |  |

|         |           | LVCMOS           | 0 = no comma yet detected in the incoming serial stream or receiver PLL no               |                                       |                                                        |  |  |  |  |

|         |           |                  | 1 = the receive                                                                          | er PLL is locked                      | and a positive or negative comma bit sequence detected |  |  |  |  |

|         |           |                  | in the incoming bit stream. The serial to parallel converter is aligned to the proper 10 |                                       |                                                        |  |  |  |  |

|         |           |                  | bit word boun                                                                            | idary when com                        | ma alignment is enabled (CALIGN_EN = 1).               |  |  |  |  |

| CONTROL | PINS      |                  | *                                                                                        |                                       |                                                        |  |  |  |  |

| 82      | PE [0]    | I, LVTTL or 1.8V | Transmitter de-emphasis configuration.                                                   |                                       |                                                        |  |  |  |  |

| 81      | PE [1]    | LVCMOS Internal  | Pulling both pins low enables MDIO control, default is no de-emphasis.                   |                                       |                                                        |  |  |  |  |

|         |           | pull down        | PE1                                                                                      | PE0                                   |                                                        |  |  |  |  |

|         |           |                  | 0                                                                                        | 0                                     | No de-emphasis                                         |  |  |  |  |

|         |           |                  | 0                                                                                        | 1                                     | Low de-emphasis                                        |  |  |  |  |

|         |           |                  | 1                                                                                        | 0                                     | Medium de-emphasis                                     |  |  |  |  |

|         |           |                  | 1                                                                                        | 1                                     | Maximum de-emphasis                                    |  |  |  |  |

| 88      | EQ [0]    | I, LVTTL or 1.8V | Receive input                                                                            | t equalization co                     | onfiguration.                                          |  |  |  |  |

| 89      | EQ [1]    | LVCMOS Internal  | Pulling both p                                                                           | oins low enables                      | MDIO control, default is no receive equalization.      |  |  |  |  |

|         |           | pull down        | EQ1                                                                                      | EQ0                                   |                                                        |  |  |  |  |

|         |           |                  | 0                                                                                        | 0                                     | No receive equalization                                |  |  |  |  |

|         |           |                  | 0                                                                                        | 1                                     | Low receive equalization                               |  |  |  |  |

|         |           |                  | 1                                                                                        | 0                                     | Medium receive equalization                            |  |  |  |  |

|         |           |                  | 1                                                                                        | 1                                     | Maximum receive equalization                           |  |  |  |  |

| 90      | TXPWDNB   | I, LVTTL or 1.8V | Power down control signals.                                                              |                                       |                                                        |  |  |  |  |

| 91      | RXPWDNB   | LVCMOS Internal  | =                                                                                        |                                       |                                                        |  |  |  |  |

|         |           | pull down        | 0 = Transmitter is powered down and DOUT± pins are high impedance.                       |                                       |                                                        |  |  |  |  |

|         |           |                  | 1 = Transmitt                                                                            | er is powered up                      | 0.                                                     |  |  |  |  |

|         |           |                  |                                                                                          | is nowered dow                        | n and ROUT [9:0] as well as LOS, LOCKB, CDET,          |  |  |  |  |

|         |           |                  |                                                                                          | SYSCLK are hig                        |                                                        |  |  |  |  |

|         |           |                  |                                                                                          | is powered up.                        | ·····                                                  |  |  |  |  |

| 92      | CALIGN_EN | I, LVTTL or 1.8V | Comma align                                                                              |                                       |                                                        |  |  |  |  |

|         |           | LVCMOS Internal  | _                                                                                        | lignment circuitr                     | y disabled.                                            |  |  |  |  |

|         |           | pull down        |                                                                                          | •                                     | nent circuitry enabled. Receiver aligns 10-bit data to |  |  |  |  |

|         |           |                  | incoming con                                                                             | nma character a                       | nd flags comma detect through CDET pin.                |  |  |  |  |

| 93      | RXCLKMODE | I, LVTTL or 1.8V |                                                                                          | overed clock mo                       | <del></del>                                            |  |  |  |  |

|         |           |                  |                                                                                          | •                                     | s a recovered clock output.                            |  |  |  |  |

|         |           | pull down        | (RXCLK = ou                                                                              |                                       | s the ROUT [9:0] bus read input strobe.                |  |  |  |  |

|         |           |                  | (RXCLK = inp                                                                             | · · · · · · · · · · · · · · · · · · · | s the NOOT [9:0] bus read input strobe.                |  |  |  |  |

| 80      | VSEL      | I, LVTTL or 1.8V | <u> </u>                                                                                 |                                       | data and control pins are 3.3V LVTTL or 1.8V LVCMOS.   |  |  |  |  |

|         |           | LVCMOS Internal  |                                                                                          | •                                     | to ground and power IOVDD at 1.8 V.                    |  |  |  |  |

|         |           | pull down        |                                                                                          |                                       | IOVDD supply and power IOVDD at 3.3 V.                 |  |  |  |  |

| 94      | OPMODE    | I, LVTTL or 1.8V | Selects SerD                                                                             | es mode.                              |                                                        |  |  |  |  |

|         |           | LVCMOS Internal  |                                                                                          |                                       |                                                        |  |  |  |  |

|         |           | pull down        | 0 = Base stat                                                                            |                                       |                                                        |  |  |  |  |

|         |           |                  | 1 = Reserved                                                                             | I for future use                      |                                                        |  |  |  |  |

| 95      | RESETB    | I, LVTTL or 1.8V | Hardware Se                                                                              | rDes reset. Res                       | ets PLLs and MDIO registers.                           |  |  |  |  |

|         |           | LVCMOS Internal  | l                                                                                        |                                       |                                                        |  |  |  |  |

|         |           | pull down        |                                                                                          | SerDes reset                          |                                                        |  |  |  |  |

|         |           | 1                | 1 = Normal o                                                                             | peration                              |                                                        |  |  |  |  |

| Pin # Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| Part   |            |  |  |  |  |  |

| Pull down   SPMODE [1]   SPMODE [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |  |  |  |  |  |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |

| Section   Page   Pag |            |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |

| TENBMODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |  |  |  |  |  |

| LVCMOS, Internal pull down   Dull down   Dull down   Selects 8-bit mode. Enables the internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Duling policies   Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder   Duling policies   Duli |            |  |  |  |  |  |

| Pull down   0 = Selects 8-bit mode. Enables the internal 8b/10b encoder and decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>)</b>   |  |  |  |  |  |

| 1 = Selects 10-bit mode. Bypasses internal 8b/10b encoder and decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |  |  |  |  |  |

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |  |  |  |  |  |

| LOOP [1]   LVCMOS, Internal pull down   Pulling both pins low enables MDIO control.   Note: During Special line (remote) loop back mode, output de-emphasis of disabled.   LOOP [1]   LOOP [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u> </u>   |  |  |  |  |  |

| D   D   Normal mode—no loop back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | control is |  |  |  |  |  |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |  |  |  |  |  |

| 1   1   Special line (remote) loop back mode   MDC/MDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |  |  |  |  |

| MDC/MDIO   3.3V LVTTL   Internal pull up on ADDR pins   ADDR pins   ADDR pins   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible.   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible.   Protocol per IEEE 802.2ae-202 MDC/MDIO Clause 45. These pins are 3 compatible.   Protocol per IEEE 802.2ae-202 MDC/MDIO Clause 45. These pins are 3 c |            |  |  |  |  |  |

| 30   MDC   3.3V LVTTL   Internal pull up on ADDR pins   Protocol per IEEE 802.2ae-2002 MDC/MDIO Clause 45. These pins are 3 compatible, not 1.2V signal compatible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | de et      |  |  |  |  |  |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |  |  |  |  |  |

| 36 ADD1 35 ADD2 34 ADD3 33 ADD4  IEEE 1149.1 (JTAG)  45 TDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3V LVTTL |  |  |  |  |  |

| 35 ADD2 34 ADD3 33 ADD4  IEEE 1149.1 (JTAG)  45 TDI 3.3V LVTTL Internal pull up on TDI, TMS, and TRSTB 46 TRSTB  RESERVED PINS  83 RES1 I Reserved. 84 RES2 Tie with 5 KΩ resistor to ground.  POWER  9, 15, 20, AVDD18 I, Power 1.8V analog supply. 32, 38, 47,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |  |

| 34   ADD3   33   ADD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |  |  |  |  |  |

| State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |  |  |  |  |  |

| IEEE 1149.1 (JTAG)   3.3V LVTTL   JTAG test bus for IEEE 1149.1 and 1149.6 support.   Internal pull up on TDI, TMS, and 43 TCK TRSTB   TRSTB   RESERVED PINS   83 RES1 RES2   Tie with 5 KΩ resistor to ground.   POWER   9, 15, 20, 32, 38, 47,   I Power   1.8V analog supply.   1.8V ana |            |  |  |  |  |  |

| 45   TDI   3.3V LVTTL   Internal pull up on   TDI, TMS, and   43   TCK   TRSTB   TR |            |  |  |  |  |  |

| 41       TDO       Internal pull up on TDI, TMS, and TRSTB         44       TMS       TRSTB         43       TCK       TRSTB         RESERVED PINS         83       RES1       I         84       RES2       Tie with 5 KΩ resistor to ground.         POWER         9, 15, 20, 38, 47,       AVDD18       I, Power         1.8V analog supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |  |  |  |  |  |

| 44 TMS TDI, TMS, and TRSTB 46 TRSTB  RESERVED PINS  83 RES1 I Reserved. Tie with 5 KΩ resistor to ground.  POWER  9, 15, 20, AVDD18 I, Power 1.8V analog supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |  |

| 43 TCK TRSTB 46 TRSTB  RESERVED PINS  83 RES1 I Reserved. 84 RES2 Tie with 5 KΩ resistor to ground.  POWER  9, 15, 20, AVDD18 I, Power 1.8V analog supply.  32, 38, 47,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |  |  |  |  |