# Servo signal processor for CD use BU9314KS

The BU9314KS is a servo signal processor for CD players that incorporates a double-speed, no-adjustment PLL, program servo, and signal processing block, and D/A converter on one chip. It operates off a low power supply voltage, and has low power consumption.

### Applications

Portable CD players, radio cassette players, and minicomponent systems.

### Features

- PLL on chip. Bit clock extraction possible with just a few external components. EFM data modulation is possible.

- 2) Frame synchronizing signal detection and protection.

- Servo filters for focus, tracking, and sled are on chip.

Characteristics can be controlled using commands from the controller.

- 4) Sub-code serial output pin provided.

- 5) Output pins for both P-code and Q-code.

- 6) CLV sequencer automatically determines the CLV mode.

- 7) Track jump sequencer on chip. Possible to jump any number of tracks.

- 8) De-interleave function, and 2-level error detection, correction and flag processing for C1 and C2.

- 9) The signal to the D/A converter is output by the MSB first 2'SCOMP serial out, and offset circuit ON and OFF can be controlled for CD-ROM compatibility.

- 10) 16k bits of on-chip SRAM absorb ±4 frames of jitter.

- 11) Double-speed playback is possible.

- 12) Built-in 8Fs digital filter and 16-bit D/A converter.

- 13) Built-in digital de-emphasis function.

### ■Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol | Limits           | Unit |

|-----------------------|--------|------------------|------|

| Power supply voltage  | Vcc    | 7                | V    |

| Power dissipation     | Pd     | 400*             | mW   |

| Operating temperature | Topr   | <b>−25~+70</b>   | ొ    |

| Storage temperature   | Tstg   | <b>−55∼</b> +125 | °C   |

## ■Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply voltage | Vcc    | 3.0  | _    | 5.5  | V    |

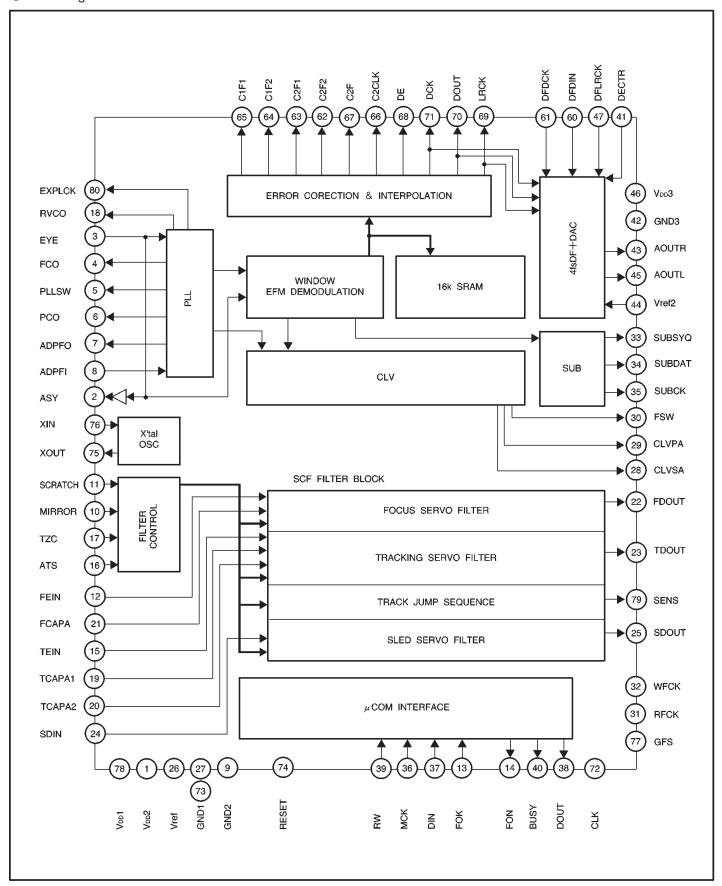

## Block diagram

# Pin descriptions

| Pin No. | Pin name          | Analog / digital | 1/0 | Function                                                           | I / O circuit |

|---------|-------------------|------------------|-----|--------------------------------------------------------------------|---------------|

| 1       | V <sub>DD</sub> 2 | _                | _   | PLL and servo filter block power supply                            | _             |

| 2       | ASY               | Digital          | 0   | EFM signal slice level control output                              | 5             |

| 3       | EYE               | Digital          | ı   | EFM signal input pin from the RF amplifier                         | 4             |

| 4       | FCO               | Analog           | 0   | PLL phase comparison error voltage output                          | 7             |

| 5       | PLLSW             | Digital          | 0   | PLL time constant switch pin                                       | 3             |

| 6       | PCO               | Analog           | 0   | PLL phase comparison error voltage output                          | 7             |

| 7       | ADPFO             | Analog           | 0   | PLL addition amplifier output                                      | 2             |

| 8       | ADPFI             | Analog           | ı   | PLL addition amplifier inversion signal                            | 1             |

| 9       | GND2              | _                | _   | PLL servo filter block ground                                      | _             |

| 10      | MIRROR            | Digital          | ı   | Mirror signal input                                                | 4             |

| 11      | SCRATCH           | Digital          | 1   | Scratch signal input                                               | 4             |

| 12      | FEIN              | Analog           | ı   | Focus error signal input                                           | 1             |

| 13      | FOK               | Digital          | 1   | Focus OK signal input                                              | 4             |

| 14      | FON               | Digital          | 0   | Focus on signal output                                             | 5             |

| 15      | TEIN              | Analog           | I   | Tracking error signal input                                        | 1             |

| 16      | ATS               | Analog           | I   | Anti-shock detector window comparator input                        | 1             |

| 17      | TZC               | Analog           | 1   | PLL VCO free-run resistor                                          | 1             |

| 18      | RVCO              | Analog           | 0   | Tracking/zero cross comparator input                               | 1             |

| 19      | TCAPA1            | Analog           | 1/0 | For connection of switch 1 for tracking servo filter               | 11            |

| 20      | TCAPA2            | Analog           | 1/0 | For connection of switch 2 for tracking servo filter               | 3             |

| 21      | FCAPA             | Analog           | 1/0 | For connection of capacitor for focus servo filter                 | 11            |

| 22      | FDOUT             | Analog           | 0   | Focus drive output                                                 | 1             |

| 23      | TDOUT             | Analog           | 0   | Tracking drive output                                              | 1             |

| 24      | SDIN              | Analog           | I   | Sled amplifier input                                               | 1             |

| 25      | SDOUT             | Analog           | 0   | Sled drive output                                                  | 2             |

| 26      | Vref              | Analog           | 1   | Bias voltage input                                                 | 6             |

| 27      | GND1              | _                | _   | Digital ground                                                     | _             |

| 28      | CLVSA             | Analog           | 0   | Spindle motor drive speed control output (analog)                  | 1             |

| 29      | CLVPA             | Analog           | 0   | Spindle motor drive rough control or phase control output (analog) | 1             |

| 30      | FSW               | Digital          | 0   | Spindle motor output filter time constant switching output         | 3             |

| 31      | RFCK              | Digital          | 0   | Read frame clock output (Xtal 7.35kHz)                             | 5             |

| 32      | WFCK              | Digital          | 0   | Write frame clock output (7.35kHz when locked to X'tal)            | 5             |

| 33      | SUBSYQ            | Digital          | 0   | Sub-code sync signal S0+S1 output                                  | 5             |

| 34      | SUBDATA           | Digital          | 0   | Sub-code serial output                                             | 5             |

| 35      | SUBCK             | Digital          | ı   | Clock input for sub-code read                                      | 4             |

| Pin No. | Pin name          | Analog / digital | 1/0 | Function                                                                                   | I / O circuit |

|---------|-------------------|------------------|-----|--------------------------------------------------------------------------------------------|---------------|

| 36      | MCK               | Digital          | 1   | Clock for reading serial data from CPU or sub Q-code                                       | 4             |

| 37      | DIN               | Digital          | 1   | Input for serial data from clock                                                           | 4             |

| 38      | DOUT              | Digital          | 0   | Sub Q-code or internal status serial output                                                | 7             |

| 39      | RW                | Digital          | I   | Read/write switch input (outputs data from DOUT when High and inputs data to DIN when Low) | 4             |

| 40      | BUSY              | Digital          | 0   | Busy output ("L" during track jump)                                                        | 5             |

| 41      | DECTR             | Digital          | I   | De-emphasis control (de-emphasis filter on when High)                                      | 4             |

| 42      | GND3              | _                | _   | _                                                                                          | _             |

| 43      | AOUTL             | Analog           | 0   | Lch analog audio output                                                                    | 12            |

| 44      | Vref2             | Analog           | 0   | Reference voltage for D/A converter (connect capacitor between this pin and GND)           | 6             |

| 45      | AOUTR             | Analog           | 0   | Rch analog audio output                                                                    | 12            |

| 46      | V <sub>DD</sub> 3 | _                | _   | _                                                                                          | _             |

| 47      | DFLRCK            | Digital          | 1   | External serial data L/R switching signal input                                            | 4             |

| 48      | N.C.              | _                | _   | _                                                                                          | _             |

| 49      | N.C.              | _                | _   | _                                                                                          | _             |

| 50      | N.C.              | _                | _   | _                                                                                          | _             |

| 51      | N.C.              | _                | _   | _                                                                                          | _             |

| 52      | N.C.              | _                | _   | _                                                                                          | _             |

| 53      | N.C.              | _                | _   | _                                                                                          | _             |

| 54      | N.C.              | _                | _   | _                                                                                          | _             |

| 55      | N.C.              | _                | _   | _                                                                                          | _             |

| 56      | N.C.              | _                | _   | _                                                                                          | _             |

| 57      | N.C.              | _                | _   | _                                                                                          | _             |

| 58      | N.C.              | _                | _   | _                                                                                          | _             |

| 59      | N.C.              | _                | _   | _                                                                                          | _             |

| 60      | DFDIN             | Digital          | - 1 | External serial data input                                                                 | 4             |

| 61      | DFDCK             | Digital          | 1   | Bit clock input for external serial data                                                   | 4             |

| 62      | C2F2              | Digital          | 0   | C22 correction flag output                                                                 | 5             |

| 63      | C2F1              | Digital          | 0   | C21 correction flag output                                                                 | 5             |

| 64      | C1F2              | Digital          | 0   | C12 correction flag output                                                                 | 5             |

| 65      | C1F1              | Digital          | 0   | C11 correction flag output                                                                 | 5             |

| 66      | C2CLK             | Digital          | 0   | Strobe signal (f=176.4kHz)                                                                 | 5             |

| 67      | C2F               | Digital          | 0   | Correction status output                                                                   | 5             |

| 68      | DE                | Digital          | 0   | Strobe signal (f=88.2kHz)                                                                  | 5             |

| 69      | LRCK              | Digital          | 0   | Strobe signal (f=44.1kH)                                                                   | 5             |

| Pin No. | Pin name          | Analog / digital | 1/0 | Function                                                              | I / O circuit |

|---------|-------------------|------------------|-----|-----------------------------------------------------------------------|---------------|

| 70      | DOUTA             | Digital          | 0   | Audio data output (2'SCOMP)                                           | 5             |

| 71      | DOCK              | Digital          | 0   | Bit clock for DOUT (f=2.1168MHz)                                      | 5             |

| 72      | CLK               | Digital          | 0   | Clock output (select from four types using &hE4 command)              | 5             |

| 73      | GND1              | _                | _   | Digital ground                                                        | _             |

| 74      | RESET             | Digital          | 1   | Internal circuit reset (pull up with internal 100k $\Omega$ resistor) | 8             |

| 75      | XOUT              | Digital          | 0   | X'tal oscillation circuit output (f=16.9MHz)                          | 9             |

| 76      | XIN               | Digital          | 1   | X'tal oscillation circuit input (f=16.9MHz)                           | 9             |

| 77      | GFS               | Digital          | 0   | GFS monitor output (select from four types using &hE4 command)        | 5             |

| 78      | V <sub>DD</sub> 1 | _                | _   | Digital power supply                                                  | _             |

| 79      | SENS              | Digital          | 0   | Status output of signal specified by &hE4 command)                    | 5             |

| 80      | EXPLCK            | Digital          | 1/0 | PLL playback clock output or external PLL playback clock input        | 10            |

### Input / output circuits

|    | out / output circuits |    |                 |

|----|-----------------------|----|-----------------|

| 1  | 300Ω 3kΩ              | 2  | 500Ω            |

| 3  |                       | 4  | 300Ω 3kΩ        |

| 5  |                       | 6  |                 |

| 7  |                       | 8  | 300 Ω 3kΩ 100kΩ |

| 9  |                       | 10 | 3kΩ 300Ω        |

| 11 | 100Ω 3kΩ  100Ω 3kΩ    | 12 | 300Ω            |

\*1 MIRROR, SCRATCH, FOK, SUBCK, MCK, DIN, RW, RESET, EXPLCK, EYE, DECTR, DFLRCK, DFDIN, DFDCK

**\*4 PLLSW, TCAPA2, FSW**

≉5 FEIN, TEIN

<sup>\*2</sup> FON, RFCK, WFCK, SUBSYQ, SUBDATA, DOUT, BUSY, XOUT, SENS, GFS, ASY, C1F1, C1F2, C2F1, C2F2, C2CLK, C2F, DE, LRCK, DOCK, CLK \*3 RESET

# Electrical characteristics

Digital system characteristics (unless otherwise noted, Ta = 25°C and  $V_{DD} = 5V$ )

| Parameter                        | Symbol            | Min. | Тур. | Max. | Unit | Conditions            | Applicable pin |

|----------------------------------|-------------------|------|------|------|------|-----------------------|----------------|

| Input high level voltage         | ViH               | 3.5  | _    | _    | V    | _                     | *1             |

| Input low level voltage          | VIL               | _    | _    | 0.3  | V    | _                     | *1             |

| Output high level voltage        | Vон               | 4.0  | _    | Voo  | V    | I <sub>OH</sub> =-1mA | *2             |

| Output low level voltage         | Vol               | 0    | _    | 0.4  | V    | loL=1mA               | *2, 4          |

| Input resistance 1               | V <sub>01</sub>   | 80   | 100  | 120  | kΩ   | Between Vpp1 pin      | *3             |

| Input resistance 2               | V <sub>O2</sub>   | 60   | 75   | 90   | kΩ   | Between BIAS pin      | TZC            |

| Input resistance 3               | Voз               | 180  | 230  | 280  | kΩ   | Between BIAS pin      | ATS            |

| Input resistance 4               | V <sub>04</sub>   | 20   | 25   | 30   | kΩ   | Between BIAS pin      | *5             |

| Input leak current               | lu                | _    | _    | ±5   | μΑ   | VI=0~5.25V            | *1             |

| Output leak current              | ILO               | _    | _    | ±5   | μΑ   | VI=0~5.25V            | *4             |

| V <sub>ref2</sub> output voltage | V <sub>ref2</sub> | _    | 2.5  | _    | V    | _                     | Vref2          |

Analog system characteristics (unless otherwise noted, Ta = 25°C,  $V_{DD} = 5V$ , and  $V_{C}$  reference)

| Parameter                | Symbol            | Min.        | Тур.                   | Max.       | Unit      | Conditions                                   | Setting command    |

|--------------------------|-------------------|-------------|------------------------|------------|-----------|----------------------------------------------|--------------------|

| ⟨Focus servo⟩            |                   |             |                        |            |           |                                              |                    |

| DC voltage gain          | G <sub>FD1</sub>  | 17          | 20                     | 23         | dB        | V <sub>IN</sub> =1Hz, 100mV <sub>P-P</sub>   | &h10XF, 1462       |

| AC voltage gain 1        | GFDF1             | -0.7        | 2.3                    | 5.3        | dB        | V <sub>IN</sub> =1kHz, 100mV <sub>P-P</sub>  | &h10XF, 1462       |

| AC voltage gain 2        | GFDF2             | <b>-5.1</b> | -2.1                   | 0.9        | dB        | V <sub>IN</sub> =300Hz, 100mV <sub>P-P</sub> | &h10XF, 1462       |

| Maximum output voltage   | V <sub>FD1</sub>  | 1.5         | 2.1                    | _          | V         | _                                            | _                  |

| Minimum output voltage   | V <sub>FD2</sub>  | _           | -2.1                   | -1.5       | ٧         | _                                            | _                  |

| Offset voltage           | VFOF              | -350        | 0                      | 350        | mV        | _                                            | &h10XF, 1462       |

| 〈Tracking servo〉         |                   |             |                        |            |           |                                              |                    |

| DC voltage gain          | G <sub>TD1</sub>  | 23          | 26                     | 29         | dB        | V <sub>IN</sub> =1Hz, 20mV <sub>P-P</sub>    | &h10DX, 1159, 1207 |

| AC voltage gain 1        | GTDF1             | -0.5        | 2.5                    | 5.5        | dB        | V <sub>IN</sub> =1kHz, 200mV <sub>P-P</sub>  | &h10DX, 1159, 1207 |

| AC voltage gain 2        | GTDF2             | -4          | -1                     | 2          | dB        | VIN=300Hz, 200mV <sub>P-P</sub>              | &h10DX, 1159, 1207 |

| AC voltage gain 3        | GтDF3             | 28          | 31                     | 34         | dB        | V <sub>IN</sub> =1kHz, 20mV <sub>P-P</sub>   | &h10DX, 1159, 1207 |

| AC voltage gain 4        | GTDF4             | 21.5        | 24.5                   | 27.5       | dB        | V <sub>IN</sub> =300Hz, 20mV <sub>P-P</sub>  | &h10DX, 1159, 1207 |

| Maximum output voltage   | V <sub>TD1</sub>  | 1.5         | 2.1                    | _          | ٧         | _                                            | _                  |

| Minimum output voltage   | V <sub>TD2</sub>  | _           | -2.1                   | -1.5       | V         | _                                            | _                  |

| Offset voltage           | Vtof              | -500        | 0                      | 500        | mV        | _                                            | &h10DX, 1159, 1287 |

| Jump output voltage 1    | V <sub>JP1</sub>  | 1.2         | 1.8                    | _          | V         | _                                            | &h13XF             |

| Jump output voltage 2    | V <sub>JP2</sub>  | _           | -1.9                   | -1.1       | ٧         | _                                            | &h13FX             |

| ATS threshold voltage 1  | V <sub>ATS1</sub> | 10          | 25                     | 40         | mV        | _                                            | _                  |

| ATS threshold voltage 2  | V <sub>ATS2</sub> | -40         | -25                    | 10         | mV        | _                                            | _                  |

| TZC threshold voltage    | Vtzc              | -25         | 0                      | 25         | mV        | _                                            | _                  |

| ⟨Sled servo⟩             |                   |             |                        |            |           |                                              | •                  |

| DC voltage gain          | G <sub>SD1</sub>  | 24          | 27                     | 30         | dB        | V <sub>IN</sub> =100Hz, 20mV <sub>P-P</sub>  | &h124X             |

| Maximum output voltage   | V <sub>SD1</sub>  | 1.4         | 2                      | _          | V         | _                                            | _                  |

| Minimum output voltage   | V <sub>SD2</sub>  | _           | -2.1                   | -1.5       | V         | _                                            | _                  |

| Offset voltage           | Vsof              | -220        | 0                      | 220        | mV        | _                                            | &h124X             |

| Kick output voltage 1    | V <sub>KC1</sub>  | 1.5         | 2.0                    | _          | ٧         | _                                            | &h18XF             |

| Kick output voltage 2    | VKC2              | _           | -1.8                   | -1.3       | V         | _                                            | &h18FX             |

| ⟨Digital filter+D / A    | converter         | ·> (RL=10   | $0$ k $\Omega$ , using | DIN-AUDI   | O filter) |                                              |                    |

| Resolution               | RES               | _           | _                      | 16         | bit       | _                                            | _                  |

| Maximum output amplitude | VMAX              | 1.7         | 1.9                    | _          | V         | Data pattern: 1kHz, 2V <sub>P-P</sub>        | _                  |

| Distortion               | THD               | _           | 0.02                   | 0.3        | %         | Data pattern: 1kHz, 2V <sub>P-P</sub>        | _                  |

| Crosstalk                | СТ                | _           | -90                    | <b>—70</b> | dB        | Data pattern: 1kHz, 2V <sub>P-P</sub>        | _                  |

| S / N ratio              | \$/N              | _           | -90                    | <b>-70</b> | dB        | _                                            | _                  |

ONot designed for radiation resistance.

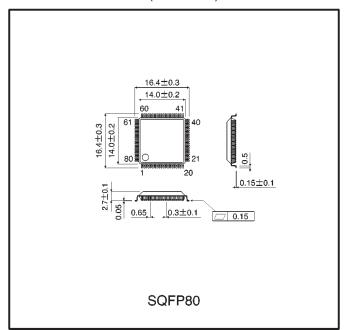

# External dimensions (Units: mm)