# Servo signal processor for CD BU9312AKS

The BU9312AKS is a CD servo signal processing IC that contains a speed doubling unadjusted PLL, program servo, and signal processor, and that delivers low voltage operation and low power consumption. This IC is ideal for miniaturized, low-power-consumption applications.

#### Applications

Portable CD players, portable stereos and mini component stereo systems

#### Features

- Internal PLL circuit, allowing EFM data demodulation and bit clock sampling with minimum attached components.

- 2) Frame synch signal detection and protection.

- Internal focus, tracking and thread servo filters.

Characteristics can be controlled with commands from the controller.

- 4) Subcode serial output pin.

- 5) Output pins for P code and Q code.

- Internal CLV sequencer that automatically sets the CLV mode.

- 7) Internal track jump sequencer that jumps the desired number of tracks.

- Single-chip IC with deinterleaving function and internal C1 / C2 double error detection, correction and flag processor.

- Signals to DAC are output via MSB fast 2'SCOMP serial outputs, enabling control of ON / OFF operation of CD-ROM interpolators.

- 10) 16k bits of internal SRAM, for the storage of up to ± 4 frames of jitters.

- 11) Doubled-speed playback.

ROHM

### ■Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol | Limits                | Unit |  |

|-----------------------|--------|-----------------------|------|--|

| Power supply voltage  | Vcc    | 7                     | V    |  |

| Power dissipation     | Pd     | 400*                  | mW   |  |

| Operating temperature | Topr   | <b>−25~+75</b>        | °C   |  |

| Storage temperature   | Tstg   | -55~ <del>+</del> 125 | °C   |  |

<sup>\*</sup> Reduced by 4.0 mW for each increase in Ta of 1°C over 25°C.

### ● Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply voltage | Vcc    | 3.0  | _    | 5.5  | V    |

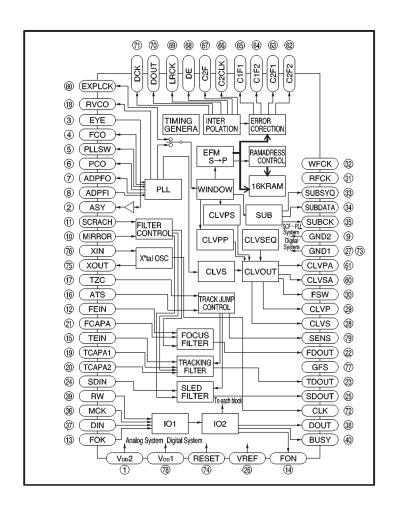

### ●Block diagram

80 ROHM

Optical disc ICs BU9312AKS

# Pin description

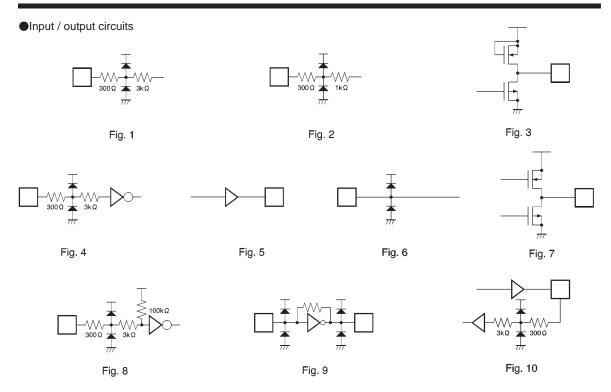

| Pin No. | Pin name          | Analog /<br>digital | 1/0 | Function                                                     | I / O circuit |

|---------|-------------------|---------------------|-----|--------------------------------------------------------------|---------------|

| 1       | V <sub>DD</sub> 2 | _                   | _   | PLL and servo filter block power supply                      | _             |

| 2       | ASY               | Digital             | 0   | EFM signal slicing level control output                      | Fig.5         |

| 3       | EYE               | Digital             | - 1 | Input of EFM signals from the RF amplifier                   | Fig.4         |

| 4       | FCO               | Analog              | 0   | PLL frequency comparison error voltage output                | Fig.7         |

| 5       | PLLSW             | Digital             | 0   | PLL time constant switching                                  | Fig.3         |

| 6       | PCO               | Analog              | 0   | PLL phase comparison error voltage output                    | Fig.7         |

| 7       | ADPFO             | Analog              | 0   | PLL adding amplifier output                                  | Fig.2         |

| 8       | ADPFI             | Analog              | I   | PLL adding amplifier inverted input                          | Fig.1         |

| 9       | GND2              | _                   | _   | PLL servo filter block ground                                | _             |

| 10      | MIRROR            | Digital             | I   | Mirror signal input                                          | Fig.4         |

| 11      | SCRACH            | Digital             | 1   | Scratch signal input                                         | Fig.4         |

| 12      | FEIN              | Analog              | 1   | Focus error signal input                                     | Fig.1         |

| 13      | FOK               | Digital             | 1   | Focus OK signal input                                        | Fig.4         |

| 14      | FON               | Digital             | 0   | Focus ON signal output                                       | Fig.5         |

| 15      | TEIN              | Analog              | 1   | Tracking error signal input                                  | Fig.1         |

| 16      | ATS               | Analog              | I   | Anti-shock detection window comparator input                 | Fig.1         |

| 17      | TZC               | Analog              | I   | Tracking zero-cross comparator input                         | Fig.1         |

| 18      | RVCO              | Analog              | 0   | PLL VCO free running resistor                                | Fig.2         |

| 19      | TCAPA1            | Analog              | 1/0 | Tracking servo filter capacitor connection                   | Fig.6         |

| 20      | TCAPA2            | Analog              | 1/0 | Tracking servo filter capacitor connection                   | Fig.6         |

| 21      | FCAPA             | Analog              | 1/0 | Focus servo filter capacitor connection                      | Fig.6         |

| 22      | FDOUT             | Analog              | 0   | Focus driver output                                          | Fig.2         |

| 23      | TDOUT             | Analog              | 0   | Tracking drive output                                        | Fig.2         |

| 24      | SDIN              | Analog              | 1   | Thread amplifier input                                       | Fig.1         |

| 25      | SDOUT             | Analog              | 0   | Thread driver output                                         | Fig.2         |

| 26      | VREF              | Analog              | I   | Bias voltage input                                           | Fig.6         |

| 27      | GND1              | _                   | _   | Digital ground                                               | _             |

| 28      | CLVS              | Digital             | 0   | Spindle motor drive output (speed control output)            | Fig.7         |

| 29      | CLVP              | Digital             | 0   | Spindle motor drive output (rough or phase control output)   | Fig.7         |

| 30      | FSW               | Digital             | 0   | Spindle motor output (filter time constant switching output) | Fig.3         |

| 31      | RFCK              | Digital             | 0   | Read frame clock output (X'tal 7.35 kHz)                     | Fig.5         |

| 32      | WFCK              | Digital             | 0   | Write frame clock output (7.35 kHz when locked on X'tal)     | Fig.5         |

| 33      | SUBSYQ            | Digital             | 0   | Subcode sink S0 + S1 output                                  | Fig.5         |

| 34      | SUBDATA           | Digital             | 0   | Subcode serial output                                        | Fig.5         |

Optical disc ICs BU9312AKS

| Pin No. | Pin name          | Analog /<br>digital | 1/0 | Function                                                                                                | I / O circuit |

|---------|-------------------|---------------------|-----|---------------------------------------------------------------------------------------------------------|---------------|

| 35      | SUBCK             | Digital             | I   | Subcode read clock                                                                                      | Fig.4         |

| 36      | MCK               | Digital             | 1   | Clock for CPU serial data reading or sub Q code reading                                                 | Fig.4         |

| 37      | DIN               | Digital             | 1   | CPU serial data input                                                                                   | Fig.4         |

| 38      | DOUT              | Digital             | 0   | Sub Q code or internal status serial output                                                             | Fig.7         |

| 39      | RW                | Digital             | I   | Read / write switching or track jump command input (H = data output from DOUT, L = data input from DIN) | Fig.4         |

| 40      | BUSY              | Digital             | 0   | Busy output (L during track jumping)                                                                    | Fig.5         |

| 41~59   | N.C.              | _                   | _   | _                                                                                                       | _             |

| 60      | CLVPA             | Analog              | 0   | CLV phase linear output                                                                                 | Fig.1         |

| 61      | CLVSA             | Analog              | 0   | CLV speed linear output                                                                                 | Fig.1         |

| 62      | C2F2              | Digital             | 0   | C2 double correction flag                                                                               | Fig.5         |

| 63      | C2F1              | Digital             | 0   | C2 single correction flag                                                                               | Fig.5         |

| 64      | C1F2              | Digital             | 0   | C1 double correction flag                                                                               | Fig.5         |

| 65      | C1F1              | Digital             | 0   | C1 single correction flag                                                                               | Fig.5         |

| 66      | C2CLK             | Digital             | 0   | Strobe signal (f = 176.4 kHz)                                                                           | Fig.5         |

| 67      | C2F               | Digital             | 0   | Correction status output                                                                                | Fig.5         |

| 68      | DE                | Digital             | 0   | Strobe signal (f = 88.2 kHz)                                                                            | Fig.5         |

| 69      | LRCK              | Digital             | 0   | Strobe signal (f = 44.1 kHz)                                                                            | Fig.5         |

| 70      | DOUTA             | Digital             | 0   | Audio data output (2'SCOMP)                                                                             | Fig.5         |

| 71      | DOCK              | Digital             | 0   | DOUTA bit clock (f = 2.1168 MHz)                                                                        | Fig.5         |

| 72      | CLK               | Digital             | 0   | Clock output (4 settings selected with &hE4 command)                                                    | Fig.5         |

| 73      | GND1              | _                   | _   | Digital ground                                                                                          | _             |

| 74      | RESET             | Digital             | 1   | Internal circuit reset (pulled up with 100 kΩ internal resistor)                                        | Fig.8         |

| 75      | XOUT              | Digital             | 0   | X'tal oscillator output (f = 16.9 MHz)                                                                  | Fig.9         |

| 76      | XIN               | Digital             | 1   | X'tal oscillator input (f = 16.9 MHz)                                                                   | Fig.9         |

| 77      | GFS               | Digital             | 0   | GFS monitor output (4 settings selected with &hE4 command)                                              | Fig.5         |

| 78      | V <sub>DD</sub> 1 | _                   | _   | Digital power supply                                                                                    | _             |

| 79      | SENS              | Digital             | 0   | Status output for signal selected with the &hE4 command                                                 | Fig.5         |

| 80      | EXPLCK            | Digital             | 1/0 | PLL output and playback clock input for attached PLL                                                    | Fig.10        |

●Electrical characteristics (unless otherwise noted, Ta = 25°C, VDD = 5V)

| Parameter                  | Symbol          | Min. | Тур. | Max.            | Unit | Conditions            | Suitable pins |

|----------------------------|-----------------|------|------|-----------------|------|-----------------------|---------------|

| Input voltage, high level  | Vін             | 3.5  | _    | _               | V    |                       | *1            |

| Input voltage, low level   | VIL             | _    | _    | 0.3             | V    |                       | *1            |

| Output voltage, high level | Vон             | 4.0  | _    | V <sub>DD</sub> | V    | I <sub>OH</sub> =-1mA | *2            |

| Output voltage, low level  | Vol             | 0    | _    | 0.4             | V    | I <sub>OL</sub> =1mA  | *2, 5         |

| Input resistance 1         | V <sub>01</sub> | 80   | 100  | 120             | kΩ   | Between VDD1 pins     | *3            |

| Input resistance 2         | V02             | 60   | 75   | 90              | kΩ   | Between BIAS pins     | TZC           |

| Input resistance 3         | Vоз             | 180  | 230  | 280             | kΩ   | Between BIAS pins     | ATS           |

| Input resistance 4         | V <sub>04</sub> | 20   | 25   | 30              | kΩ   | Between BIAS pins     | *6            |

| Input leakage current      | lu              | _    | _    | ±5              | μΑ   | V₁=0~5.25V            | *1, 2         |

| Output leakage current     | ILO             | _    | _    | ±5              | μΑ   | Vo=0~5.25V            | *4, 5         |

#### Suitable pins

- \*1 MIRROR, SCRACH, FOK, SUBCK, MCK, DIN, RW, RESET, EXPLCK, EYE

- \*2 FON, CLVS, CLVP, RFCK, WFCK, SUBSYQ, SUBDATA, DOUT, BUSY, XOUT, SENS, GFS, ASY, C1F1, C1F2, C2F1, C2F2, C2CLK, C2F, DE, LRCK, DOCK, CLK

- \*3 RESET

- \*4 CLVS, CLVP

- \*5 PLLSW, TCAPA2, FSW

- \*6 FEIN, TEIN

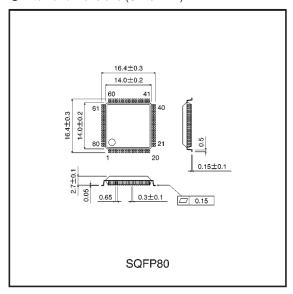

# ●External dimensions (Units: mm)

84 NOHM