# ST92F124/ST92F150/ST92F250

# 8/16-BIT SINGLE VOLTAGE FLASH MCU FAMILY WITH RAM, E<sup>3 TM</sup>(EMULATED EEPROM), CAN 2.0B AND J1850 BLPD

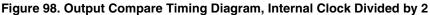

### Memories

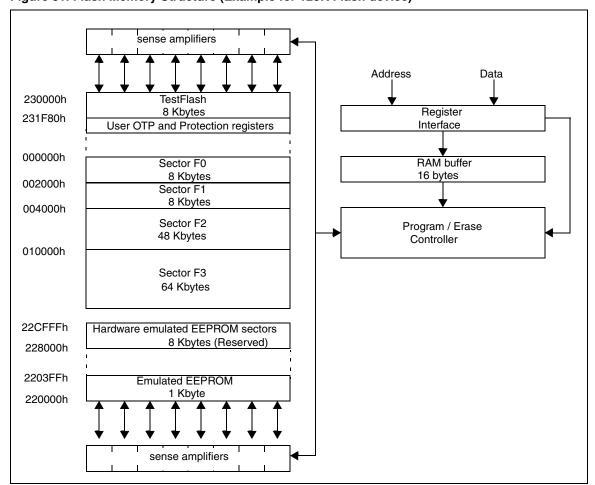

- Internal Memory: Single Voltage FLASH up to 256 Kbytes, RAM up to 8Kbytes, 1K byte E<sup>3 TM</sup> (Emulated EEPROM)

- In-Application Programming (IAP)

- 224 general purpose registers (register file) available as RAM, accumulators or index pointers

### Clock, Reset and Supply Management

- Register-oriented 8/16 bit CORE with RUN, WFI. SLOW, HALT and STOP modes

- 0-24 MHz Operation (Int. Clock), 4.5-5.5 V range

- PLL Clock Generator (3-5 MHz crystal)

- Minimum instruction time: 83 ns (24 MHz int. clock)

### ■ Up to 80 I/O pins

### **■ Interrupt Management**

- 4 external fast interrupts + 1 NMI

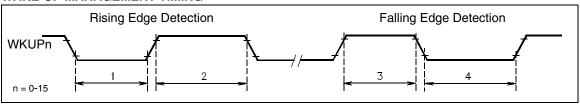

- Up to 16 pins programmable as wake-up or additional external interrupt with multi-level interrupt handler

### ■ DMA controller for reduced processor overhead

### Timers

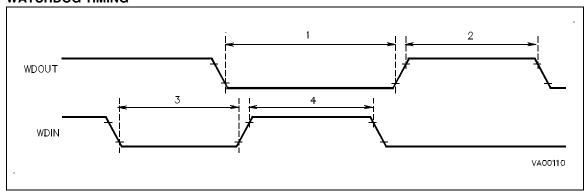

- 16-bit Timer with 8-bit Prescaler, and Watchdog Timer (activated by software or by hardware)

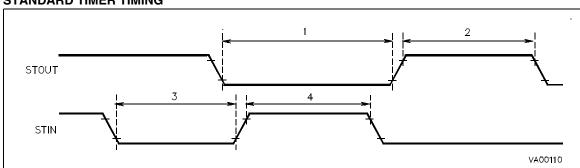

- 16-bit Standard Timer that can be used to generate a time base independent of PLL Clock Generator

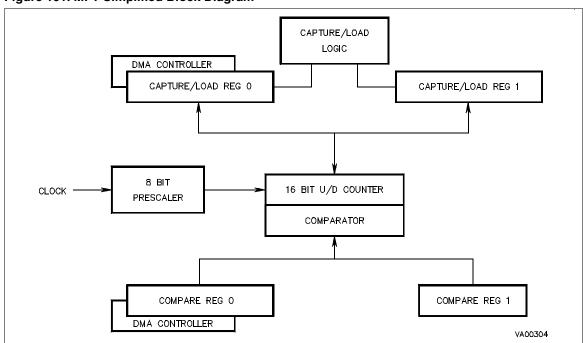

- Two 16-bit independent Extended Function Timers (EFTs) with Prescaler, up to two Input Captures and ùp to two Output Compares

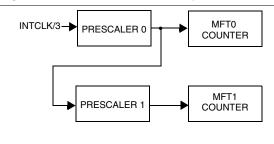

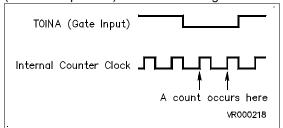

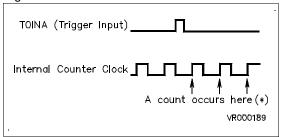

- Two 16-bit Multifunction Timers, with Prescaler, up to two Input Captures and up to two Output Com-

### **Communication Interfaces**

- Serial Peripheral Interface (SPI) with Selectable Master/Slave mode

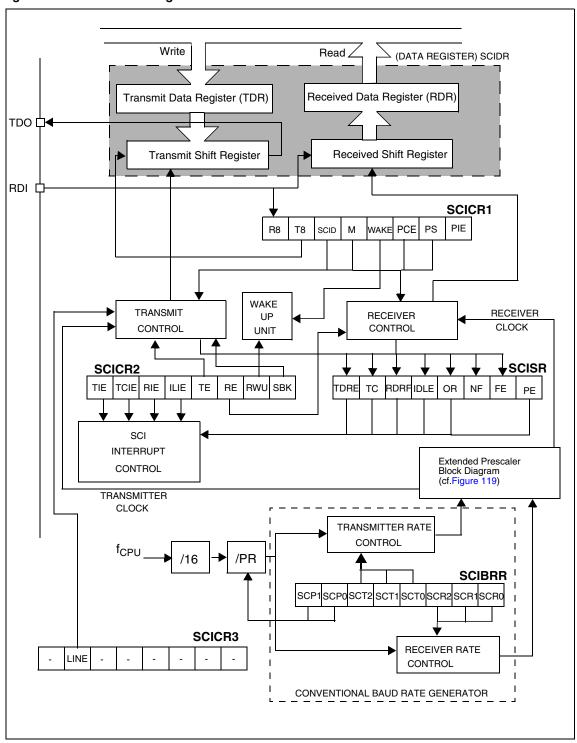

- One Multiprotocol Serial Communications Interface with asynchronous and synchronous capabilities

- One asynchronous Serial Communications Interface with 13-bit LIN Synch Break generation capability

- J1850 Byte Level Protocol Decoder (JBLPD)

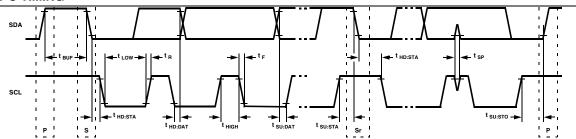

- Up to two full I2C multiple Master/Slave Interfaces supporting Access Bus

- Up to two CAN 2.0B Active interfaces

### ■ Analog peripheral (low current coupling)

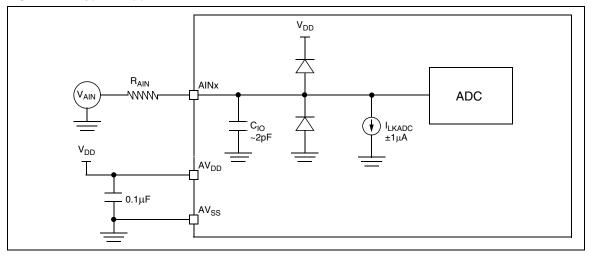

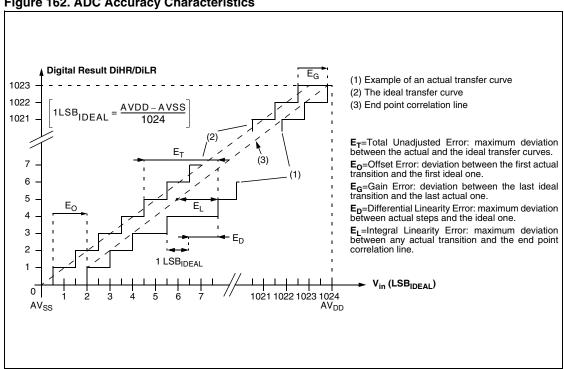

10-bit A/D Converter witvalh up to 16 robust input channels

### ■ Development Tools

- Free High performance Development environment (IDE) based on Visual Debugger, Assembler, Linker, and C-Compiler; Real Time Operating System (OS-EK OS, CMX) and CAN drivers

- Hardware Emulator and Flash Programming Board for development and ISP Flasher for production

### **DEVICE SUMMARY 2)**

| Features                  | ST92F124R9                 | ST92F124V1                   | ST92F150CR9/1              | ST92F150CV9/1                | ST92F150JDV1                 | ST92F250CV2                           |

|---------------------------|----------------------------|------------------------------|----------------------------|------------------------------|------------------------------|---------------------------------------|

| FLASH - bytes             | 64K                        | 128K                         | 64K/128K                   | 64K/128K                     | 128K                         | 256K                                  |

| RAM - bytes               | 2K                         | 4K                           | 2K/4K                      | 2K/4K                        | 6K                           | 8K                                    |

| E <sup>3 TM</sup> - bytes | 1K                         | 1K                           | 1K                         | 1K                           | 1K                           | 1K                                    |

| Timers and                | 2 MFT, 2 EFT,              | 2 MFT, 2 EFT,                | 2 MFT, 2 EFT,              | 2 MFT, 2 EFT,                | 2 MFT, 2 EFT,                | 2 MFT, 2 EFT,                         |

| Serial                    | STIM, WD,                  | STIM, WD,                    | STIM, WD,                  | STIM, WD,                    | STIM, WD,                    | STIM, WD, 2 SCI,                      |

| Interface                 | SCI, SPI, I <sup>2</sup> C | 2 SCI, SPI, I <sup>2</sup> C | SCI, SPI, I <sup>2</sup> C | 2 SCI, SPI, I <sup>2</sup> C | 2 SCI, SPI, I <sup>2</sup> C | SPI, 2 I <sup>2</sup> C <sup>1)</sup> |

| ADC                       | 16 x 10 bits               | 16 x 10 bits                 | 16 x 10 bits               | 16 x 10 bits                 | 16 x 10 bits                 | 16 x 10 bits                          |

| Network Inter-<br>face    | -                          | LIN Master                   | CAN                        | CAN, LIN Master              | 2 CAN,J1850,<br>LIN Master   | CAN, LIN Master                       |

| Packages                  | TQFP64                     | P/TQFP100                    | TQFP64                     | P/TQFP100                    | P/TQ                         | FP100                                 |

1) see Section 12.4 on page 406 for important information 2) see Table 71 on page 403 for the list of supported part numbers

Rev. 4.0

1/426 November 2004

# **Table of Contents**

| 1 GENE         | RAL DESCRIPTION                                               | 4   |

|----------------|---------------------------------------------------------------|-----|

| 1.1            | INTRODUCTION                                                  | 4   |

| 1.2            | PIN DESCRIPTION                                               | 10  |

| 1.3            | VOLTAGE REGULATOR                                             | 22  |

| 1.4            | I/O PORTS                                                     |     |

| 1.5            | ALTERNATE FUNCTIONS FOR I/O PORTS                             | 25  |

| 1.6            | OPERATING MODES                                               |     |

| 2 DEVIC        | E ARCHITECTURE                                                | 30  |

| 2.1            | CORE ARCHITECTURE                                             | 30  |

| 2.2            | MEMORY SPACES                                                 | 30  |

| 2.3            | SYSTEM REGISTERS                                              |     |

| 2.4            | MEMORY ORGANIZATION                                           | 41  |

| 2.5            | MEMORY MANAGEMENT UNIT                                        | 42  |

| 2.6            | ADDRESS SPACE EXTENSION                                       |     |

| 2.7            | MMU REGISTERS                                                 |     |

| 2.8            | MMU USAGE                                                     |     |

| 3 SINGL        | E VOLTAGE FLASH & E3 TM (EMULATED EEPROM)                     |     |

| 3.1            | INTRODUCTION                                                  |     |

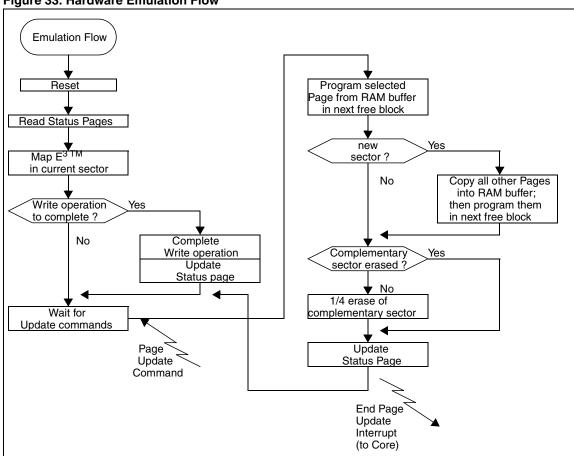

| 3.2            | FUNCTIONAL DESCRIPTION                                        | 51  |

| 3.3            | REGISTER DESCRIPTION                                          | 55  |

| 3.4            | WRITE OPERATION EXAMPLE                                       | 59  |

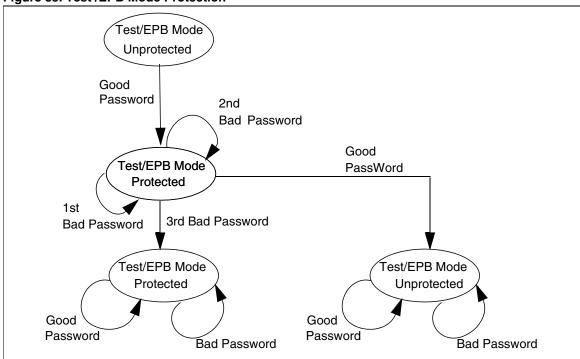

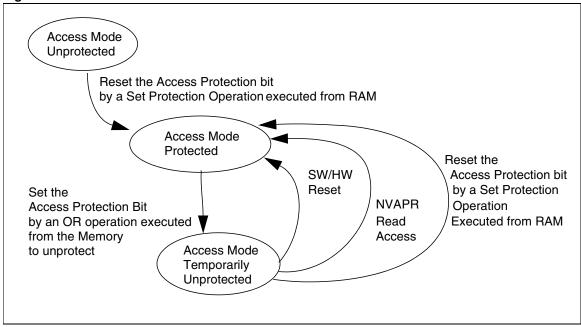

| 3.5            | PROTECTION STRATEGY                                           |     |

| 3.6            | FLASH IN-SYSTEM PROGRAMMING                                   |     |

| 4 REGIS        | TER AND MEMORY MAP                                            |     |

| 4.1            | INTRODUCTION                                                  |     |

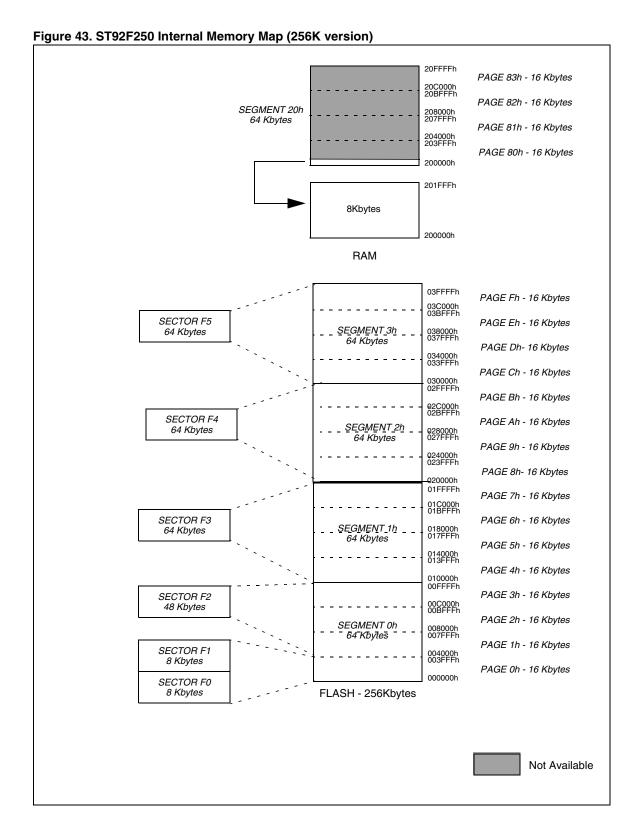

| 4.2            | MEMORY CONFIGURATION                                          | 67  |

| 4.3            | ST92F124/F150/F250 REGISTER MAP                               |     |

| <b>5 INTER</b> | RUPTS                                                         |     |

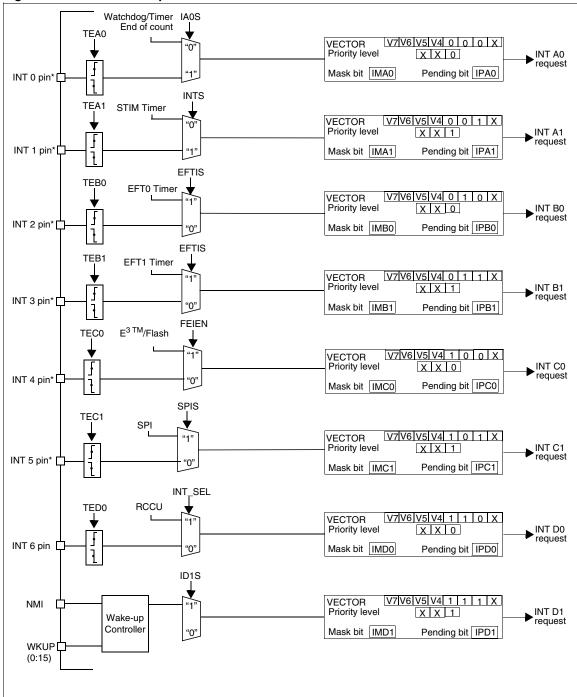

| 5.1            | INTRODUCTION                                                  | 91  |

| 5.2            | INTERRUPT VECTORING                                           | 91  |

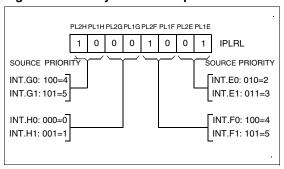

| 5.3            | INTERRUPT PRIORITY LEVELS                                     |     |

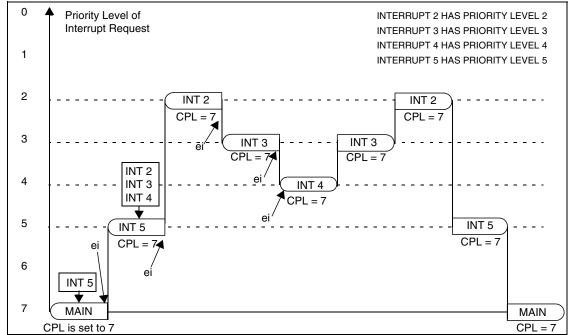

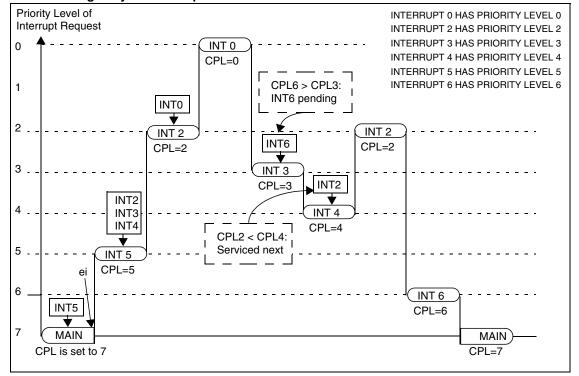

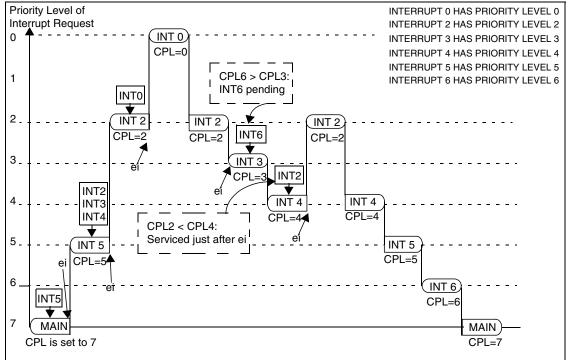

| 5.4            | PRIORITY LEVEL ARBITRATION                                    |     |

| 5.5            | ARBITRATION MODES                                             |     |

| 5.6            | EXTERNAL INTERRUPTS                                           |     |

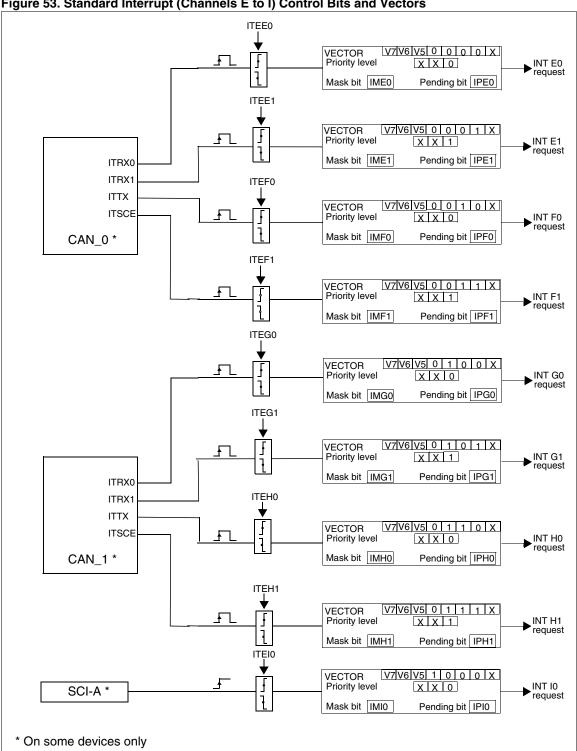

| 5.7            | STANDARD INTERRUPTS (CAN AND SCI-A)                           |     |

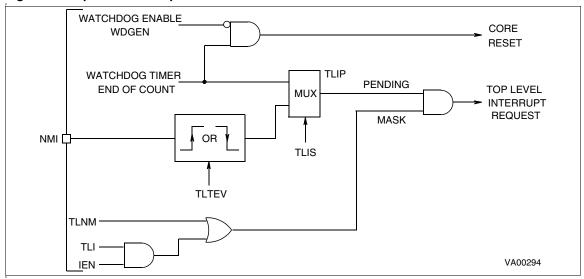

| 5.8            | TOP LEVEL INTERRUPT                                           |     |

| 5.9            | DEDICATED ON-CHIP PERIPHERAL INTERRUPTS                       |     |

|                | INTERRUPT RESPONSE TIME                                       |     |

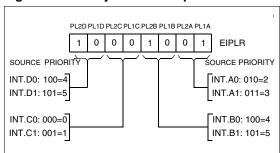

| 5.11           | INTERRUPT REGISTERS                                           |     |

|                | ${\sf WAKE\text{-}UP/INTERRUPTLINESMANAGEMENTUNIT(WUIMU)}\ .$ |     |

|                | IIP DIRECT MEMORY ACCESS (DMA)                                |     |

| 6.1            | INTRODUCTION                                                  |     |

| 6.2            | DMA PRIORITY LEVELS                                           |     |

| 6.3            | DMA TRANSACTIONS                                              |     |

| 6.4            | DMA CYCLE TIME                                                |     |

| 6.5            | SWAP MODE                                                     | 123 |

# Table of Contents

| 6.6      | DMA REGISTERS                                         | 124 |

|----------|-------------------------------------------------------|-----|

| 7 RESE   | T AND CLOCK CONTROL UNIT (RCCU)                       | 125 |

| 7.1      | INTRODUCTION                                          |     |

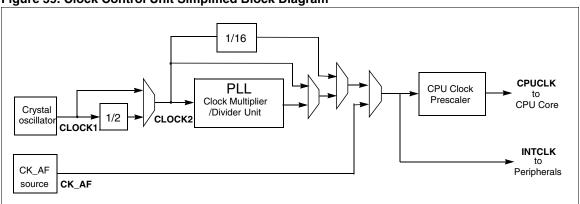

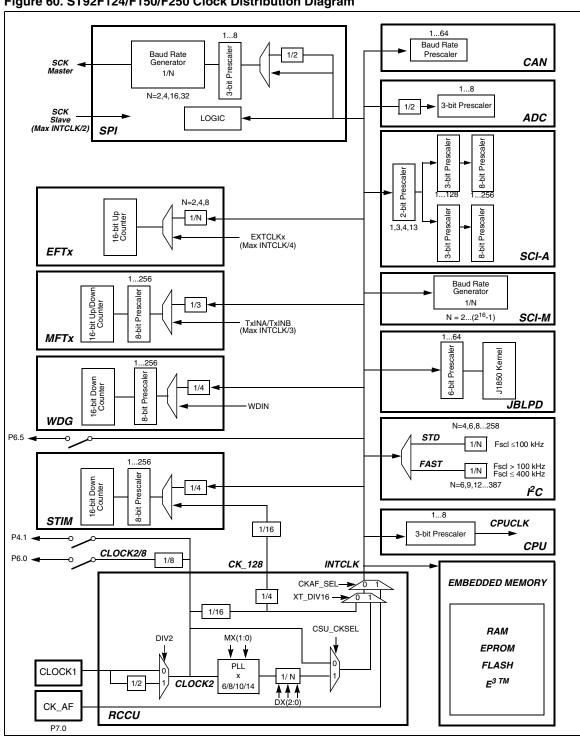

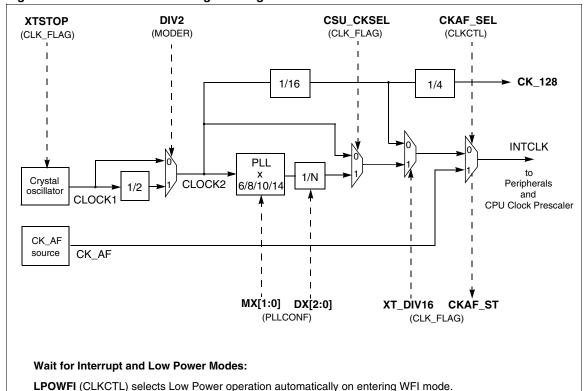

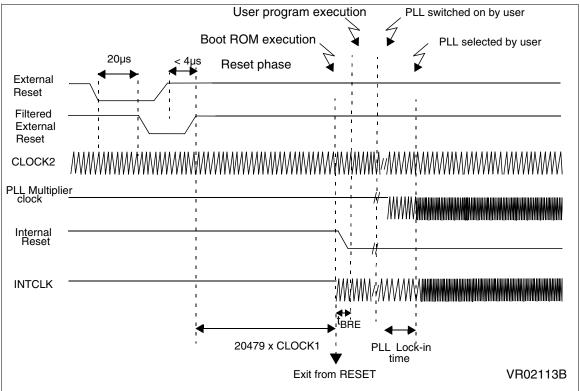

| 7.2      | CLOCK CONTROL UNIT                                    | 125 |

| 7.3      | CLOCK MANAGEMENT                                      |     |

| 7.4      | CLOCK CONTROL REGISTERS                               | 133 |

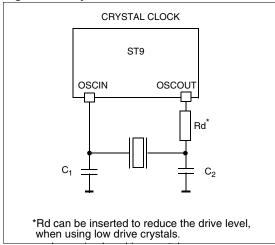

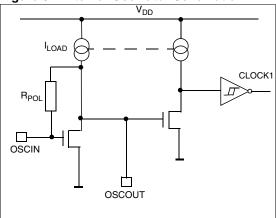

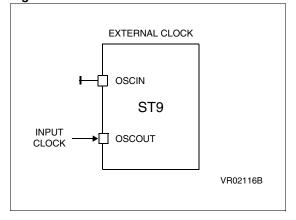

| 7.5      | CRYSTAL OSCILLATOR                                    |     |

| 7.6      | RESET/STOP MANAGER                                    |     |

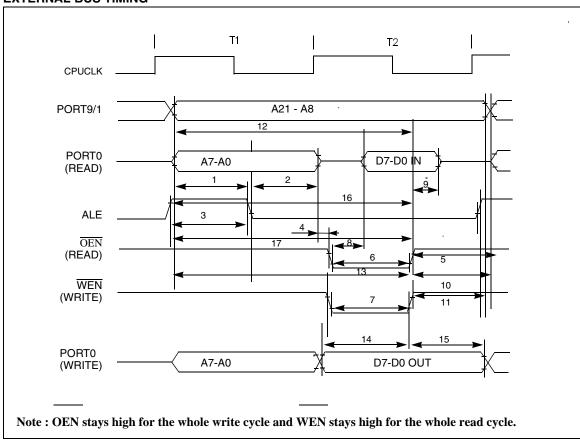

| 8 EXTER  | RNAL MEMORY INTERFACE (EXTMI)                         | 141 |

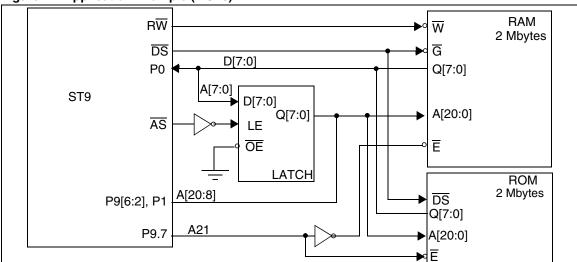

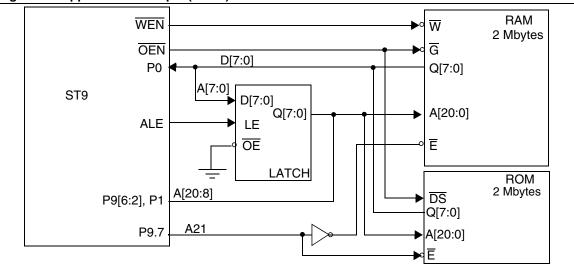

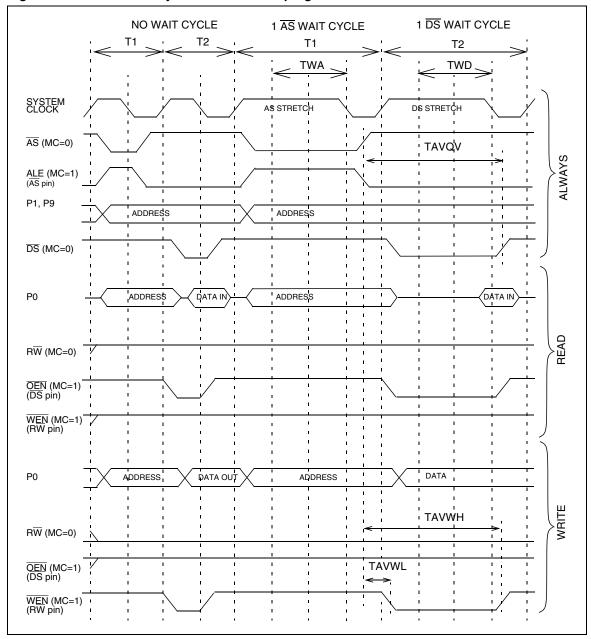

| 8.1      | INTRODUCTION                                          |     |

| 8.2      | EXTERNAL MEMORY SIGNALS                               | 142 |

| 8.3      | REGISTER DESCRIPTION                                  | 147 |

| 9 I/O PO | PRTS                                                  | 150 |

| 9.1      | INTRODUCTION                                          |     |

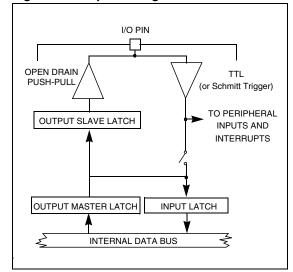

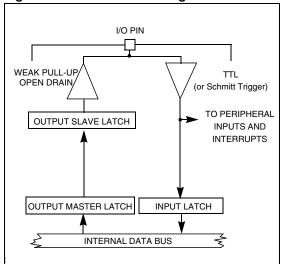

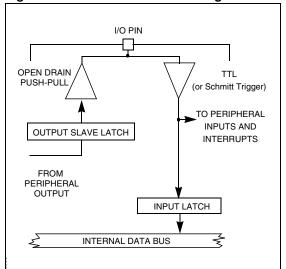

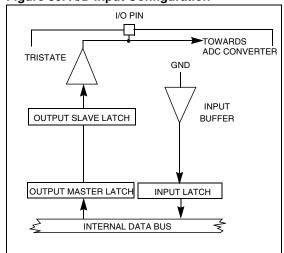

| 9.2      | SPECIFIC PORT CONFIGURATIONS                          | 150 |

| 9.3      | PORT CONTROL REGISTERS                                |     |

| 9.4      | INPUT/OUTPUT BIT CONFIGURATION                        | 151 |

| 9.5      | ALTERNATE FUNCTION ARCHITECTURE                       | 155 |

| 9.6      | I/O STATUS AFTER WFI, HALT AND RESET                  | 155 |

| 10 ON-C  | CHIP PERIPHERALS                                      | 156 |

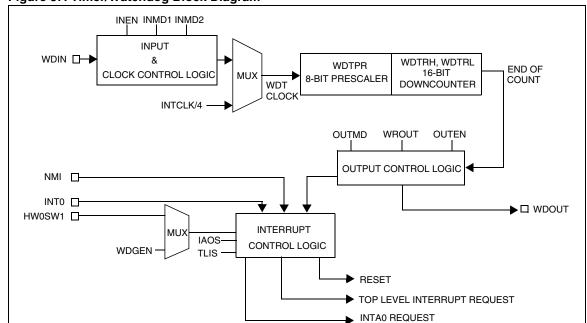

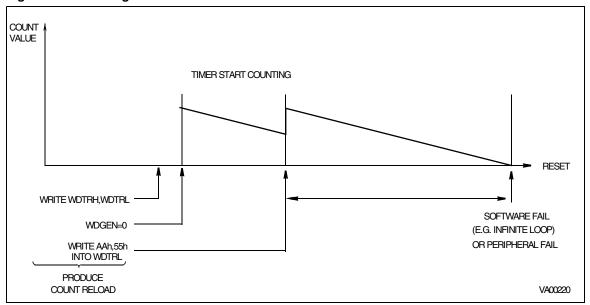

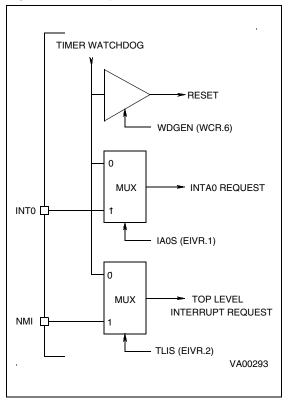

| 10.1     | TIMER/WATCHDOG (WDT)                                  | 156 |

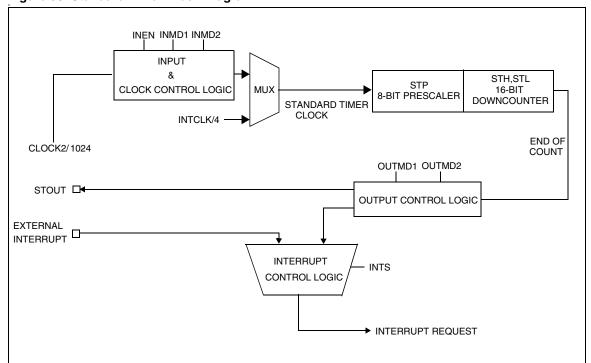

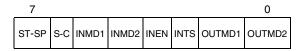

| 10.2     | STANDARD TIMER (STIM)                                 | 163 |

| 10.3     |                                                       |     |

| 10.4     | MULTIFUNCTION TIMER (MFT)                             |     |

| 10.5     | MULTIPROTOCOL SERIAL COMMUNICATIONS INTERFACE (SCI-M) | 211 |

| 10.6     | (                                                     |     |

| 10.7     | SERIAL PERIPHERAL INTERFACE (SPI)                     | 249 |

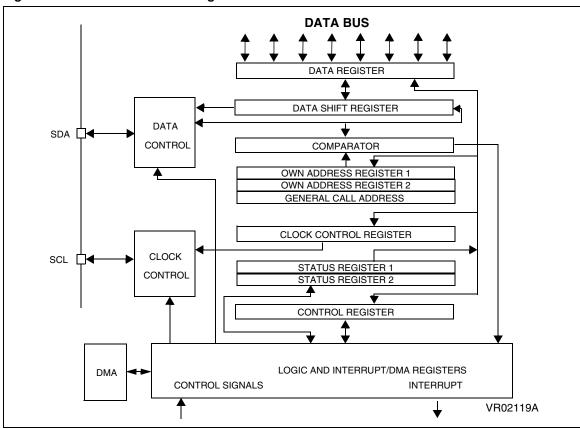

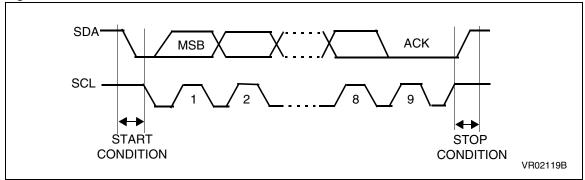

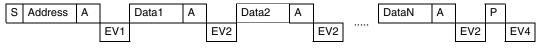

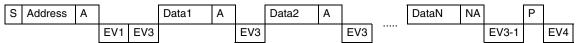

| 10.8     | I2C BUS INTERFACE                                     |     |

| 10.9     |                                                       |     |

|          | CONTROLLER AREA NETWORK (BXCAN)                       |     |

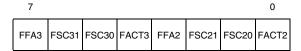

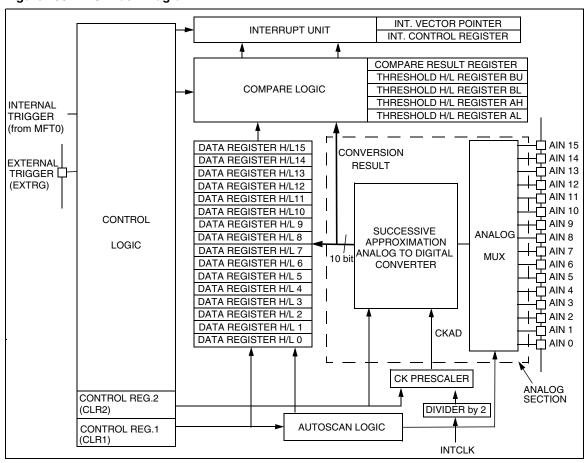

| 10.11    | 10-BIT ANALOG TO DIGITAL CONVERTER (ADC)              | 361 |

| 11 ELEC  | CTRICAL CHARACTERISTICS                               | 374 |

| 12 GENI  | ERAL INFORMATION                                      | 402 |

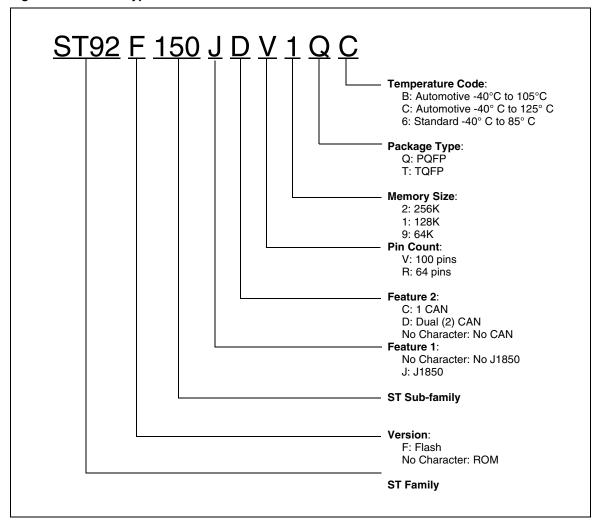

|          | ORDERING INFORMATION                                  |     |

| 12.2     | VERSION-SPECIFIC SALES CONDITIONS                     | 402 |

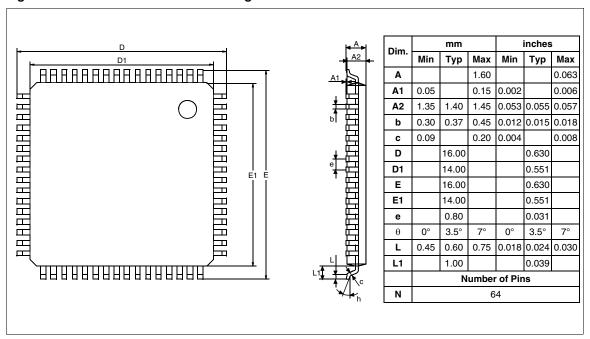

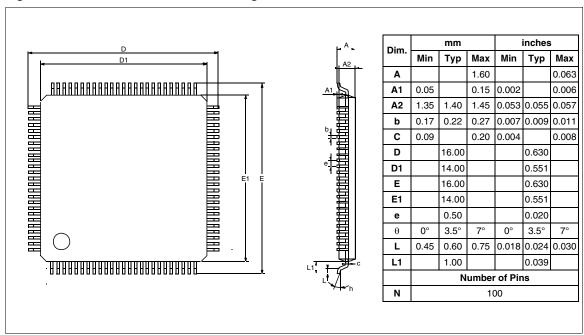

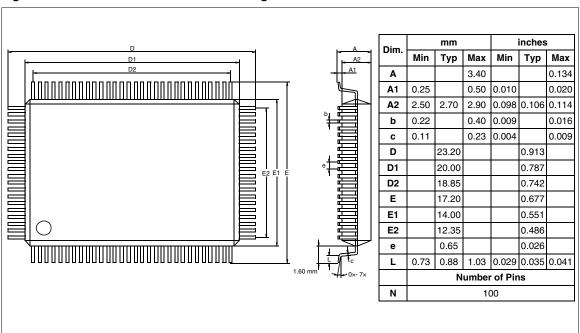

| 12.3     | PACKAGE MECHANICAL DATA                               | 404 |

|          | DEVELOPMENT TOOLS                                     |     |

|          | WN LIMITATIONS                                        |     |

| _        | ST92F124/F150/F250 KNOWN LIMITATIONS                  | -   |

| 13.2     | ST92F150-EMU2 EMULATION CHIP KNOWN LIMITATIONS        | 418 |

| 14 REVI  | SION HISTORY                                          | 425 |

**57**

### 1 GENERAL DESCRIPTION

### 1.1 INTRODUCTION

The ST92F124/F150/F250 microcontroller is developed and manufactured by STMicroelectronics using a proprietary n-well HCMOS process. Its performance derives from the use of a flexible 256-register programming model for ultra-fast context switching and real-time event response. The intelligent on-chip peripherals offload the ST9 core from I/O and data management processing tasks allowing critical application tasks to get the maximum use of core resources. The new-generation ST9 MCU devices now also support low power consumption and low voltage operation for power-efficient and low-cost embedded systems.

### 1.1.1 ST9+ Core

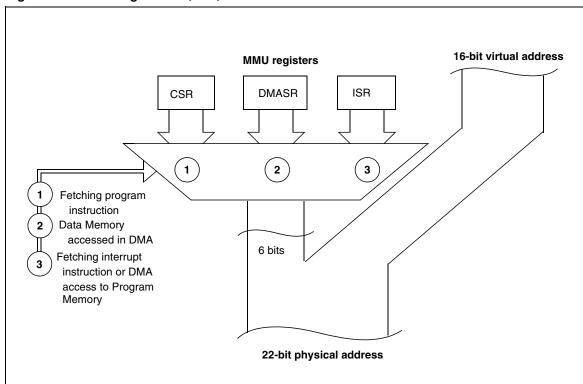

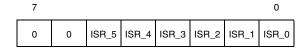

The advanced Core consists of the Central Processing Unit (CPU), the Register File, the Interrupt and DMA controller, and the Memory Management Unit. The MMU allows a single linear address space of up to 4 Mbytes.

Four independent buses are controlled by the Core: a 22-bit memory bus, an 8-bit register data bus, an 8-bit register address bus and a 6-bit interrupt/DMA bus which connects the interrupt and DMA controllers in the on-chip peripherals with the core.

This multiple bus architecture makes the ST9 family devices highly efficient for accessing on and offchip memory and fast exchange of data with the on-chip peripherals.

The general-purpose registers can be used as accumulators, index registers, or address pointers. Adjacent register pairs make up 16-bit registers for addressing or 16-bit processing. Although the ST9 has an 8-bit ALU, the chip handles 16-bit operations, including arithmetic, loads/stores, and memory/register and memory/memory exchanges.

The powerful I/O capabilities demanded by microcontroller applications are fulfilled by the ST92F150/F124 with 48 (64-pin devices) or 77 (100-pin devices) I/O lines dedicated to digital Input/Output and with 80 I/O lines by the ST92F250. These lines are grouped into up to ten 8-bit I/O Ports and can be configured on a bit basis under software control to provide timing, status signals, an address/data bus for interfacing to the external memory, timer inputs and outputs, analog inputs, external interrupts and serial or parallel I/O. Two memory spaces are available to support this wide range of configurations: a combined Program/ Data Memory Space and the internal Register File,

which includes the control and status registers of the on-chip peripherals.

### 1.1.2 External Memory Interface

100-pin devices have a 22-bit external address bus allowing them to address up to 4M bytes of external memory.

### 1.1.3 On-chip Peripherals

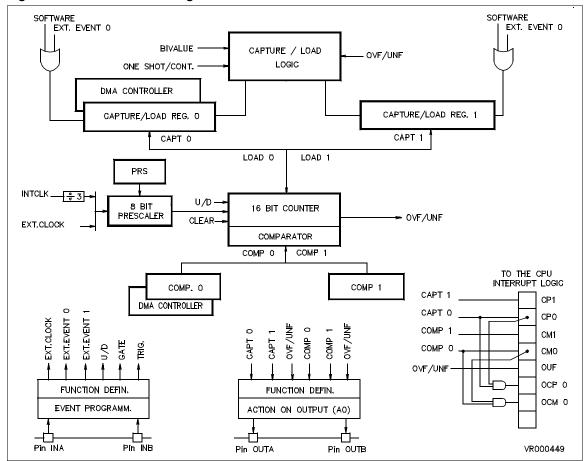

Two 16-bit Multifunction Timers, each with an 8 bit Prescaler and 12 operating modes allow simple use for complex waveform generation and measurement, PWM functions and many other system timing functions by the usage of the two associated DMA channels for each timer.

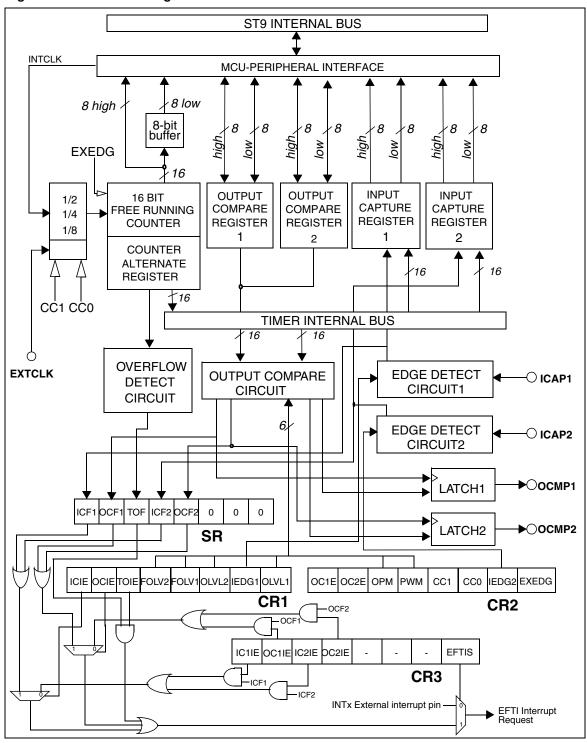

Two Extended Function Timers provide further timing and signal generation capabilities.

A Standard Timer can be used to generate a stable time base independent from the PLL.

An I<sup>2</sup>C interface (two in the ST92F250 device) provides fast I<sup>2</sup>C and Access Bus support.

The SPI is a synchronous serial interface for Master and Slave device communication. It supports single master and multimaster systems.

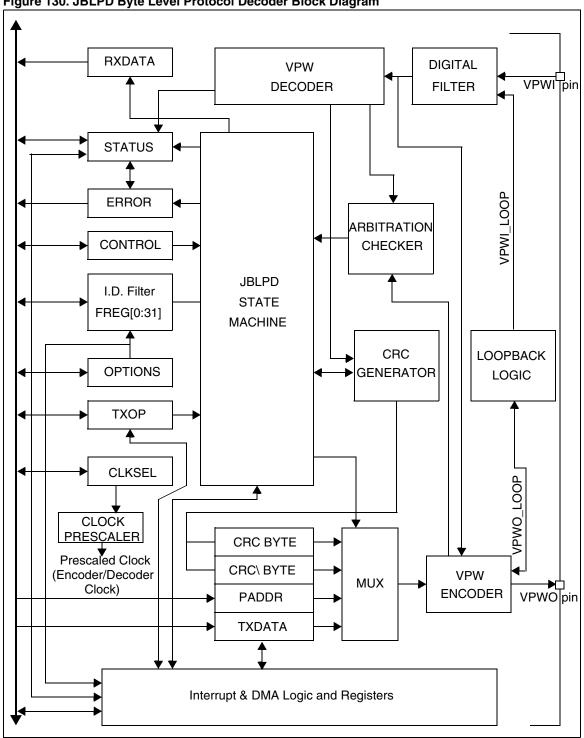

A J1850 Byte Level Protocol Decoder is available (ST92F150JDV1 device only) for communicating with a J1850 network.

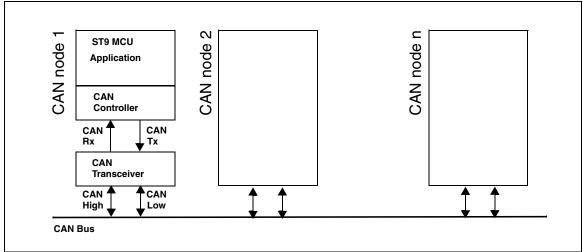

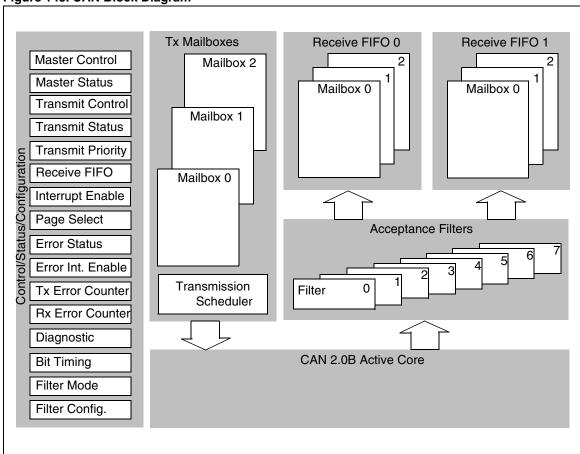

The bxCAN (basic extended) interface (two in the ST92F150JDV1 device) supports 2.0B Active protocol. It has 3 transmit mailboxes, 2 independent receive FIFOs and 8 filters.

In addition, there is an 16 channel Analog to Digital Converter with integral sample and hold, fast conversion time and 10-bit resolution.

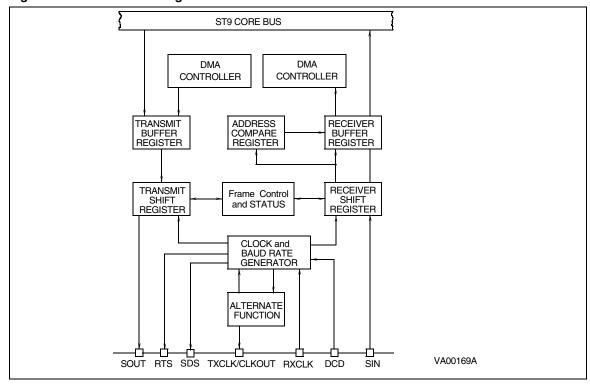

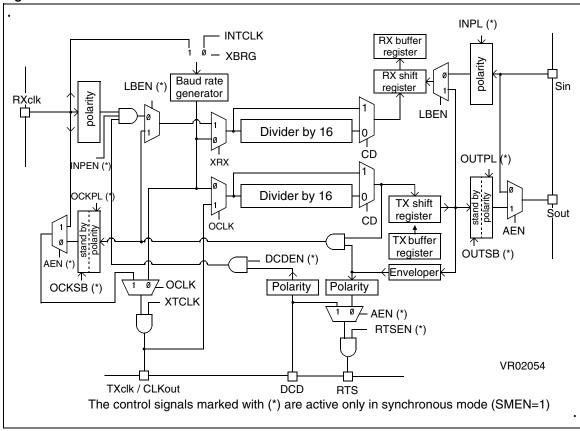

There is one Multiprotocol Serial Communications Interface with an integral generator, asynchronous and synchronous capability (fully programmable format) and associated address/wake-up option, plus two DMA channels.

On 100-pin devices, there is an additional asynchronous Serial Communications interface with 13-bit LIN Synch Break generation capability.

Finally, a programmable PLL Clock Generator allows the usage of standard 3 to 5 MHz crystals to obtain a large range of internal frequencies up to 24 MHz. Low power Run (SLOW), Wait For Interrupt, low power Wait For Interrupt, STOP and HALT modes are also available.

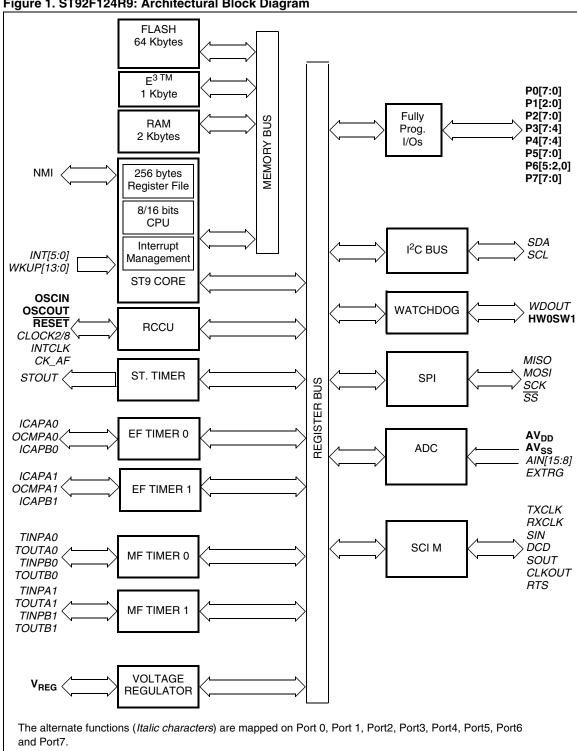

Figure 1. ST92F124R9: Architectural Block Diagram

47/ 5/426

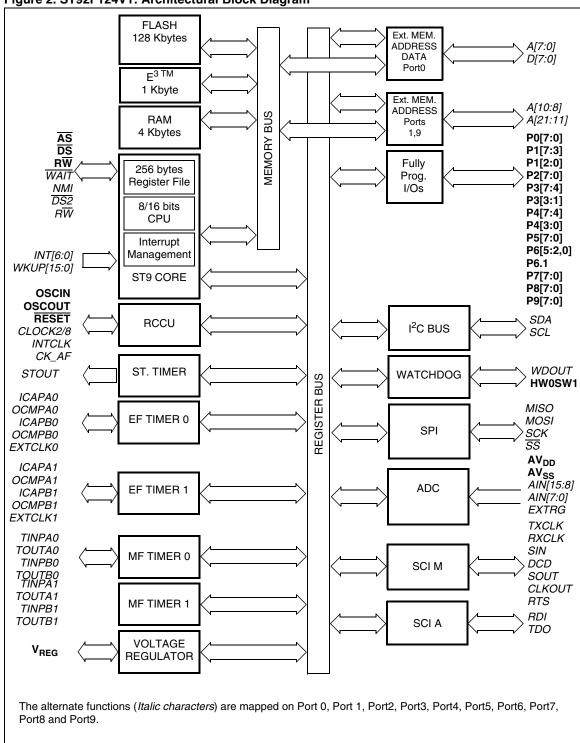

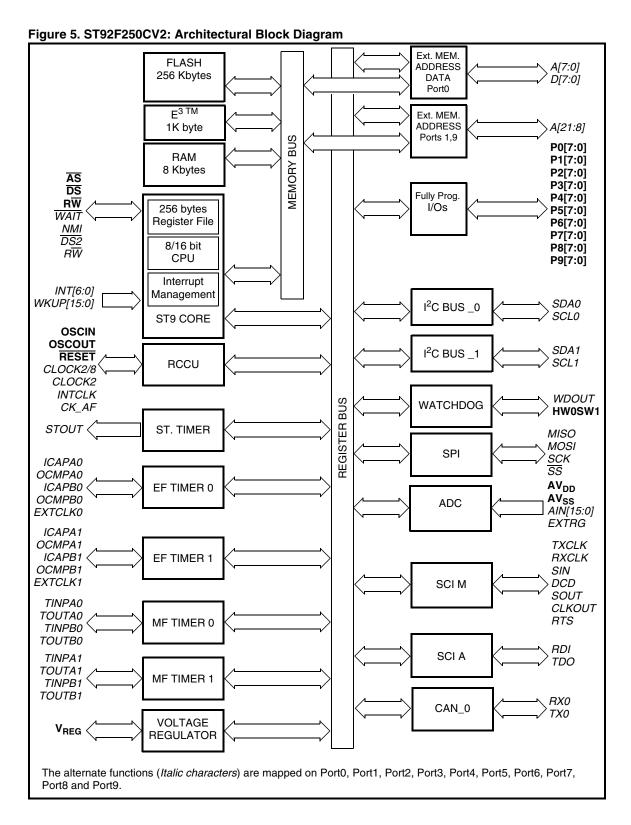

Figure 2. ST92F124V1: Architectural Block Diagram

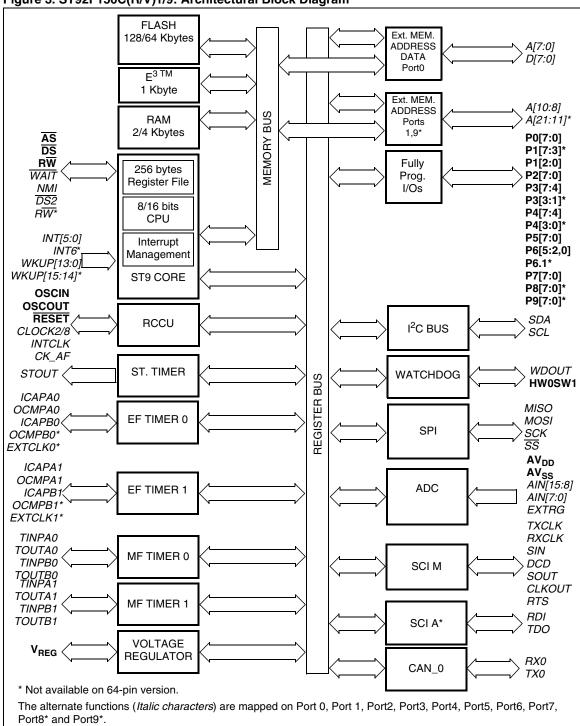

Figure 3. ST92F150C(R/V)1/9: Architectural Block Diagram

**577**

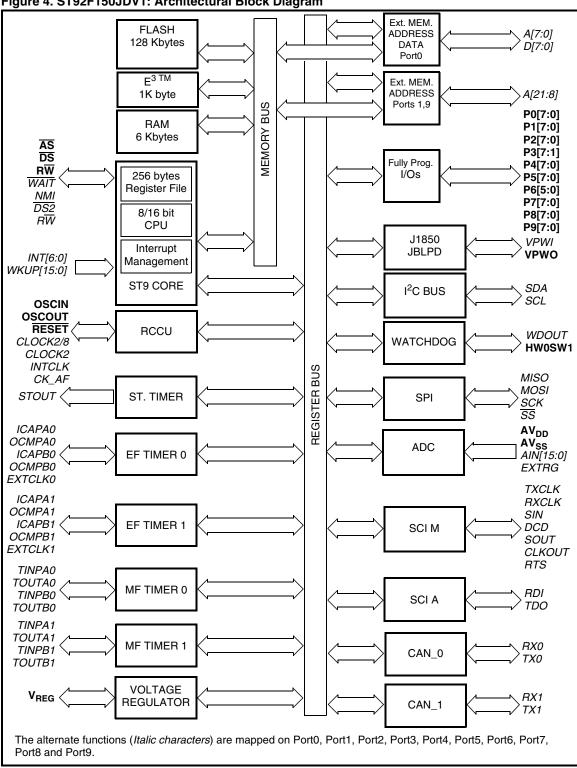

Figure 4. ST92F150JDV1: Architectural Block Diagram

### 1.2 PIN DESCRIPTION

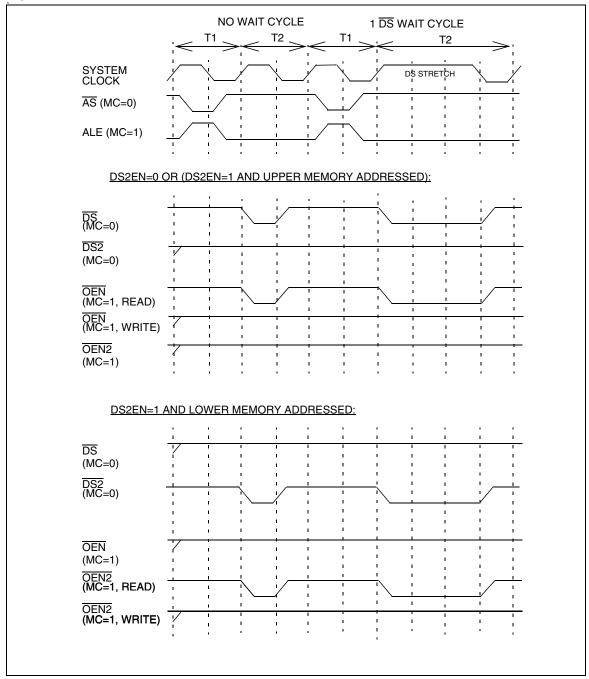

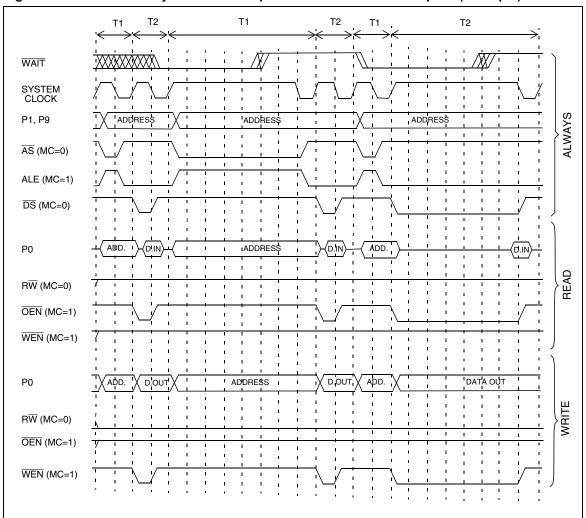

**AS.** Address Strobe (output, active low, 3-state). Address Strobe is pulsed low once at the beginning of each memory cycle. The rising edge of AS indicates that address, Read/Write (RW), and Data signals are valid for memory transfers.

DS. Data Strobe (output, active low, 3-state). Data Strobe provides the timing for data movement to or from Port 0 for each memory transfer. During a write cycle, data out is valid at the leading edge of DS. During a read cycle, Data In must be valid prior to the trailing edge of DS. When the ST9 accesses on-chip memory, DS is held high during the whole memory cycle.

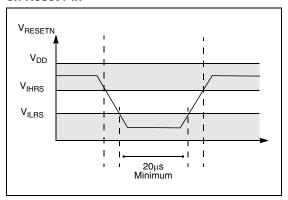

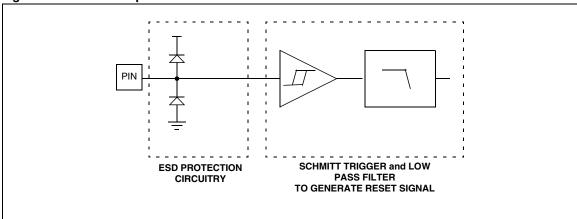

**RESET.** Reset (input, active low). The ST9 is initialised by the Reset signal. With the deactivation of RESET, program execution begins from the Program memory location pointed to by the vector contained in program memory locations 00h and 01h

**RW.** Read/Write (output, 3-state). Read/Write determines the direction of data transfer for external memory transactions. RW is low when writing to external memory, and high for all other transactions.

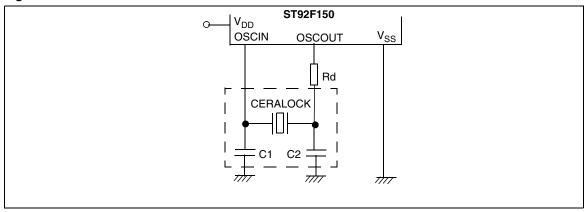

**OSCIN**, **OSCOUT**. Oscillator (input and output). These pins connect a parallel-resonant crystal, or an external source to the on-chip clock oscillator and buffer. OSCIN is the input of the oscillator inverter; OSCOUT is the output of the oscillator inverter.

**HW0SW1.** When connected to  $V_{DD}$  through a 1K pull-up resistor, the software watchdog option is selected. When connected to  $V_{SS}$  through a 1K pull-down resistor, the hardware watchdog option is selected.

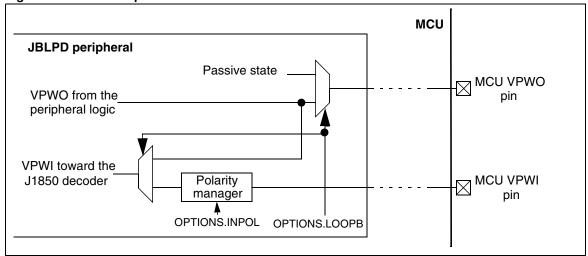

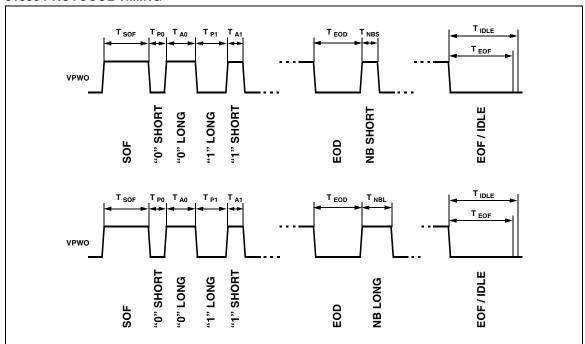

**VPWO**. This pin is the output line of the J1850 peripheral (JBLPD). It is available only on some devices

**RX1/WKUP6.** Receive Data input of CAN1 and Wake-up line 6. Available only on some devices. When the CAN1 peripheral is disabled, a pull-up resistor is connected internally to this pin.

**TX1.** Transmit Data output of CAN1. Available on some devices.

**P0[7:0]**, **P1[7:0]** or **P9[7:2]** (Input/Output, TTL or CMOS compatible). 11 lines (64-pin devices) or 22 lines (100-pin devices) providing the external memory interface for addressing 2K or 4M bytes of external memory.

P0[7:0], P1[2:0], P2[7:0], P3[7:4], P4.[7:4], P5[7:0], P6[5:2,0], P7[7:0] I/O Port Lines (Input/Output, TTL or CMOS compatible). I/O lines grouped into I/O ports of 8 bits, bit programmable under software control as general purpose I/O or as alternate functions.

P1[7:3], P3[3:1], P4[3:0], P6.1, P8[7:0], P9[7:0] Additional I/O Port Lines available on 100-pin versions only.

**P3.0**, **P6[7:6]** Additional I/O Port Lines available on ST92F250 version only.

$AV_{DD}$ . Analog  $V_{DD}$  of the Analog to Digital Converter (common for ADC 0 and ADC 1). AVDD can be switched off when the ADC is not in

$\text{AV}_{\text{SS}}.$  Analog  $\text{V}_{\text{SS}}$  of the Analog to Digital Converter (common for ADC 0 and ADC 1).

**V**<sub>DD</sub>. Main Power Supply Voltage. Four pins are available on 100-pin versions, two on 64-pin versions. The pins are internally connected.

**V<sub>SS</sub>.** Digital Circuit Ground. Four pins are available on 100-pin versions, two on 64-pin versions. The pins are internally connected.

$\mathbf{V}_{\mathsf{TEST}}$  Power Supply Voltage for Flash test purposes. This pin must be kept to 0 in user mode.

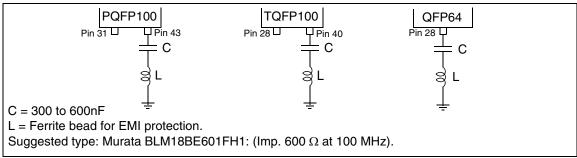

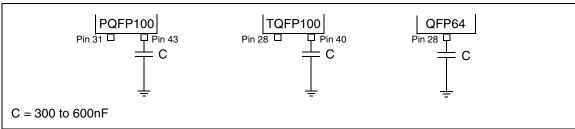

**V**<sub>REG</sub>. Stabilization capacitors for the internal voltage regulator. The user must connect external stabilization capacitors to these pins. Refer to Figure

# 1.2.1 I/O Port Alternate Functions

Each pin of the I/O ports of the ST92F124/F150/F250 may assume software programmable Alternate Functions as shown in Section 1.4.

## 1.2.2 Termination of Unused Pins

For unused pins, input mode is not recommended. These pins must be kept at a fixed voltage using the output push pull mode of the I/O or an external pull-up or pull-down resistor.

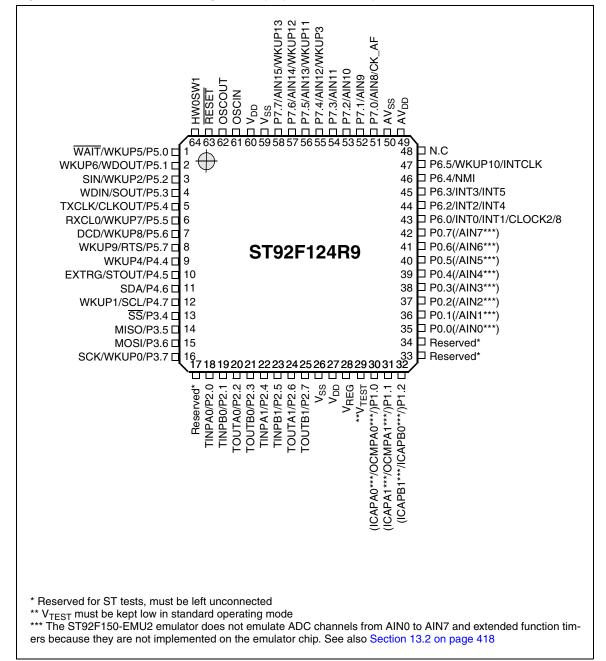

Figure 6. ST92F124R9: Pin Configuration (Top-view TQFP64)

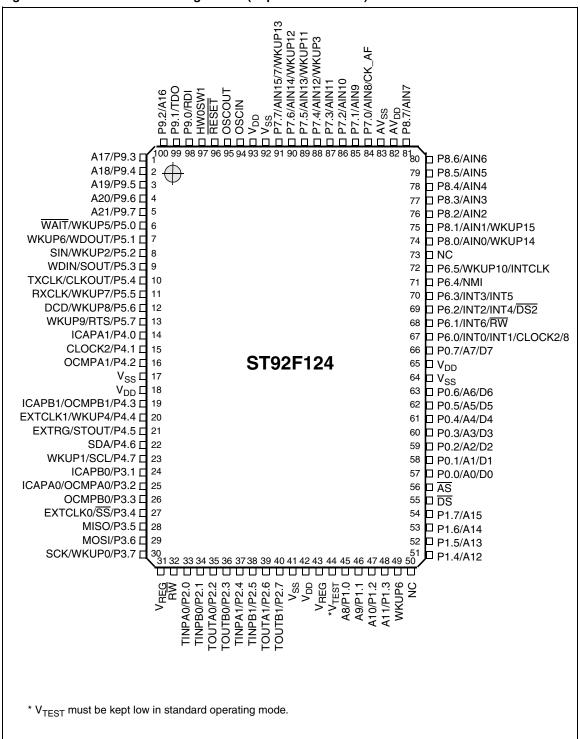

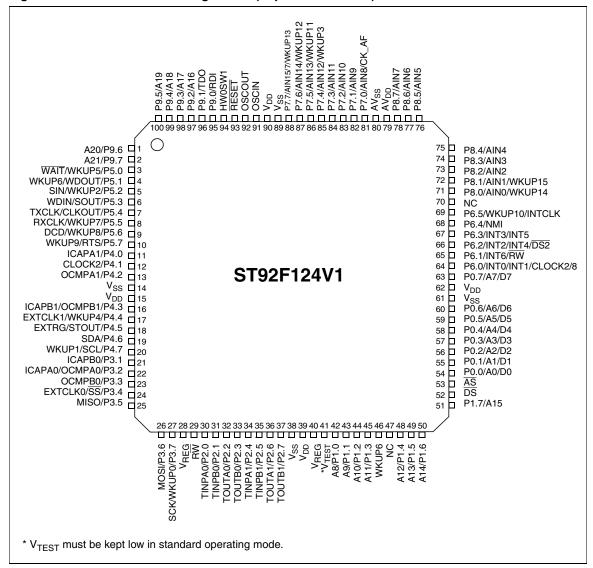

Figure 7. ST92F124V1: Pin Configuration (Top-view PQFP100)

Figure 8. ST92F124V1: Pin Configuration (Top-view TQFP100)

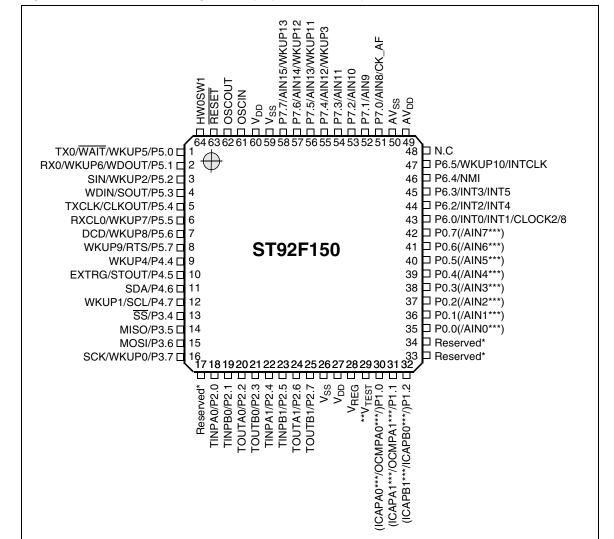

Figure 9. ST92F150: Pin Configuration (Top-view TQFP64)

<sup>\*</sup> Reserved for ST tests, must be left unconnected

<sup>\*\*</sup> V<sub>TEST</sub> must be kept low in standard operating mode.

<sup>\*\*\*</sup> Not emulated. Refer to Section 13.2 on page 418

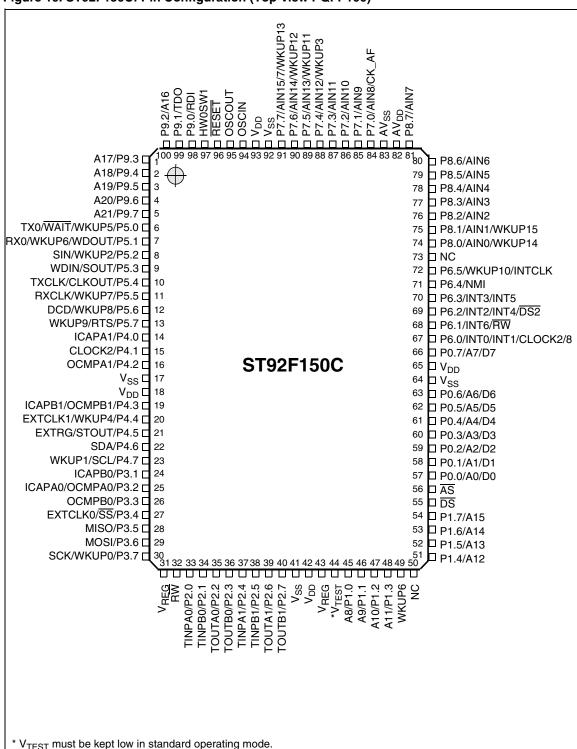

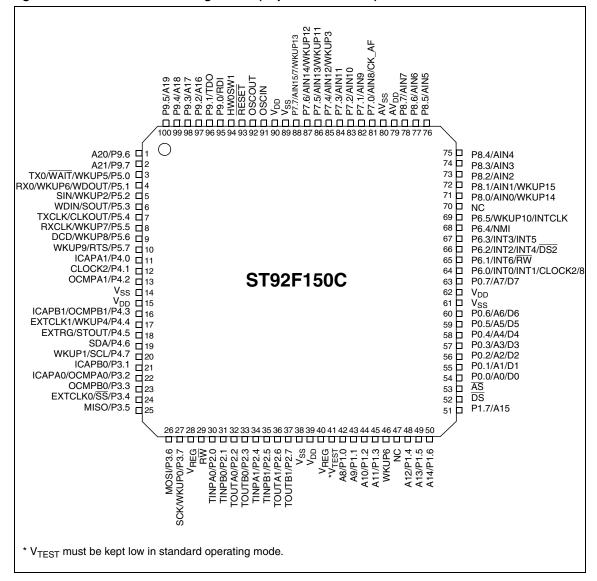

Figure 10. ST92F150C: Pin Configuration (Top-view PQFP100)

<u>577</u>

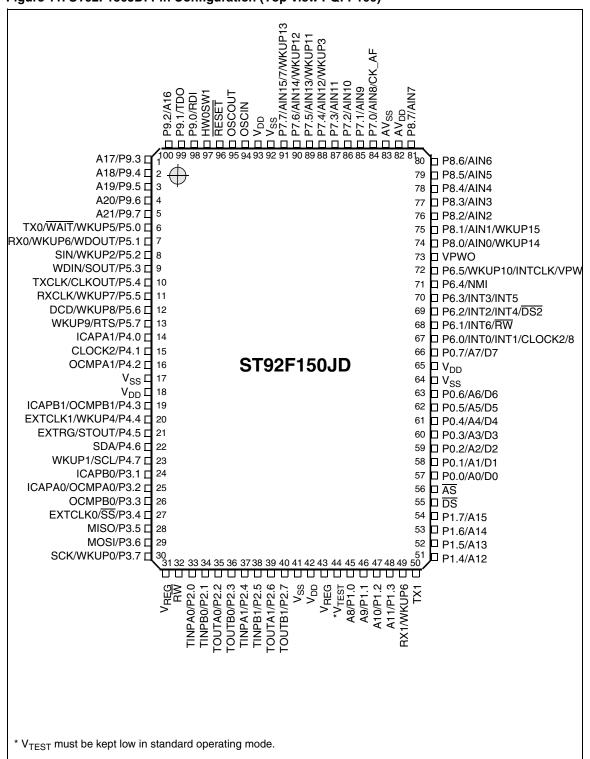

Figure 11. ST92F150JD: Pin Configuration (Top-view PQFP100)

Figure 12. ST92F150C: Pin Configuration (Top-view TQFP100)

**577**

\* V<sub>TEST</sub> must be kept low in standard operating mode.

P9.5/A19

P9.4/A18

P9.4/A18

P9.3/A17

P9.3/A17

P9.3/A17

P9.3/A17

P9.3/A16

P9.1/TDO

P9.0/RDI

HW0SW1

HW0SW1

HW0SW1

HW0SW1

COCOUT

OSCIN

VSD

VS

P7.3/AIN13/WKUP12

P7.5/AIN13/WKUP12

P7.5/AIN13/WKUP13

P7.5/AIN13/WKUP11

P7.4/AIN12/WKUP3

P7.5/AIN13/WKUP3

P7.5/AIN13/WKUP3

P7.5/AIN13/WKUP3

P7.5/AIN13/WKUP3

P7.5/AIN13/WKUP3

P7.5/AIN15/WKUP3

P7.5/AIN16

P7.1/AIN9

P7.1/AIN7

P8.5/AIN5 \_\_\_\_\_ 100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76 75 🗖 A20/P9.6 □ P8.4/AIN4 74 | 73 | A21/P9.7 🗖 2 P8.3/AIN3 P8.2/AIN2 72 P8.1/AIN1/WKUP15 71 | 70 | SIN/WKUP2/P5.2 5 P8.0/AIN0/WKUP14 WDIN/SOUT/P5.3 □6 VPWO TXCLK/CLKOUT/P5.4 G7 RXCLK/WKUP7/P5.5 G8 69 68 P6.5/WKUP10/INTCLK/VPW P6.4/NMI 67 | 66 | P6.3/INT3/INT5 P6.2/INT2/INT4/DS2 65 | 64 | P6.1/INT6/RW P6.0/INT0/INT1/CLOCK2/8 ST92F150JD P0.7/A7/D7  $V_{DD}$ V<sub>SS</sub> P0.6/A6/D6 P0.5/A5/D5 P0.4/A4/D4 P0.3/A3/D3 57 🗖 WKUP1/SCL/P4.7 20 P0 2/A2/D2 56 ICAPA0/OCMPA0/P3.2 22 P0.1/A1/D1 55 🗖 54 53 P0.0/A0/D0 AS DS 51 P1.7/A15 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 MOSI/P3.6 I SCK/WKUPO/P3.7 I VREG I TINPAO/P2.1 I TOUTAO/P2.2 I VBC I VBC I VBC I ASI/P1.3 I A10/P1.3 I A11/P1.3 I

Figure 13. ST92F150JD: Pin Configuration (Top-view TQFP100)

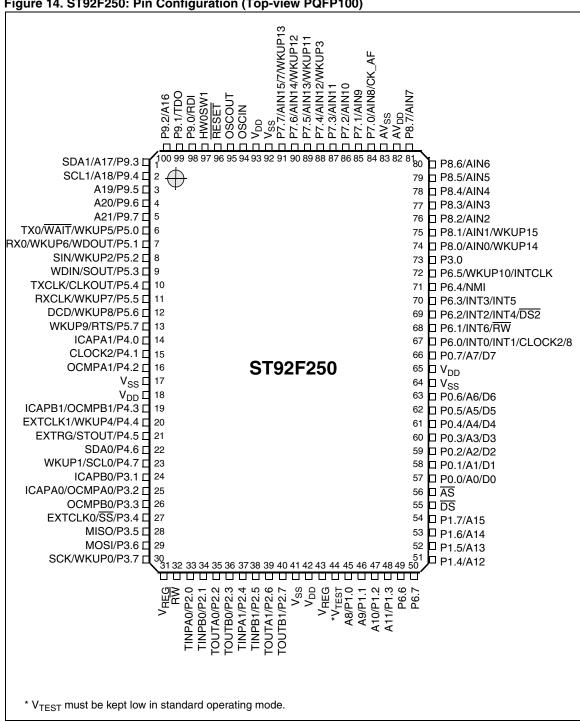

Figure 14. ST92F250: Pin Configuration (Top-view PQFP100)

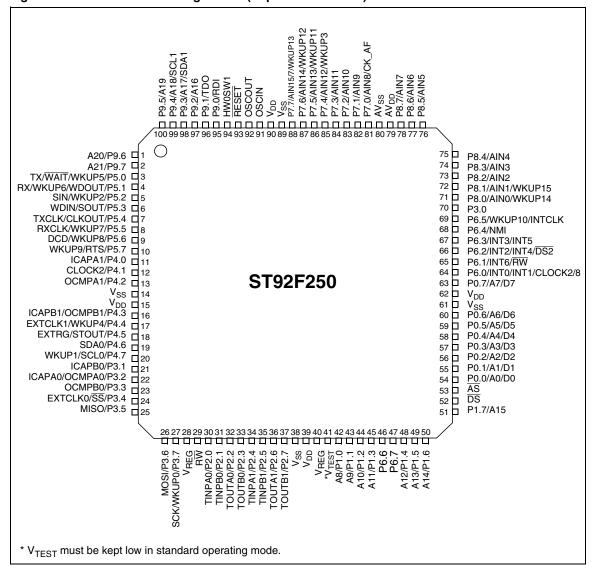

Figure 15. ST92F250: Pin Configuration (Top-view TQFP100)

Table 1. ST92F124/F150/F250 Power Supply Pins

| Name             | Function                                                  | TQFP64 | PQFP100  | TQFP100  |

|------------------|-----------------------------------------------------------|--------|----------|----------|

|                  |                                                           | -      | 18       | 15       |

| $V_{DD}$         | Main Power Supply Voltage                                 | 27     | 42       | 39       |

| <b>V</b> DD      | (Pins internally connected)                               | -      | 65       | 62       |

|                  |                                                           | 60     | 93       | 90       |

|                  |                                                           | -      | 17       | 14       |

| Voc              | Digital Circuit Ground                                    | 26     | 41       | 38       |

| $V_{SS}$         | (Pins internally connected)                               | -      | 64       | 61       |

|                  |                                                           | 59     | 92       | 89       |

| $AV_DD$          | Analog Circuit Supply Voltage                             | 49     | 82       | 79       |

| AV <sub>SS</sub> | Analog Circuit Ground                                     | 50     | 83       | 80       |

| $V_{TEST}$       | Must be kept low in standard operating mode               | 29     | 44       | 41       |

| V <sub>REG</sub> | Stabilization capacitor(s) for internal voltage regulator | 28     | 31<br>43 | 28<br>40 |

Table 2. ST92F124/F150/F250 Primary Function Pins

| Name                    | Function                                | TQFP64 | PQFP100 | TQFP100 |

|-------------------------|-----------------------------------------|--------|---------|---------|

| ĀS                      | Address Strobe                          | -      | 56      | 53      |

| DS                      | Data Strobe                             | -      | 55      | 52      |

| RW                      | Read/Write                              | -      | 32      | 29      |

| OSCIN                   | Crystal Oscillator Input                | 61     | 94      | 91      |

| OSCOUT                  | Crystal Oscillator Output               | 62     | 95      | 92      |

| RESET                   | Reset to initialize the Microcontroller | 63     | 96      | 93      |

| HW0SW1                  | Watchdog HW/SW enabling selection       | 64     | 97      | 94      |

| VPWO <sup>1)</sup>      | J1850 JBLPD Output                      | -      | 73      | 70      |

| RX1/WKUP6 <sup>1)</sup> | CAN1 Receive Data / Wake-up Line 6      | -      | 49      | 46      |

| TX1 <sup>1)</sup>       | CAN1 Transmit Data.                     | -      | 50      | 47      |

Note 1: ST92F150JDV1 only.

### 1.3 VOLTAGE REGULATOR

The internal Voltage Regulator (VR) is used to power the microcontroller starting from the external power supply. The VR comprises a Main voltage regulator and a Low-power regulator.

- The Main voltage regulator generates sufficient current for the microcontroller to operate in any mode. It has a static power consumption (300 µA typ.).

- The separate Low-Power regulator consumes less power is used only when the microcontroller is in Low Power mode. It has a different design from the main VR and generates a lower,

non-stabilized and non-thermally-compensated voltage sufficient for maintaining the data in RAM and the Register File.

For both the Main VR and the Low-Power VR, stabilization is achieved by an external capacitor, connected to one of the  $V_{REG}$  pins. The minimum recommended value is 300 nF, and care must be taken to minimize distance between the chip and the capacitor. Care should also be taken to limit the serial inductance to less than 60nH.

Figure 16. Recommended Connections for V<sub>REG</sub>

**IMPORTANT:** The V<sub>REG</sub> pin cannot be used to drive external devices.

Figure 17. Minimum Required Connections for V<sub>REG</sub>

**Note:** Pin 31 of PQFP100 or pin 28 of TQFP100 can be left unconnnected. A secondary stabilization network can also be connected to these pins.

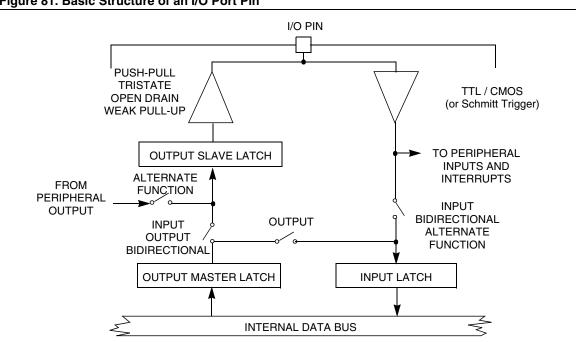

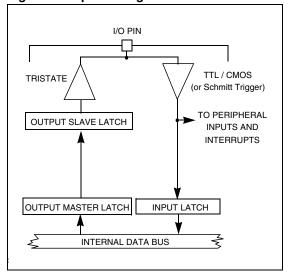

#### 1.4 I/O PORTS

Port 0, Port 1 and Port 9[7:2] provide the external memory interface. All the ports of the device can be programmed as Input/Output or in Input mode, compatible with TTL or CMOS levels (except where Schmitt Trigger is present). Each bit can be programmed individually (Refer to the I/O ports chapter).

### Internal Weak Pull-up

As shown in Table 3, not all input sections implement a Weak Pull-up. This means that the pull-up must be connected externally when the pin is not used or programmed as bidirectional.

### **TTL/CMOS Input**

For all those port bits where no input schmitt trigger is implemented, it is always possible to program the input level as TTL or CMOS compatible by programming the relevant PxC2.n control bit. Refer I/O Ports Chapter to the section titled "Input/Output Bit Configuration".

### Schmitt Trigger Input

Two different kinds of Schmitt Trigger circuitries are implemented: Standard and High Hysteresis. Standard Schmitt Trigger is widely used (see Ta-

ble 3), while the High Hysteresis Schmitt Trigger is present on ports P4[7:6] and P6[5:4].

All inputs which can be used for detecting interrupt events have been configured with a "Standard" Schmitt Trigger, apart from the NMI pin which implements the "High Hysteresis" version. In this way, all interrupt lines are guaranteed as "edge sensitive".

### **Push-Pull/OD Output**

The output buffer can be programmed as push-pull or open-drain: attention must be paid to the fact that the open-drain option corresponds only to a disabling of P-channel MOS transistor of the buffer itself: it is still present and physically connected to the pin. Consequently it is not possible to increase the output voltage on the pin over  $V_{DD}+0.3$  Volt, to avoid direct junction biasing.

### **Pure Open-Drain Output**

The user can increase the voltage on an I/O pin over  $V_{DD}+0.3$  Volt where the P-channel MOS transistor is physically absent: this is allowed on all "Pure Open Drain" pins. In this case, the push-pull option is not available and any weak pull-up must be implemented externally.

Table 3. I/O Port Characteristics

|                          | Input                           | Output       | Weak Pull-Up | Reset State       |

|--------------------------|---------------------------------|--------------|--------------|-------------------|

| Port 0[7:0]              | TTL/CMOS                        | Push-Pull/OD | No           | Bidirectional     |

| Port 1[7:0]              | TTL/CMOS                        | Push-Pull/OD | No           | Bidirectional     |

| Port 2[1:0]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 2[3:2]              | TTL/CMOS                        | Pure OD      | No           | Input CMOS        |

| Port 2[5:4]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 2[7:6]              | TTL/CMOS                        | Push-Pull/OD | Yes          | Input CMOS        |

| Port 3[2:0] 1)           | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 3.3                 | TTL/CMOS                        | Push-Pull/OD | Yes          | Input CMOS        |

| Port 3[7:4]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 4.0, Port 4.4       | Schmitt trigger                 | Push-Pull/OD | No           | Input             |

| Port 4.1                 | Schmitt trigger                 | Push-Pull/OD | Yes          | Bidirectional WPU |

| Port 4.2, Port 4.5       | TTL/CMOS                        | Push-Pull/OD | Yes          | Input CMOS        |

| Port 4.3                 | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 4[7:6]              | High hysteresis Schmitt trigger | Pure OD      | No           | Input             |

| Port 5[2:0], Port 5[7:4] | Schmitt trigger                 | Push-Pull/OD | No           | Input             |

| Port 5.3                 | TTL/CMOS                        | Push-Pull/OD | Yes          | Input CMOS        |

| Port 6[3:0]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 6[5:4]              | High hysteresis Schmitt trigger | Push-Pull/OD | Yes          | Input             |

| Port 6[7:6] 1)           | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 7[7:0]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 8[1:0]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Input             |

| Port 8[7:2]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Bidirectional WPU |

| Port 9[7:0]              | Schmitt trigger                 | Push-Pull/OD | Yes          | Bidirectional WPU |

**Legend:** WPU = Weak Pull-Up, OD = Open Drain.

Note 1: Port 3.0 and Port6 [7:6] present on ST92F250 version only.

### How to Configure the I/O Ports

To configure the I/O ports, use the information in Table 3, Table 4 and the Port Bit Configuration Table in the I/O Ports Chapter (See page 152).

**Input Note** = the hardware characteristics fixed for each port line in Table 3.

- If Input note = TTL/CMOS, either TTL or CMOS input level can be selected by software.

- If Input note = Schmitt trigger, selecting CMOS or TTL input by software has no effect, the input will always be Schmitt Trigger.

Alternate Functions (AF) = More than one AF cannot be assigned to an I/O pin at the same time:

An alternate function can be selected as follows.

### AF Inputs:

- AF is selected implicitly by enabling the corresponding peripheral. Exception to this are ADC inputs which must be explicitly selected as AF input by software.

AF Outputs or Bidirectional Lines:

- In the case of Outputs or I/Os, AF is selected explicitly by software.

## **Example 1: SCI-M input**

AF: SIN, Port: P5.2. Schmitt Trigger input.

Write the port configuration bits:

P5C2.2=1

P5C1.2=0

P5C0.2 =1

Enable the SCI peripheral by software as described in the SCI chapter.

### **Example 2: SCI-M output**

AF: SOUT, Port: P5.3, Push-Pull/OD output.

Write the port configuration bits (for AF OUT PP):

P5C2.3=0

P5C1.3=1

P5C0.3 =1

### Example 3: External Memory I/O

AF: A0/D0, Port: P0.0, Input Note: TTL/CMOS input.

Write the port configuration bits:

P0C2.0=1

P0C1.0=1

P0C0.0 = 1

### **Example 4: Analog input**

AF: AIN8, Port: 7.0, Analog input.

Write the port configuration bits: P7C2.0=1

P7C1.0=1

P7C0.0 =1

# 1.5 Alternate Functions for I/O Ports

All the ports in the following table are useable for general purpose I/O (input, output or bidirectional).

**Table 4. I/O Port Alternate Functions**

| Port | ort Pin No. |         |         | Alternate Functions  |     |                                  |  |

|------|-------------|---------|---------|----------------------|-----|----------------------------------|--|

| Name | TQFP64      | PQFP100 | TQFP100 |                      |     | Alternate Functions              |  |

| D0 0 | -           | 57      | 54      | A0/D0                | I/O | Address/Data bit 0               |  |

| P0.0 | 35          | -       | -       | AIN0 <sup>1)</sup>   | ı   | Analog Data Input 0              |  |

| P0.1 | -           | 58      | 55      | A1/D1                | I/O | Address/Data bit 1               |  |

| P0.1 | 36          | -       | -       | AIN1 <sup>1)</sup>   | 1   | Analog Data Input 1              |  |

| P0.2 | -           | 59      | 56      | A2/D2                | I/O | Address/Data bit 2               |  |

| PU.2 | 37          | -       | -       | AIN2 <sup>1)</sup>   | I   | Analog Data Input 2              |  |

| P0.3 | -           | 60      | 57      | A3/D3                | I/O | Address/Data bit 3               |  |

| F0.5 | 38          | -       | -       | AIN3 <sup>1)</sup>   | I   | Analog Data Input 3              |  |

| P0.4 | -           | 61      | 58      | A4/D4                | I/O | Address/Data bit 4               |  |

| FU.4 | 39          | -       | -       | AIN4 <sup>1)</sup>   | I   | Analog Data Input 4              |  |

| P0.5 | -           | 62      | 59      | A5/D5                | I/O | Address/Data bit 5               |  |

| F0.5 | 40          | -       | -       | AIN5 <sup>1)</sup>   | I   | Analog Data Input 5              |  |

| P0.6 | -           | 63      | 60      | A6/D6                | I/O | Address/Data bit 6               |  |

| FU.0 | 41          | -       | -       | AIN6 <sup>1)</sup>   | I   | Analog Data Input 6              |  |

| P0.7 | -           | 66      | 63      | A7/D7                | I/O | Address/Data bit 7               |  |

| PU.7 | 42          | -       | -       | AIN7 <sup>1)</sup>   | ı   | Analog Data Input 7              |  |

|      | -           | 45      | 42      | A8                   | I/O | Address bit 8                    |  |

| P1.0 | 30          | _       |         | ICAPA01)             | I   | Ext. Timer 0 - Input Capture A   |  |

|      | 30          | -       | -       | OCMPA0 <sup>1)</sup> | 0   | Ext. Timer 0 - Output Compare A  |  |

|      | -           | 46      | 43      | A9                   | I/O | Address bit 9                    |  |

| P1.1 | 31          |         |         | ICAPA1 <sup>1)</sup> | I   | Ext. Timer 1- Input Capture A    |  |

|      | 31          | -       | -       | OCMPA1 <sup>1)</sup> | 0   | Ext. Timer 1- Output Compare A   |  |

|      | -           | 47      | 44      | A10                  | I/O | Address bit 10                   |  |

| P1.2 | 32          | _       |         | ICAPB1 <sup>1)</sup> | I   | Ext. Timer 1- Input Capture B    |  |

|      | 32          | -       | -       | ICAPB0 <sup>1)</sup> | I   | Ext. Timer 0- Input Capture B    |  |

| P1.3 | -           | 48      | 45      | A11                  | I/O | Address bit 11                   |  |

| P1.4 | -           | 51      | 48      | A12                  | I/O | Address bit 12                   |  |

| P1.5 | -           | 52      | 49      | A13                  | I/O | Address bit 13                   |  |

| P1.6 | -           | 53      | 50      | A14                  | I/O | Address bit 14                   |  |

| P1.7 | -           | 54      | 51      | A15                  | I/O | Address bit 15                   |  |

| P2.0 | 18          | 33      | 30      | TINPA0               | 1   | Multifunction Timer 0 - Input A  |  |

| P2.1 | 19          | 34      | 31      | TINPB0               | Ι   | Multifunction Timer 0 - Input B  |  |

| P2.2 | 20          | 35      | 32      | TOUTA0               | 0   | Multifunction Timer 0 - Output A |  |

| P2.3 | 21          | 36      | 33      | TOUTB0               | 0   | Multifunction Timer 0 - Output B |  |

| P2.4 | 22          | 37      | 34      | TINPA1               | ı   | Multifunction Timer 1 - Input A  |  |

| Port               | Pin No. |         | Alternate Franctions |                   |     |                                      |

|--------------------|---------|---------|----------------------|-------------------|-----|--------------------------------------|

| Name               | TQFP64  | PQFP100 | TQFP100              |                   |     | Alternate Functions                  |

| P2.5               | 23      | 38      | 35                   | TINPB1            | I   | Multifunction Timer 1 - Input B      |

| P2.6               | 24      | 39      | 36                   | TOUTA1            | 0   | Multifunction Timer 1 - Output A     |

| P2.7               | 25      | 40      | 37                   | TOUTB1            | 0   | Multifunction Timer 1 - Output B     |

| P3.0 <sup>2)</sup> | -       | 73      | 70                   |                   |     |                                      |

| P3.1               | -       | 24      | 21                   | ICAPB0            | ı   | Ext. Timer 0 - Input Capture B       |

| P3.2               |         | 25      | 22                   | ICAPA0            | I   | Ext. Timer 0 - Input Capture A       |

| F3.2               | -       | 25      | 22                   | OCMPA0            | 0   | Ext. Timer 0 - Output Compare A      |

| P3.3               | =       | 26      | 23                   | OCMPB0            | 0   | Ext. Timer 0 - Output Compare B      |

| P3.4               |         | 27      | 24                   | EXTCLK0           | I   | Ext. Timer 0 - Input Clock           |

| F3.4               | -       | 21      | 24                   | SS                | I   | SPI - Slave Select                   |

| P3.5               | 14      | 28      | 25                   | MISO              | I/O | SPI - Master Input/Slave Output Data |

| P3.6               | 15      | 29      | 26                   | MOSI              | I/O | SPI - Master Output/Slave Input Data |

|                    |         |         |                      | SCK               | I   | SPI - Serial Input Clock             |

| P3.7               | 16      | 30      | 27                   | WKUP0             | I   | Wake-up Line 0                       |

|                    |         |         |                      | SCK               | 0   | SPI - Serial Output Clock            |

| P4.0               | -       | 14      | 11                   | ICAPA1            | ı   | Ext. Timer 1 - Input Capture A       |

| P4.1               | -       | 15      | 12                   | CLOCK2            | 0   | CLOCK2 internal signal               |

| P4.2               | -       | 16      | 13                   | OCMPA1            | 0   | Ext. Timer 1 - Output Compare A      |

| D4.0               |         | 40      |                      | ICAPB1            | ı   | Ext. Timer 1 - Input Capture B       |

| P4.3               | -       | 19      | 16                   | OCMPB1            | 0   | Ext. Timer 1 - Output Compare B      |

| P4.4               |         | 20      | 17                   | EXTCLK1           | I   | Ext. Timer 1 - Input Clock           |

| Г4.4               | -       | 20      | 17                   | WKUP4             | I   | Wake-up Line 4                       |

| P4.5               | 10      | 21      | 18                   | EXTRG             | I   | ADC Ext. Trigger                     |

| F4.5               | 10      | 21      | 10                   | STOUT             | 0   | Standard Timer Output                |

| P4.6               | 11      | 22      | 19                   | SDA0              | I/O | I <sup>2</sup> C 0 Data              |

| P4.7               | 12      | 23      | 20                   | WKUP1             | I   | Wake-up Line 1                       |

| Γ4.7               | 12      | 23      | 20                   | SCL0              | I/O | I <sup>2</sup> C 0 Clock             |

|                    |         |         |                      | WAIT              | I   | External Wait Request                |

| P5.0               | 1       | 6       | 3                    | WKUP5             | I   | Wake-up Line 5                       |

|                    |         |         |                      | TX0 <sup>2)</sup> | 0   | CAN 0 output                         |

|                    |         |         |                      | WKUP6             | I   | Wake-up Line 6                       |

| P5.1               | 2       | 7       | 4                    | RX0 <sup>2)</sup> | I   | CAN 0 input                          |

|                    |         |         |                      | WDOUT             | 0   | Watchdog Timer Output                |

| P5.2               | 3       | 8       | 5                    | SIN0              | ı   | SCI-M - Serial Data Input            |

| F 3.2              | ٥       | 0       | 3                    | WKUP2             | I   | Wake-up Line 2                       |

| P5.3               | 4       | 9       | 6                    | WDIN              | ı   | Watchdog Timer Input                 |

| F 3.3              | +       | 9       | U                    | SOUT              | 0   | SCI-M - Serial Data Output           |

# ST92F124/F150/F250 - GENERAL DESCRIPTION

| Port               | t Pin No. |          | Alternate Functions |                     |   |                              |

|--------------------|-----------|----------|---------------------|---------------------|---|------------------------------|

| Name               | TQFP64    | PQFP100  | TQFP100             | Alternate Functions |   |                              |

| DE 4               | -         | 10       | 7                   | TXCLK               | I | SCI-M - Transmit Clock Input |

| P5.4               | 5         | 10       | 7                   | CLKOUT              | 0 | SCI-M - Clock Output         |

| Dr.c               |           | 4.4      | 0                   | RXCLK               | I | SCI-M - Receive Clock Input  |

| P5.5               | P5.5 6 11 | 11       | 8                   | WKUP7               | I | Wake-up Line 7               |

| DE 6               | 7         | 10       | 9                   | DCD                 | I | SCI-M - Data Carrier Detect  |

| P5.6               | 7         | 12       | 9                   | WKUP8               | I | Wake-up Line 8               |

| DE 7               | 0         | 10       | 10                  | WKUP9               | I | Wake-up Line 9               |

| P5.7               | 8         | 13       | 10                  | RTS                 | 0 | SCI-M - Request To Send      |

|                    |           |          |                     | INT0                | I | External Interrupt 0         |

| P6.0               | 43        | 67       | 64                  | INT1                | I | External Interrupt 1         |

|                    |           |          |                     | CLOCK2/8            | 0 | CLOCK2 divided by 8          |

| P6.1               |           | 60       | GE                  | INT6                | I | External Interrupt 6         |

| P6.1               | -         | 68       | 65                  | R₩                  | 0 | Read/Write                   |

|                    |           |          |                     | INT2                | I | External Interrupt 2         |

| P6.2               | 44        | 69       | 66                  | INT4                | I | External Interrupt 4         |

|                    |           |          |                     | DS2                 | 0 | Data Strobe 2                |

| De a               | 45        | 70       | 67                  | INT3                | I | External Interrupt 3         |

| P6.3               | 45        | 70       |                     | INT5                | I | External Interrupt 5         |

| P6.4               | 46        | 71       | 68                  | NMI                 | I | Non Maskable Interrupt       |

|                    |           |          |                     | WKUP10              | I | Wake-up Line 10              |

| P6.5               | 47        | 72       | 69                  | VPWI <sup>2)</sup>  | I | JBLPD input                  |

|                    |           |          |                     | INTCLK              | 0 | Internal Main Clock          |

| P6.6 <sup>2)</sup> | -         | 49       | 46                  |                     |   |                              |

| P6.7 <sup>2)</sup> | -         | 50       | 47                  |                     |   |                              |

|                    |           |          |                     | AIN8                | 1 | Analog Data Input 8          |

| P7.0               | 51        | 84       | 81                  | CK_AF               | ı | Clock Alternative Source     |

| P7.1               | 52        | 85       | 82                  | AIN9                | ı | Analog Data Input 9          |

| P7.2               | 53        | 86       | 83                  | AIN10               | I | Analog Data Input 10         |

| P7.3               | 54        | 87       | 84                  | AIN11               | ı | Analog Data Input 11         |

|                    |           |          |                     | WKUP3               | I | Wake-up Line 3               |

| P7.4               | 55        | 88       | 85                  | AIN12               | I | Analog Data Input 12         |

|                    |           |          | _                   | AIN13               | I | Analog Data Input 13         |

| P7.5               | 56        | 89       | 86                  | WKUP11              | ı | Wake-up Line 11              |

|                    |           | 57 90 87 |                     | AIN14               | I | Analog Data Input14          |

| P7.6               | 57        |          | 87                  | WKUP12              | I | Wake-up Line 12              |

| D7 -               | 50        | 0.       | 00                  | AIN15               | I | Analog Data Input 15         |

| P7.7               | 58        | 91       | 88                  | WKUP13              | ı | Wake-up Line 13              |

## ST92F124/F150/F250 - GENERAL DESCRIPTION

| Port  |        | Pin No. |         |                    |     | Alternate Functions        |  |

|-------|--------|---------|---------|--------------------|-----|----------------------------|--|

| Name  | TQFP64 | PQFP100 | TQFP100 |                    |     |                            |  |

| P8.0  |        | 74      | 71      | AIN0               | I   | Analog Data Input 0        |  |

| F6.0  | -      | 74      | / 1     | WKUP14             | I   | Wake-up Line 14            |  |

| P8.1  | _      | 75      | 72      | AIN1               | I   | Analog Data Input 1        |  |

| F0.1  | -      | 75      | 12      | WKUP15             | I   | Wake-up Line 15            |  |

| P8.2  | -      | 76      | 73      | AIN2               | I   | Analog Data Input 2        |  |

| P8.3  | -      | 77      | 74      | AIN3               | I   | Analog Data Input 3        |  |

| P8.4  | -      | 78      | 75      | AIN4               | I   | Analog Data Input 4        |  |

| P8.5  | -      | 79      | 76      | AIN5               | I   | Analog Data Input 5        |  |

| P8.6  | -      | 80      | 77      | AIN6               | I   | Analog Data Input 6        |  |

| P8.7  | -      | 81      | 78      | AIN7               | I   | Analog Data Input 7        |  |

| P9.0  | -      | 98      | 95      | RDI <sup>2)</sup>  | I   | SCI-A Receive Data Input   |  |

| P9.1  | -      | 99      | 96      | TDO <sup>2)</sup>  | 0   | SCI-A Transmit Data Output |  |

| P9.2  | -      | 100     | 97      | A16                | 0   | Address bit 16             |  |

| P9.3  |        | 1       | 98      | A17 <sup>3)</sup>  | 0   | Address bit 17             |  |

| F9.3  | -      | ļ       | 90      | SDA1 <sup>2)</sup> | I/O | I <sup>2</sup> C 1 Data    |  |

| P9.4  |        | 2       | 99      | A18 <sup>3)</sup>  | 0   | Address bit 18             |  |

| F 9.4 | -      | - 2     | 99      | SCL1 <sup>2)</sup> | I/O | I <sup>2</sup> C 1 Clock   |  |

| P9.5  | -      | 3       | 100     | A19                | 0   | Address bit 19             |  |

| P9.6  | -      | 4       | 1       | A20                | 0   | Address bit 20             |  |

| P9.7  | -      | 5       | 2       | A21                | 0   | Address bit 21             |  |

**Note1:** The ST92F150-EMU2 emulator does not emulate ADC channels from AIN0 to AIN7 and extended function timers because they are not implemented on the emulator chip. See also Section 13.2 on page 418.

Note 2: Available on some devices only.

**Note 3:** For the ST92F250 device, since A[18:17] share the same pins as SDA1 and SCL1 of  $I^2C_1$ , these address bits are not available when the  $I^2C_1$  is in use (when I2CCR.PE bit is set).

### 1.6 OPERATING MODES

To optimize the performance versus the power consumption of the device, the ST92F124/F150/F250 supports different operating modes that can be dynamically selected depending on the performance and functionality requirements of the application at a given moment.

**RUN MODE**: This is the full speed execution mode with CPU and peripherals running at the maximum clock speed delivered by the Phase Locked Loop (PLL) of the Clock Control Unit (CCU).

**SLOW MODE**: Power consumption can be significantly reduced by running the CPU and the peripherals at reduced clock speed using the CPU Prescaler and CCU Clock Divider.

WAIT FOR INTERRUPT MODE: The Wait For Interrupt (WFI) instruction suspends program execution until an interrupt request is acknowledged. During WFI, the CPU clock is halted while the peripheral and interrupt controller keep running at a frequency depending on the CCU programming.

**LOW POWER WAIT FOR INTERRUPT MODE:** Combining SLOW mode and Wait For Interrupt mode it is possible to reduce the power consumption by more than 80%.

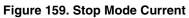

**STOP MODE**: When the STOP is requested by executing the STOP bit writing sequence (see dedicated section on Wake-up Management Unit paragraph), and if NMI is kept low, the CPU and the peripherals stop operating. Operations resume after a wake-up line is activated (16 wake-up lines plus NMI pin). See the RCCU and Wake-up Man-

agement Unit paragraphs in the following for the details. The difference with the HALT mode consists in the way the CPU exits this state: when the STOP is executed, the status of the registers is recorded, and when the system exits from the STOP mode the CPU continues the execution with the same status, without a system reset.

When the MCU enters STOP mode the Watchdog stops counting. After the MCU exits from STOP mode, the Watchdog resumes counting from where it left off.

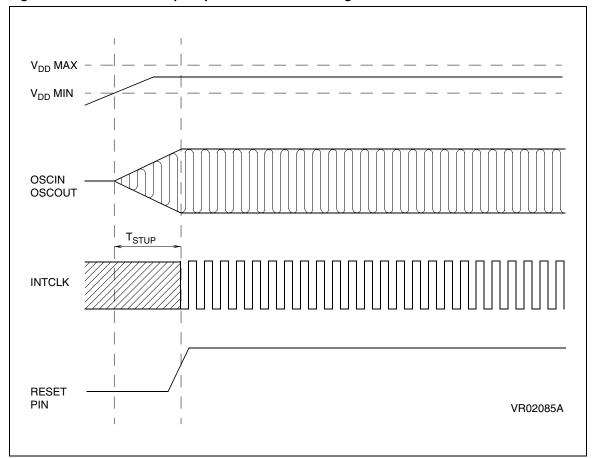

When the MCU exits from STOP mode, the oscillator, which was sleeping too, requires about 5 ms to restart working properly (at a 4 MHz oscillator frequency). An internal counter is present to guarantee that all operations after exiting STOP Mode, take place with the clock stabilised.

The counter is active only when the oscillation has already taken place. This means that 1-2 ms must be added to take into account the first phase of the oscillator restart.

In STOP mode, the oscillator is stopped. Therefore, if the PLL is used to provide the CPU clock before entering STOP mode, it will have to be selected again when the MCU exits STOP mode.

**HALT MODE**: When executing the HALT instruction, and if the Watchdog is not enabled, the CPU and its peripherals stop operating and the status of the machine remains frozen (the clock is also stopped). A reset is necessary to exit from Halt mode.

### 2 DEVICE ARCHITECTURE

### 2.1 CORE ARCHITECTURE

The ST9 Core or Central Processing Unit (CPU) features a highly optimised instruction set, capable of handling bit, byte (8-bit) and word (16-bit) data, as well as BCD and Boolean formats; 14 addressing modes are available.

Four independent buses are controlled by the Core: a 16-bit Memory bus, an 8-bit Register data bus, an 8-bit Register address bus and a 6-bit Interrupt/DMA bus which connects the interrupt and DMA controllers in the on-chip peripherals with the Core.

This multiple bus architecture affords a high degree of pipelining and parallel operation, thus making the ST9 family devices highly efficient, both for numerical calculation, data handling and with regard to communication with on-chip peripheral resources.

### 2.2 MEMORY SPACES

There are two separate memory spaces:

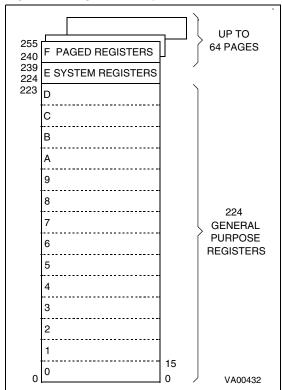

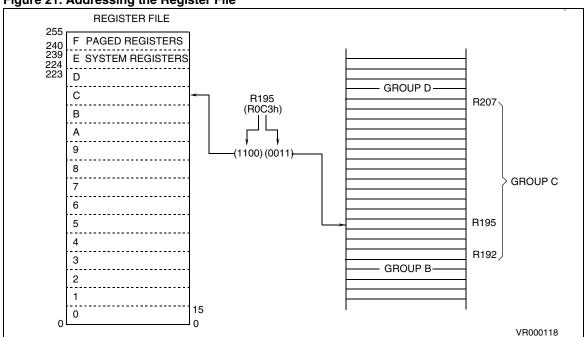

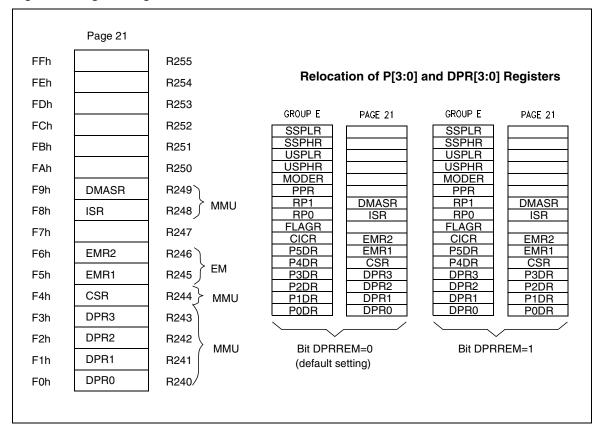

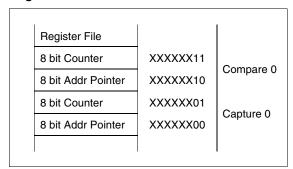

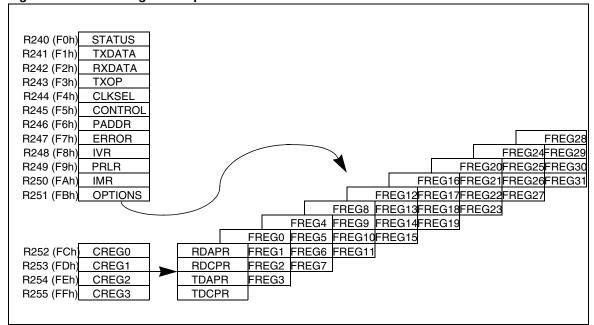

The Register File, which comprises 240 8-bit registers, arranged as 15 groups (Group 0 to E), each containing sixteen 8-bit registers plus up to 64 pages of 16 registers mapped in Group F, which hold data and control bits for the on-chip peripherals and I/Os.

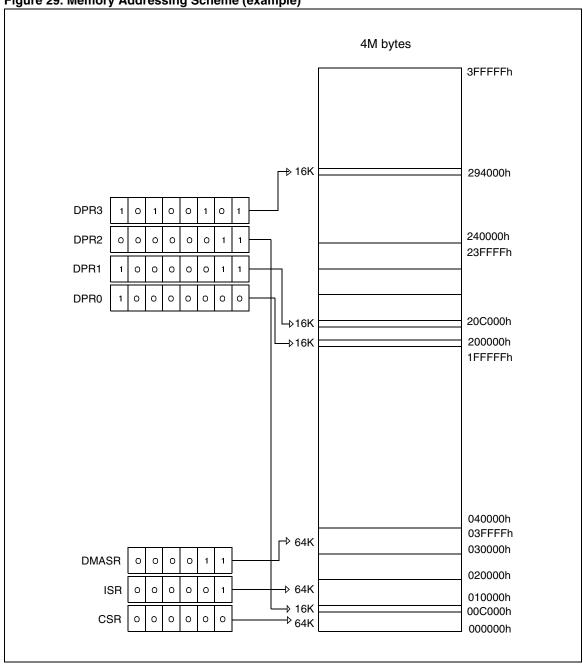

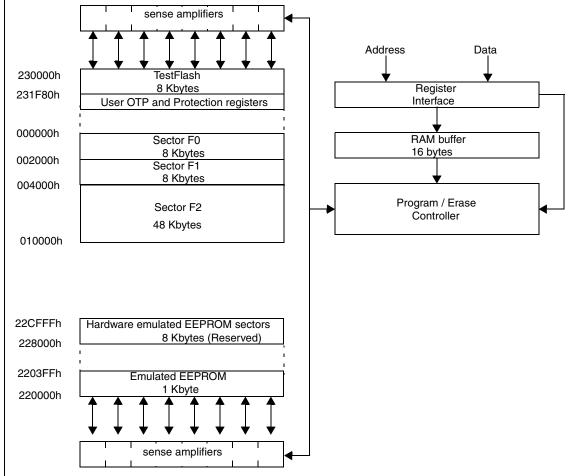

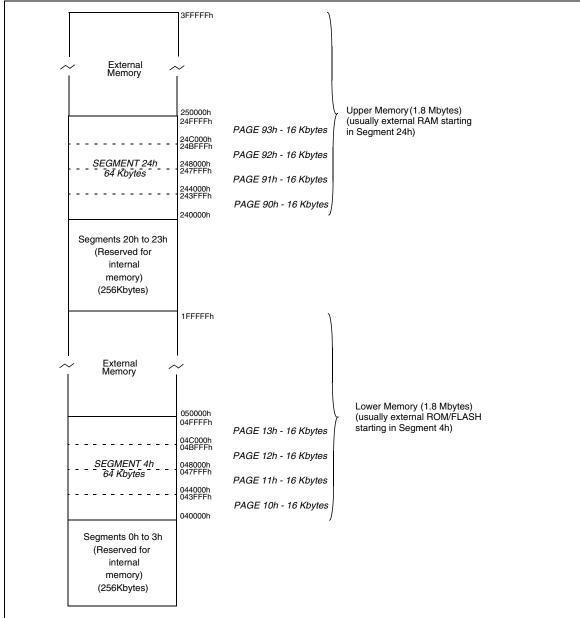

A single linear memory space accommodating both program and data. All of the physically separate memory areas, including the internal ROM, internal RAM and external memory are mapped in this common address space. The total addressable memory space of 4 Mbytes (limited by the size of on-chip memory and the number of external address pins) is arranged as 64 segments of 64 Kbytes. Each segment is further subdivided into four pages of 16 Kbytes, as illustrated in Figure 18. A Memory Management Unit uses a set of pointer registers to address a 22-bit memory field using 16-bit address-based instructions.

### 2.2.1 Register File

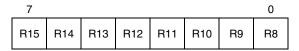

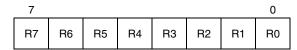

The Register File consists of (see Figure 19):

- 224 general purpose registers (Group 0 to D, registers R0 to R223)

- 6 system registers in the System Group (Group E, registers R224 to R239)

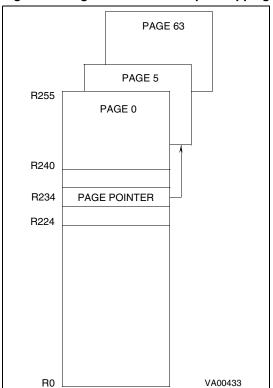

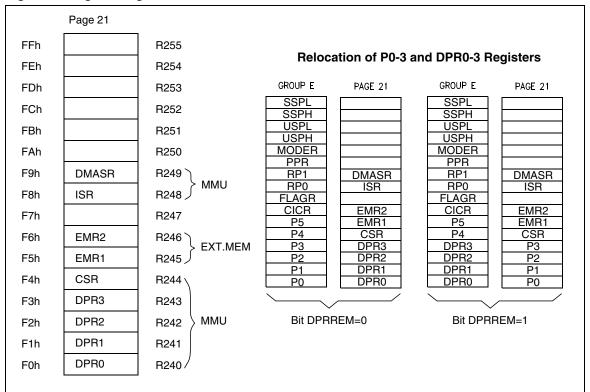

- Up to 64 pages, depending on device configuration, each containing up to 16 registers, mapped to Group F (R240 to R255), see Figure 20.

Data Code **Address** 16K Pages 64K Segments 3FFFFFh 254 63 253 3F0000h 252 3EFFFFh 250 62 249 3E0000h 247 up to 4 Mbytes 21FFFFh 134 Reserved 33 210000h 20FFFFh 02FFFFh 10 2 020000h 01FFFFh 1 010000h 00FFFFh 0 000000h

Figure 18. Single Program and Data Memory Address Space

## **MEMORY SPACES** (Cont'd)

Figure 19. Register Groups

Figure 20. Page Pointer for Group F mapping

Figure 21. Addressing the Register File

### **MEMORY SPACES** (Cont'd)

### 2.2.2 Register Addressing

Register File registers, including Group F paged registers (but excluding Group D), may be addressed explicitly by means of a decimal, hexadecimal or binary address; thus R231, RE7h and R11100111b represent the same register (see Figure 21). Group D registers can only be addressed in Working Register mode.

Note that an upper case "R" is used to denote this direct addressing mode.

# **Working Registers**

Certain types of instruction require that registers be specified in the form "rx", where x is in the range 0 to 15: these are known as Working Registers.

Note that a lower case "r" is used to denote this indirect addressing mode.

Two addressing schemes are available: a single group of 16 working registers, or two separately mapped groups, each consisting of 8 working registers. These groups may be mapped starting at any 8 or 16 byte boundary in the register file by means of dedicated pointer registers. This technique is described in more detail in Section 2.3.3 Register Pointing Techniques, and illustrated in Figure 22 and in Figure 23.

## **System Registers**

The 16 registers in Group E (R224 to R239) are System registers and may be addressed using any of the register addressing modes. These registers are described in greater detail in Section 2.3 SYSTEM REGISTERS.

### **Paged Registers**

Up to 64 pages, each containing 16 registers, may be mapped to Group F. These are addressed using any register addressing mode, in conjunction with the Page Pointer register, R234, which is one of the System registers. This register selects the page to be mapped to Group F and, once set, does not need to be changed if two or more registers on the same page are to be addressed in succession.

Therefore if the Page Pointer, R234, is set to 5, the instructions:

spp #5 1d R242, r4

will load the contents of working register r4 into the third register of page 5 (R242).

These paged registers hold data and control information relating to the on-chip peripherals, each peripheral always being associated with the same pages and registers to ensure code compatibility between ST9 devices. The number of these registers therefore depends on the peripherals which are present in the specific ST9 family device. In other words, pages only exist if the relevant peripheral is present.

**Table 5. Register File Organization**

| Hex.<br>Address | Decimal<br>Address | Function            | Register<br>File Group |

|-----------------|--------------------|---------------------|------------------------|

| F0-FF           | 240-255            | Paged<br>Registers  | Group F                |

| E0-EF           | 224-239            | System<br>Registers | Group E                |

| D0-DF           | 208-223            |                     | Group D                |

| C0-CF           | 192-207            |                     | Group C                |

| B0-BF           | 176-191            |                     | Group B                |

| A0-AF           | 160-175            |                     | Group A                |

| 90-9F           | 144-159            |                     | Group 9                |

| 80-8F           | 128-143            |                     | Group 8                |

| 70-7F           | 112-127            | General<br>Purpose  | Group 7                |

| 60-6F           | 96-111             | Registers           | Group 6                |

| 50-5F           | 80-95              | 3                   | Group 5                |

| 40-4F           | 64-79              |                     | Group 4                |

| 30-3F           | 48-63              |                     | Group 3                |

| 20-2F           | 32-47              |                     | Group 2                |

| 10-1F           | 16-31              |                     | Group 1                |

| 00-0F           | 00-15              |                     | Group 0                |

### 2.3 SYSTEM REGISTERS

The System registers are listed in Table 6. They are used to perform all the important system settings. Their purpose is described in the following pages. Refer to the chapter dealing with I/O for a description of the PORT[5:0] Data registers.

Table 6. System Registers (Group E)

| R239 (EFh) | SSPLR                 |

|------------|-----------------------|

| R238 (EEh) | SSPHR                 |

| R237 (EDh) | USPLR                 |

| R236 (ECh) | USPHR                 |

| R235 (EBh) | MODE REGISTER         |

| R234 (EAh) | PAGE POINTER REGISTER |

| R233 (E9h) | REGISTER POINTER 1    |

| R232 (E8h) | REGISTER POINTER 0    |

| R231 (E7h) | FLAG REGISTER         |

| R230 (E6h) | CENTRAL INT. CNTL REG |

| R229 (E5h) | PORT5 DATA REG.       |

| R228 (E4h) | PORT4 DATA REG.       |

| R227 (E3h) | PORT3 DATA REG.       |

| R226 (E2h) | PORT2 DATA REG.       |

| R225 (E1h) | PORT1 DATA REG.       |

| R224 (E0h) | PORT0 DATA REG.       |

### 2.3.1 Central Interrupt Control Register

Please refer to the "INTERRUPT" chapter for a detailed description of the ST9 interrupt philosophy.

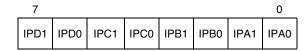

# CENTRAL INTERRUPT CONTROL REGISTER (CICR)

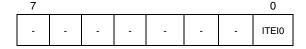

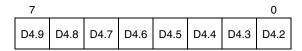

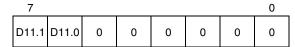

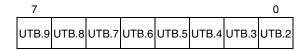

R230 - Read/Write

Register Group: E (System) Reset Value: 1000 0111 (87h)

| 7        | 7    |     |     |     |      |      |      |  |

|----------|------|-----|-----|-----|------|------|------|--|

| GCE<br>N | TLIP | TLI | IEN | IAM | CPL2 | CPL1 | CPL0 |  |

Bit 7 = **GCEN**: *Global Counter Enable*.

This bit is the Global Counter Enable of the Multifunction Timers. The GCEN bit is ANDed with the CE bit in the TCR Register (only in devices featuring the MFT Multifunction Timer) in order to enable the Timers when both bits are set. This bit is set after the Reset cycle. **Note:** If an MFT is not included in the ST9 device, then this bit has no effect.

Bit 6 = **TLIP**: Top Level Interrupt Pending.

This bit is set by hardware when a Top Level Interrupt Request is recognized. This bit can also be set by software to simulate a Top Level Interrupt Request.

- 0: No Top Level Interrupt pending

- 1: Top Level Interrupt pending

Bit 5 = **TLI**: *Top Level Interrupt bit*.

- 0: Top Level Interrupt is acknowledged depending on the TLNM bit in the NICR Register.

- 1: Top Level Interrupt is acknowledged depending on the IEN and TLNM bits in the NICR Register (described in the Interrupt chapter).

Bit 4 = **IEN**: Interrupt Enable.

This bit is cleared by interrupt acknowledgement, and set by interrupt return (iret). IEN is modified implicitly by iret, ei and di instructions or by an interrupt acknowledge cycle. It can also be explicitly written by the user, but only when no interrupt is pending. Therefore, the user should execute a di instruction (or guarantee by other means that no interrupt request can arrive) before any write operation to the CICR register.

- 0: Disable all interrupts except Top Level Interrupt.

- 1: Enable Interrupts

Bit 3 = IAM: Interrupt Arbitration Mode.

This bit is set and cleared by software to select the arbitration mode.

- 0: Concurrent Mode

- 1: Nested Mode.

Bits 2:0 = CPL[2:0]: Current Priority Level.

These three bits record the priority level of the routine currently running (i.e. the Current Priority Level, CPL). The highest priority level is represented by 000, and the lowest by 111. The CPL bits can be set by hardware or software and provide the reference according to which subsequent interrupts are either left pending or are allowed to interrupt the current interrupt service routine. When the current interrupt is replaced by one of a higher priority, the current priority value is automatically stored until required in the NICR register.

### SYSTEM REGISTERS (Cont'd)

### 2.3.2 Flag Register

The Flag Register contains 8 flags which indicate the CPU status. During an interrupt, the flag register is automatically stored in the system stack area and recalled at the end of the interrupt service routine, thus returning the CPU to its original status.

This occurs for all interrupts and, when operating in nested mode, up to seven versions of the flag register may be stored.

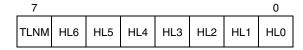

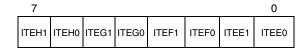

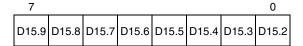

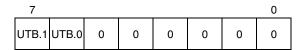

# **FLAG REGISTER (FLAGR)**

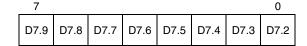

R231- Read/Write

Register Group: E (System) Reset value: 0000 0000 (00h)

| 7 |   |   |   |    |   |   | 0  |

|---|---|---|---|----|---|---|----|

| С | Z | S | ٧ | DA | Н | - | DP |

Bit 7 = **C**: Carry Flag.

The carry flag is affected by:

Addition (add, addw, adc, adcw),

Subtraction (sub, subw, sbc, sbcw),

Compare (cp, cpw),

Shift Right Arithmetic (sra, sraw),

Shift Left Arithmetic (sla, slaw),

Swap Nibbles (swap),

Rotate (rrc, rrcw, rlc, rlcw, ror, rol),

Decimal Adjust (da),

Multiply and Divide (mul, div, divws).

When set, it generally indicates a carry out of the most significant bit position of the register being used as an accumulator (bit 7 for byte operations and bit 15 for word operations).

The carry flag can be set by the Set Carry Flag (scf) instruction, cleared by the Reset Carry Flag (rcf) instruction, and complemented by the Complement Carry Flag (ccf) instruction.

### Bit 6 = **Z**: Zero Flag. The Zero flag is affected by:

```

Addition (add, addw, adc, adcw),

Subtraction (sub, subw, sbc, sbcw),

Compare (cp, cpw),

Shift Right Arithmetic (sra, sraw),

Shift Left Arithmetic (sla, slaw),

Swap Nibbles (swap),

Rotate (rrc, rrcw, rlc, rlcw, ror,

rol),

Decimal Adjust (da),

Multiply and Divide (mul, div, divws),

Logical (and, andw, or, orw, xor,

xorw, cpl).

```

Increment and Decrement (inc, incw, dec,

```

decw),

Test(tm, tmw, tcm, tcmw, btset).

```

In most cases, the Zero flag is set when the contents of the register being used as an accumulator become zero, following one of the above operations.

Bit 5 = S: Sign Flag.

The Sign flag is affected by the same instructions as the Zero flag.

The Sign flag is set when bit 7 (for a byte operation) or bit 15 (for a word operation) of the register used as an accumulator is one.

Bit  $4 = \mathbf{V}$ : Overflow Flag.

The Overflow flag is affected by the same instructions as the Zero and Sign flags.

When set, the Overflow flag indicates that a two'scomplement number, in a result register, is in error, since it has exceeded the largest (or is less than the smallest), number that can be represented in two's-complement notation.

Bit 3 = **DA**: Decimal Adjust Flag.

The DA flag is used for BCD arithmetic. Since the algorithm for correcting BCD operations is different for addition and subtraction, this flag is used to specify which type of instruction was executed last, so that the subsequent Decimal Adjust (da) operation can perform its function correctly. The DA flag cannot normally be used as a test condition by the programmer.

### Bit 2 = **H**: Half Carry Flag.

The H flag indicates a carry out of (or a borrow into) bit 3, as the result of adding or subtracting two 8-bit bytes, each representing two BCD digits. The H flag is used by the Decimal Adjust (da) instruction to convert the binary result of a previous addition or subtraction into the correct BCD result. Like the DA flag, this flag is not normally accessed by the user.

Bit 1 = Reserved bit (must be 0).

### Bit 0 = **DP**: Data/Program Memory Flag.

This bit indicates the memory area addressed. Its value is affected by the Set Data Memory (sdm) and Set Program Memory (spm) instructions. Refer to the Memory Management Unit for further details.

### SYSTEM REGISTERS (Cont'd)

If the bit is set, data is accessed using the Data Pointers (DPRs registers), otherwise it is pointed to by the Code Pointer (CSR register); therefore, the user initialization routine must include a Sdm instruction. Note that code is always pointed to by the Code Pointer (CSR).

**Note:** In the current ST9 devices, the DP flag is only for compatibility with software developed for the first generation of ST9 devices. With the single memory addressing space, its use is now redundant. It must be kept to 1 with a Sdm instruction at the beginning of the program to ensure a normal use of the different memory pointers.

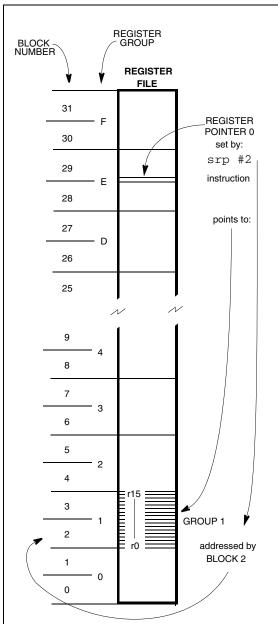

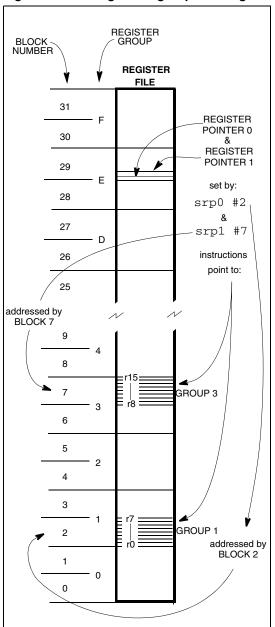

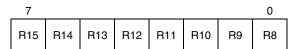

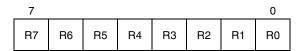

### 2.3.3 Register Pointing Techniques

Two registers within the System register group, are used as pointers to the working registers. Register Pointer 0 (R232) may be used on its own as a single pointer to a 16-register working space, or in conjunction with Register Pointer 1 (R233), to point to two separate 8-register spaces.

For the purpose of register pointing, the 16 register groups of the register file are subdivided into 32 8-register blocks. The values specified with the Set Register Pointer instructions refer to the blocks to be pointed to in twin 8-register mode, or to the lower 8-register block location in single 16-register mode.

The Set Register Pointer instructions srp, srp0 and srp1 automatically inform the CPU whether the Register File is to operate in single 16-register mode or in twin 8-register mode. The srp instruction selects the single 16-register group mode and

specifies the location of the lower 8-register block, while the srp0 and srp1 instructions automatically select the twin 8-register group mode and specify the locations of each 8-register block.

There is no limitation on the order or position of these register groups, other than that they must start on an 8-register boundary in twin 8-register mode, or on a 16-register boundary in single 16register mode.

The block number should always be an even number in single 16-register mode. The 16-register group will always start at the block whose number is the nearest even number equal to or lower than the block number specified in the srp instruction. Avoid using odd block numbers, since this can be confusing if twin mode is subsequently selected.

#### Thus:

srp #3 will be interpreted as srp #2 and will allow using R16 ..R31 as r0 .. r15.

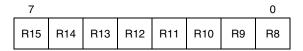

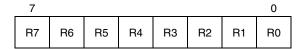

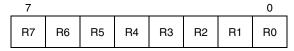

In single 16-register mode, the working registers are referred to as r0 to r15. In twin 8-register mode, registers r0 to r7 are in the block pointed to by RP0 (by means of the srp0 instruction), while registers r8 to r15 are in the block pointed to by RP1 (by means of the srp1 instruction).

**Caution**: Group D registers can only be accessed as working registers using the Register Pointers, or by means of the Stack Pointers. They cannot be addressed explicitly in the form "RXXX".

**577**

# SYSTEM REGISTERS (Cont'd)

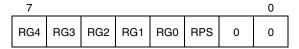

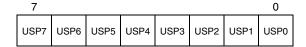

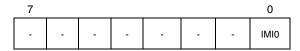

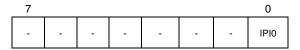

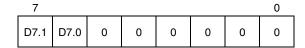

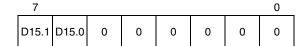

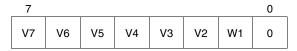

## POINTER 0 REGISTER (RP0)

R232 - Read/Write

Register Group: E (System) Reset Value: xxxx xx00 (xxh)

| 7   |     |     |     |     |     |   |   |

|-----|-----|-----|-----|-----|-----|---|---|

| RG4 | RG3 | RG2 | RG1 | RG0 | RPS | 0 | 0 |

### Bits 7:3 = **RG[4:0]**: Register Group number.

These bits contain the number (in the range 0 to 31) of the register block specified in the srp0 or srp instructions. In single 16-register mode the number indicates the lower of the two 8-register blocks to which the 16 working registers are to be mapped, while in twin 8-register mode it indicates the 8-register block to which r0 to r7 are to be mapped.

### Bit 2 = **RPS**: Register Pointer Selector.

This bit is set by the instructions  $\mathtt{srp0}$  and  $\mathtt{srp1}$  to indicate that the twin register pointing mode is selected. The bit is reset by the  $\mathtt{srp}$  instruction to indicate that the single register pointing mode is selected.

0: Single register pointing mode1: Twin register pointing mode

0 . 0

Bits 1:0: Reserved. Forced by hardware to zero.

### **POINTER 1 REGISTER (RP1)**

R233 - Read/Write

Register Group: E (System) Reset Value: xxxx xx00 (xxh)

This register is only used in the twin register pointing mode. When using the single register pointing mode, or when using only one of the twin register groups, the RP1 register must be considered as RESERVED and may NOT be used as a general purpose register.

Bits  $7:3 = \mathbf{RG[4:0]}$ : Register Group number. These bits contain the number (in the range 0 to 31) of the 8-register block specified in the srp1 instruction, to which r8 to r15 are to be mapped.

### Bit 2 = **RPS**: Register Pointer Selector.

This bit is set by the srp0 and srp1 instructions to indicate that the twin register pointing mode is selected. The bit is reset by the srp instruction to indicate that the single register pointing mode is selected.

0: Single register pointing mode

1: Twin register pointing mode

Bits 1:0: Reserved. Forced by hardware to zero.

#### SYSTEM REGISTERS (Cont'd)

Figure 22. Pointing to a single group of 16 registers

Figure 23. Pointing to two groups of 8 registers

#### **SYSTEM REGISTERS** (Cont'd)

#### 2.3.4 Paged Registers

Up to 64 pages, each containing 16 registers, may be mapped to Group F. These paged registers hold data and control information relating to the on-chip peripherals, each peripheral always being associated with the same pages and registers to ensure code compatibility between ST9 devices. The number of these registers depends on the peripherals present in the specific ST9 device. In other words, pages only exist if the relevant peripheral is present.

The paged registers are addressed using the normal register addressing modes, in conjunction with the Page Pointer register, R234, which is one of the System registers. This register selects the page to be mapped to Group F and, once set, does not need to be changed if two or more registers on the same page are to be addressed in succession.

Thus the instructions:

spp #5 ld R242, r4

will load the contents of working register r4 into the third register of page 5 (R242).

**Warning:** During an interrupt, the PPR register is not saved automatically in the stack. If needed, it should be saved/restored by the user within the interrupt routine.

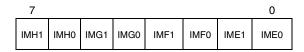

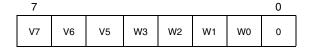

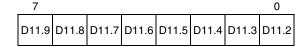

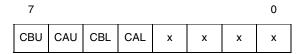

#### PAGE POINTER REGISTER (PPR)

R234 - Read/Write

Register Group: E (System)

Reset value: xxxx xx00 (xxh)

| 7   |     |     |     |     |     |   | 0 |

|-----|-----|-----|-----|-----|-----|---|---|

| PP5 | PP4 | PP3 | PP2 | PP1 | PP0 | 0 | 0 |

#### Bits 7:2 = **PP[5:0]**: Page Pointer.

These bits contain the number (in the range 0 to 63) of the page specified in the spp instruction. Once the page pointer has been set, there is no need to refresh it unless a different page is required.

Bits 1:0: Reserved. Forced by hardware to 0.

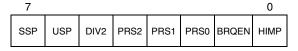

#### 2.3.5 Mode Register

The Mode Register allows control of the following operating parameters:

Selection of internal or external System and User Stack areas,

- Management of the clock frequency,

- Enabling of Bus request and Wait signals when interfacing to external memory.

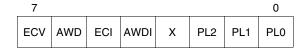

#### **MODE REGISTER (MODER)**

R235 - Read/Write

Register Group: E (System) Reset value: 1110 0000 (E0h)

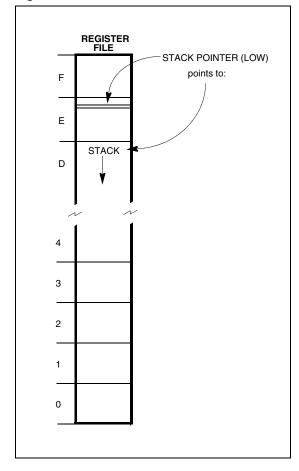

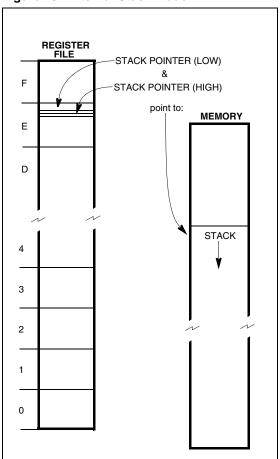

Bit 7 = **SSP**: System Stack Pointer.

This bit selects an internal or external System Stack area.

- 0: External system stack area, in memory space.

- 1: Internal system stack area, in the Register File (reset state).

Bit 6 = **USP**: User Stack Pointer.

This bit selects an internal or external User Stack area

- 0: External user stack area, in memory space.

- 1: Internal user stack area, in the Register File (reset state).

Bit 5 = **DIV2**: *Crystal Oscillator Clock Divided by 2*. This bit controls the divide-by-2 circuit operating on the crystal oscillator clock (CLOCK1).

0: Clock divided by 1

1: Clock divided by 2

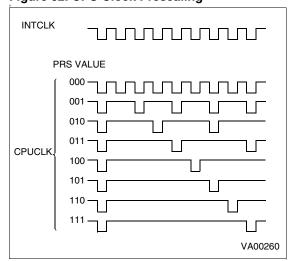

#### Bits 4:2 = PRS[2:0]: CPUCLK Prescaler.

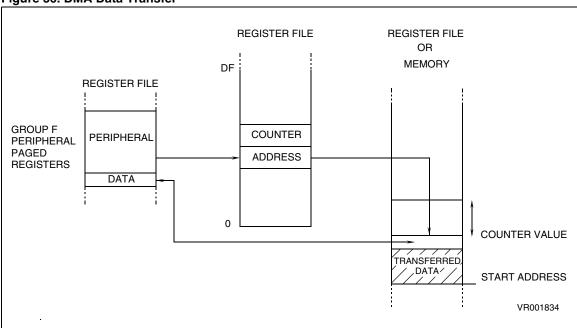

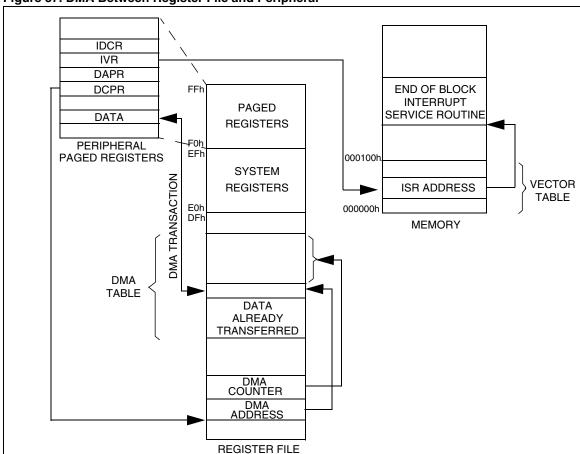

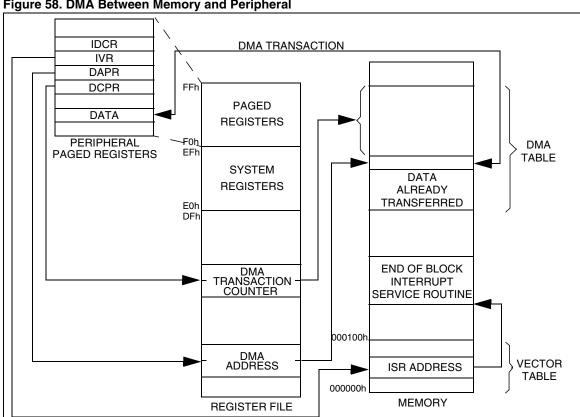

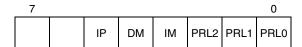

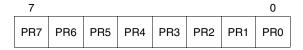

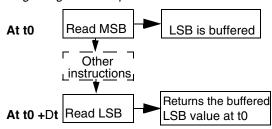

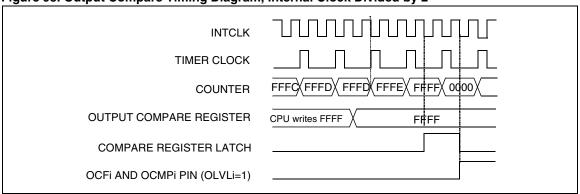

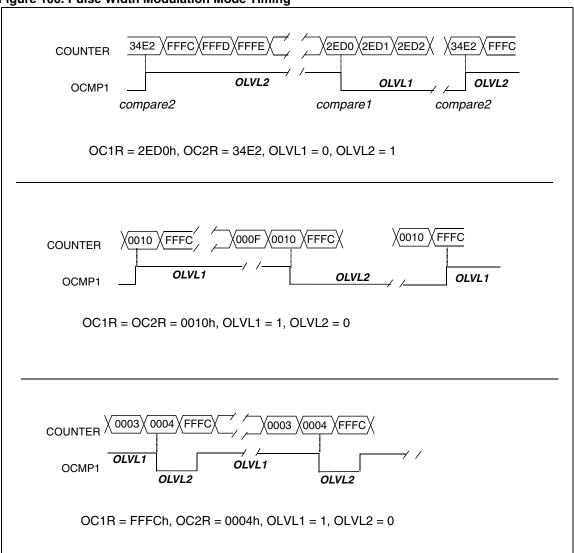

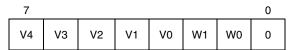

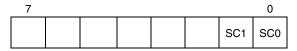

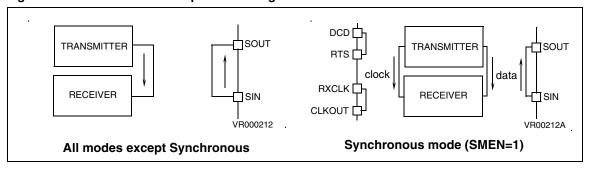

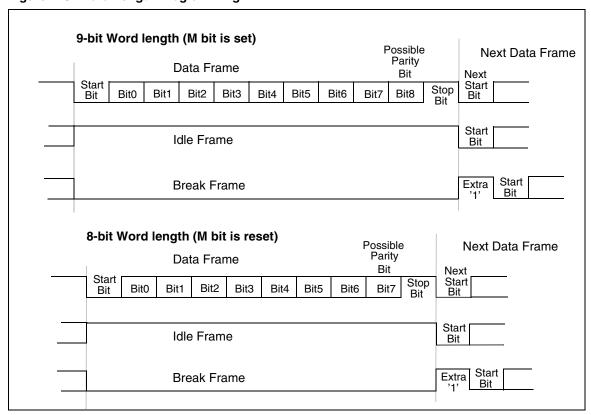

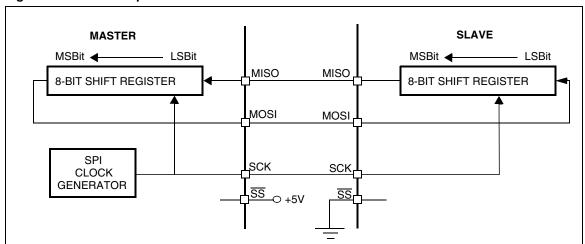

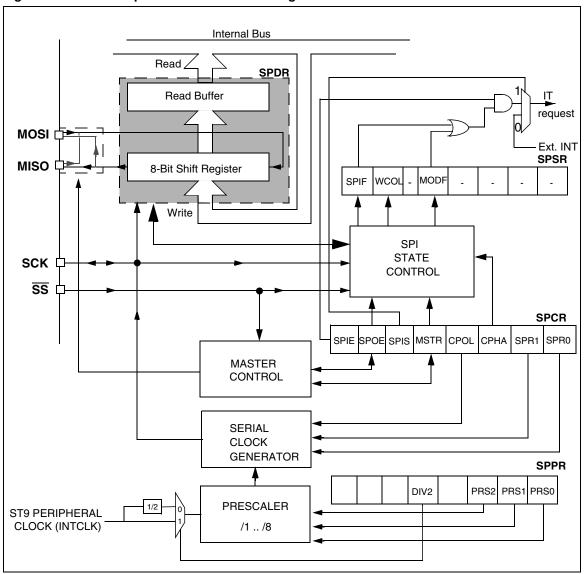

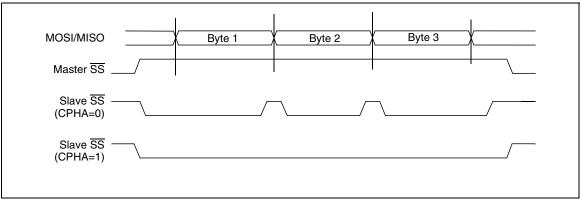

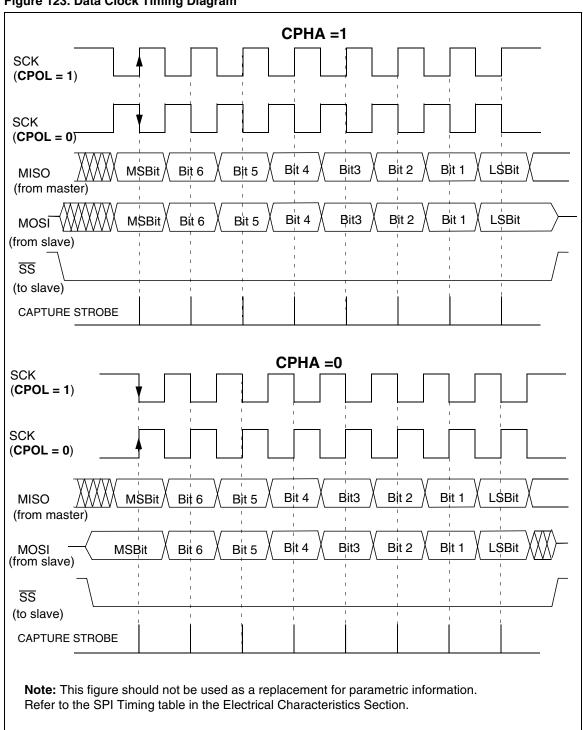

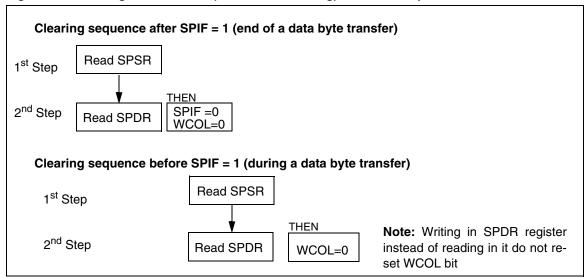

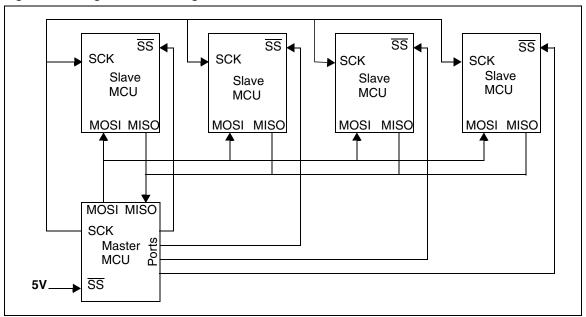

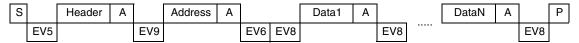

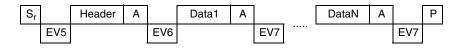

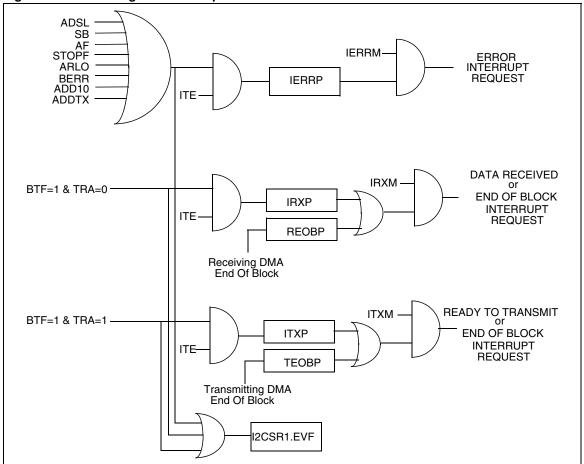

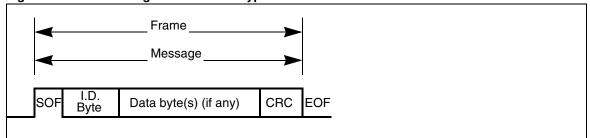

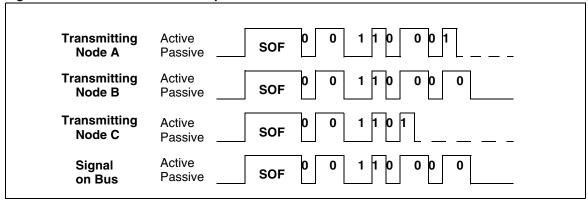

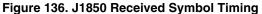

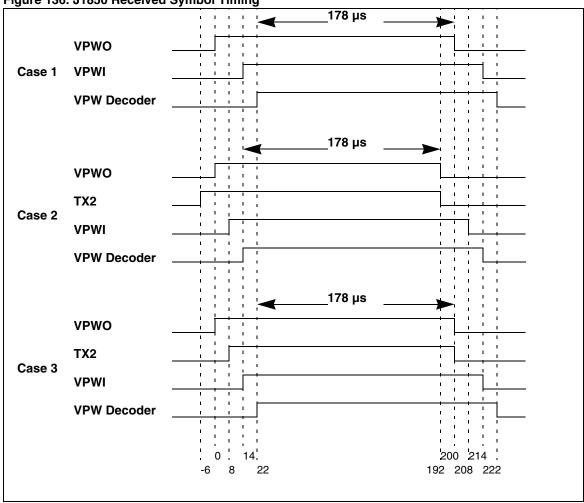

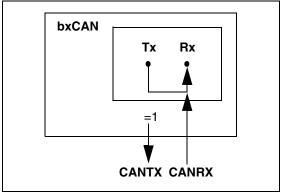

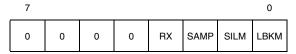

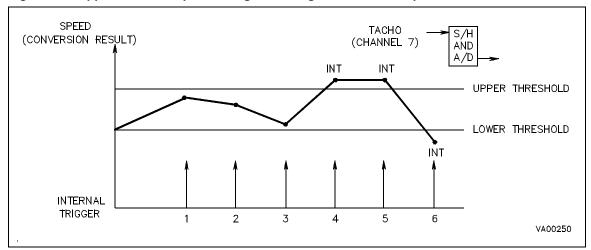

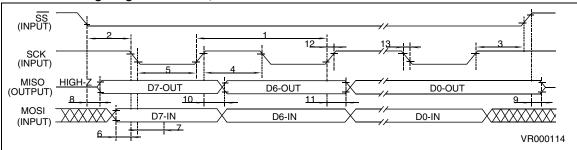

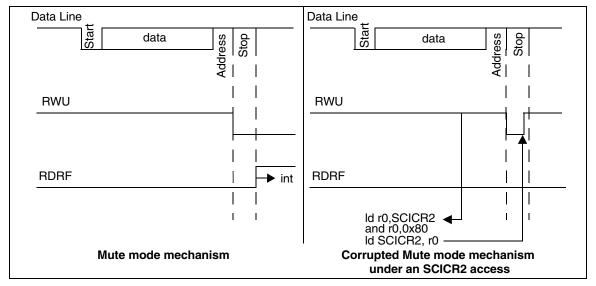

These bits load the prescaler division factor for the internal clock (INTCLK). The prescaler factor selects the internal clock frequency, which can be divided by a factor from 1 to 8. Refer to the Reset and Clock Control chapter for further information.