LTC 1427-50

### Micropower, 10-Bit Current Output DAC with SMBus Serial Interface

#### FEATURES

- Precision 50µA, ±1.5% Initial Full-Scale Output Current, ±2.5% Over Temperature

- Wide Output Voltage DC Compliance: –15V to (V<sub>CC</sub> – 1.3V)

- Wide Supply Range:  $2.7V \le V_{CC} \le 5.5V$

- Supply Current in Shutdown: 10µA Typ

- Low Supply Current: 115µA Typ

- Available in 8-Pin SO

- SMBus Serial Interface

- Four Selectable SMBus Addresses

- DAC Powers Up at Zero or Midscale

- DAC Contents Are Retained in Shutdown

#### **APPLICATIONS**

- LCD Contrast and Backlight Brightness Control

- Power Supply Voltage Adjustment

- Battery Charger Voltage/Current Adjustment

- GaAs FET Bias Adjustment

- Trimmer Pot Elimination

#### DESCRIPTION

The LTC<sup>®</sup>1427-50 is a micropower, 10-Bit current output DAC with an output range of 0µA to 50µA. The DAC output is guaranteed monotonic and DNL is less than 0.9LSB under all operating conditions. Full-scale accuracy is  $\pm 2.5\%$  over the commercial temperature range. The LTC1427-50 operates with power supply voltages from 2.7V to 5.5V and the DAC current source output can be biased from (V<sub>CC</sub> – 1.3V) to –15V.

The LTC1427-50 communicates with external circuitry by using the SMBus serial interface. It acts as an SMBus slave device using one of four selectable SMBus addresses set by the two address pins AD0 and AD1.

On power-up, the DAC output assumes midrange or zero scale, depending on the logic state of the two address pins. The LTC1427-50 can be shut down through the SHDN pin or by setting the SHDN bit = 1 in the SMBus command byte. Digital data for the DAC output is retained internally and the supply current drops to  $10\mu$ A typically when in shutdown.

The LTC1427-50 is available in an 8-pin SO package.

C, LTC and LT are registered trademarks of Linear Technology Corporation.

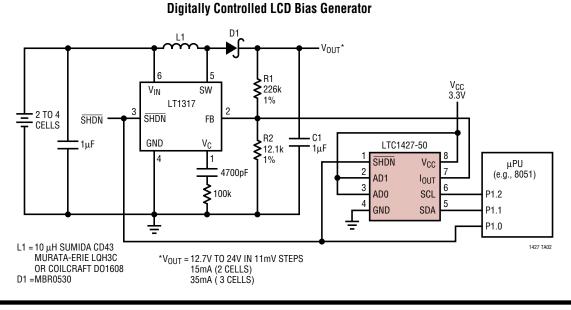

# TYPICAL APPLICATION

Downloaded from Elcodis.com electronic components distributor

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V <sub>CC</sub> )7V                      |

|----------------------------------------------------------------|

| Input Voltage (All Inputs) $-0.3V$ to (V <sub>CC</sub> + 0.3V) |

| DAC Output Voltage $-15V$ to (V <sub>CC</sub> + 0.3V)          |

| DAC Output Short-Circuit Duration Indefinite                   |

| Operating Ambient Temperature Range 0°C to 70°C                |

| Junction Temperature 125°C                                     |

| Storage Temperature Range –65°C to 150°C                       |

| Lead Temperature (Soldering, 10 sec.)                          |

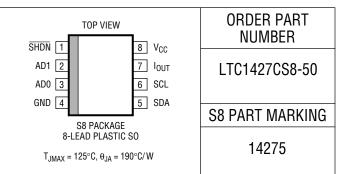

# PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** $T_A$ = operating temperature range unless otherwise specified.

| SYMBOL          | PARAMETER                     | CONDITIONS                                                                              |   | MIN                                 | ТҮР       | MAX            | UNITS       |

|-----------------|-------------------------------|-----------------------------------------------------------------------------------------|---|-------------------------------------|-----------|----------------|-------------|

| V <sub>CC</sub> | Supply Voltage                |                                                                                         | ٠ | 2.7                                 |           | 5.5            | V           |

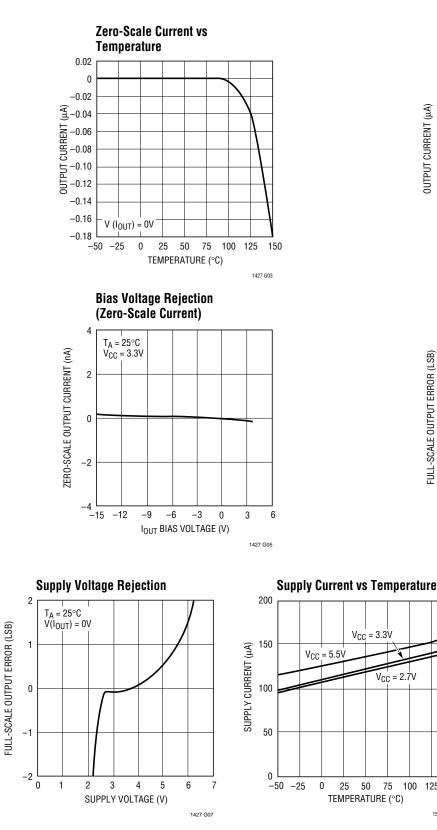

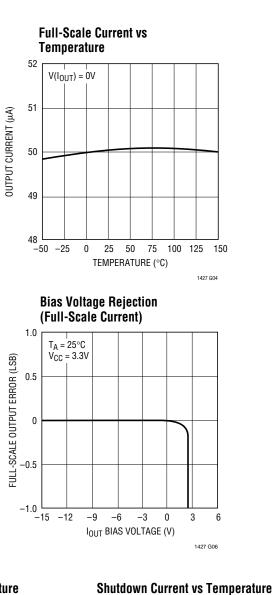

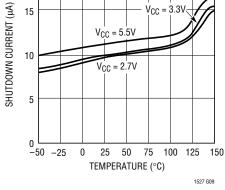

| I <sub>CC</sub> | Supply Current                | $V_{\overline{SHDN}} = V_{SCL} = V_{SDA} = V_{CC} = 3.3V$<br>$V_{\overline{SHDN}} = 0V$ | • |                                     | 115<br>10 | 225<br>25      | μΑ<br>μΑ    |

|                 | DAC Resolution                |                                                                                         | ٠ |                                     | 10        |                | Bits        |

| I <sub>FS</sub> | DAC Full-Scale Current        | $V_{CC} = 3.3V, V(I_{OUT}) = 0V$                                                        | • | 49.25<br>48.75                      | 50<br>50  | 50.75<br>51.25 | μA<br>μA    |

| I <sub>ZS</sub> | DAC Zero-Scale Current        | $V_{CC} = 3.3V, V(I_{OUT}) = 0V$                                                        | ٠ |                                     | ±0.1      | ±200           | nA          |

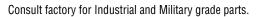

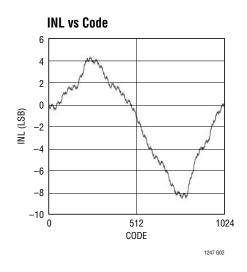

| DNL             | DAC Differential Nonlinearity | $V_{CC} = 3.3V$ , Monotonicity Guaranteed, $V(I_{OUT}) = 0V$                            | ٠ |                                     | ±0.15     | ±0.9           | LSB         |

|                 | Supply Voltage Rejection      | V <sub>CC</sub> = 2.7V to 5.5V, V(I <sub>OUT</sub> ) = 0V                               | ٠ |                                     |           | ±8             | LSB         |

|                 | Output Voltage Rejection      | $V_{CC} = 3.3V$ , Full-Scale Current, $-15V \le V(I_{OUT}) \le 2V$                      | ٠ |                                     |           | ±5             | LSB         |

| I <sub>IN</sub> | Logic Input Current           | $0V \le V_{IN} \le V_{CC}$                                                              | ٠ |                                     |           | ±1             | μA          |

| V <sub>IH</sub> | High Level Input Voltage      | AD0, AD1<br>SHDN<br>SCL, SDA                                                            | • | V <sub>CC</sub> - 0.3<br>2.4<br>1.4 |           |                | V<br>V<br>V |

| V <sub>IL</sub> | Low Level Input Voltage       | SHDN, AD0, AD1<br>SCL, SDA                                                              | • |                                     |           | 0.8<br>0.6     | V<br>V      |

| V <sub>OL</sub> | Low Level Output Voltage      | I <sub>OUT</sub> = 3mA, SDA Only                                                        | ٠ |                                     |           | 0.4            | V           |

#### **RECOMMENDED OPERATING CONDITIONS**

$V_{CC}$  = 3.3V,  $T_A$  = operating temperature range unless otherwise specified.

| SYMBOL              | PARAMETER                                      | CONDITIONS |   | MIN | ТҮР | MAX  | UNITS |

|---------------------|------------------------------------------------|------------|---|-----|-----|------|-------|

| SMBus Tim           | ing (Notes 2, 3)                               |            |   | •   |     |      |       |

| f <sub>SMB</sub>    | SMB Operating Frequency                        |            |   | 10  |     | 100  | kHz   |

| t <sub>BUF</sub>    | Bus Free Time Between Stop and Start Condition |            | • | 4.7 |     |      | μs    |

| t <sub>HD:STA</sub> | Hold Time After (Repeated) Start Condition     |            | • | 4.0 |     |      | μs    |

| t <sub>SU:STA</sub> | Repeated Start Condition Setup Time            |            | • | 4.7 |     |      | μs    |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                      |            | • | 4.0 |     |      | μs    |

| t <sub>HD:DAT</sub> | Data Hold Time                                 |            |   | 300 |     |      | ns    |

| t <sub>SU:DAT</sub> | Data Setup Time                                |            |   | 250 |     |      | ns    |

| t <sub>LOW</sub>    | Clock Low Period                               |            | • | 4.7 |     |      | μs    |

| t <sub>HIGH</sub>   | Clock High Period                              |            | • | 4.0 |     | 50   | μs    |

| t <sub>f</sub>      | Clock/Data Fall Time                           |            | • |     |     | 300  | ns    |

| t <sub>r</sub>      | Clock/Data Rise Time                           |            |   |     |     | 1000 | ns    |

The  ${\ensuremath{\bullet}}$  denotes specifications that apply over the full operating temperature range.

Note 2: All values are referenced to  $V_{\text{IH}}$  and  $V_{\text{IL}}$  levels.

**Note 3:** These parameters are guaranteed by design and are not tested. Refer to the Timing Diagrams for additional information.

**Note 1:** Absolute Maximum Ratings are those beyond which the life of the device may be impaired.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

# TYPICAL PERFORMANCE CHARACTERISTICS

20 15 V<sub>CC</sub> =

$V_{CC} = 3.3V$

25 50 75 100 125 150

$V_{CC} = 2.7V$

1527 G08

Downloaded from Elcodis.com electronic components distributor

#### PIN FUNCTIONS

**SHDN (Pin 1):** Shutdown. A logic low puts the chip into shutdown mode. In shutdown, the digital settings for the DAC are retained. On release from shutdown, the previously programmed value for I<sub>OUT</sub> is reinstated.

**AD1, AD0 (Pins 2, 3):** Address Selection Pins. Tie these two pins to either  $V_{CC}$  or GND to select one of four SMBus addresses to which the LTC1427-50 will respond.

**GND (Pin 4):** Ground. Ground should be tied directly to a ground plane.

**SDA (Pin 5):** SMBus Bidirectional Data Input/Digital Output. This pin is an open-drain output and requires a pull-

up resistor or current source to  $V_{\mbox{CC}}.$  Data is shifted into the SDA pin and acknowledged by the SDA pin.

**SCL (Pin 6):** SMBus Clock Input. Data is shifted into the SDA pin at the rising edges of the SCL clock during data transfer.

IOUT (Pin 7): DAC Current Output.

**V<sub>CC</sub> (Pin 8):** Voltage Supply. This supply must be kept free from noise and ripple by bypassing directly to the ground plane.

#### FUNCTION TABLE

| AD1 | ADO | SMBus Address Location | DAC Power-Up Value | Application            |

|-----|-----|------------------------|--------------------|------------------------|

| L   | L   | 0101101                | Zero-Scale         | CCFL Backlight Control |

| L   | Н   | 0101111                | Zero-Scale         | General Purpose        |

| Н   | L   | 0101110                | Zero-Scale         | General Purpose        |

| Н   | Н   | 0101100                | Midscale           | LCD Contrast Control   |

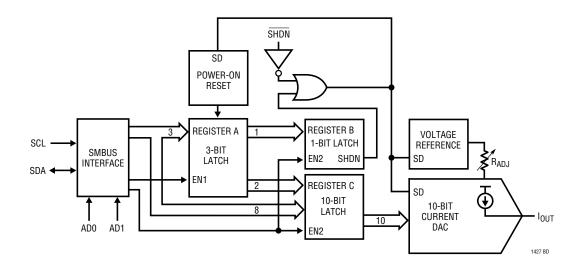

### **BLOCK DIAGRAM**

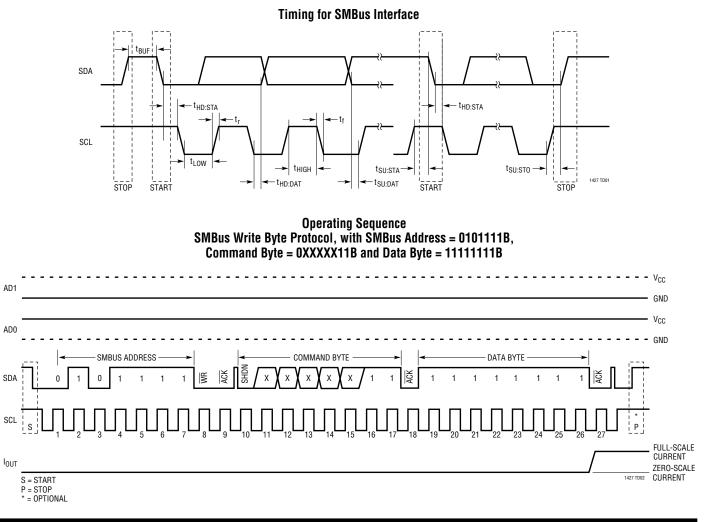

### TIMING DIAGRAMS

### **APPLICATIONS INFORMATION**

#### **Digital Interface**

The LTC1427-50 communicates with an SMBus host using the standard 2-wire SMBus interface. The Timing Diagram shows the signals on the SMBus. The SCL and SDA bus lines must be high when the bus is not in use. External pull-up resistors or current sources are required at these lines.

The LTC1427-50 is a receive-only (slave) device. The master must apply the following Write Byte protocol to communicate with the LTC1427-50:

| 1     | 7                                                                         | 1  | 1 | 8            | 1 | 8         | 1 | 1 |

|-------|---------------------------------------------------------------------------|----|---|--------------|---|-----------|---|---|

| S     | Slave Address                                                             | WR | А | Command Byte | А | Data Byte | А | Ρ |

| S = S | S = Start Condition WB = Write Bit A = Acknowledge Bit P = Stop Condition |    |   |              |   |           |   |   |

The master initiates communication with the LTC1427-50 with a START condition (see SMBus Operating Sequence) and a 7-bit address followed by the write bit = 0. The LTC1427-50 acknowledges and the master delivers the command byte. The LTC1427-50 acknowledges and latches the active bits of the command byte into register A (see Block Diagram) at the falling edge of the acknowledge pulse. The master sends the data byte and the LTC1427-50 acknowledges the data byte. The data byte and last two output bits from register A are latched into register C at the falling edge of the final acknowledge pulse and the DAC current output assumes the new 10-bit data value (see Block Diagram). A STOP condition is optional. The com-

#### **APPLICATIONS INFORMATION**

mand code and data byte are defined with the following format:

| Command | Byte |  |

|---------|------|--|

|         |      |  |

7 7 6 5 2 1 0 6 5 4 3 2 0 4 3 1

SHDN

X

X

X

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

SHDN: 0 for Normal Operation, 1 for Shutdown

D9 to D0: DAC Data Bits, D9 is the Most Significant Bit

#### **START and STOP Conditions**

At the beginning of any SMBus communication, the master must transmit a START condition by switching the SDA from high to low while SCL is high. When a master has finished communicating with a slave device, a STOP condition is issued by switching the SDA from low to high while SCL is high. The SMBus is then free for communication with another SMBus slave device.

#### **Early STOP Conditions**

The LTC1427-50 recognizes a STOP condition at any point in the SMBus communication sequence. If the STOP occurs prematurely before the data byte is acknowledged in the Write Byte protocol, the DAC output current value is not updated; otherwise internal register C is updated with the new data and the DAC output current changes correspondingly.

#### The Slave Address

The LTC1427-50 can respond to one of four 7-bit addresses. The first five bits have been factory programmed to 01011. The two address bits, AD1 and AD0, are programmed by the user (see Function Table).

#### **10-Bit Current Output DAC**

The 10-Bit current output DAC is guaranteed monotonic and is digitally adjustable in 1023 equal steps. On powerup, if AD1 and AD0 are both connected to V<sub>CC</sub>, the 10-bit internal register C (see Block Diagram) resets to 1000000000B and the DAC output is set to midrange. If either AD1 or AD0 is connected to ground, register C resets to 000000000B on power-up and the DAC output is set to zero. For the LTC1427-50, the source current output (I<sub>OUT</sub>) can be biased from -15V to (V<sub>CC</sub> - 1.3V). Full-scale current is trimmed to  $\pm$ 1.5% at room temperature and  $\pm$ 2.5% over the commercial temperature range.

#### Shutdown

There are two ways to shut down the LTC1427-50 (see Block Diagram). The LTC1427-50 will enter shutdown mode whenever it sees a logic low at the SHDN pin or whenever it receives a logic high at bit 7 of the command byte through the SMBus interface. In shutdown mode, the digital data is retained internally and the supply current drops to only  $10\mu$ A typically.

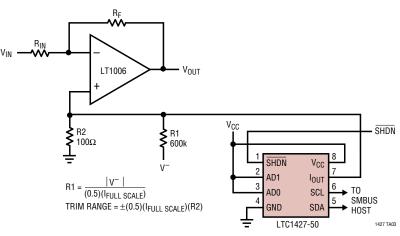

### TYPICAL APPLICATIONS

#### LTC1427-50 Used to Null Op Amp's Offset Voltage

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

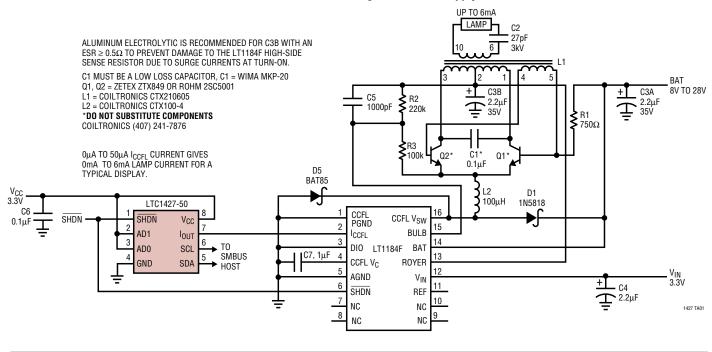

### TYPICAL APPLICATIONS

#### SMBus-Controlled Floating CCFL Power Supply

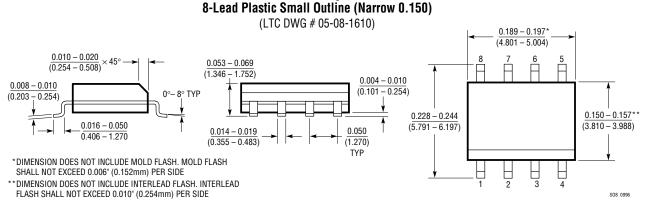

PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

**S8** Package

# RELATED PARTS

| PART NUMBER           | DESCRIPTION                                                         | COMMENTS                                                        |

|-----------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|

| LTC1329-10/LTC1329-50 | Micropower 8-Bit Current Source DAC                                 | 1-Wire, 2-Wire or Standard 3-Wire SPI Control                   |

| LTC1380/LTC1393       | SMBus Single-Ended 8-Channel/Differential<br>4-Channel Multiplexers | Single 2.7V to $\pm$ 5V Supply, Low Power                       |

| LTC1426               | Micropower Dual 6-Bit PWM DAC                                       | Pulse Mode and Push-Button Mode Interface                       |

| LTC1428               | Micropower 8-Bit Current Sink DAC                                   | 1-Wire, 2-Wire or Standard 3-Wire SPI Control                   |

| LTC1623               | SMBus Dual High Side Switch Controller                              | Regulated Onboard Charge Pump Drives External N-Channel MOSFETs |