### FEATURES

- Precision Full-Scale DAC Output Current at 25°C: 50µA ±3%

- Wide Output Voltage DC Compliance: 2V to 10V

- Wide Supply Range:  $3V \le V_{CC} \le 6.5V$

- Supply Current in Shutdown: 0.2µA

- Low Supply Current: 130µA

- Available in 8-Pin SO

- Triple Mode<sup>™</sup> Interface

- 1. Standard 3-Wire Mode

- 2. 1-Wire Pulse Mode Interface: Increment-Only

- 3. 2-Wire Pulse Mode Interface: Increment/Decrement

- DAC Value Read Back Capability in 3-Wire Mode

- DAC Powers Up at Midrange

- DAC Contents Are Retained in Shutdown

## **APPLICATIONS**

- LCD Contrast Control

- Backlight Brightness Control

- Power Supply Voltage Adjustment

- Battery Charger Voltage/Current Adjustment

- GaAs FET Bias Adjustment

- Trimmer Pot Elimination

# Micropower 8-Bit Current Sink Output D/A Converter

## DESCRIPTION

The LTC<sup>®</sup>1428-50 is a micropower 8-bit current sink output D/A converter (DAC) with an output range of  $0\mu$ A to 50 $\mu$ A. In 3.3V or 5V systems, the DAC I<sub>OUT</sub> pin can be biased from 2V to 10V. Supply current is only 130 $\mu$ A. Shutdown mode drops the supply current to 0.2 $\mu$ A.

The LTC1428-50 communicates with external circuitry by using one of three interface modes: standard 3-wire serial mode or one of two pulse modes. Upon power-up, the internal counter resets to 10000000B, the DAC output assumes midrange and the chip configures to 3-wire or pulse mode depending on the CS signal level.

In 3-wire mode, the system MPU can serially transfer 8-bit data to and from the LTC1428-50. In pulse mode, the upper six bits of the DAC output program for increment-only (1-wire interface) or increment/decrement (2-wire interface) operation depending on the  $D_{IN}$  signal level. In increment-only mode, the counter rolls over and sets the DAC to zero if the counter increases beyond full scale. In increment/decrement mode, the counter stops incrementing at full scale, stops decrementing at zero scale and does not roll over.

LTC1428-50 is available in an 8-pin SO package.

T, LTC and LT are registered trademarks of Linear Technology Corporation. Triple Mode is a trademark of Linear Technology Corporation.

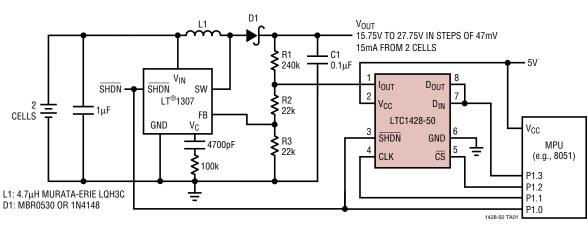

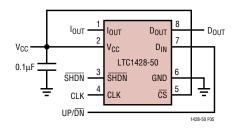

# TYPICAL APPLICATION

### Digitally Controlled LCD Bias Generator (Standard 3-Wire Mode)

# **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                       |

|----------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> ) 7V                           |

| Input Voltage (All Inputs) $-0.3V$ to (V <sub>CC</sub> + 0.3V) |

| Output Voltage                                                 |

| I <sub>OUT</sub> –0.3V to 10V                                  |

| $D_{OUT}$                                                      |

| Short-Circuit Duration (All Outputs) Indefinite                |

| Operating Temperature Range 0°C to 70°C                        |

| Storage Temperature Range –65°C to 150°C                       |

| Lead Temperature (Soldering, 10 sec)                           |

|                                                                |

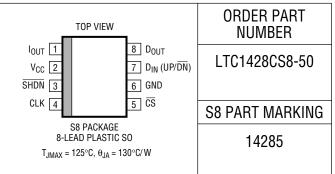

# PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

# **ELECTRICAL CHARACTERISTICS** $V_{CC} = 3.3V$ , $T_A = 25^{\circ}C$ , unless otherwise specified.

| SYMBOL PARAMETER |                                  | CONDITIONS                                                                                                                  |   | MIN          | ТҮР        | MAX          | UNITS    |

|------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---|--------------|------------|--------------|----------|

| V <sub>CC</sub>  |                                  |                                                                                                                             |   | 3.0          |            | 6.5          | V        |

| I <sub>CC</sub>  | Supply Current                   | $V_{\overline{SHDN}} = V_{DIN} = V_{\overline{CS}} = V_{CC}$ , $V_{CLK} = 0V$ , $D_{OUT} = NC$ , $I_{OUT} = NC$<br>Shutdown | • |              | 130<br>0.2 | 225<br>10    | μA<br>μA |

|                  | DAC Resolution                   |                                                                                                                             |   |              | 8          |              | Bits     |

|                  | DAC Full-Scale Current           | I <sub>OUT</sub> Bias Voltage = 2.5V                                                                                        | • | 48.5<br>47.5 | 50<br>50   | 51.5<br>52.5 | μA<br>μA |

|                  | DAC Zero-Scale Current           | I <sub>OUT</sub> Bias Voltage = 2.5V                                                                                        | • |              |            | 200          | nA       |

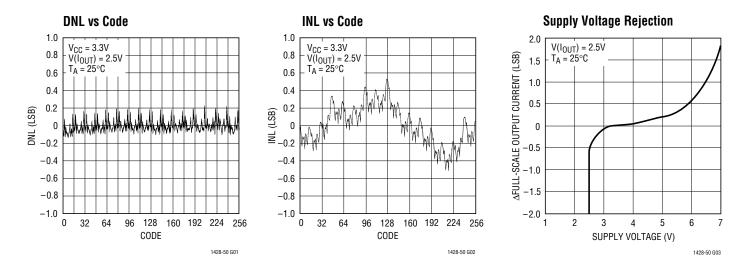

|                  | DAC Differential<br>Nonlinearity | Monotonicity Guaranteed, No Missing Codes                                                                                   | • |              |            | ±0.9         | LSB      |

|                  | Supply Voltage Rejection         | $V_{CC}$ = 3V to 6.5V, Full Scale Current, I <sub>OUT</sub> Bias Voltage = 2.5V                                             |   |              | ±1         | ±4           | LSB      |

|                  | Output Voltage Rejection         | $V_{CC}$ = 5V, Full Scale Current,<br>2V $\leq$ V(I <sub>OUT</sub> ) $\leq$ 3V                                              | • |              |            | ±1           | LSB      |

|                  |                                  | $V_{CC}$ = 5V, Full Scale Current,<br>3V $\leq$ V(I <sub>OUT</sub> ) $\leq$ 10V                                             | • |              | ±1         | ±4           | LSB      |

|                  | Logic Input Current              | $0V \le V_{IN} \le V_{CC}$                                                                                                  |   |              |            | ±1           | μA       |

| V <sub>IH</sub>  | High Level Input Voltage         | $V_{CC} = 5V$<br>$V_{CC} = 3.3V$                                                                                            | • | 2.0<br>1.9   |            |              | V<br>V   |

| V <sub>IL</sub>  | Low Level Input Voltage          | V <sub>CC</sub> = 5V<br>V <sub>CC</sub> = 3.3V                                                                              | • |              |            | 0.80<br>0.45 | V<br>V   |

| V <sub>OH</sub>  | High Level Output Voltage        | $V_{CC} = 5V, I_0 = 400\mu A$<br>$V_{CC} = 3.3V, I_0 = 400\mu A$                                                            | • | 2.4<br>2.1   |            |              | V<br>V   |

| V <sub>OL</sub>  | Low Level Output Voltage         | $V_{CC} = 5V, I_0 = 2mA$<br>$V_{CC} = 3.3V, I_0 = 1mA$                                                                      | • |              |            | 0.4<br>0.4   | V<br>V   |

| I <sub>OZ</sub>  | Three-State Output Leakage       | $V_{\overline{CS}} = V_{CC}$                                                                                                |   |              |            | ±5           | μA       |

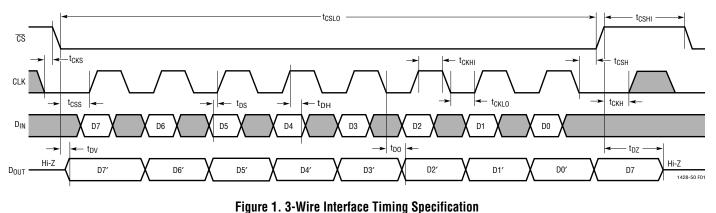

## **RECOMMENDED OPERATING CONDITIONS** $V_{CC} = 5V$ , unless otherwise specified. (Notes 2, 3)

| SYMBOL            | PARAMETER                                                          | CONDITIONS                                                |   | MIN         | ТҮР | MAX | UNITS    |

|-------------------|--------------------------------------------------------------------|-----------------------------------------------------------|---|-------------|-----|-----|----------|

| Serial In         | terface                                                            |                                                           |   |             |     |     |          |

| f <sub>CLK</sub>  | Clock Frequency                                                    |                                                           |   |             |     | 2   | MHz      |

| t <sub>CKS</sub>  | Setup Time, CLK $\downarrow$ Before $\overline{CS}\downarrow$      |                                                           | • | 150         |     |     | ns       |

| t <sub>CSS</sub>  | Setup Time, $\overline{\text{CS}}\downarrow$ Before CLK $\uparrow$ |                                                           | • | 400         |     |     | ns       |

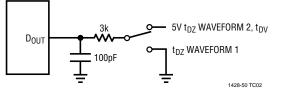

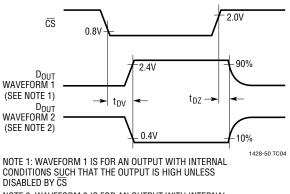

| t <sub>DV</sub>   | $\overline{\text{CS}}\downarrow$ to D <sub>OUT</sub> Valid         | See Test Circuits                                         | • | 150         |     |     | ns       |

| t <sub>DS</sub>   | D <sub>IN</sub> Setup Time Before CLK↑                             |                                                           | • | 150         |     |     | ns       |

| t <sub>DH</sub>   | D <sub>IN</sub> Hold Time After CLK <sup>↑</sup>                   |                                                           | • | 150         |     |     | ns       |

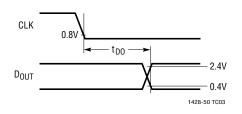

| t <sub>DO</sub>   | $CLK\downarrow$ to $D_{OUT}$ Valid                                 | See Test Circuits                                         | • | 150         |     |     | ns       |

| t <sub>CKHI</sub> | CLK High Time                                                      |                                                           | • | 200         |     |     | ns       |

| t <sub>CKLO</sub> | CLK Low Time                                                       |                                                           | • | 250         |     |     | ns       |

| t <sub>CSH</sub>  | CLK↓ Before CS↑                                                    |                                                           | • | 150         |     |     | ns       |

| t <sub>DZ</sub>   | CS↑ to D <sub>OUT</sub> in Hi-Z                                    | See Test Circuits                                         | • |             |     | 400 | ns       |

| t <sub>CKH</sub>  | CS↑ Before CLK↑                                                    |                                                           | • |             |     | 400 | ns       |

| t <sub>CSLO</sub> | CS Low Time                                                        | f <sub>CLK</sub> = 2MHz (Note 4)<br>V <sub>CLK</sub> = 0V | • | 4550<br>400 |     |     | ns<br>ns |

| t <sub>CSHI</sub> | CS High Time                                                       |                                                           | • | 400         |     |     | ns       |

The  $\bullet$  denotes specifications which apply over the full operating temperature range.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

**Note 2:** Timing for all input signals is measured at 0.8V for a High-to-Low transition and at 2V for a Low-to-High transition.

**Note 3:** Timing specifications are guaranteed by design but not tested. **Note 4:** This is the minimum time required for valid data transfer.

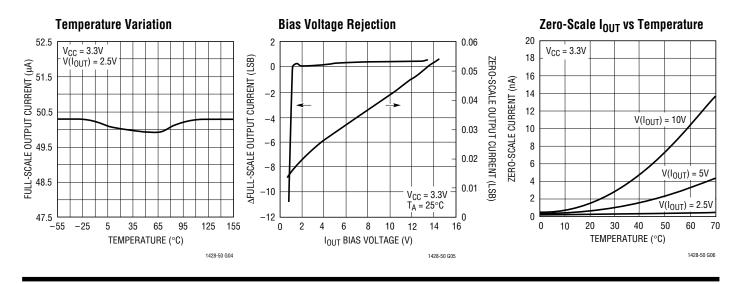

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

## PIN FUNCTIONS

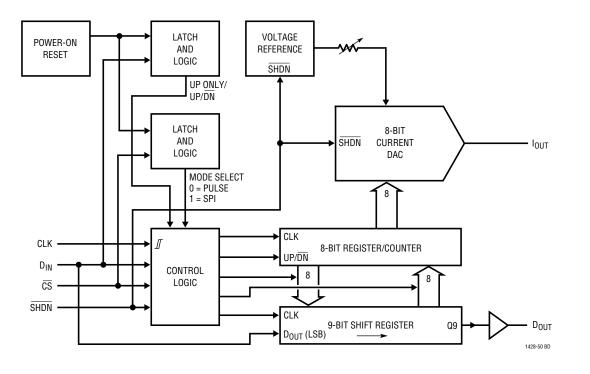

$I_{OUT}$  (Pin 1): DAC Current Sink Output. In 3.3V or 5V systems, the DAC I<sub>OUT</sub> pin can be biased from 2V to 10V.

**V<sub>CC</sub> (Pin 2):** Voltage Supply ( $3V \le V_{CC} \le 6.5V$ ). This supply must be kept free from noise and ripple by bypassing directly to a ground plane.

**SHDN** (Pin 3): Shutdown. A logic low puts the chip into shutdown mode. The digital setting for the DAC is retained.

**CLK (Pin 4):** Shift Clock. This clock synchronizes the serial data and has a Schmitt trigger input.

**CS** (Pin 5): Chip Select Input. In 3-wire mode, a logic low enables the LTC1428-50. Upon power-up, a logic high

puts the chip into pulse mode. If  $\overline{\text{CS}}$  ever goes low, the chip is configured into 3-wire mode until V<sub>CC</sub> is reset.

**GND (Pin 6):** Ground. Ground should be tied directly to a ground plane.

$D_{IN}$  (UP/DN)(Pin 7): Data Input. In 3-wire mode, the DAC data is shifted into  $D_{IN}$ . In pulse mode, upon power-up a logic high puts the counter into increment-only mode. If  $D_{IN}$  ever goes low, the counter is configured in increment/ decrement mode until V<sub>CC</sub> is reset.

$D_{OUT}$  (Pin 8): Data Output. In 3-wire mode, on every conversion  $D_{OUT}$  serially outputs the previous 8-bit DAC data. In pulse mode,  $D_{OUT}$  is three-stated.

### **BLOCK DIAGRAM**

## **TEST CIRCUITS**

Load Circuit for t<sub>D0</sub>

1428-50 TC01

### Voltage Waveforms for $t_{DO}$

Load Circuit for t<sub>DZ,</sub> t<sub>DV</sub>

#### Voltage Waveforms for $t_{\text{DZ}}, t_{\text{DV}}$

NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY  $\overline{\rm CS}$

# SERIAL I/O OPERATING SEQUE CE

# **APPLICATIONS INFORMATION**

### **8-BIT CURRENT OUTPUT DAC**

The LTC1428-50 is an 8-bit, current sink output digital-toanalog (DAC) converter. The LTC1428-50 is guaranteed monotonic and is digitally adjustable in 256 equal steps. Upon power up, the counter resets to 1000000B and the DAC output assumes midrange. The  $I_{OUT}$  pin can be biased from 2V to 10V. The LTC1428-50 features a full-scale output current of  $50\mu A \pm 3\%$  at room temperature ( $\pm 5\%$ over temperature). This device also includes a flexible serial digital interface that allows easy interconnection to a variety of digital systems.

### **DIGITAL INTERFACE**

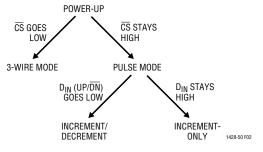

### Automatic Mode Selection

The LTC1428-50 includes a serial interface capable of communicating with the host system using one of three protocols; standard 3-wire mode, a 2-wire up/down pulse mode and a 1-wire increment-only pulse mode. The LTC1428-50 is designed to autoconfigure itself depending on the method

Figure 2. LTC1428-50 Operating Modes

of data presentation. A diagram illustrating this autodetection behavior is shown in Figure 2. At power-up, the interface is set to 1-wire pulse mode. If the CS line ever goes low (as it will at the beginning of a valid 3-wire serial transfer) the chip immediately reconfigures itself into 3-wire mode and remains in this mode until power is cycled. If  $\overline{CS}$ stays high, the device stays in pulse mode and monitors the UP/DN pin to determine whether to switch to 2-wire mode. If UP/DN ever goes low (as it will the first time a "down" command is given) the chip switches into 2-wire pulse mode and remains in this mode until power is cycled. In a properly configured 1-wire system, CS and UP/DN will always remain high. 2-wire pulse mode systems must provide a single logic low pulse before the first data pulses are sent to prevent the LTC1428-50 from remaining in 1-wire mode if the first several pulses are logic high.

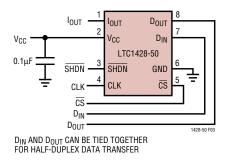

### Standard 3-Wire Mode (Figure 3)

Refer to the Serial Interface Operating Sequence in Figure 1. When operating in 3-wire mode, the LTC1428-50 will interface directly with most standard 3- or 4-wire serial interface systems. The clock (CLK) input synchronizes the data transfer with each input bit captured at the rising edge of CLK and each output data bit shifted through  $D_{OUT}$  at the falling edge. Data is shifted into and out of the LTC1428-50 starting with the MSB bit. A falling edge at  $\overline{CS}$  initiates the data transfer and brings the  $D_{OUT}$  pin out of three-state. The serial 8-bit data representing the new DAC setting is shifted out of the  $D_{OUT}$  pin. After the new data is

## **APPLICATIONS INFORMATION**

shifted in, a rising edge at  $\overline{\text{CS}}$  transfers the data from the input shift register into the DAC register. The DAC output assumes the new value and the D<sub>OUT</sub> pin returns to a high-impedance state.

I<sub>OUT</sub> = (B7 B6 B5 B4 B3 B2 B1 B0)I<sub>FULLSCALE</sub>/255

Figure 3. 3-Wire Mode; Serial Interface (3-Wire Control by  $\overline{\text{CS}},$  CLK and  $\text{D}_{\text{IN}})$

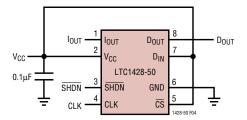

### 1-Wire Interface (Pulse Mode, Figure 4)

In 1-wire pulse mode, each rising edge at CLK increments the upper six bits of the DAC register by one count. When incremented beyond 11111100B, the counter rolls over and sets the DAC to the minimum value (00000000B). In this way, a single pulse applied to CLK increases the DAC output by a single 4LSB step and 63 pulses decrease the

Figure 4. Pulse Mode: Increment Only (1-Wire Control by CLK)

DAC output by one step. The last two LSBs are always zero in pulse mode.

I<sub>OUT</sub> = (B7 B6 B5 B4 B3 B2 0 0)I<sub>FULLSCALE</sub>/255

To configure the LTC1428-50 in 1-wire pulse mode, tie both the  $\overline{\text{CS}}$  and  $\text{D}_{\text{IN}}$  pins to  $\text{V}_{\text{CC}}.$

### 2-Wire Interface (Pulse Mode, Figure 5)

In 2-wire pulse mode, a logic high at UP/DN programs the DAC register to increment and each rising edge at CLK increments the upper six bits of the register by one count. Similarly, a logic low at UP/DN programs the DAC register to decrement and a rising edge at CLK decrements the upper six bits of the register by one count. Each count in 2-wire mode changes the DAC output by a single 4LSB step. The DAC register stops incrementing at 11111100B and stops decrementing at 00000000B and will not roll over in 2-wire pulse mode. The last two LSBs are always zero in pulse mode.

I<sub>OUT</sub> = (B7 B6 B5 B4 B3 B2 0 0)I<sub>FULLSCALE</sub>/255

To configure the LTC1428-50 in 2-wire pulse mode, tie  $\overline{\text{CS}}$  to V<sub>CC</sub> and bring the UP/DN pin low at least once during power-up.

Figure 5. Pulse Mode; Increment/Decrement (2-Wire Control by CLK and UP/DN)

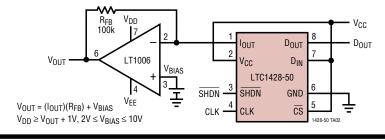

## TYPICAL APPLICATION

Pulse Mode: Increment-Only (1-Wire Control by CLK) with Voltage Output

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

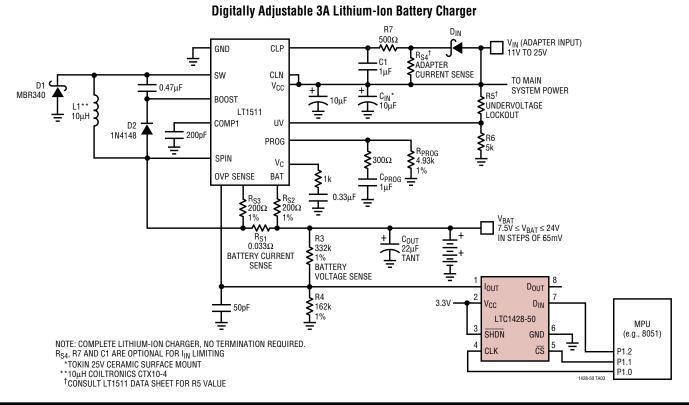

## TYPICAL APPLICATION

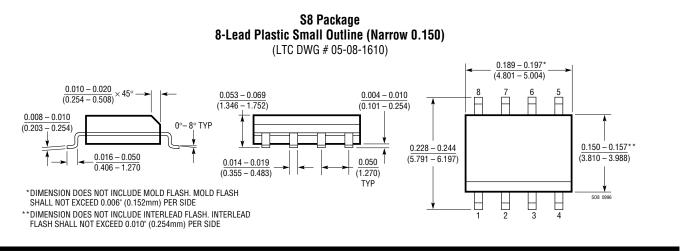

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                          | COMMENTS                                               |

|-------------|------------------------------------------------------|--------------------------------------------------------|

| LTC1329     | 8-Bit Current Output D/A Converter                   | Current Source Output, Full-Scale Current 10µA or 50µA |

| LTC1451     | 12-Bit Micropower Serial Input V <sub>OUT</sub> DAC  | Higher Resolution, 8-Pin SO                            |

| LTC1452     | 12-Bit Multiplying Serial Input V <sub>OUT</sub> DAC | Higher Resolution, 8-Pin SO                            |

| LTC8043     | 12-Bit Multiplying Serial Input IOUT DAC             | Higher Resolution, 8-Pin SO                            |