Step-Down Switching Regulators

### **FEATURES**

- 1.5A Switch in a Small MSOP Package

- Constant 1.25MHz Switching Frequency

- High Power Exposed Pad (MS8E) Package

- Wide Operating Voltage Range: 3V to 25V

- High Efficiency 0.22Ω Switch

- 1.2V Feedback Reference Voltage

- Fixed Output Voltages of 1.8V, 2.5V, 3.3V, 5V

- 2% Overall Output Tolerance

- Uses Low Profile Surface Mount Components

- Low Shutdown Current: 6µA

- Synchronizable to 2MHz

- Current Mode Loop Control

- Constant Maximum Switch Current Rating at All Duty Cycles\*

### **APPLICATIONS**

- DSL Modems

- **Portable Computers**

- Wall Adapters

- **Battery-Powered Systems**

TYPICAL APPLICATION

**Distributed Power**

### DESCRIPTION

The LT<sup>®</sup>1767 is a 1.25MHz monolithic buck switching regulator. A high efficiency 1.5A,  $0.22\Omega$  switch is included on the die together with all the control circuitry required to complete a high frequency, current mode switching regulator. Current mode control provides fast transient response and excellent loop stability.

New design techniques achieve high efficiency at high switching frequencies over a wide operating range. A low dropout internal regulator maintains consistent performance over a wide range of inputs from 24V systems to Li-Ion batteries. An operating supply current of 1mA improves efficiency, especially at lower output currents. Shutdown reduces guiescent current to 6µA. Maximum switch current remains constant at all duty cycles. Synchronization allows an external logic level signal to increase the internal oscillator from 1.4MHz to 2MHz.

The LT1767 is available in an 8-pin MSOP fused leadframe package and a low thermal resistance exposed pad package. Full cycle-by-cycle short-circuit protection and thermal shutdown are provided. High frequency operation allows the reduction of input and output filtering components and permits the use of chip inductors.

**LT**, LTC and LT are registered trademarks of Linear Technology Corporation. \*Patent Pending

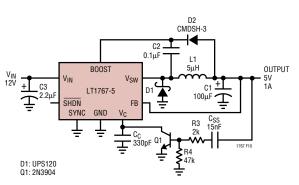

#### 12V to 3.3V Step-Down Converter D2 CMDSH-3 C2 0.1µF L1 5μΗ BOOST OUTPUT VIN 3.3V V<sub>IN</sub> V<sub>SW</sub> 12V C3 1.2A\* OPEN LT1767-3.3 2.2µF 0R CERAMIC \_ SHDN FB HIGH SYNC GND Vc = ON C1 C D1 ر CC 10µF 1.5nF **UPS120** CERAMIC 4.7k \*MAXIMUM OUTPUT CURRENT IS SUBJECT TO THERMAL DERATING. 1767 TA01

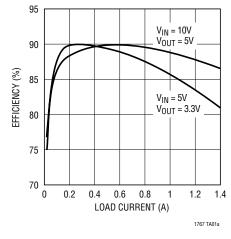

#### **Efficiency vs Load Current**

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Input Voltage         | 25V  |

|-----------------------|------|

| BOOST Pin Above SW    | 20V  |

| Max BOOST Pin Voltage | 35V  |

| SHDN Pin              | 25V  |

| FB Pin Voltage        | . 6V |

| FB Pin Current        | 1mA  |

| SYNC Pin Current 1mA                          |

|-----------------------------------------------|

| Operating Junction Temperature Range (Note 2) |

| LT1767E – 40°C to 125°C                       |

| Storage Temperature Range –65°C to 150°C      |

| Lead Temperature (Soldering, 10 sec) 300°C    |

|                                               |

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes the specifications which <u>apply</u> over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 15V, V<sub>C</sub> = 0.8V, Boost = V<sub>IN</sub> + 5V, SHDN, SYNC and switch open unless otherwise noted.

| PARAMETER                            | CONDITION                                                            |                                                                                            |   | MIN            | ТҮР   | MAX            | UNITS       |

|--------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---|----------------|-------|----------------|-------------|

| Maximum Switch Current Limit         | $T_{A} = 0^{\circ}C \text{ to } 125^{\circ}C$ $T_{A} = < 0^{\circ}C$ |                                                                                            |   |                | 2     | 3<br>3         | A<br>A      |

| Oscillator Frequency                 | 3.3V < V <sub>IN</sub> < 25V                                         | 3.3V < V <sub>IN</sub> < 25V                                                               |   | 1.1<br>1.1     | 1.25  | 1.4<br>1.5     | MHz<br>MHz  |

| Switch On Voltage Drop               | $I_{SW}$ = $-1.5 A,  0^\circ C \leq T_A \leq 125^\circ C$ and $-$    | $I_{SW} = -1.5A, 0^{\circ}C \le T_A \le 125^{\circ}C \text{ and } -1.3A, T_A < 0^{\circ}C$ |   |                | 330   | 400<br>500     | mV<br>mV    |

| V <sub>IN</sub> Undervoltage Lockout | (Note 3)                                                             | (Note 3)                                                                                   |   | 2.47           | 2.6   | 2.73           | V           |

| V <sub>IN</sub> Supply Current       | V <sub>FB</sub> = V <sub>NOM</sub> + 17%                             | V <sub>FB</sub> = V <sub>NOM</sub> + 17%                                                   |   |                | 1     | 1.3            | mA          |

| Shutdown Supply Current              | $V_{\overline{SHDN}} = 0V, V_{IN} = 25V, V_{SW} = 0V$                | $V_{\overline{SHDN}} = 0V, V_{IN} = 25V, V_{SW} = 0V$                                      |   |                | 6     | 20<br>45       | μΑ<br>μΑ    |

| Feedback Voltage                     | $3V < V_{IN} < 25V, 0.4V < V_C < 0.9V$<br>(Note 3)                   | LT1767 (Adj)                                                                               | • | 1.182<br>1.176 | 1.2   | 1.218<br>1.224 | V<br>V      |

|                                      |                                                                      | LT1767-1.8                                                                                 | • | 1.764          | 1.8   | 1.836          | V           |

|                                      |                                                                      | LT1767-2.5                                                                                 | • | 2.45           | 2.5   | 2.55           | V           |

|                                      |                                                                      | LT1767-3.3                                                                                 | • | 3.234          | 3.3   | 3.366          | V           |

|                                      |                                                                      | LT1767-5                                                                                   | • | 4.9            | 5     | 5.1            | V           |

| FB Input Current                     | LT1767 (Adj)                                                         | ·                                                                                          | • |                | -0.25 | -0.5           | μA          |

|                                      |                                                                      |                                                                                            |   |                |       | sn1            | 767 1767fas |

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 15V, V<sub>C</sub> = 0.8V, Boost = V<sub>IN</sub> + 5V, SHDN, SYNC and switch open unless otherwise noted.

| PARAMETER CONDITION                                   |                                                                                                         |   | MIN                      | ТҮР                    | MAX                  | UNITS                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---|--------------------------|------------------------|----------------------|----------------------|

| FB Input Resistance                                   | LT1767-1.8<br>LT1767-2.5<br>LT1767-3.3<br>LT1767-5                                                      |   | 10.5<br>14.7<br>19<br>29 | 15<br>21<br>27.5<br>42 | 21<br>30<br>39<br>60 | kΩ<br>kΩ<br>kΩ<br>kΩ |

| Error Amp Voltage Gain                                | $0.4V < V_{C} < 0.9V$                                                                                   |   | 150                      | 350                    |                      |                      |

| Error Amp Transconductance                            | $\Delta I_{VC} = \pm 10 \mu A$                                                                          | • | 500                      | 850                    | 1300                 | μMho                 |

| V <sub>C</sub> Pin Source Current                     | $V_{FB} = V_{NOM} - 17\%$                                                                               | ٠ | 80                       | 120                    | 160                  | μA                   |

| V <sub>C</sub> Pin Sink Current                       | V <sub>FB</sub> = V <sub>NOM</sub> + 17%                                                                | ٠ | 70                       | 110                    | 180                  | μA                   |

| V <sub>C</sub> Pin to Switch Current Transconductance |                                                                                                         |   |                          | 2.5                    |                      | A/V                  |

| V <sub>C</sub> Pin Minimum Switching Threshold        | Duty Cycle = 0%                                                                                         |   |                          | 0.35                   |                      | V                    |

| V <sub>C</sub> Pin 1.5A I <sub>SW</sub> Threshold     |                                                                                                         |   |                          | 0.9                    |                      | V                    |

| Maximum Switch Duty Cycle                             | V <sub>C</sub> = 1.2V, I <sub>SW</sub> = 400mA                                                          | • | 85<br>80                 | 90                     |                      | %<br>%               |

| Minimum Boost Voltage Above Switch                    | $I_{SW} = -1.5A$ , 0°C $\leq T_A \leq 125$ °C and $-1.3A$ , $T_A < 0$ °C                                | ٠ |                          | 1.8                    | 2.7                  | V                    |

| Boost Current                                         | $I_{SW}$ = –0.5A (Note 4) $I_{SW}$ = –1.5A, 0°C $\leq$ T_A $\leq$ 125°C and –1.3A, T_A $<$ 0°C (Note 4) | • |                          | 10<br>30               | 15<br>45             | mA<br>mA             |

| SHDN Threshold Voltage                                |                                                                                                         | • | 1.27                     | 1.33                   | 1.40                 | V                    |

| SHDN Input Current (Shutting Down)                    | SHDN = 60mV Above Threshold                                                                             |   | -7                       | -10                    | -13                  | μA                   |

| SHDN Threshold Current Hysteresis                     | SHDN = 100mV Below Threshold                                                                            | ٠ | 4                        | 7                      | 10                   | μA                   |

| SYNC Threshold Voltage                                |                                                                                                         |   |                          | 1.5                    | 2.2                  | V                    |

| SYNC Input Frequency                                  |                                                                                                         |   | 1.5                      |                        | 2                    | MHz                  |

| SYNC Pin Resistance                                   | I <sub>SYNC</sub> = 1mA                                                                                 |   |                          | 20                     |                      | kΩ                   |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LT1767E is guaranteed to meet performance specifications from 0°C to 125°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** Minimum input voltage is defined as the voltage where the internal regulator enters lockout. Actual minimum input voltage to maintain a regulated output will depend on output voltage and load current. See Applications Information.

**Note 4:** Current flows into the BOOST pin only during the on period of the switch cycle.

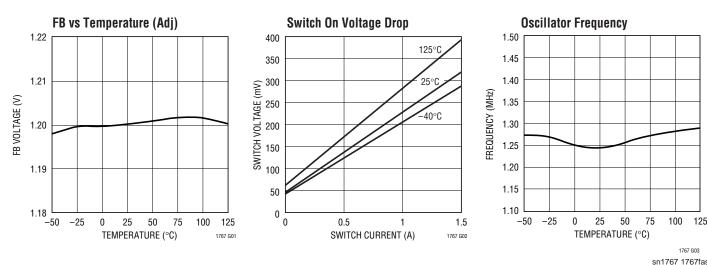

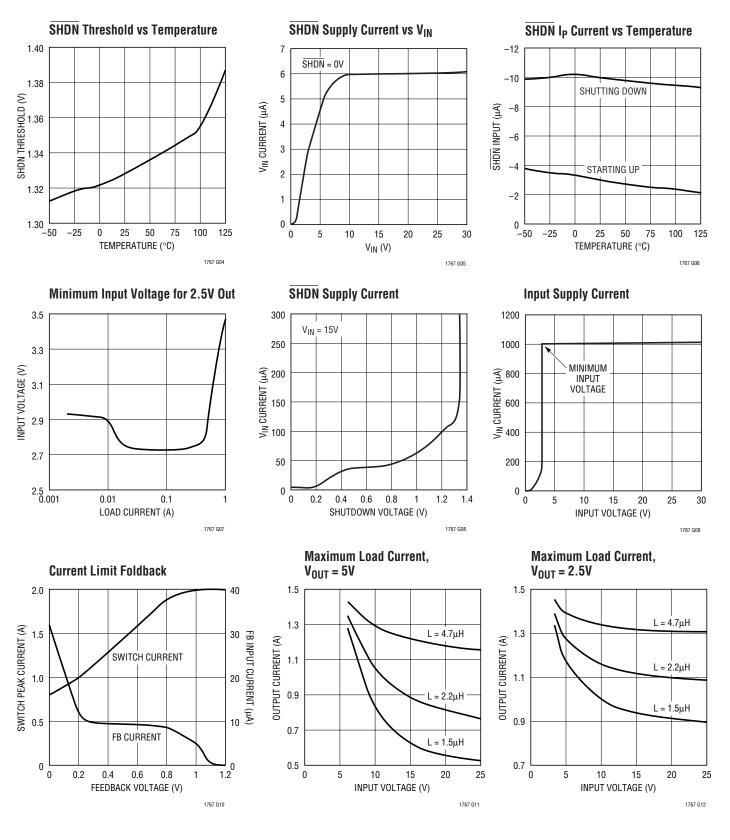

# **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

sn1767 1767fas

Downloaded from Elcodis.com electronic components distributor

### PIN FUNCTIONS

**FB**: The feedback pin is used to set output voltage using an external voltage divider that generates 1.2V at the pin with the desired output voltage. The fixed voltage 1.8V, 2.5V, 3.3V and 5V versions have the divider network included internally and the FB pin is connected directly to the output. If required, the current limit can be reduced during start up or short-circuit when the FB pin is below 0.5V (see the Current Limit Foldback graph in the Typical Performance Characteristics section). An impedance of less than 5k $\Omega$  (adjustable part only) at the FB pin is needed for this feature to operate.

**BOOST:** The BOOST pin is used to provide a drive voltage, higher than the input voltage, to the internal bipolar NPN power switch. Without this added voltage, the typical switch voltage loss would be about 1.5V. The additional boost voltage allows the switch to saturate and voltage loss approximates that of a  $0.22\Omega$  FET structure.

$V_{IN}$ : This is the collector of the on-chip power NPN switch. This pin powers the internal circuitry and internal regulator. At NPN switch on and off, high dl/dt edges occur on this pin. Keep the external bypass capacitor and catch diode close to this pin. All trace inductance in this path will create a voltage spike at switch off, adding to the V<sub>CE</sub> voltage across the internal NPN.

**GND:** The GND pin acts as the reference for the regulated output, so load regulation will suffer if the "ground" end of the load is not at the same voltage as the GND pin of the IC. This condition will occur when load current or other currents flow through metal paths between the GND pin and the load ground point. Keep the ground path short between the GND pin and the load and use a ground plane

when possible. Keep the path between the input bypass and the GND pin short. The GND pin of the MS8 package is directly attached to the internal tab. This pin should be attached to a large copper area to improve thermal resistance. The exposed pad of the MS8E package is also connected to GND. This should be soldered to a large copper area to improve its thermal resistance.

$V_{SW}$ : The switch pin is the emitter of the on-chip power NPN switch. This pin is driven up to the input pin voltage during switch on time. Inductor current drives the switch pin negative during switch off time. Negative voltage must be clamped with an external catch diode with a V<sub>BR</sub> < 0.8V.

**SYNC:** The sync pin is used to synchronize the internal oscillator to an external signal. It is directly logic compatible and can be driven with any signal between 20% and 80% duty cycle. The synchronizing range is equal to *initial* operating frequency, up to 2MHz. See Synchronization section in Applications Information for details. When not in use, this pin should be grounded.

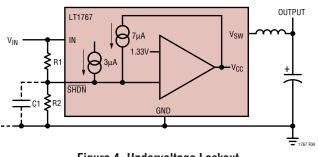

**SHDN**: The shutdown pin is used to turn off the regulator and to reduce input drain current to a few microamperes. The 1.33V threshold can function as an accurate undervoltage lockout (UVLO), preventing the regulator from operating until the input voltage has reached a predetermined level. Float or pull high to put the regulator in the operating mode.

$V_C$ : The V<sub>C</sub> pin is the output of the error amplifier and the input of the peak switch current comparator. It is normally used for frequency compensation, but can do double duty as a current clamp or control loop override. This pin sits at about 0.35V for very light loads and 0.9V at maximum load. It can be driven to ground to shut off the output.

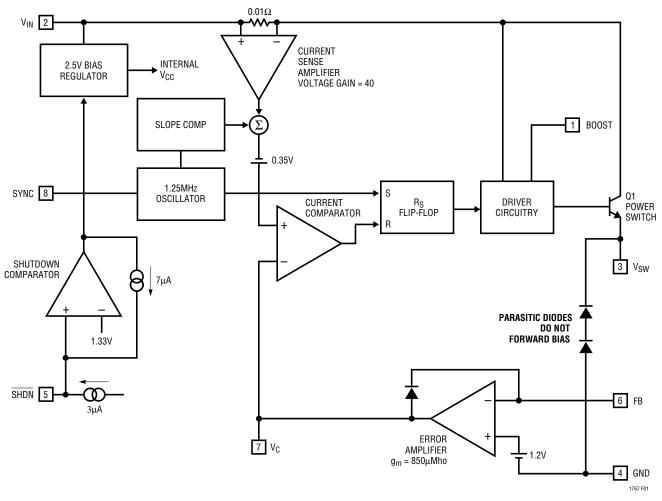

### **BLOCK DIAGRAM**

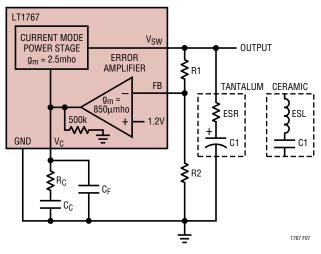

The LT1767 is a constant frequency, current mode buck converter. This means that there is an internal clock and two feedback loops that control the duty cycle of the power switch. In addition to the normal error amplifier, there is a current sense amplifier that monitors switch current on a cycle-by-cycle basis. A switch cycle starts with an oscillator pulse which sets the  $R_S$  flip-flop to turn the switch on. When switch current reaches a level set by the inverting input of the comparator, the flip-flop is reset and the switch turns off. Output voltage control is obtained by using the output of the error amplifier to set the switch current trip point. This technique means that the error amplifier commands current to be delivered to the output rather than voltage. A voltage fed system will have low phase shift up to the resonant frequency of the inductor

and output capacitor, then an abrupt 180° shift will occur. The current fed system will have 90° phase shift at a much lower frequency, but will not have the additional 90° shift until well beyond the LC resonant frequency. This makes it much easier to frequency compensate the feedback loop and also gives much quicker transient response.

High switch efficiency is attained by using the BOOST pin to provide a voltage to the switch driver which is higher than the input voltage, allowing switch to be saturated. This boosted voltage is generated with an external capacitor and diode. A comparator connected to the shutdown pin disables the internal regulator, reducing supply current.

Figure 1. Block Diagram

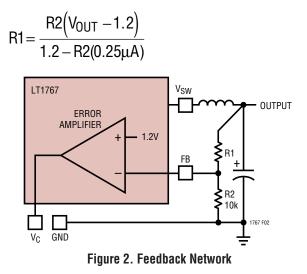

#### **FB RESISTOR NETWORK**

If an output voltage of 1.8V, 2.5V, 3.3V or 5V is required, the respective fixed option part, -1.8, -2.5, -3.3 or -5, should be used. The FB pin is tied directly to the output; the necessary resistive divider is already included on the part. For other voltage outputs, the adjustable part should be used and an external resistor divider added. The suggested resistor (R2) from FB to ground is 10k. This reduces the contribution of FB input bias current to output voltage to less than 0.25%. The formula for the resistor (R1) from V<sub>OUT</sub> to FB is:

#### **INPUT CAPACITOR**

Step-down regulators draw current from the input supply in pulses. The rise and fall times of these pulses are very fast. The input capacitor is required to reduce the voltage ripple this causes at the input of LT1767 and force the switching current into a tight local loop, thereby minimizing EMI. The RMS ripple current can be calculated from:

$$I_{\text{RIPPLE}(\text{RMS})} = I_{\text{OUT}} \sqrt{V_{\text{OUT}} (V_{\text{IN}} - V_{\text{OUT}}) / V_{\text{IN}}^{2}}$$

Higher value, lower cost ceramic capacitors are now available in smaller case sizes. These are ideal for input bypassing since their high frequency capacitive nature removes most ripple current rating and turn-on surge problems. At higher switching frequency, the energy storage requirement of the input capacitor is reduced so values in the range of 1 $\mu$ F to 4.7 $\mu$ F are suitable for most applications. Y5V or similar type ceramics can be used since the absolute value

of capacitance is less important and has no significant effect on loop stability. If operation is required close to the minimum input required by the output of the LT1767, a larger value may be required. This is to prevent excessive ripple causing dips below the minimum operating voltage, resulting in erratic operation.

If tantalum capacitors are used, values in the  $22\mu$ F to  $470\mu$ F range are generally needed to minimize ESR and meet ripple current and surge ratings. Care should be taken to ensure the ripple and surge ratings are not exceeded. The AVX TPS and Kemet T495 series are surge rated. AVX recommends derating capacitor operating voltage by 2:1 for high surge applications.

#### **OUTPUT CAPACITOR**

Unlike the input capacitor, RMS ripple current in the output capacitor is normally low enough that ripple current rating is not an issue. The current waveform is triangular, with an RMS value given by:

$$\mathsf{I}_{\mathsf{RIPPLE}(\mathsf{RMS})} = \frac{0.29(\mathsf{V}_{\mathsf{OUT}})(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}})}{(\mathsf{L})(\mathsf{f})(\mathsf{V}_{\mathsf{IN}})}$$

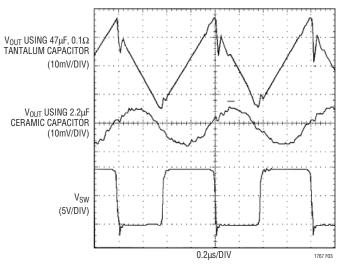

The LT1767 will operate with both ceramic and tantalum output capacitors. Ceramic capacitors are generally chosen for their small size, very low ESR (effective series resistance), and good high frequency operation, reducing output ripple voltage. Their low ESR removes a useful zero in the loop frequency response, common to tantalum capacitors. To compensate for this, the V<sub>C</sub> loop compensation pole frequency must typically be reduced by a factor of 10. Typical ceramic output capacitors are in the 1 $\mu$ F to 10 $\mu$ F range. Since the absolute value of capacitance defines the pole frequency of the output stage, an X7R or X5R type ceramic, which have good temperature stability, is recommended.

Tantalum capacitors are usually chosen for their bulk capacitance properties, useful in high transient load applications. ESR rather than capacitive value defines output ripple at 1.25MHz. Typical LT1767 applications require a tantalum capacitor with less than  $0.3\Omega$  ESR at  $22\mu$ F to  $500\mu$ F, see Table 2.

Table 2. Surface Mount Solid Tantalum Capacitor ESR and Ripple Current

| E Case Size           | ESR (Max, $\Omega$ ) | Ripple Current (A) |  |  |  |

|-----------------------|----------------------|--------------------|--|--|--|

| AVX TPS, Sprague 593D | 0.1 to 0.3           | 0.7 to 1.1         |  |  |  |

| AVX TAJ               | 0.7 to 0.9 0.4       |                    |  |  |  |

| D Case Size           |                      |                    |  |  |  |

| AVX TPS, Sprague 593D | 0.1 to 0.3           | 0.7 to 1.1         |  |  |  |

| C Case Size           |                      |                    |  |  |  |

| AVX TPS               | 0.2 (typ)            | 0.5 (typ)          |  |  |  |

Figure 3 shows a comparison of output ripple for a ceramic and tantalum capacitor at 200mA ripple current.

# INDUCTOR CHOICE AND MAXIMUM OUTPUT CURRENT

Maximum output current for a buck converter is equal to the maximum switch rating  $(I_P)$  minus one half peak to peak inductor current. In past designs, the maximum switch current has been reduced by the introduction of slope compensation. Slope compensation is required at duty cycles above 50% to prevent an affect called subharmonic oscillation (see Application Note 19 for details). The LT1767 has a new circuit technique that maintains a constant switch current rating at all duty cycles. (Patent Pending)

For most applications, the output inductor will be in the  $1\mu$ H to  $10\mu$ H range. Lower values are chosen to reduce the physical size of the inductor, higher values allow higher output currents due to reduced peak to peak ripple current,

and reduces the current at which discontinuous operation occurs. The following formula gives maximum output current for continuous mode operation, implying that the peak to peak ripple (2x the term on the right) is less than the maximum switch current.

Discontinuous operation occurs when

$$I_{OUT(DIS)} = \frac{(V_{OUT})}{2(L)(f)}$$

For  $V_{IN} = 8V$ ,  $V_{OUT} = 5V$  and  $L = 3.3\mu H$ ,

$$I_{OUT(MAX)} = 1.5 - \frac{(5)(8-5)}{2(3.3 \cdot 10^{-6})(1.25 \cdot 10^{6})(8)}$$

$$= 1.5 - 0.23 = 1.27 \text{ A}$$

Note that the worst case (minimum output current available) condition is at the maximum input voltage. For the same circuit at 15V, maximum output current would be only 1.1A.

When choosing an inductor, consider maximum load current, core and copper losses, allowable component height, output voltage ripple, EMI, fault current in the inductor, saturation, and of course, cost. The following procedure is suggested as a way of handling these somewhat complicated and conflicting requirements.

1. Choose a value in microhenries from the graphs of maximum load current. Choosing a small inductor with lighter loads may result in discontinuous mode of operation, but the LT1767 is designed to work well in either mode.

Assume that the average inductor current is equal to load current and decide whether or not the inductor must withstand continuous fault conditions. If maximum load current is 0.5A, for instance, a 0.5A inductor may not survive a continuous 2A overload condition. Also, the instantaneous application of input or release from shutdown, at high input voltages, may cause

saturation of the inductor. In these applications, the soft-start circuit shown in Figure 10 should be used.

2. Calculate peak inductor current at full load current to ensure that the inductor will not saturate. Peak current can be significantly higher than output current, especially with smaller inductors and lighter loads, so don't omit this step. Powdered iron cores are forgiving because they saturate softly, whereas ferrite cores saturate abruptly. Other core materials fall somewhere in between.

$$I_{\text{PEAK}} = I_{\text{OUT}} + \frac{V_{\text{OUT}} \left( V_{\text{IN}} - V_{\text{OUT}} \right)}{2 \left( L \right) \left( f \right) \left( V_{\text{IN}} \right)}$$

V<sub>IN</sub> = Maximum input voltage f = Switching frequency, 1.25MHz

3. Decide if the design can tolerate an "open" core geometry like a rod or barrel, which have high magnetic field radiation, or whether it needs a closed core like a toroid to prevent EMI problems. This is a tough decision because the rods or barrels are temptingly cheap and small and there are no helpful guidelines to calculate when the magnetic field radiation will be a problem.

#### Table 3

| PART NUMBER  | VALUE (uH) | I <sub>SAT</sub> (Amps) | DCR ( $\Omega$ ) | HEIGHT (mm) |  |  |

|--------------|------------|-------------------------|------------------|-------------|--|--|

| Coiltronics  |            |                         |                  |             |  |  |

| TP1-2R2      | 2.2        | 1.3                     | 0.188            | 1.8         |  |  |

| TP2-2R2      | 2.2        | 1.5                     | 0.111            | 2.2         |  |  |

| TP3-4R7      | 4.7        | 1.5                     | 0.181            | 2.2         |  |  |

| TP4- 100     | 10         | 1.5                     | 0.146            | 3.0         |  |  |

| Murata       |            |                         |                  |             |  |  |

| LQH1C1R0M04  | 1.0        | 0.51                    | 0.28             | 1.8         |  |  |

| LQH3C1R0M24  | 1.0        | 1.0                     | 0.06             | 2.0         |  |  |

| LQH3C2R2M24  | 2.2        | 0.79                    | 0.1              | 2.0         |  |  |

| LQH4C1R5M04  | 1.5        | 1.0                     | 0.09             | 2.6         |  |  |

| Sumida       |            |                         |                  |             |  |  |

| CD73- 100    | 10         | 1.44                    | 0.080            | 3.5         |  |  |

| CDRH4D18-2R2 | 2.2        | 1.32                    | 0.058            | 1.8         |  |  |

| CDRH5D18-6R2 | 6.2        | 1.4                     | 0.071            | 1.8         |  |  |

| CDRH5D28-100 | 10         | 1.3                     | 0.048            | 2.8         |  |  |

4. After making an initial choice, consider the secondary things like output voltage ripple, second sourcing, etc. Use the experts in the Linear Technology's applications department if you feel uncertain about the final choice. They have experience with a wide range of inductor types and can tell you about the latest developments in low profile, surface mounting, etc.

### **CATCH DIODE**

The suggested catch diode (D1) is a UPS120 Schottky, or its Motorola equivalent, MBRM120LTI/MBRM130LTI. It is rated at 2A average forward current and 20V/30V reverse voltage. Typical forward voltage is 0.5V at 1A. The diode conducts current only during switch off time. Peak reverse voltage is equal to regulator input voltage. Average forward current in normal operation can be calculated from:

$$I_{D(AVG)} = \frac{I_{OUT}(V_{IN} - V_{OUT})}{V_{IN}}$$

### **BOOST PIN**

For most applications, the boost components are a 0.1 µF capacitor and a CMDSH-3 diode. The anode is typically connected to the regulated output voltage to generate a voltage approximately  $V_{OUT}$  above  $V_{IN}$  to drive the output stage. The output driver requires at least 2.7V of headroom throughout the on period to keep the switch fully saturated. However, the output stage discharges the boost capacitor during the on time. If the output voltage is less than 3.3V, it is recommended that an alternate boost supply is used. The boost diode can be connected to the input, although, care must be taken to prevent the 2x V<sub>IN</sub> boost voltage from exceeding the BOOST pin absolute maximum rating. The additional voltage across the switch driver also increases power loss, reducing efficiency. If available, an independent supply can be used with a local bypass capacitor.

A  $0.1 \mu F$  boost capacitor is recommended for most applications. Almost any type of film or ceramic capacitor is

suitable, but the ESR should be  $<1\Omega$  to ensure it can be fully recharged during the off time of the switch. The capacitor value is derived from worst-case conditions of 700ns on-time, 50mA boost current, and 0.7V discharge ripple. This value is then guard banded by 2x for secondary factors such as capacitor tolerance, ESR and temperature effects. The boost capacitor value could be reduced under less demanding conditions, but this will not improve circuit operation or efficiency. Under low input voltage and low load conditions, a higher value capacitor will reduce discharge ripple and improve start up operation.

### SHUTDOWN AND UNDERVOLTAGE LOCKOUT

Figure 4 shows how to add undervoltage lockout (UVLO) to the LT1767. Typically, UVLO is used in situations where the input supply is *current limited*, or has a relatively high source resistance. A switching regulator draws constant power from the source, so source current increases as source voltage drops. This looks like a negative resistance load to the source and can cause the source to current limit or latch low under low source voltage conditions. UVLO prevents the regulator from operating at source voltages where these problems might occur.

Figure 4. Undervoltage Lockout

An internal comparator will force the part into shutdown below the minimum  $V_{IN}$  of 2.6V. This feature can be used to prevent excessive discharge of battery-operated systems. If an adjustable UVLO threshold is required, the shutdown pin can be used. The threshold voltage of the shutdown pin comparator is 1.33V. A  $3\mu$ A internal current source defaults the open pin condition to be operating (see Typical Performance Graphs). Current hysteresis is added above the SHDN threshold. This can be used to set voltage hysteresis of the UVLO using the following:

$$R1 = \frac{V_{H} - V_{L}}{7\mu A}$$

$$R2 = \frac{1.33V}{\frac{(V_{H} - 1.33V)}{R1} + 3\mu A}$$

$$V_{H} - \text{Turn-on threshold}$$

V<sub>L</sub> – Turn-off threshold

Example: switching should not start until the input is above 4.75V and is to stop if the input falls below 3.75V.

$$V_{H} = 4.75V$$

$$V_{L} = 3.75V$$

$$R1 = \frac{4.75V - 3.75V}{7\mu A} = 143k$$

$$R2 = \frac{1.33V}{\frac{(4.75V - 1.33V)}{143k}} = 49.4k$$

Keep the connections from the resistors to the SHDN pin short and make sure that the interplane or surface capacitance to the switching nodes are minimized. If high resistor values are used, the SHDN pin should be bypassed with a 1nF capacitor to prevent coupling problems from the switch node.

### **SYNCHRONIZATION**

The SYNC pin, is used to synchronize the internal oscillator to an external signal. The SYNC input must pass from a logic level low, through the maximum synchronization threshold with a duty cycle between 20% and 80%. The input can be driven directly from a logic level output. The synchronizing range is equal to *initial* operating frequency up to 2MHz. This means that *minimum* practical sync frequency is equal to the worst-case *high* self-oscillating frequency (1.5MHz), not the typical operating frequency of 1.25MHz. Caution should be used when synchronizing above 1.6MHz because at higher sync frequencies the amplitude of the internal slope compensation used to

prevent subharmonic switching is reduced. This type of subharmonic switching only occurs at input voltages less than twice output voltage. Higher inductor values will tend to eliminate this problem. See Frequency Compensation section for a discussion of an entirely different cause of subharmonic switching before assuming that the cause is insufficient slope compensation. Application Note 19 has more details on the theory of slope compensation.

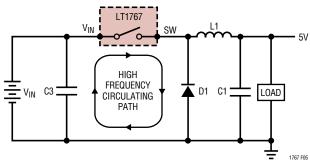

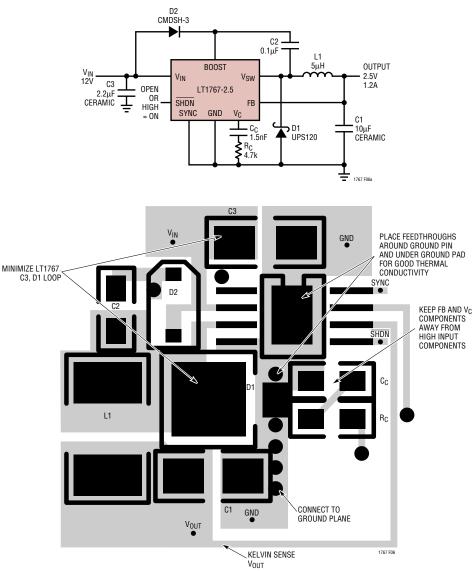

#### LAYOUT CONSIDERATIONS

As with all high frequency switchers, when considering layout, care must be taken in order to achieve optimal electrical, thermal and noise performance. For maximum efficiency, switch rise and fall times are typically in the nanosecond range. To prevent noise both radiated and conducted, the high speed switching current path, shown in Figure 5, must be kept as short as possible. This is implemented in the suggested layout of Figure 6. Shortening this path will also reduce the parasitic trace inductance of approximately 25nH/inch. At switch off, this parasitic inductance produces a flyback spike across the LT1767 switch. When operating at higher currents and input voltages, with poor layout, this spike can generate voltages across the LT1767 that may exceed its absolute maximum rating. A ground plane should always be used under the switcher circuitry to prevent interplane coupling and overall noise.

Figure 5. High Speed Switching Path

The V<sub>C</sub> and FB components should be kept as far away as possible from the switch and boost nodes. The LT1767 pinout has been designed to aid in this. The ground for these components should be separated from the switch current path. Failure to do so will result in poor stability or subharmonic like oscillation.

Board layout also has a significant effect on thermal resistance. Soldering the exposed pad to as large a copper area as possible and placing feedthroughs under the pad to a ground plane, will reduce die temperature and increase the power capacity of the LT1767. For the nonexposed package, Pin 4 is connected directly to the pad inside the package. Similar treatment of this pin will result in lower die temperatures.

#### THERMAL CALCULATIONS

Power dissipation in the LT1767 chip comes from four sources: switch DC loss, switch AC loss, boost circuit current, and input quiescent current. The following formulas show how to calculate each of these losses. These formulas assume continuous mode operation, so they should not be used for calculating efficiency at light load currents.

Switch loss:

$$P_{SW} = \frac{R_{SW} (I_{OUT})^2 (V_{OUT})}{V_{IN}} + 17 ns (I_{OUT}) (V_{IN}) (f)$$

Boost current loss for  $V_{BOOST} = V_{OUT}$ :

$$P_{BOOST} = \frac{V_{OUT}^{2} (I_{OUT} / 50)}{V_{IN}}$$

Quiescent current loss:

$$P_Q = V_{IN}(0.001)$$

$R_{SW}$  = Switch resistance ( $\approx 0.27\Omega$  when hot) 17ns = Equivalent switch current/voltage overlap time f = Switch frequency

Example: with  $V_{IN} = 10V$ ,  $V_{OUT} = 5V$  and  $I_{OUT} = 1A$ :

$$P_{SW} = \frac{(0.27)(1)^{2}(5)}{10} + (17 \cdot 10^{-9})(1)(10)(1.25 \cdot 10^{6})$$

$$= 0.135 + 0.21 = 0.34W$$

$$P_{BOOST} = \frac{(5)^{2}(1/50)}{10} = 0.05W$$

$$P_{Q} = 10(0.001) = 0.01W$$

Figure 6. Typical Application and Suggested Layout (Topside Only Shown)

Total power dissipation is 0.34 + 0.05 + 0.01 = 0.4W.

Thermal resistance for LT1767 package is influenced by the presence of internal or backside planes. With a full plane under the package, thermal resistance for the exposed pad package will be about 40°C/W. No plane will increase resistance to about 150°C/W. To calculate die temperature, use the appropriate thermal resistance number and add in worst-case ambient temperature:

$T_{J} = T_{A} + \theta_{JA} (P_{TOT})$

When estimating ambient, remember the nearby catch diode and inductor will also be dissipating power.

$$P_{\text{DIODE}} = \frac{\left(V_{\text{F}}\right)\left(V_{\text{IN}} - V_{\text{OUT}}\right)\left(I_{\text{LOAD}}\right)}{V_{\text{IN}}}$$

$V_F$  = Forward voltage of diode (assume 0.5V at 1A)

$$P_{\text{DIODE}} = \frac{(0.5)(12-5)(1)}{12} = 0.29W$$

Notice that the catch diode's forward voltage contributes a significant loss in the overall system efficiency. A larger, lower  $V_F$  diode can improve efficiency by several percent.

$P_{INDUCTOR} = (I_{LOAD}) (L_{DCR})$

$L_{DCR}$  = Inductor DC resistance (assume 0.1 $\Omega$ )

$P_{INDUCTOR} = (1) (0.1) = 0.1W$

Typical thermal resistance of the board is 35°C/W. At an ambient temperature of 65°C,

$T_j = 65 + 40 (0.4) + 35 (0.39) = 95^{\circ}C$

If a true die temperature is required, a measurement of the SYNC to GND pin resistance can be used. The SYNC pin resistance across temperature must first be calibrated, with no device power, in an oven. The same measurement can then be used in operation to indicate the die temperature.

#### FREQUENCY COMPENSATION

Before starting on the theoretical analysis of frequency response, the following should be remembered – the worse the board layout, the more difficult the circuit will be to stabilize. This is true of almost all high frequency analog circuits, read the 'LAYOUT CONSIDERATIONS' section first. Common layout errors that appear as stability problems are distant placement of input decoupling capacitor and/or catch diode, and connecting the V<sub>C</sub> compensation to a ground track carrying significant switch current. In addition, the theoretical analysis considers only first order non-ideal component behavior. For these reasons, it is important that a final stability check is made with production layout and components.

The LT1767 uses current mode control. This alleviates many of the phase shift problems associated with the inductor. The basic regulator loop is shown in Figure 7, with both tantalum and ceramic capacitor equivalent circuits. The LT1767 can be considered as two  $g_m$  blocks, the error amplifier and the power stage.

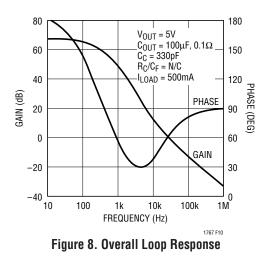

Figure 8 shows the overall loop response with a 330pF  $V_C$  capacitor and a typical 100 $\mu F$  tantalum output capacitor. The response is set by the following terms:

Figure 7. Model for Loop Response

#### Error amplifier:

DC gain set by  $g_m$  and  $R_L = 850\mu \cdot 500k = 425$ . Pole set by  $C_F$  and  $R_L = (2\pi \cdot 500k \cdot 330p)^{-1} = 965Hz$ . Unity-gain set by  $C_F$  and  $g_m = (2\pi \cdot 330p \cdot 850\mu^{-1})^{-1} = 410kHz$ .

#### Power stage:

DC gain set by  $g_m$  and  $R_L$  (assume  $10\Omega$ ) = 2.5 • 10 = 25. Pole set by  $C_{OUT}$  and  $R_L = (2\pi • 100\mu • 10)^{-1} = 159$ Hz. Unity-gain set by  $C_{OUT}$  and  $g_m = (2\pi • 100\mu • 2.5^{-1})^{-1} = 3.98$ kHz.

### Tantalum output capacitor:

Zero set by  $C_{OUT}$  and  $C_{ESR} = (2\pi \cdot 100\mu \cdot 0.1)^{-1} = 15.9$  kHz.

The zero produced by the ESR of the tantalum output capacitor is very useful in maintaining stability. Ceramic output capacitors do not have a zero due to very low ESR, but are dominated by their ESL. They form a notch in the 1MHz to 10MHz range. Without this zero, the  $V_C$  pole must be made dominant. A typical value of 2.2nF will achieve this.

If better transient response is required, a zero can be added to the loop using a resistor ( $R_C$ ) in series with the compensation capacitor. As the value of  $R_C$  is increased, transient response will generally improve, but two effects limit its value. First, the combination of output capacitor ESR and a large  $R_C$  may stop loop gain rolling off altogether. Second, if the loop gain is not rolled sufficiently at the switching frequency, output ripple will perturb the  $V_C$ pin enough to cause unstable duty cycle switching similar to subharmonic oscillation. This may not be apparent at the output. Small signal analysis will not show this since a continuous time system is assumed. If needed, an additional capacitor ( $C_F$ ) can be added to form a pole at typically one fifth the switching frequency (If  $R_C = \sim 5k$ ,  $C_F = \sim 100pF$ ).

When checking loop stability, the circuit should be operated over the application's full voltage, current and temperature range. Any transient loads should be applied and the output voltage monitored for a well-damped behavior. See Application Note 76 for more details.

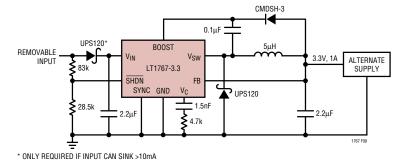

### CONVERTER WITH BACKUP OUTPUT REGULATOR

In systems with a primary and backup supply, for example, a battery powered device with a wall adapter input, the output of the LT1767 can be held up by the backup supply with its input disconnected. In this condition, the SW pin will source current into the V<sub>IN</sub> pin. If the SHDN pin is held at ground, only the shut down current of  $6\mu$ A will be pulled via the SW pin from the second supply. With the SHDN pin floating, the LT1767 will consume its quiescent operating current of 1mA. The V<sub>IN</sub> pin will also source current to any other components connected to the input line. If this load is greater than 10mA or the input could be shorted to ground, a series Schottky diode must be added, as shown in Figure 9. With these safeguards, the output can be held at voltages up to the V<sub>IN</sub> absolute maximum rating.

### **BUCK CONVERTER WITH ADJUSTABLE SOFT-START**

Large capacitive loads or high input voltages can cause high input currents at start-up. Figure 10 shows a circuit that limits the dv/dt of the output at start-up, controlling the capacitor charge rate. The buck converter is a typical configuration with the addition of R3, R4,  $C_{SS}$  and Q1. As the output starts to rise, Q1 turns on, regulating switch current via the V<sub>C</sub> pin to maintain a constant dv/dt at the output. Output rise time is controlled by the current through  $C_{SS}$  defined by R4 and Q1's V<sub>BE</sub>. Once the output is in regulation, Q1 turns off and the circuit operates normally. R3 is transient protection for the base of Q1.

$$RiseTime = \frac{(R4)(C_{SS})(V_{OUT})}{(V_{BE})}$$

Using the values shown in Figure 10,

RiseTime =

$$\frac{(47 \cdot 10^3)(15 \cdot 10^{-9})(5)}{0.7} = 5$$

ms

The ramp is linear and rise times in the order of 100ms are possible. Since the circuit is voltage controlled, the ramp rate is unaffected by load characteristics and maximum output current is unchanged. Variants of this circuit can be used for sequencing multiple regulator outputs.

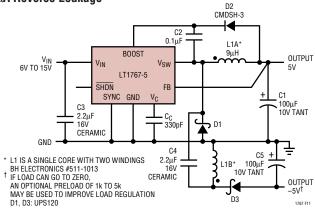

#### **Dual Output SEPIC Converter**

The circuit in Figure 11 generates both positive and negative 5V outputs with a single piece of magnetics. The two inductors shown are actually just two windings on a standard B H Electronics inductor. The topology for the 5V output is a standard buck converter. The -5V topology would be a simple flyback winding coupled to the buck converter if C4 were not present. C4 creates a SEPIC (single-ended primary inductance converter) topology which improves regulation and reduces ripple current in L1. Without C4, the voltage swing on L1B compared to L1A would vary due to relative loading and coupling losses. C4 provides a low impedance path to maintain an equal voltage swing in L1B, improving regulation. In a flyback converter, during switch on time, all the converter's energy is stored in L1A only, since no current flows in L1B. At switch off, energy is transferred by magnetic coupling into L1B, powering the -5V rail. C4 pulls L1B positive

during switch on time, causing current to flow, and energy to build in L1B and C4. At switch off, the energy stored in both L1B and C4 supply the -5V rail. This reduces the

current in L1A and changes L1B current waveform from square to triangular. For details on this circuit, including maximum output currents, see Design Note 100.

#### Figure 9. Dual Source Supply with $6\mu A$ Reverse Leakage

Figure 10. Buck Converter with Adjustable Soft-Start

#### Figure 11. Dual Output SEPIC Converter

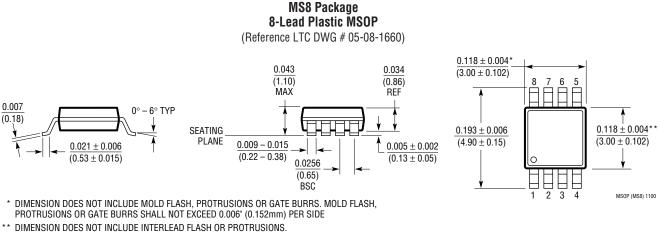

### PACKAGE DESCRIPTION

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

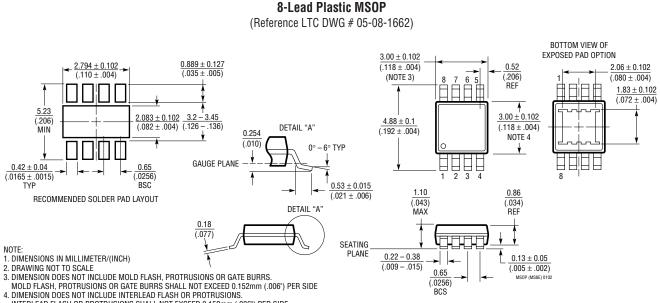

## PACKAGE DESCRIPTION

MS8E Package

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

### **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                                                                             | COMMENTS                                                                                                                |  |

|---------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| LT1370        | High Efficiency DC/DC Converter                                                         | 42V, 6A, 500kHz Switch                                                                                                  |  |

| LT1371        | High Efficiency DC/DC Converter                                                         | 35V, 3A, 500kHz Switch                                                                                                  |  |

| LT1372/LT1377 | 500kHz and 1MHz High Efficiency 1.5A Switching Regulators                               | Boost Topology                                                                                                          |  |

| LT1374        | High Efficiency Step-Down Switching Regulator                                           | 25V, 4.5A, 500kHz Switch                                                                                                |  |

| LT1375/LT1376 | 1.5A Step-Down Switching Regulators                                                     | 500kHz, Synchronizable in SO-8 Package                                                                                  |  |

| LT1507        | 1.5A Step-Down Switching Regulator                                                      | 500kHz, 4V to 16V Input, SO-8 Package                                                                                   |  |

| LT1576        | 1.5A Step-Down Switching Regulator                                                      | 200kHz, Reduced EMI Generation                                                                                          |  |

| LT1578        | 1.5A Step-Down Switching Regulator                                                      | 200kHz, Reduced EMI Generation                                                                                          |  |

| LT1616        | 600mA Step-Down Switching Regulator                                                     | 1.4MHz, 4V to 25V Input, SOT-23 Package                                                                                 |  |

| LT1676/LT1776 | Wide Input Range Step-Down Switching Regulators                                         | 60V Input, 700mA Internal Switches                                                                                      |  |

| LTC1765       | 1.25MHz, 3A Wide Input Range Step-Down DC/DC                                            | V <sub>TH</sub> = 3V to 25V, SO-8 and TSSOP-16E Packages                                                                |  |

| LTC1877       | High Efficiency Monolithic Step-Down Regulator                                          | 550kHz, MS8, V <sub>IN</sub> Up to 10V, $I_Q$ =10 $\mu$ A, $I_{OUT}$ to 600mA at V <sub>IN</sub> = 5V                   |  |

| LTC1878       | High Efficiency Monolithic Step-Down Regulator                                          | 550kHz, MS8, V <sub>IN</sub> Up to 6V, I <sub>Q</sub> = 10 $\mu$ A, I <sub>OUT</sub> to 600mA at V <sub>IN</sub> = 3.3V |  |

| LTC3401       | Single Cell, High Current (1A), Micropower, Synchronous 3MHz<br>Step-Up DC/DC Converter | V <sub>IN</sub> = 0.5V to 5V, Up to 97% Efficiency Synchronizable<br>Oscillator from 100kHz to 3MHz                     |  |

| LTC3402       | Single Cell, High Current (2A), Micropower, Synchronous 3MHz<br>Step-Up DC/DC Converter | Iz V <sub>IN</sub> = 0.7V to 5V, Up to 95% Efficiency Synchronizable<br>Oscillator from 100kHz to 3MHz                  |  |

| LTC3404       | 1.4MHz High Efficiency, Monolithic Synchronous Step-Down<br>Regulator                   | Up to 95% Efficiency, 100% Duty Cycle, IQ = 10 $\mu$ A, V <sub>IN</sub> = 2.65V to 6V                                   |  |

Burst Mode is a trademark of Linear Technology Corporation.