AS1364 DataSheet

# 1A, Low-Dropout Linear Voltage Regulator

# 1 General Description

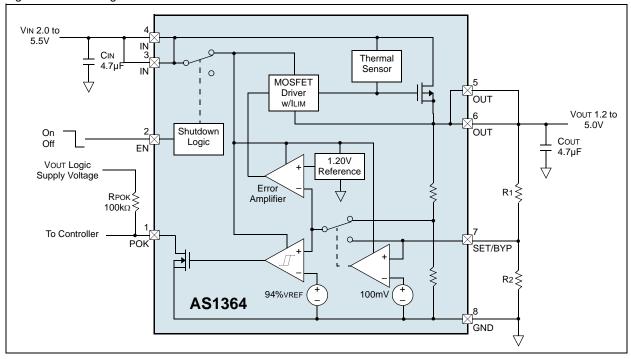

The AS1364 is a low-dropout linear regulator (LDO) designed to operate from 2V to 5.5V input, that delivers a wide range of highly accurate (±0.75%) factory-trimmed output voltages as well as adjustable output voltages (using an external resistor-divider network).

The ultra-low dropout device requires only 140mV dropout voltage while delivering a guaranteed 1A load current and is therefore perfectly suited for battery-operated portable applications.

Additionally the AS1364 offers extremly low 10 $\mu$ VRMs (100Hz to 100kHz) or 45 $\mu$ VRMs (10Hz to 1MHz) output voltage noise.

Table 1. Standard Products

| Model     | <b>Output Type</b> | ВҮР | SET |

|-----------|--------------------|-----|-----|

| AS1364-AD | Adjustable         | No  | Yes |

| AS1364    | Fixed              | Yes | No  |

The device features an internal PMOS pass transistor (for a low supply current of only 35 $\mu$ A), reset output, a low-power shutdown mode, and protection from short-circuit and thermal-overload conditions.

The AS1364 is available in an 8-pin TDFN 3x3mm package.

# 2 Key Features

Guaranteed Output Current: 1A

■ Low Dropout: 140mV @ 1A

Output Voltage Accuracy: Up to ±0.75%

■ 2.0 to 5.5V Input Voltage

■ Fixed VouT: 1.2 to 5.0V

■ Adjustable VouT: 1.2 to 5.0V

■ Low Ground Current: 35µA

Low Shutdown Current: 10nA

■ Low Output Noise: 45µVRMS (from 10Hz to 1MHz)

■ Thermal Overload Protection

Output Current Limit

■ 8-pin TDFN 3x3mm Package

# 3 Applications

The device is ideal for laptops, PDAs, portable audio devices, mobile phones, cordless phones, and any other battery-operated portable device.

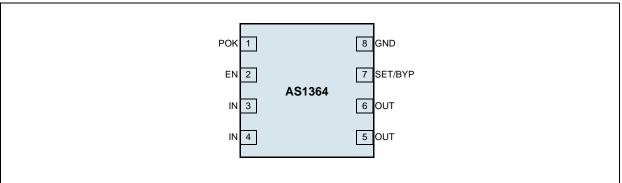

## 4 Pinout

## **Pin Assignments**

Figure 2. Pin Assignments (Top View)

## **Pin Descriptions**

Table 2. Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | POK      | <b>Note:</b> Open-Drain POK Output. POK remains low while VouT is below the POK threshold. Connect a $100k\Omega$ pull-up resistor from this pin to OUT to obtain an output voltage (see Figure 1 on page 1).                                                                                                                                            |

| 2          | EN       | Active-Low Shutdown Input. A logic low disables the output and reduces the supply current to 0.1µA. In shutdown, the POK output is low and OUT high impedance.  VDD: Normal operation.  GND: Shutdown.                                                                                                                                                   |

| 3, 4       | IN       | <b>2.0V to 5.5V Supply Voltage.</b> Bypass with a 4.7μF input capacitor to GND (see Capacitor Selection and Regulator Stability on page 11). These inputs are internally connected, but they also must be externally connected for proper operation.                                                                                                     |

| 5, 6       | OUT      | <b>Regulator Output</b> . Bypass with a 4.7µF low-ESR output capacitor to GND. Connect the OUT pins together externally.                                                                                                                                                                                                                                 |

| 7          | SET/BYP  | Voltage-Setting Input. Connect to GND to select the factory-preset output voltage. Connect this pin to an external resistor-divider for adjustable-output operation (see Figure 1 on page 1). (AS1364-AD only)  Bypass Pin. Connect a 10nF capacitor from this pin to OUT to improve PSRR and noise performance. (AS1364-AD does not offer this feature) |

| 8          | GND      | Ground                                                                                                                                                                                                                                                                                                                                                   |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3. Absolute Maximum Ratings

| Parameter                     | Min  | Max          | Units | Comments                                                                                                                                                                                                                                                                            |

|-------------------------------|------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN, EN, POK to GND            | -0.3 | +7           | V     |                                                                                                                                                                                                                                                                                     |

| OUT, SET/BYP to GND           | -0.3 | VIN +<br>0.3 | V     |                                                                                                                                                                                                                                                                                     |

| Output Short-Circuit Duration |      | Infinite     |       |                                                                                                                                                                                                                                                                                     |

| Thermal Resistance ⊕JA        |      | 36.3         | °C/W  | on PCB                                                                                                                                                                                                                                                                              |

| ESD                           |      | 2            | kV    | HBM MIL-Std. 883E 3015.7 methods                                                                                                                                                                                                                                                    |

| Latch-Up                      | -100 | +100         | mA    | JEDEC 78                                                                                                                                                                                                                                                                            |

| Operating Temperature Range   | -40  | +85          | °C    |                                                                                                                                                                                                                                                                                     |

| Storage Temperature Range     | -65  | +150         | °C    |                                                                                                                                                                                                                                                                                     |

| Junction Temperature          |      | +150         | °C    |                                                                                                                                                                                                                                                                                     |

| Package Body Temperature      |      | +260         | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

## **6 Electrical Characteristics**

VIN = VOUT + 500mV or VIN = +2.0V (whichever is greater),  $CIN = COUT = 4.7\mu$ F, EN = IN, TAMB = -40 to  $+85^{\circ}$ C (unless otherwise specified). Typical values are at  $TAMB = +25^{\circ}$ C.

Table 4. Electrical Characteristics

| Symbol         | Parameter                                   | Condition                                       |        | Тур  | Max    | Unit    |  |

|----------------|---------------------------------------------|-------------------------------------------------|--------|------|--------|---------|--|

| VIN            | Input Voltage                               |                                                 | 2.0    |      | 5.5    | V       |  |

| Vpor           | Power On Reset                              | Falling, 75mV hysteresis                        | 1.79   | 1.87 | 1.95   | V       |  |

|                |                                             | IOUT = 250mA, TAMB = +25°C                      | -0.75  |      | +0.75  | %       |  |

|                | Output Voltage Accuracy<br>(Preset Mode)    | IOUT = 250mA                                    | -1.5   |      | +1.5   |         |  |

|                | (i reset Mode)                              | IOUT = 1mA to 1A, $VIN > (VOUT + 0.5V)^{1}$     |        |      | +2     |         |  |

| Vout           | Adjustable Output Voltage<br>Range          |                                                 | 1.2    |      | 5.0    | V       |  |

| VSET/BYP       | SET/BYP Voltage Threshold (Adjustable Mode) | VIN = 2.5V, IOUT = 250mA,<br>VOUT set to 2.0V   | 1.17   | 1.20 | 1.23   | V       |  |

| Іоит           | Guaranteed Output Current (RMS)             | VIN ≥ 2.0V                                      | 1      |      |        | А       |  |

| ILIMIT         | Short-Circuit Current Limit                 | $Vout = 0$ , $Vin \ge 2.0V$                     | 1.1    | 1.5  | 2.3    | Α       |  |

|                | In-Regulation Current Limit                 | Vout > 96% of nominal value, Vin $\geq 2.0V$    |        | 1.5  |        | Α       |  |

|                | SET/BYP Threshold                           |                                                 | 50     | 100  | 150    | mV      |  |

| ISET           | SET/BYP Input Bias Current                  | VSET/BYP = 1.20V                                | -100   |      | +100   | nA      |  |

| IQ             | Ground-Pin Current                          | Ιουτ = 100μΑ                                    |        | 35   | 150    |         |  |

| IQ             | Ground-Pin Current                          | IOUT = 1A                                       |        | 75   | 200    | μA      |  |

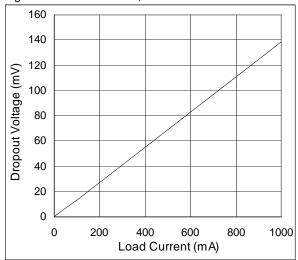

| VIN -          | 2                                           | IOUT = 250mA, VOUT = 3.3V                       |        | 35   | 85     | mV      |  |

| Vout           | Dropout Voltage <sup>2</sup>                | IOUT = 1A, VOUT = 3.3V                          |        | 140  | 320    |         |  |

| $\Delta V$ LNR | Line Regulation                             | VIN from (VOUT + 100mV) to 5.5V,<br>ILOAD = 5mA | -0.125 |      | +0.125 | %/V     |  |

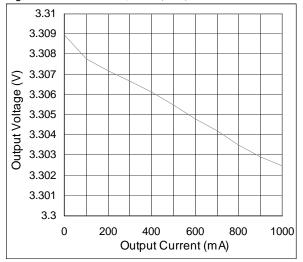

| $\Delta VLDR$  | Load Regulation                             | egulation Iout = 1mA to 1A                      |        |      | 0.001  | %/mA    |  |

|                |                                             | f = 1kHz, Iout = 10mA, CBYP = 10nF              |        | 78   |        |         |  |

|                |                                             | f = 1kHz, Iout = 10mA                           |        | 72   |        |         |  |

| PSRR           | Dinala Daiastian                            | f = 10kHz, IOUT = 10mA, CBYP = 10nF             | 75     |      |        | dB      |  |

| FORK           | Ripple Rejection                            | f = 10kHz, IouT = 10mA                          |        | 65   |        | иь      |  |

|                |                                             | f = 100kHz, Iout = 10mA, CBYP = 10nF            |        | 54   |        |         |  |

|                |                                             | f = 100kHz, Iout = 10mA                         |        | 46   |        | 1       |  |

|                |                                             | 100Hz to 100kHz, Cout = 3.3μF,<br>CBYP = 10nF;  | 10     |      |        |         |  |

|                | Output Voltage Noise                        | 100Hz to 100kHz, Couτ = 3.3μF;                  |        | 50   |        | μVRMS   |  |

|                | Output voitage Noise                        | 10Hz to 1MHz, Cout = 3.3μF,<br>CBYP = 10nF;     |        | 45   |        | μνκινιδ |  |

|                |                                             | 10Hz to 1MHz, Couт = 3.3µF;                     | 70     |      |        |         |  |

Table 4. Electrical Characteristics (Continued)

| Symbol             | Parameter                                       | Condition                               | Min        | Тур  | Max  | Unit |  |

|--------------------|-------------------------------------------------|-----------------------------------------|------------|------|------|------|--|

| Shutdown           |                                                 |                                         |            |      |      |      |  |

| loff               | Chutdown Cupply Current                         | EN = GND, $VIN = 5.5V$ , $TAMB = 25$ °C |            | 0.01 | 0.5  |      |  |

| IOFF               | Shutdown Supply Current                         | EN = GND, VIN = 5.5V                    |            | 0.1  | 15   | μA   |  |

| ViH                | CN Input Throphold                              | 2.0V < VIN < 5.5V                       | : 5.5V 1.6 |      |      | V    |  |

| VIL                | EN Input Threshold                              | 2.0V < VIN < 5.5V                       |            |      | 0.6  | V    |  |

| ISHDNN             | EN Input Pigo Current                           | EN = IN or GND, TAMB = +25°C            |            | 1    |      | nΛ   |  |

| ISHDININ           | EN Input Bias Current                           | TAMB = +85°C                            |            | 5    |      | nA   |  |

| POK Output         |                                                 |                                         |            |      |      |      |  |

| Vol                | POK Output Low Voltage                          | POK sinking 1mA                         |            | 0.05 | 0.25 | V    |  |

|                    | Operating Voltage Range for<br>Valid POK Signal | POK sinking 100μA                       | 1.0        |      | 5.5  | V    |  |

|                    | POK Output High leakage                         | $POK = 5.5V, TAMB = +25^{\circ}C$       |            | 1    |      | nA   |  |

|                    | Current                                         | TAMB = +85°C                            |            | 5    |      | IIA  |  |

|                    | POK Threshold                                   | Rising edge (referenced to VouT(NOM))   | 90         | 94   | 98   | %    |  |

| Thermal Protection |                                                 |                                         |            |      |      |      |  |

| TSHDNN             | Thermal Shutdown<br>Temperature                 |                                         |            | 170  | _    | °C   |  |

| $\Delta TSHDNN$    | Thermal Shutdown Hysteresis                     |                                         |            | 20   |      | °C   |  |

<sup>1.</sup> Guaranteed by production test of load regulation and line regulation.

<sup>2.</sup> Dropout voltage is defined as VIN - VOUT, when VOUT is 100mV below the value of VOUT measured for VIN = (VOUT(NOM) + 500mV). Since the minimum input voltage is 2.0V, this specification is only valid when VOUT(NOM) > 2.0V.

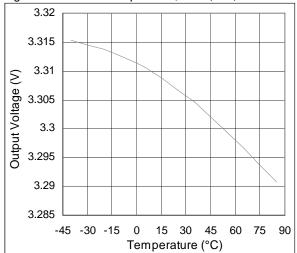

# 7 Typical Operating Characteristics

VIN = VOUT + 0.5V,  $CIN = COUT = 4.7\mu F$ ,  $TAMB = 25^{\circ}C$  (unless otherwise specified).

Figure 3. VDROP vs. IOUT;

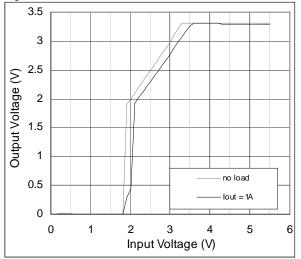

Figure 5. Vout vs. Temperature; Vout(Nom) = 3.3V

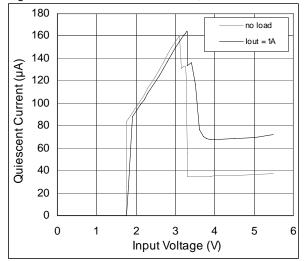

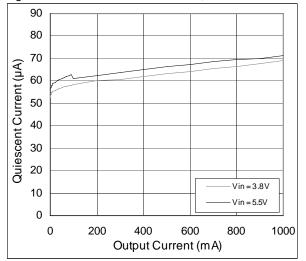

Figure 7. Quiescent Current vs. VIN;

Figure 4. Vout vs. Vin; Vout(NOM) = 3.3V

Figure 6. Vout vs. Vin; Vout(Nom) = 3.3V

Figure 8. Quiescent Current vs. IOUT;

www.austriamicrosystems.com

Revision 1.00

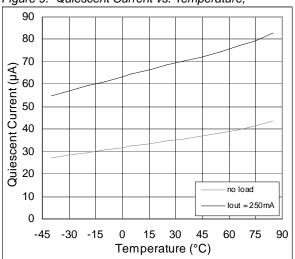

Figure 9. Quiescent Current vs. Temperature;

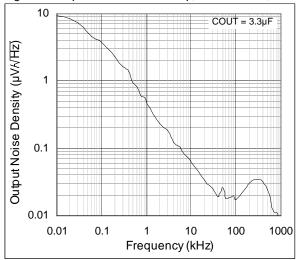

Figure 10. Spectral Noise vs. Freq.; IOUT = 10mA,

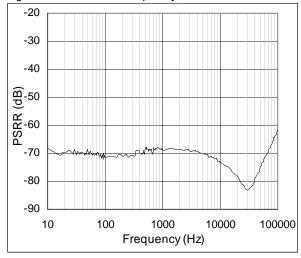

Figure 11. PSRR vs. Frequency; IOUT = 10mA

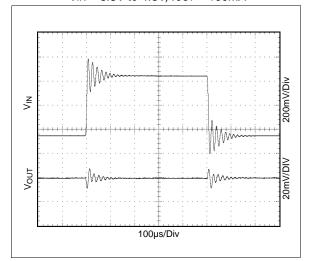

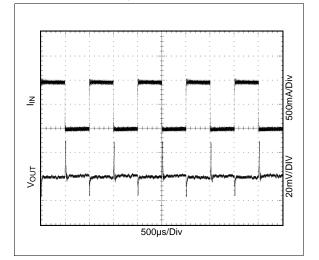

Figure 12. Line Transient Response; VIN = 3.8V to 4.3V, IOUT = 100mA

Figure 13. Load Transient Response; VIN = 3.8V, IOUT = 100mA to 1A

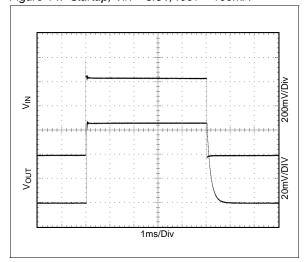

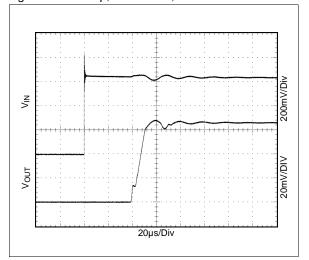

Figure 14. Startup; VIN = 3.8V, IOUT = 100mA

Figure 15. Startup; VIN = 3.8V, IOUT = 100mA

# 8 Detailed Description

The AS1364 output voltage is factory-trimmed or is adjustable from +1.2 to +5V, and is guaranteed to supply 1A of output current. The device consists of a +1.20V internal reference, error amplifier, MOSFET driver, P-channel pass transistor, internal feedback voltage-divider and a comparator (see Figure 1 on page 1).

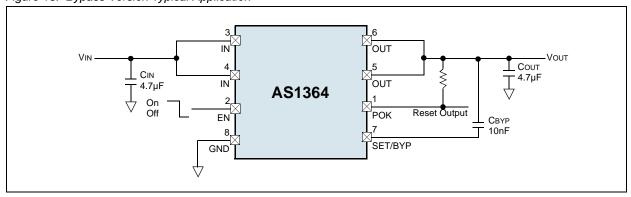

Figure 16. Bypass Version Typical Application

The +1.20V reference is connected to the inverting input of the error amplifier, which compares this reference with the selected feedback voltage and amplifies the difference.

The MOSFET driver reads the error signal and applies the appropriate drive to the P-channel transistor. If the feedback voltage is lower than the reference, the pass transistor gate is pulled lower, allowing more current to pass increasing the output voltage. If the feedback voltage is too high, the pass transistor gate is pulled up, allowing less current to pass to the output.

The low Vout comparator senses when the feedback voltage has dropped 6% below its expected level, causing POK to go low.

The output voltage is fed back through either an internal resistor-divider connected to OUT or an external resistor network connected to SET. The comparator examines VSET/BYP and selects the feedback path. If VSET/BYP is below 50mV, the internal feedback path is used and the output is regulated to the factory-preset voltage.

#### Internal P-Channel Pass Transistor

The AS1364 features a 1A P-channel MOSFET pass transistor and consumes only a maximum of  $200\mu A$  of quiescent current under heavy loads as well as in dropout.

## **Output Voltage Selection**

At the factory trimmed versions of the AS1364 offering the bypass pin (see Figure 16), the output voltage is then set to an internally trimmed voltage (see Ordering Information on page 13).

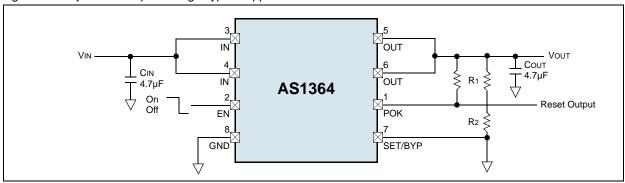

For the adjustable AS1364-AD, an output voltage between +1.2V and +5V can be set by using two external resistors (see Figure 17). In this mode, VOUT is determined by:

$$VSET/BYP (1 + (R_1 / R_2))$$

(EQ 1)

#### Where:

VSET/BYP = +1.20V.

A simplification of R1 and R2 selection is:

$$R1 = R2 ((VOUT / VSET/BYP) - 1)$$

(EQ 2)

Since the input bias current at SET is less than 100nA, large resistance values can be used for R1 and R2 to minimize power consumption and therefore increasing efficiency.

**Note:** Up to  $125k\Omega$  is acceptable for R2. If the SET pin is connected to GND without a resistor, 3.3V will be set as output voltage.

In preset voltage mode, the impedance from SET to GND should be less than  $10k\Omega$  or spurious conditions may cause the voltage at SET to exceed the 50mV threshold.

Figure 17. Adjustable Output Voltage Typical Application

#### Shutdown

If pin EN is connected to GND the AS1364 is disabled. In shutdown mode all internal circuits are turned off, reducing supply current to 10nA (typ). For normal device operation pin EN must be connected to IN. During shutdown, POK goes low.

#### Power-OK

The AS1364 features a power-ok indicator that asserts when the output voltage falls out of regulation. The open-drain POK output goes low when output voltage at OUT falls 6% below its nominal value. A  $100k\Omega$  pull-up resistor from POK to a (typically OUT) provides a logic control signal.

POK can be used as a power-on-reset (POR) signal to a microcontroller or can drive an external LED to indicate a power failure condition.

Note: POK is low during shutdown.

### **Current Limiter**

The AS1364 features current limiting circuitry that monitors the pass transistor, limiting short-circuit output current to 1.5A (typ). The circuitry of the AS1364 allows that the output can be shorted to ground for an indefinite period of time without damaging the device.

## **Thermal Protection**

Integrated thermal overload protection limits the total power dissipation in the AS1364. When the junction temperature (TJ) exceeds +170°C typically, the pass transistor is turned off. Normal operation is continued when TJ drops approximately 20°C.

Note: Regardless of the hysteresis, continuous short-circuit condition will result in a pulsed output.

## **Operating Region and Power Dissipation**

Maximum power dissipation of the AS1364 depends on the thermal resistance of the package and the PCB, the temperature difference between the die junction and ambient air, and the rate of air flow.

The power dissipated in the device is given as:

$$PD = IOUT \sim (VIN - VOUT)$$

(EQ 3)

The maximum power dissipation is calculated:

$$PDMAX = (T_{J(MAX)} - T_{AMB})/(\theta_{JC} + \theta_{CA})$$

(EQ 4)

#### Where:

$T_{J(MAX)}$  - TAMB is the temperature difference between the device die junction and the surrounding air.  $\theta_{JC}$  is the thermal resistance of the junction to the case.

$\theta$ CA is the thermal resistance from the case through the PCB, copper traces, and other materials to the surrounding air.

Connect the exposed thermal pad and GND to circuit ground by using a large pad, or multiple vias to the ground plane.

# 9 Application Information

## Capacitor Selection and Regulator Stability

Input and output capacitors are required for stable operation of the AS1364 over the full temperature range and with load currents up to 1A. Connect CIN and COUT as close to the AS1364 as possible to minimize the impact of PC board trace inductance.

### **Input Capacitor**

For CIN, a 4.7µF capacitor between IN and ground is sufficient. CIN reduces the source impedance of the input supply and may be smaller than 4.7µF if powered from regulated power supplies or low-impedance batteries. Larger input capacitor values and lower ESR provide better noise rejection and line-transient response.

## **Output Capacitor**

A  $4.7\mu F$  low-ESR capacitor between OUT and ground is sufficient for Cout. The output capacitor's ESR affects stability and output noise. An output capacitors with an ESR of  $0.5\Omega$  or less is recommended to ensure stability and optimum transient response. Reduced output noise and improve load-transient response, stability, and power-supply rejection by using large output capacitors with low ESR.

## Noise, PSRR, and Transient Response

AS1364 output noise is typically  $10\mu V_{RMS}$  (100Hz to 100kHz) or  $45\mu V_{RMS}$  (10Hz to 1MHz) during normal operation. This is suitably low for most applications (see Figure 10 on page 7).

The AS1364 is designed to achieve extremly low dropout voltage and low quiescent current in battery-powered systems while still maintaining excellent noise performance, transient response, and PSRR. See the Figure 11 on page 7 for a plot of power-supply rejection ratio (PSRR) versus frequency.

When operating from very noisy sources, the factory preset variants a recommanded since they offer improved noise performance over the adjustable variants.

# 10 Package Drawings and Markings

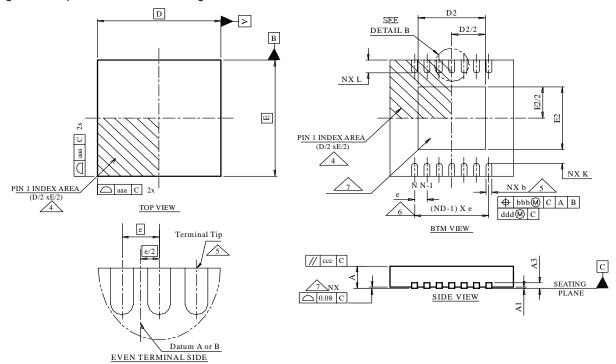

The device is available in an 8-pin TDFN 3x3mm package.

Figure 18. 8-pin TDFN 3x3mm Package

| Symbol | Min  | Тур      | Max  | Notes |

|--------|------|----------|------|-------|

| Α      | 0.70 | 0.75     | 0.80 | 1, 2  |

| A1     | 0.00 | 0.02     | 0.05 | 1, 2  |

| А3     |      | 0.20 REF |      | 1, 2  |

| L1     |      |          | 0.15 | 1, 2  |

| L2     |      |          | 0.13 | 1, 2  |

| aaa    |      | 0.15     |      | 1, 2  |

| bbb    |      | 0.10     |      | 1, 2  |

| ccc    |      | 0.10     |      | 1, 2  |

| ddd    |      | 0.05     |      | 1, 2  |

| eee    |      | 0.08     |      | 1, 2  |

| 999    |      | 0.10     |      | 1, 2  |

| Symbol | Min  | Тур  | Max  | Notes   |

|--------|------|------|------|---------|

| D BSC  |      | 3.00 |      | 1, 2    |

| E BSC  |      | 3.00 |      | 1, 2    |

| D2     | 1.60 |      | 2.50 | 1, 2    |

| E2     | 1.35 |      | 1.75 | 1, 2    |

| L      | 0.30 | 0.40 | 0.50 | 1, 2    |

| θ      | 00   |      | 14º  | 1, 2    |

| K      | 0.20 |      |      | 1, 2    |

| b      | 0.25 | 0.30 | 0.35 | 1, 2, 5 |

| е      |      | 0.65 |      |         |

| N      |      | 8    |      | 1, 2    |

| ND     |      | 4    |      | 1, 2, 5 |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters, angle is in degrees.

- 3. N is the total number of terminals.

- 4. Terminal #1 identifier and terminal numbering convention shall conform to JESD 95-1 SPP-012. Details of terminal #1 identifier are optional, but must be located within the area indicated. The terminal #1 identifier may be either a mold, embedded metal or mark feature.

- 5. Dimension b applies to metallized terminal and is measured between 0.15 and 0.30mm from terminal tip.

- 6. ND refers to the maximum number of terminals on D side.

- 7. Unilateral coplanarity zone applies to the exposed heat sink slug as well as the terminals.

# 11 Ordering Information

The device is available as the standard products shown in Table 5.

Table 5. Ordering Information

| Model           | Marking | Output                         | SET/BYP | Delivery Form | Package          |

|-----------------|---------|--------------------------------|---------|---------------|------------------|

| AS1364-BTDT-AD  | ASRF    | adjustable<br>(preset to 3.3V) | SET     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-12* | ASRN    | 1.2V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-15* | ASRA    | 1.5V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-18* | ASRB    | 1.8V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-30* | ASRC    | 3.0V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-33* | ASRD    | 3.3V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

| AS1364-BTDT-45* | ASRE    | 4.5V                           | BYP     | Tape and Reel | 8-pin TDFN 3x3mm |

All devices are RoHS compliant and free of halogene substances.

Non-standard devices are available between 1.4V and 4.6V in 50mV steps and between 4.6V and 5.0V in 100mV steps. For more information and inquiries contact <a href="http://www.austriamicrosystems.com/contact">http://www.austriamicrosystems.com/contact</a>

<sup>\*</sup>Future product.

## Copyrights

Copyright © 1997-2007, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

## Headquarters

austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact