# DiskOnChip G4 128MB (1Gb)/256MB (2Gb) 1.8V Flash Disk with MLC NAND and M-Systems' x2 Technology

Data Sheet, November 2005

#### Highlights

DiskOnChip G4 is M-Systems' 4<sup>th</sup> generation of the DiskOnChip family of products. Based on Multi-Level Cell (MLC) NAND, utilizing Toshiba's 90nm MLC NAND Large Block flash technology and x2 technology from M-Systems, it is one of the industry's most efficient storage solutions. MLC NAND flash technology provides the smallest die size by storing 2 bits of information in a single memory cell. x2 technology enables MLC NAND to achieve highly reliable, high-performance data and code storage with a specially designed error detection and correction mechanism, optimized file management, and proprietary algorithms for enhanced performance.

Further cost benefits derive from the cost-effective architecture of DiskOnChip G4, which includes a boot block that can replace expensive NOR flash, and incorporates both the flash array and an embedded thin controller in a single die.

DiskOnChip G4 provides:

- Flash disk for both code and data storage

- Low voltage: 1.8V core and I/O

- Hardware protection and security-enabling features

- High capacity: single die 1Gb (128MB), dual die - 2Gb (256MB)

- Device cascade capacity: up to 4Gb (512MB)

- Enhanced Programmable Boot Block enabling eXecute In Place (XIP) functionality using 16-bit interface

- Small form factors:

69-ball FBGA 9x12 mm package

- Enhanced performance by implementation of:

- □ DMA support

- □ MultiBurst operation

- Unrivaled data integrity with a robust Error Detection Code/Error Correction Code (EDC/ECC) tailored for MLC NAND flash technology

- Maximized flash endurance with TrueFFS<sup>®</sup>

6.3.2 (and higher)

- Support for major operating systems (OSs), including Symbian OS, Microsoft Windows Mobile, Palm OS, Nucleus, Linux, OSE, Windows CE, and more.

- Compatible with major CPUs, including TI OMAP, TI DBB, Intel XScale, Infinion, EGold and SGold, ADI 652x, Freescale MX, and Qualcomm MSMxxxx.

#### Performance

- MultiBurst read: 15 MB/sec

- Sustained read: 9 MB/sec

- Sustained write: 2.4 MB/sec

- Access time: Normal: 33 nsec

#### **Protection & Security-Enabling Features**

- 16-byte Unique Identification (UID) number

- 16KByte user-controlled One Time Programmable (OTP) area

- Two configurable hardware-protected partitions for data and code:

- □ Read-only mode

- □ Write-only mode

- □ One-Time Write mode (ROM-like) partition

- □ Protection key and LOCK# signal

- □ Sticky Lock (SLOCK) to lock boot partition

- □ Protected Bad Block Table

#### **Reliability and Data Integrity**

- Hardware- and software-driven, on-the-fly EDC and ECC algorithms

- 4-bit Error Detection Code/Error Correction Code (EDC/ECC), based on a patented combination of BCH and Hamming code algorithms, tailored for MLC NAND flash technology

- Guaranteed data integrity after power failure

- Transparent bad-block management

- Dynamic and static wear-leveling

#### **Boot Capability**

- 2KB Programmable Boot Block with XIP capability to replace boot NOR

- Download Engine (DE) for automatic download of boot code from Programmable Boot Block

- Asynchronous Boot mode to boot from ARM-based CPUs, e.g. XScale, TI OMAP, Freescale MX without the need for external glue logic

- Virtual and Paged RAM boot modes.Enable booting from DiskOnChip under Secure Boot platforms

- Exceptional boot performance with MultiBurst operation and DMA support enhanced by external clock

#### Hardware Compatibility

- Configurable interface: simple NOR-like or multiplexed address/data interface

- CPU compatibility, including:

- □ ARM-based CPUs

- □ Texas Instruments OMAP, DBB

- □ Intel XScale PXAxxx family

- □ Infinion xGold family

- □ Analog Devices (ADI) AD652x family

- □ Freescale MX family

- □ Zoran ER4525

- □ Renesas SH mobile

- □ Qualcomm MSMxxxx

- □ AMD Alchemy

- □ Motorola PowerPC<sup>TM</sup> MPC8xx

- □ Hitachi SuperH<sup>TM</sup> SH-x

- Supports 8-, 16- and 32-bit architectures

#### TrueFFS<sup>®</sup> Software

M-Systems

Flash Disk Pioneers

- Full hard-disk read/write emulation for transparent file system management

- Patented TrueFFS

- □ Flash file system management

- □ Automatic block management

- □ Data management to maximize the limit of typical flash life expectancy

- □ Dynamic virtual mapping

- Dynamic and static wear-leveling

- Programming, duplicating, testing and debugging tools available in source code

#### **Operating Environment**

- Wide OS support, including:

- $\Box$  Symbian OS

- □ Microsoft Windows Mobile

- □ Palm OS

- □ Nucleus

- $\Box$  Windows CE

- □ Linux

- □ OSE

- □ VxWorks

- TrueFFS Software Development Kit (SDK) for quick and easy support for proprietary OSs, or OS-less environment

- TrueFFS Boot Software Development Kit (BDK)

#### **Power Requirements**

- Operating voltage Core, I/O: 1.65 to 1.95V

- Current Consumption

Active mode: Read 4.2mA

Program 7.4mA

- Erase 7.4mA □ Deep Power-Down mode: 10 µA (1Gb/128MB) 20 µA (2Gb/256MB)

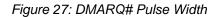

## **Capacity and Packaging**

- 128MB (1Gb) capacity (single die):

- □ Device cascading option for up to four devices (4Gb)

- 69-ball FBGA package: 9x12x1.2 mm (width x length x height)

- Ballout compatible with

DiskOnChip G3/P3, G3/P3 LP and

H1 FBGA products

- 256MB (2Gb) capacity (dual die):

- □ Device cascading option for up to two devices (4Gb)

- 69-ball FBGA package: 9x12x1.4 mm (width x length x height)

- Ballout compatible with DiskOnChip G3/P3, G3/P3 LP, H1 and, H3 FBGA products

# **REVISION HISTORY**

| Doc. No       | Revision | Date         | Description                                                                                        | Reference    |

|---------------|----------|--------------|----------------------------------------------------------------------------------------------------|--------------|

| 92-DT-0305-00 | 0.1      | March 2005   | Preliminary version                                                                                | -            |

|               | 0.2      | October 2005 | Device ball number was reduced<br>from 115 to 69 balls (only not<br>connected balls were reduced). | Section 2    |

|               |          |              | Updated mechanical dimensions.                                                                     | Section 10.4 |

|               |          |              | Updated Ordering Information.                                                                      | Section 11   |

| 92-DS-1105-00 | 0.3      | November     | Updated electrical information                                                                     | -            |

# TABLE OF CONTENTS

| 1. | Intro | duction                  |                                                         | 9  |  |  |  |

|----|-------|--------------------------|---------------------------------------------------------|----|--|--|--|

| 2. | Proc  | uct Overview             | /                                                       | 10 |  |  |  |

|    | 2.1   | Product Desc             | cription                                                | 10 |  |  |  |

|    | 2.2   | Standard Inte            | erface                                                  | 11 |  |  |  |

|    |       | 2.2.1 Ball D             | iagrams                                                 | 11 |  |  |  |

|    |       | 2.2.2 System             | n Interface                                             | 12 |  |  |  |

|    |       | 2.2.3 Signal             | Description                                             | 13 |  |  |  |

|    | 2.3   | •                        | nterface                                                |    |  |  |  |

|    |       |                          | iagram                                                  |    |  |  |  |

|    |       | •                        | n Interface                                             |    |  |  |  |

| _  |       | -                        | Description                                             |    |  |  |  |

| 3. | Theo  |                          | on                                                      |    |  |  |  |

|    | 3.1   | Overview                 |                                                         | 19 |  |  |  |

|    | 3.2   | System Inter             | face                                                    | 20 |  |  |  |

|    |       |                          | ard (NOR-Like) Interface                                |    |  |  |  |

|    |       |                          | lexed Interface                                         |    |  |  |  |

|    | 3.3   | Configuration Interface2 |                                                         |    |  |  |  |

|    | 3.4   | Protection ar            | d Security-Enabling Features                            | 21 |  |  |  |

|    |       |                          | Write Protection                                        |    |  |  |  |

|    |       |                          | e Identification (UID) Number                           |    |  |  |  |

|    |       |                          | ime Programmable (OTP) Area                             |    |  |  |  |

|    |       |                          | ime Write (ROM-Like) Partition                          |    |  |  |  |

|    | 0.5   | -                        |                                                         |    |  |  |  |

|    | 3.5   | 0                        | le Boot Block with eXecute In Place (XIP) Functionality |    |  |  |  |

|    | 3.6   |                          | ngine (DE)                                              |    |  |  |  |

|    | 3.7   | Error Detection          | on Code/Error Correction Code (EDC/ECC)                 | 23 |  |  |  |

|    | 3.8   | Control and S            | Status                                                  | 23 |  |  |  |

|    | 3.9   | Flash Archite            | cture                                                   | 23 |  |  |  |

| 4. | x2 T  | echnology                |                                                         | 25 |  |  |  |

|    | 4.1   | MultiBurst Op            | peration                                                | 25 |  |  |  |

|    | 4.2   | -                        | on                                                      |    |  |  |  |

|    | 4.3   |                          | ultiBurst Mode and DMA Operation                        |    |  |  |  |

| 5. | Harc  |                          | ion                                                     |    |  |  |  |

|    | 5.1  | Method of Operation                                                | 30  |  |  |  |  |  |  |

|----|------|--------------------------------------------------------------------|-----|--|--|--|--|--|--|

| 6. | Mode | es of Operation31                                                  |     |  |  |  |  |  |  |

|    | 6.1  | Normal Mode                                                        | 32  |  |  |  |  |  |  |

|    | 6.2  | Reset Mode                                                         | 32  |  |  |  |  |  |  |

|    | 6.3  | Deep Power-Down Mode                                               | 32  |  |  |  |  |  |  |

|    | 6.4  | TrueFFS Technology                                                 | 33  |  |  |  |  |  |  |

|    |      | 6.4.1 General Description                                          |     |  |  |  |  |  |  |

|    |      | 6.4.2 Built-In Operating System Support                            | 34  |  |  |  |  |  |  |

|    |      | 6.4.3 TrueFFS Software Development Kit (SDK)                       | 34  |  |  |  |  |  |  |

|    |      | 6.4.4 File Management                                              | 34  |  |  |  |  |  |  |

|    |      | 6.4.5 Bad-Block Management                                         | 34  |  |  |  |  |  |  |

|    |      | 6.4.6 Wear-Leveling                                                |     |  |  |  |  |  |  |

|    |      | 6.4.7 Power Failure Management                                     |     |  |  |  |  |  |  |

|    |      | 6.4.8 Error Detection/Correction                                   |     |  |  |  |  |  |  |

|    |      | 6.4.9 Special Features Through I/O Control (IOCTL) Mechanism       |     |  |  |  |  |  |  |

|    |      | 6.4.10 Compatibility                                               |     |  |  |  |  |  |  |

|    | 6.5  | 8KB Memory Window                                                  |     |  |  |  |  |  |  |

| 7. | Regi | ster Descriptions                                                  |     |  |  |  |  |  |  |

|    | 7.1  | Definition of Terms                                                | 38  |  |  |  |  |  |  |

|    | 7.2  | Reset Values                                                       | 39  |  |  |  |  |  |  |

|    | 7.3  | RAM Page Command Register                                          | 39  |  |  |  |  |  |  |

|    | 7.4  | RAM Page Select Register                                           | 39  |  |  |  |  |  |  |

|    | 7.5  | Paged RAM COTP Status Download Register Error! Bookmark not define | d.  |  |  |  |  |  |  |

|    | 7.6  | Paged RAM COTP Select Register Error! Bookmark not define          | ed. |  |  |  |  |  |  |

|    | 7.7  | Paged RAM Unique ID Download Register                              | 40  |  |  |  |  |  |  |

|    | 7.8  | No Operation (NOP) Register                                        | 40  |  |  |  |  |  |  |

|    | 7.9  | Chip Identification (ID) Register [0:1]                            | 40  |  |  |  |  |  |  |

|    | 7.10 | Test Register                                                      |     |  |  |  |  |  |  |

|    |      | Endian Control Register                                            |     |  |  |  |  |  |  |

|    |      | DiskOnChip Control Register/Control Confirmation Register          |     |  |  |  |  |  |  |

|    |      | Device ID Select Register                                          |     |  |  |  |  |  |  |

|    |      | Configuration Register                                             |     |  |  |  |  |  |  |

|    |      | Interrupt Control Register                                         |     |  |  |  |  |  |  |

|    |      | Interrupt Status Register                                          |     |  |  |  |  |  |  |

|    |      |                                                                    |     |  |  |  |  |  |  |

|    | 1.17 | Output Control Register                                            | 45  |  |  |  |  |  |  |

|    | 7.18   | DPD Co   | ontrol Register                     | . 46 |

|----|--------|----------|-------------------------------------|------|

|    | 7.19   | DMA Co   | ontrol Register [1:0]               | . 47 |

|    | 7.20   | MultiBur | rst Mode Control Register           | . 48 |

|    |        |          | Paged RAM Status Register           |      |

| 8. |        |          | n DiskOnChip G4                     |      |

| •  | 8.1    | -        | tion                                |      |

|    | 8.2    |          | placement                           |      |

|    | 0.2    |          | Asynchronous Boot Mode              |      |

|    |        |          | /irtual RAM Boot                    |      |

|    |        |          | Paged RAM Boot                      |      |

| 9. | Desi   |          | iderations                          |      |

|    | 9.1    | •        | Guidelines                          |      |

|    | 9.2    | Standar  | d NOR-Like Interface                | . 54 |

|    | 9.3    | Multiple | xed Interface                       | . 56 |

|    | 9.4    | Connect  | ting Control Signals                | . 56 |

|    | -      |          | Standard Interface                  |      |

|    |        | 9.4.2 N  | Multiplexed Interface               | . 57 |

|    | 9.5    | Impleme  | enting the Interrupt Mechanism      | . 58 |

|    |        | 9.5.1 ŀ  | Hardware Configuration              | . 58 |

|    |        | 9.5.2 \$ | Software Configuration              | . 58 |

|    | 9.6    | Device ( | Cascading                           | . 59 |

|    | 9.7    | Boot Re  | placement                           | . 60 |

|    | 9.8    | Platform | n-Specific Issues                   | . 61 |

|    |        | 9.8.1 V  | Nait State                          | . 61 |

|    |        | 9.8.2 E  | Big and Little Endian Systems       | . 61 |

|    |        | 9.8.3 E  | Busy Signal                         | . 61 |

|    |        | 9.8.4 V  | Norking with 8/16/32-Bit Systems    | . 61 |

|    | 9.9    | Design I | Environment                         | . 63 |

| 10 | . Prod | uct Spe  | cifications                         | . 64 |

|    | 10.1   | Environ  | mental Specifications               | . 64 |

|    |        | 10.1.1 0 | Operating Temperature               | . 64 |

|    |        | 10.1.2 7 | Thermal Characteristics             | . 64 |

|    |        |          | Humidity                            |      |

|    |        |          | Endurance Error! Bookmark not defin |      |

|    | 10.2   |          | al Specifications                   |      |

|    |        | 10.2.1 A | Absolute Maximum Ratings            | . 64 |

DiskOnChip G4 128MB (1Gb)/256MB (2Gb) 1.8V

|          | 10.2.2   | Capacitance                                        | 64 |

|----------|----------|----------------------------------------------------|----|

|          | 10.2.3   | DC Electrical Characteristics over Operating Range | 65 |

|          | 10.2.4   | AC Operating Conditions                            | 67 |

| 10.3     | Timing   | Specifications                                     | 68 |

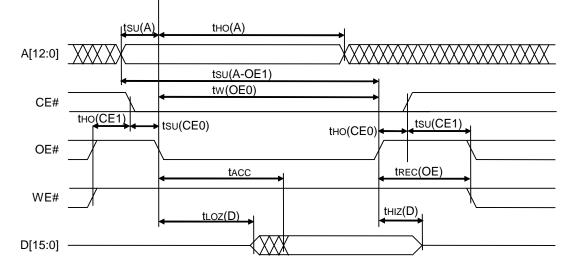

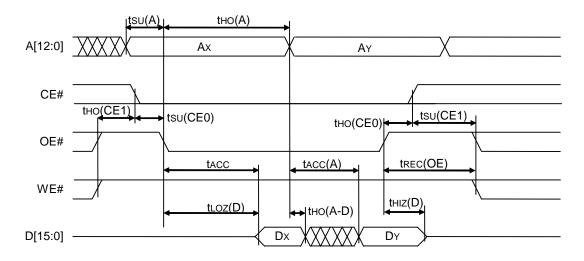

|          | 10.3.1   | Read Cycle Timing Standard Interface               | 68 |

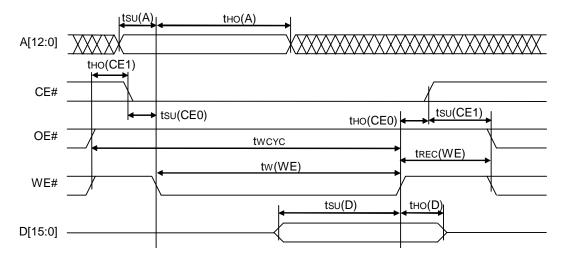

|          | 10.3.2   | Write Cycle Timing Standard Interface              | 71 |

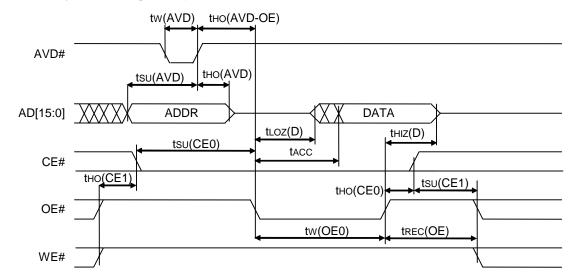

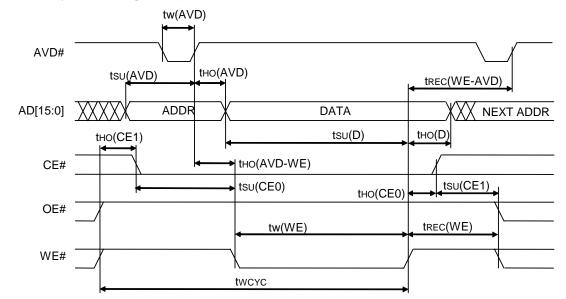

|          | 10.3.3   | Read Cycle Timing Multiplexed Interface            | 72 |

|          | 10.3.4   | Write Cycle Timing Multiplexed Interface           | 74 |

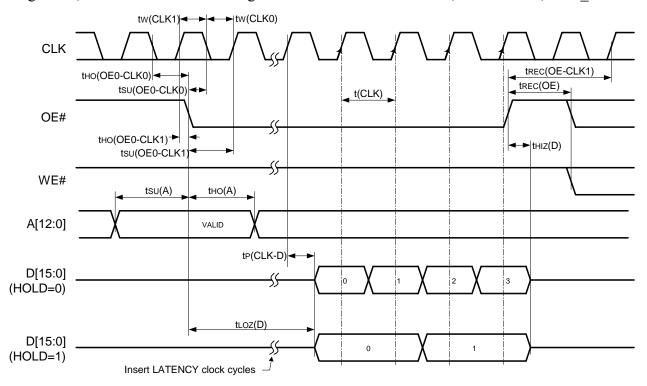

|          | 10.3.5   | Read Cycle Timing MultiBurst                       | 76 |

|          |          | Flash Characteristics                              |    |

|          |          | Power Supply Sequence                              |    |

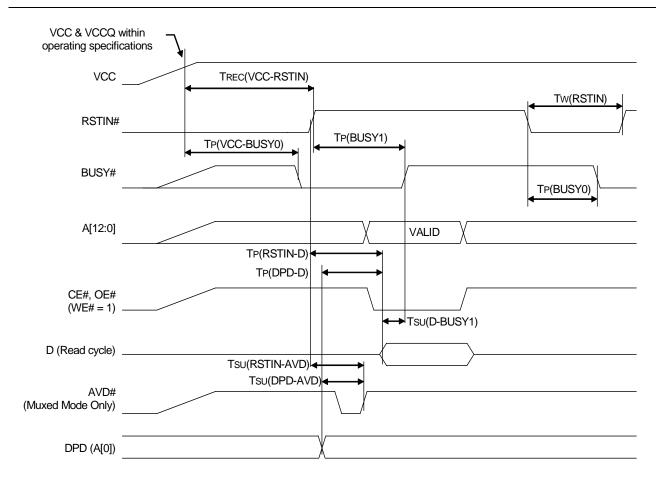

|          | 10.3.8   | Power-Up Timing                                    | 79 |

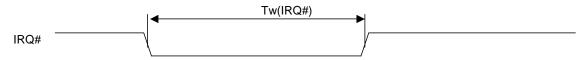

|          | 10.3.9   | Interrupt Timing                                   | 81 |

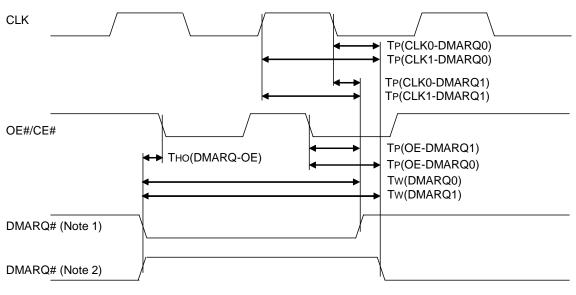

|          | 10.3.10  | DMA Request Timing                                 | 81 |

| 10.4     | Mecha    | nical Dimensions                                   | 83 |

| 11. Orde | ering In | formation                                          | 84 |

| How to   | Contact  | t Us                                               | 85 |

# 1. INTRODUCTION

This data sheet includes the following sections:

| Section 1:  | Overview of data sheet contents                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| Section 2:  | Product overview, including a brief product description, ball diagrams and signal descriptions                                 |

| Section 3:  | Theory of operation for the major building blocks                                                                              |

| Section 4:  | Major features and benefits of x2 technology                                                                                   |

| Section 5:  | Detailed description of hardware protection and security-enabling features                                                     |

| Section 6:  | Detailed description of modes of operation and TrueFFS technology, including power failure management and 8KByte memory window |

| Section 7:  | DiskOnChip G4 register descriptions                                                                                            |

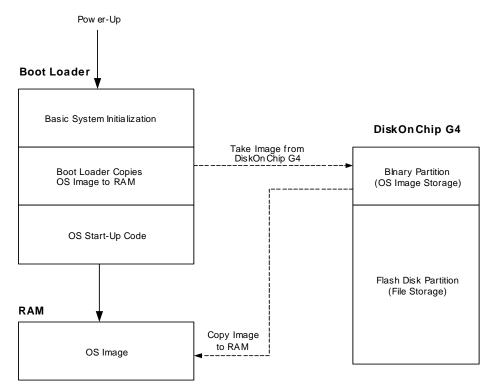

| Section 8:  | Overview of how to boot from DiskOnChip G4                                                                                     |

| Section 9:  | Hardware and software design considerations                                                                                    |

| Section 10: | Environmental, electrical, timing and product specifications                                                                   |

| Section 11: | Information on ordering DiskOnChip G4                                                                                          |

|             |                                                                                                                                |

For additional information on M-Systems' flash disk products, please contact one of the offices listed on the back page.

## 2. **PRODUCT OVERVIEW**

## 2.1 **Product Description**

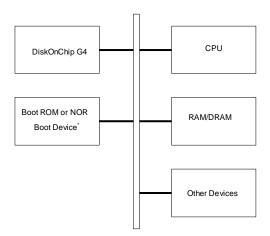

DiskOnChip G4 is the latest addition to M-Systems' DiskOnChip product family. DiskOnChip G4, packed in a small FBGA package with 128MB (1Gb) capacity, is a single-die device with an embedded thin flash controller and flash memory. It uses Toshiba's cutting-edge, 90nm NAND-based Multi-Level Cell (MLC) large block flash technology, enhanced by M-Systems' proprietary x2 technology. A dual-die device is available with a single chip capacity of 256MB (2Gb).

MLC NAND technology enables two bits of data to be stored on a single cell, cutting in half the physical die size. M-Systems' proprietary x2 technology overcomes MLC-related error patterns and slow transfer rates by using a robust error detection and correction (EDC/ECC) mechanism. Furthermore, it provides performance enhancement with multi-plane operation, DMA support, turbo operation and MultiBurst operation. The combination of MLC and x2 technology results in a low-cost, minimal-sized flash disk that achieves unsurpassed reliability levels and enhanced performance.

This breakthrough in performance, size and cost makes DiskOnChip G4 the ideal solution for product manufacturers who require high-capacity, small size, high-performance, and above all, high-reliability storage to enable applications such as Digital TVs (DTVs), rugged handheld terminals, Digital Still Cameras (DSCs), Mobile Point of Sale (POS), telecom equipment, multimedia phones, camera and Video on Demand (VOD) phones, MP3 phones, enhanced Multimedia Messaging Service (MMS), gaming, video and Personal Information Management (PIM) on mobile handsets, and Personal Digital Assistants (PDAs).

As with the DiskOnChip G3, DiskOnChip G4 content protection and security-enabling features offer several benefits. Two write- and read-protected partitions, with both software- and hardware-based protection, can be configured independently for maximum design flexibility. The 16-byte Unique ID (UID) identifies each flash device, eliminating the need for a separate ID device on the motherboard. The 16KB One Time Programmable (OTP) area is written to once and then locked to prevent data and code from being altered, is ideal for storing customer and product-specific information.

DiskOnChip G4 has a 2KB Programmable Boot Block. This block provides eXecute In Place (XIP) functionality, enabling DiskOnChip G4 to replace the boot device and function as the only non-volatile memory device on-board. Eliminating the need for an additional boot device reduces hardware expenditures, board real estate, programming time, and logistics.

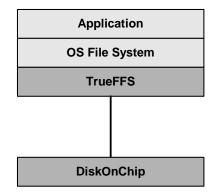

M-Systems' patented TrueFFS software technology fully emulates a hard disk to manage the files stored on DiskOnChip G4. This transparent file system management enables read/write operations that are identical to a standard, sector-based hard disk. In addition, TrueFFS employs patented methods, such as virtual mapping, dynamic and static wear-leveling, and automatic block management to ensure high data reliability and to maximize flash life expectancy.

## 2.2 Standard Interface

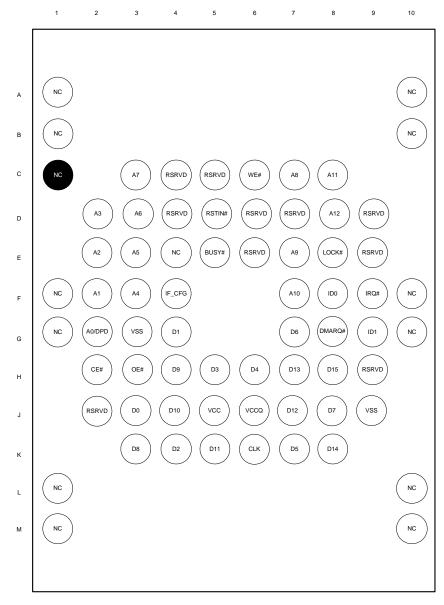

#### 2.2.1 Ball Diagrams

See Figure 1 for the DiskOnChip G4 128MB (1Gb)/256MB (2Gb) ballout for the standard interface. To ensure proper device functionality, balls marked RSRVD are reserved for future use and should not be connected.

Note: Fourth-generation DiskOnChip G4 is designed as a drop-in replacement for all DiskOnChip products. assuming that the latter were integrated according to migration guide guidelines. Refer to the *DiskOnChip* G3/P3 to G3/P3 LP, G4/P4, H1 to DiskOnChip H3 migration guide for further information.

#### 9x12 FBGA Package

#### 2.2.2 System Interface

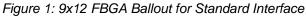

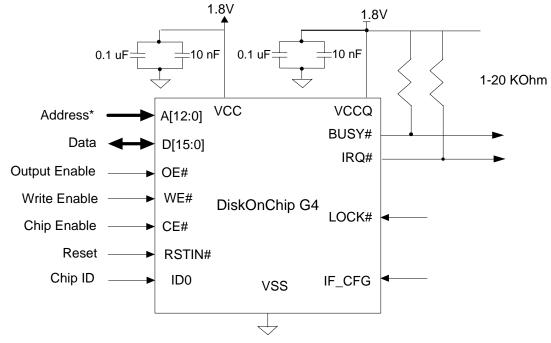

See Figure 2 for a simplified I/O diagram for a standard interface of DiskOnChip G4 128MB (1Gb) and 256MB (2Gb).

Figure 2: Standard Interface Simplified I/O Diagram

## 2.2.3 Signal Description

DiskOnChip G4 FBGA related ball designations are listed in the signal descriptions, presented in logic groups, in Table 1.

| Signal                                  | Ball No.                                                 | Input<br>Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Signal Type      |

|-----------------------------------------|----------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                         |                                                          |                            | System Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| A[12:11]<br>A[10:8]<br>A[7:4]<br>A[3:0] | D8, C8<br>F7, E7, C7<br>C3, D3, E3, F3<br>D2, E2, F2, G2 | ST                         | Address bus. A0 is multiplexed with the DPD ball.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input            |

| D[15:14]<br>D[13:12]<br>D[11:8]         | H8, K8<br>H7, J7<br>K5, J4, H4, K3                       | ST, R8                     | Data bus, high byte. Not used and may be left floating when IF_CFG is set to 0 (8-bit mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input/<br>Output |

| D[7:6]<br>D[5:3]<br>D[2:0]              | J8, G7<br>K7, H6, H5<br>K4, G4, J3                       | ST                         | Data bus, low byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input/<br>Output |

| CE#                                     | H2                                                       | ST                         | Chip Enable, active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input            |

| OE#                                     | H3                                                       | ST                         | Output Enable, active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input            |

| WE#                                     | C6                                                       | ST                         | Write Enable, active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input            |

|                                         |                                                          |                            | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

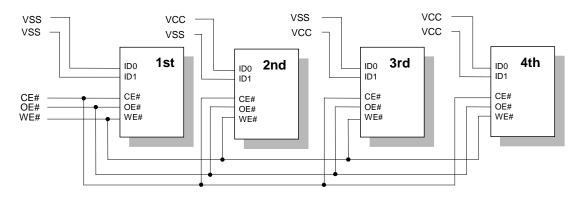

| ID[1:0]                                 | G9, F8                                                   | ST                         | Identification. Configuration control.<br>DiskOnChip G4 128MB(1Gb) supports up to four<br>chips cascaded in the same memory window:<br>Chip 1 = ID1, ID0 = VSS, VSS (0,0); must be<br>used for single chip configuration.<br>Chip 2 = ID1, ID0 = VSS, VCCQ (0,1)<br>Chip 3 = ID1, ID0 = VCCQ, VSS (1,0)<br>Chip 4 = ID1, ID0 = VCCQ, VCCQ (1,1)<br>DiskOnChip G4 256MB(2Gb) supports up to two<br>chips cascaded in the same memory window:<br>Chip 1 = ID1, ID0 = VSS, VSS (0,0); must be used<br>for single chip configuration<br>Chip 2 = ID1, ID0 = VCCQ, VCCQ (1,1) | Input            |

| LOCK#<br>IF_CFG                         | E8<br>F4                                                 | ST<br>ST                   | Lock, active low. When active, provides full<br>hardware data protection of selected partitions.<br>Interface Configuration, 1 (VCCQ) for 16-bit<br>interface mode, 0 (VSS) for 8-bit interface mode.                                                                                                                                                                                                                                                                                                                                                                    | Input<br>Input   |

Table 1: Signal Descriptions for Standard Interface

DiskOnChip G4 128MB (1Gb)/256MB (2Gb) 1.8V

| Signal | Ball No.     | Input<br>Type <sup>1</sup> | Description                                                                                                                                                                                                                                                               | Signal Type |

|--------|--------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        |              |                            | Control                                                                                                                                                                                                                                                                   |             |

| BUSY#  | E5           | OD                         | Busy, active low, open drain. Indicates that<br>DiskOnChip is initializing and should not be<br>accessed. A 10 K $\Omega$ pull-up resistor is required if this<br>ball drives an input. A 10 K $\Omega$ pull-up resistor is<br>recommended even if this ball is not used. | Output      |

| RSTIN# | D5           | ST                         | Reset, active low.                                                                                                                                                                                                                                                        | Input       |

| CLK    | K6           | ST                         | System Clock.                                                                                                                                                                                                                                                             | Input       |

| DMARQ# | G8           | OD                         | DMA Request, active low. A 10 K $\Omega$ pull-up resistor is required if this ball drives an input. A 10 K $\Omega$ pull-up resistor is recommended even if this ball is not used.                                                                                        | Output      |

| IRQ#   | F9           | OD                         | Interrupt Request, active low. A 10 K $\Omega$ pull-up resistor is required if this ball drives an input. A 10 K $\Omega$ pull-up resistor is recommended even if this ball is not used.                                                                                  | Output      |

| DPD    | G2           | ST                         | Deep Power-Down. Used to enter and exit Deep<br>Power-Down mode. This ball is assigned A0 instead<br>of DPD when working in 8-bit mode.                                                                                                                                   | Input       |

|        | •            | •                          | Power                                                                                                                                                                                                                                                                     | •           |

| VCC    | J5           | -                          | Device supply. Requires a 10 nF and 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                | Supply      |

| VCCQ   | J6           | -                          | I/O power supply. Sets the logic 1 voltage level range of I/O balls. VCCQ may be $1.65V$ to $1.95V$ . Requires a 10 nF and 0.1 $\mu$ F capacitor.                                                                                                                         | Supply      |

| VSS    | G3, J9       | -                          | Ground. All VSS balls must be connected.                                                                                                                                                                                                                                  | Supply      |

|        |              |                            | Other                                                                                                                                                                                                                                                                     | _           |

| RSRVD  | See Figure 1 | -                          | Reserved. Other reserved signals are not connected internally and must be left floating to guarantee forward compatibility with future products.                                                                                                                          |             |

|        | М            | -                          | Mechanical. These balls are for mechanical placement, and are not connected internally.                                                                                                                                                                                   |             |

The following abbreviations are used: IN - Standard (non-Schmidt) input, ST - Schmidt Trigger input, OD - Open drain output, R8 - Nominal 22K pull-up resistor, enabled only for 8-bit interface mode (IF\_CFG input is 0)

## 2.3 Multiplexed Interface

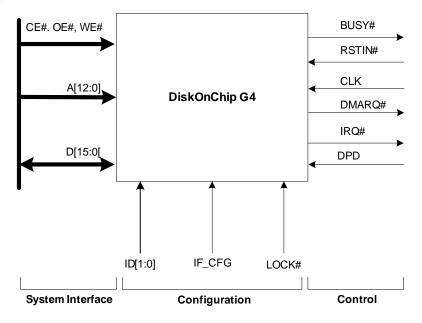

#### 2.3.1 Ball Diagram

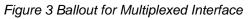

See Figure 3 for the DiskOnChip G4 ballout for the multiplexed interface. To ensure proper device functionality, balls marked RSRVD are reserved for future use and should not be connected.

Note: Forth-generation DiskOnChip G4 is designed as a drop-in replacement for all DiskOnChip products, assuming that the latter were integrated according to migration guide guidelines. Refer to the *DiskOnChip G3/P3 to G3/P3 LP, G4/P4, H1 to DiskOnChip H3* migration guide for further information.

#### 9x12 FBGA Package

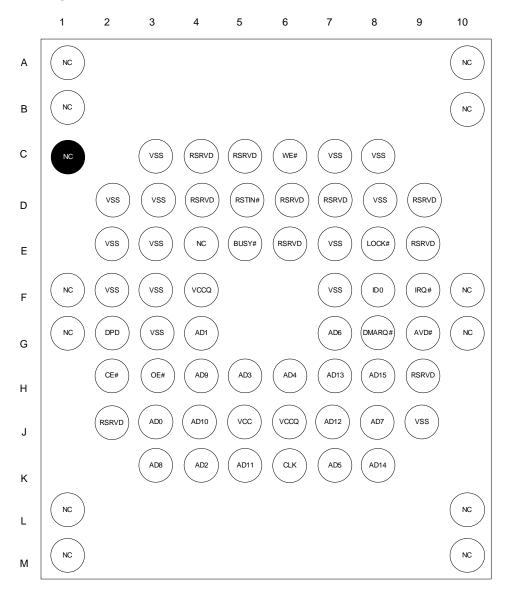

## 2.3.2 System Interface

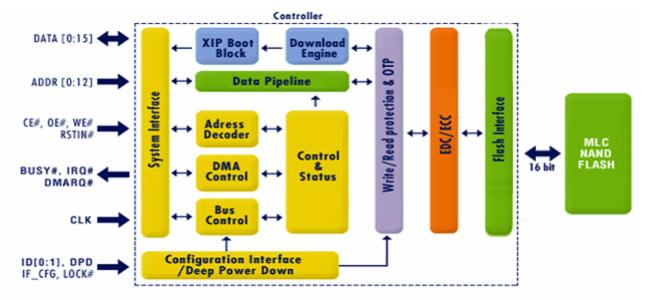

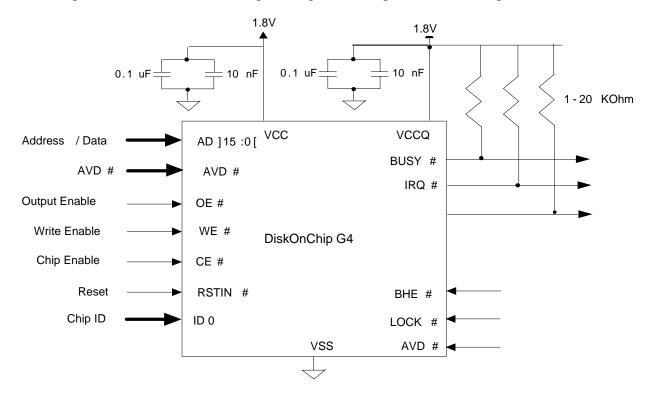

See Figure 4 for a simplified I/O diagram of DiskOnChip G4.

Figure 4: Multiplexed Interface Simplified I/O Diagram

## 2.3.3 Signal Description

DiskOnChip G4 FBGA related ball designations are listed in the signal descriptions, presented in logic groups, in Table 2.

| Signal                                                              | Pin No.                                                                  | Input<br>Type <sup>1</sup> | Description                                                                                                                                                                                                                                                  | Signal<br>Type   |

|---------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                                                     |                                                                          |                            | System Interface                                                                                                                                                                                                                                             |                  |

| AD[15:14]<br>AD[13:12]<br>AD[11:9]<br>AD[8:6]<br>AD[5:3]<br>AD[2:0] | H8, K8<br>H7, J7<br>K5, J4, H4<br>K3, J8, G7<br>K7, H6, H5<br>K4, G4, J3 | ST                         | Multiplexed bus. Address and data signals                                                                                                                                                                                                                    | Input/<br>Output |

| CE#                                                                 | H2                                                                       | ST                         | Chip Enable, active low                                                                                                                                                                                                                                      | Input            |

| OE#                                                                 | H3                                                                       | ST                         | Write Enable, active low                                                                                                                                                                                                                                     | Input            |

| WE#                                                                 | C6                                                                       | ST                         | Output Enable, active low                                                                                                                                                                                                                                    | Input            |

|                                                                     |                                                                          | _                          | Configuration                                                                                                                                                                                                                                                |                  |

| AVD#                                                                | G9                                                                       | ST                         | Address Valid. Set multiplexed interface                                                                                                                                                                                                                     | Input            |

| ID0                                                                 | F8                                                                       | ST                         | Identification. Configuration control to support up to two chips<br>cascaded in the same memory window.<br>Chip 1 = ID0 = VSS; must be used for single-chip<br>configuration<br>Chip 2 = ID0 = VCC                                                           | Input            |

| LOCK#                                                               | E8                                                                       | ST                         | Lock, active low. When active, provides full hardware data protection of selected partitions.                                                                                                                                                                | Input            |

|                                                                     |                                                                          | •                          | Control                                                                                                                                                                                                                                                      |                  |

| BUSY#                                                               | E5                                                                       | OD                         | Busy, active low, open drain. Indicates that DiskOnChip is initializing and should not be accessed A 10 K $\Omega$ pull-up resistor is required if this ball drives an input. A 10 K $\Omega$ pull-up resistor is recommended even if this ball is not used. | Output           |

| RSTIN#                                                              | D5                                                                       | ST                         | Reset, active low.                                                                                                                                                                                                                                           | Input            |

| CLK                                                                 | K6                                                                       | ST                         | System Clock.                                                                                                                                                                                                                                                | Input            |

| DMARQ#                                                              | G8                                                                       | OD                         | DMA Request, active low. A 10 K $\Omega$ pull-up resistor is required if this ball drives an input. A 10 K $\Omega$ pull-up resistor is recommended even if this ball is not used.                                                                           | Output           |

| IRQ#                                                                | F9                                                                       | OD                         | Interrupt Request, active low. A 10 K $\Omega$ pull-up resistor is required if this ball drives an input. A 10 K $\Omega$ pull-up resistor is recommended even if this ball is not used.                                                                     | Output           |

| Table 2: Signal Descriptions | for Multiplexed Interface |

|------------------------------|---------------------------|

|                              |                           |

| Signal | Pin No.                                                            | Input<br>Type <sup>1</sup> | Description                                                                                                                                         | Signal<br>Type |

|--------|--------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DPD    | G2                                                                 | ST                         | Deep Power-Down. Used to enter and exit Deep Power-<br>Down mode. Pin is assigned A0 instead of DPD when<br>working in 8-bit mode.                  | Input          |

|        | -                                                                  | 1                          | Power                                                                                                                                               | •              |

| VCC    | J5                                                                 | -                          | Device core supply. Requires a 10 nF and 0.1 µF capacitor.                                                                                          | Supply         |

| VCCQ   | J6, F4                                                             | -                          | I/O power supply. Sets the logic <b>1</b> voltage level range of I/O balls. VCCQ may be 1.65V to 1.95V. Requires a 10 nF and 0.1 $\mu$ F capacitor. | Supply         |

| VSS    | G3, J9, D8,<br>C8, F7, E7,<br>C7, C3, D3,<br>E3, F3, D2,<br>E2, F2 | -                          | Ground. All VSS pins must be connected.                                                                                                             | Supply         |

|        |                                                                    | •                          | Other                                                                                                                                               |                |

| RSRVD  | See Figure 3                                                       | -                          | Reserved. Reserved signals are not connected internally and must be left floating to guarantee forward compatibility with future products.          |                |

|        | М                                                                  |                            | Mechanical. These balls are for mechanical placement, and are not connected internally.                                                             |                |

1. The following abbreviations are used: IN - Standard (non-Schmidt) input, ST - Schmidt Trigger input, OD - Open drain output

## 3. THEORY OF OPERATION

## 3.1 Overview

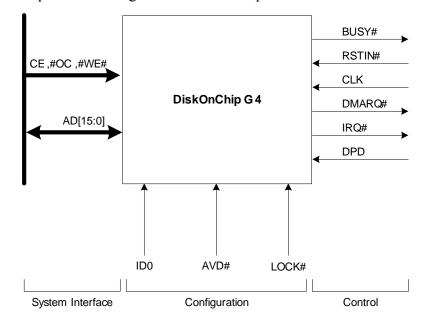

DiskOnChip G4 consists of the following major functional blocks, as shown in Figure 5.

\*ADDR[0] and DPD are multiplexed on the same ball/pin.

Figure 5: Simplified Block Diagram, Standard Interface

These components are described briefly below and in more detail in the following sections.

- System Interface for the host interface.

- **Configuration Interface** for configuring DiskOnChip G4 to operate in 8-bit, 16-bit mode, cascaded configuration, hardware read/write protection and entering/exiting Deep Power-Down mode.

- Read/Write Protection and OTP for advanced data/code security and protection.

- **Programmable Boot Block with XIP** functionality enhanced with a **Download Engine** (**DE**) for system initialization capability.

- Error Detection and Error Correction Code (EDC/ECC) for on-the-fly error handling.

- **Data Pipeline** through which the data flows from the system to the NAND flash arrays.

- **Control & Status** block that contains registers responsible for transferring the address, data and control information between the TrueFFS driver and the flash media.

- Flash Interface that interfaces to two NAND flash planes.

- **Bus Control** for translating the host bus address, and data and control signals into valid NAND flash signals.

- Address Decoder to enable the relevant unit inside the DiskOnChip controller, according to the address range received from the system interface.

# 3.2 System Interface

## 3.2.1 Standard (NOR-Like) Interface

The system interface block provides an easy-to-integrate NOR-like (also SRAM and EEPROMlike) interface to DiskOnChip G4 enabling it to interface with various CPU interfaces, such as a local bus, ISA bus, NOR interface, SRAM interface, EEPROM interface or any other compatible interface. In addition, the EEPROM-like interface enables direct access to the Programmable Boot Block to permit XIP (Execute-In-Place) functionality during system initialization.

A 13-bit wide address bus enables access to the DiskOnChip G4 8KB memory window (as shown in Section 6.5).

The Chip Enable (CE#), Write Enable (WE#) and Output Enable (OE#) signals trigger read and write cycles. A write cycle occurs while both the CE# and the WE# inputs are asserted. Similarly, a read cycle occurs while both the CE# and OE# inputs are asserted. Note that DiskOnChip G4 does not require a clock signal. It features a unique analog static design, optimized for minimal power consumption. The CE#, WE# and OE# signals trigger the controller (e.g., system interface block, bus control and data pipeline) and flash access.

The Reset In (RSTIN#) and Busy (BUSY#) control signals are used in the reset phase.

The Interrupt Request (IRQ#) signal can be used when long I/O operations, such as Block Erase, delay the CPU resources. The signal is also asserted when a Data Protection violation has occurred. This signal frees the CPU to run other tasks, continuing read/write operations with DiskOnChip G4 only after the IRQ# signal has been asserted and an interrupt handling routine (implemented in the OS) has been called to return control to the TrueFFS driver.

The DMARQ# output is used to control multi-page DMA operations, and the CLK input is used to support MultiBurst operation when reading flash data. See Section 4.1 for further information.

## 3.2.2 Multiplexed Interface

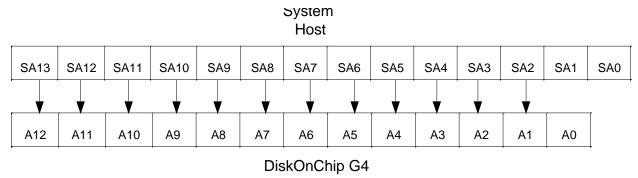

In this configuration, the address and data signals are multiplexed. The ID[1] input is driven by the host AVD# signal, and the D[15:0] pins/balls, used for both address inputs and data, are connected to the host AD[15:0] bus. While AVD# is asserted, the host drives AD[11:0] with bits [12:1] of the address. Host signals AD[15:12] are not significant during this part of the cycle.

This interface is automatically used when a falling edge is detected on ID[1]. This edge must occur after RSTIN# is negated and before the first read or write cycle to the controller. When using a multiplexed interface, the value of ID[1] is internally forced to logic-0. The only possible device ID values are 0 and 1; therefore, only up to two DiskOnChip G4 128MB (1Gb) devices may be cascaded in multiplexed configuration (dual-die DiskOnChip G4 256MB (2Gb) cannot be cascaded when used in a multiplexed interface).

# 3.3 Configuration Interface

The Configuration Interface block enables the designer to configure DiskOnChip G4 to operate in different modes. The ID[1:0] signals are used in a cascaded configuration (refer to Section 9.6), the DPD signal is used to enter and exit Deep Power-Down mode (see Section 6.3), the LOCK# signal

is used for hardware write/read protection, and the IF\_CFG signal is used to configure 8/16-bit access.

# 3.4 Protection and Security-Enabling Features

The Protection and Security-Enabling block, consisting of read/write protection, UID and an OTP area, enables advanced data and code security and content protection. Located on the main route of traffic between the host and the flash, this block monitors and controls all data and code transactions to and from DiskOnChip G4.

## 3.4.1 Read/Write Protection

Data and code protection is implemented through a Protection State Machine (PSM). The user can configure one or two independently programmable areas of the flash memory as read protected, write protected, or read/write protected.

A protected partition may be protected by either/both of these hardware mechanisms:

- 64-bit protection key

- Hard-wired LOCK# signal

If the Lock option is enabled (by means of software) and the LOCK# signal is asserted, the protected partition has an additional hardware lock that prevents read/write access to the partition, even with the use of the correct protection key.

The size and protection attributes of the protected partition are defined during the media-formatting stage.

In the event of an attempt to bypass the protection mechanism, illegally modify the protection key or in any way sabotage the configuration parameters, the entire DiskOnChip G4 becomes both read and write protected, and is completely inaccessible.

For further information on hardware protection, please refer to the *TrueFFS Software Development Kit (SDK)* developer guide.

## 3.4.2 Unique Identification (UID) Number

Each DiskOnChip G4 is assigned a 16-byte UID number. Burned onto the flash during production, the UID cannot be altered and is unique worldwide. The UID is essential in security-related applications, and can be used to identify end-user products in order to fight fraudulent duplication by imitators.

## 3.4.3 One-Time Programmable (OTP) Area

The 16KB OTP area is user programmable for complete customization. The user can write to this area once, after which it is automatically and permanently locked. After it is locked, the OTP area becomes read only, just like a ROM device.

Regardless of the state of any of the LOCK bytes, the OTP pages cannot be erased.

Typically, the OTP area is used to store customer and product information such as: product ID, software version, production data, customer ID, Service provider information and tracking information.

## 3.4.4 One-Time Write (ROM-Like) Partition

A partition in the DiskOnChip G4 can be set as One-Time Write. After it is locked, this partition becomes read only, just like a ROM device. Its capacity is defined during the media-formatting stage.

## 3.4.5 Sticky Lock (SLOCK)

The boot partition can be locked automatically by hardware after the boot phase is completed and the device is in Normal mode. This is done by setting the Sticky Lock (SLOCK) bit in the Output Control register to 1. This has the same effect as asserting the LOCK# signal. Once set, SLOCK can only be cleared by asserting the RSTIN# input. Like the LOCK# input, assertion of this bit prevents the protection key from disabling the protection for a given partition. There is no need to mount the partition before calling a hardware protection routine.

This feature can be useful when the boot code in the boot partition must be read/write protected. Upon power-up, the boot code must be unprotected so the CPU can boot directly from DiskOnChip. At the end of the boot process, protection can be set until the next power-up or reset.

# 3.5 Programmable Boot Block with eXecute In Place (XIP) Functionality

The Programmable Boot Block with XIP functionality enables DiskOnChip G4 to act as a boot device in addition to performing flash disk data storage functions. This eliminates the need for expensive, legacy NOR flash or any other boot device on the motherboard.

The Programmable Boot Block on DiskOnChip G4 is 2KB in size. The Download Engine (DE), described in the next section, expands the functionality of this block by copying the boot code from the flash into the boot block.

DiskOnChip G4 128MB (1Gb) devices may be cascaded in order to form a larger flash disk. When DiskOnChip G4 128MB (1Gb) is connected with a standard NOR-like interface, up to four devices may be cascaded to create a 4Gb flash disk. When DiskOnChip G4 128MB (1Gb) is connected with a multiplexed interface, up to two devices may be cascaded to create a 256MB (2Gb) flash disk.

- Notes: 1. When more than one DiskOnChip G4 128MB (1Gb) device is cascaded, a maximum boot block of 2KB is available.

- 2. The Programmable Boot Block size available for DiskOnChip G4 256MB (2Gb) is 2 KB as well.

# 3.6 Download Engine (DE)

Upon power-up or when the RSTIN# signal is asserted, the DE automatically downloads the Initial Program Loader (IPL) to the Programmable Boot Block. The IPL is responsible for starting the booting process. The download process is quick, and is designed so that when the CPU accesses DiskOnChip G4 for code execution, the IPL code is already located in the Programmable Boot Block. During the download process, DiskOnChip G4 does not respond to read or write accesses. Host systems must therefore observe the requirements described in Section 10.3.8.

In addition, the DE downloads the data protection rules from the flash to the Protection State Machines (PSM), so that DiskOnChip G4 is secure and protected from the first moment it is active.

During the download process, DiskOnChip G4 asserts the BUSY# signal to indicate to the system that it is not yet ready to be accessed. Once BUSY# is negated, the system can access DiskOnChip G4.

A failsafe mechanism prevents improper initialization due to a faulty VCC or invalid assertion of the RSTIN# input. Another failsafe mechanism is designed to overcome possible NAND flash data errors. It prevents internal registers from powering up in a state that bypasses the intended data protection. In addition, any attempt to sabotage the data structures causes the entire DiskOnChip to become both read and write protected, and completely inaccessible.

# 3.7 Error Detection Code/Error Correction Code (EDC/ECC)

Because NAND-based MLC flash is prone to errors, it requires unique error-handling capability. M-Systems' x2 technology implements 4-bit Error Detection Code/Error Correction Code (EDC/ECC), based on a patented combination of Bose, Chaudhuri and Hocquenghem (BCH) and Hamming code algorithms. Error Detection Code (EDC) is implemented in hardware to optimize performance, while Error Correction Code (ECC) is performed in software, when required, to save silicon costs.

Each time a 512-byte page is written, additional parity bits are calculated and written to the flash. Each time data is read from the flash, the parity bits are read and used to calculate error locations.

The Hamming code can detect 2 errors per page and correct 1 error per page. The BCH code can detect and correct 4 errors per page. It can even detect 5 errors per page with a probability of 99.9%. It ensures that the minimal amount of code required is used for detection and correction to deliver the required reliability without degrading performance.

# 3.8 Control and Status

The Control and Status block contains registers responsible for transferring address, data and control information between the DiskOnChip TrueFFS driver and the flash media. Additional registers are used to monitor the status of the flash media (ready/busy) and the DiskOnChip controller. For further information on the DiskOnChip registers, refer to Section 7.

## 3.9 Flash Architecture

DiskOnChip G4 128MB (1Gb) consists of one 128MB (1Gb) flash planes that consist of 512 blocks, organized in 128 pages, as follows:

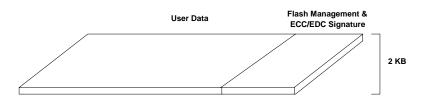

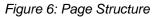

- **Page** Each page contains 2048 bytes of user data and a 64-byte extra area that is used to store flash management and EDC/ECC signature data, as shown in Figure 6.

- **Block (Erase Unit)** Each block contains 128 pages (total of 256KB), as shown in Figure 7. A block is the minimal unit that can be erased, and is sometimes referred to as an erase block.

Figure 7: Block Structure

## 4. x2 TECHNOLOGY

DiskOnChip G4 enhances performance using various proprietary techniques:

- MultiBurst operation to read large chunks of data, providing a MultiBurst read speed of up to 15 MB/sec.

- DMA operation to release the CPU for other tasks in coordination with the platform's DMA controller. This is especially useful during the boot stage. Up to 256KB of data can be transferred during a DMA operation.

## 4.1 MultiBurst Operation

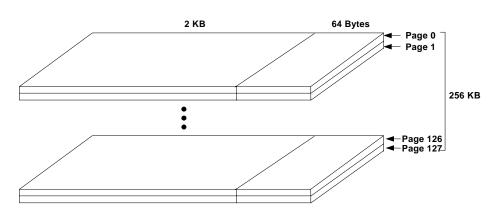

MultiBurst operation is especially effective for large file reads that are typical during boot-up. During MultiBurst operation, data is read from the flash through a 16-bit wide internal flash interface. Data is read by the host one 16-bit word after another using the CLK input, resulting in a MultiBurst read mode of up to 15 MB/sec. MultiBurst operation can only be performed on hosts that support burst reads. See Figure 8 below.

Note: A 30 nsec cycle time during MultiBurst can be achieved at VCC = VCCQ =  $1.65 \sim 1.95$ V).

Figure 8: MultiBurst Operation

Note: DiskOnChip G4 does not support MultiBurst write operations.

MultiBurst operation is controlled by 5 bits in the MultiBurst Mode Control register: BURST\_EN, CLK\_INV, LATENCY, HOLD and LENGTH. For full details on this register, please refer to Section 7.

MultiBurst mode read cycles are supported via the CLK input, which is enabled by setting the BURST\_EN bit in the MultiBurst Mode Control register.

To determine whether the rising or falling edge of the CLK input is sampled (called CLK0), the CLK\_INV bit in the MultiBurst Mode Control register must be specified. When the CLK\_INV bit is set to 0, CE# and OE# are sampled on the rising edge of CLK; when the CLK\_INV bit is set to 1, sampling is done on the falling edge of CLK.

- Notes: 1. When the CLK\_INV bit is set to 1, sampling is done on the falling edge of CLK, and an additional half-clock cycle of latency is incurred. Data continues to be output on D[15:0] on the rising edge of CLK.

- 2. Burst mode is disabled upon assertion of the RSTIN# input, and the signal may therefore be left floating.

The LATENCY field is the third field that must be set in the MultiBurst Mode Control register. When the LATENCY field is set to 0, the host can latch the first 16-bit data word two clock cycles after CLK0. This time can be extended by up to seven clock cycles by programming the LATENCY field. After latching the first word, additional 16-bit data words can be latched on each subsequent clock cycle.

The HOLD bit in the MultiBurst Mode Control register can be set to hold each data word valid for two clock cycles rather than one.

The LENGTH field in the MultiBurst Mode Control register must be programmed with the length of the burst to be performed. As read cycles from the flash are volatile, each burst cycle must read exactly this number of words.

The CLK input can be toggled continuously or can be halted. When halting the CLK input, the following guidelines must be observed:

- After asserting OE# and CE#, LATENCY + 2 CLK cycles are required prior to latching the first word (2.5 CLK cycles if CLK\_INV is set to 1).

- If the HOLD bit is set to 0, the host must provide one rising CLK edge for each word read, except for the last word latched, for which CLK does not need to be toggled.

- If the HOLD bit is set to 1, the host must provide two rising CLK edges for each word read, except for the last word, for which the second of the two CLK rising edges is not required.

- Subsequent toggling of the CLK is optional.

Two modes are provided to improve compatibility with hosts which can provide only a high CLK frequency. In each of these modes, a clock divider is used to generate only one DiskOnChip clock cycle for every two cycles of the CLK input.

• Hold mode: Causes each data word to be held for two clock cycles instead of one. Best used on platforms which support Hold mode and offer large burst lengths.

- FIFO mode: Enables FIFO in the data path. The FIFO outputs data on each cycle of the CLK input, while the FIFO is filled with Flash data on every other cycle.

- 16-bit hosts: Burst length is limited to 16 bytes. One cycle of latency is required for each word in the burst length. Best used on platforms which do not support Hold mode or which offer only shorter burst lengths.

- 8-bit host: No special limits on burst length, and only one additional cycle of latency is required.

Note: Hold and FIFO modes are enabled by the HOLD and FIFO bits bit of Burst Mode control Register respectively. Usage of these modes is mutually exclusive.

# 4.2 DMA Operation

DiskOnChip G4 provides a DMARQ# output that enables up to 256KB to be read from the flash by the host DMA controller. During DMA operation, the DMARQ# output is used to notify the host DMA controller that the next flash page is ready to be read, and the IRQ# pin indicates whether an error occurred while reading the data from the flash or the end of the DMA transfer was reached.

The DMARQ# output sensitivity is chosen by setting the EDGE bit in the DMA Control register[0]:

- Edge The DMARQ# output pulses to logic 0 for 250~500 nsec to indicate to the DMA controller that a flash page is ready to be read. The EDGE bit is set to 1 for this mode.

- Level The DMARQ# output is asserted to initiate the block transfer and returns to the negated state at the end of each block transfer. The EDGE bit is set to 0 for this mode.

The following steps are required to initiate a DMA operation:

- 1. Initialize the platform's DMA controller to transfer 512 bytes upon each assertion of the DMARQ# output. If the DMA controller supports an edge-sensitive DMARQ# signal, then initialize the DMA controller to transfer 512 bytes upon each DMA request. If the DMA controller supports a level-sensitive DMARQ# signal, then initialize the DMA controller to transfer data while DMARQ# is asserted.

- 2. Set the bits in the Interrupt Control register (see Section 7) to enable interrupts on an ECC error and at the end of the DMA operation.

- 3. Write to the DMA Control register[0] to set the DMA\_EN bit, the EDGE bit and the number of sectors (SECTOR\_COUNT field) to be transferred to the host. At this point, DiskOnChip G4 generates a DMA request to indicate to the host that it is ready to transfer data.

- 4. The host DMA controller reads one sector (512 bytes) of data from DiskOnChip G4.

- 5. If an ECC error is detected, an interrupt is generated (IRQ# signal asserted), the transfer of data is halted and control is returned to the host. If no ECC error is detected, a DMA request is initiated (DMARQ# signal asserted) and the next sector is read by the host.

- 6. The process continues until the last sector is read, after which DiskOnChip G4 generates an interrupt (IRQ# signal asserted) to indicate that it has transferred the last byte.

- Notes: 1. DiskOnChip G4 generates a DMA request (DMARQ# signal asserted) after the last byte is read. It may therefore be necessary to clear the final DMA request from the DMA controller.

- 2. DMA operation may be aborted after transferring each 512-byte block (step 4) by clearing the DMA\_EN bit in the DMA Control register[0].

# 4.3 Combined MultiBurst Mode and DMA Operation

When using MultiBurst mode and DMA operation together, and an interrupt is generated (IRQ# signal asserted), the Download Status register cannot be polled, as it will not comply with the MultiBurst mode timing specification. The following sequence is therefore required to respond to an interrupt request while in MultiBurst mode:

- Perform 7 write cycles to the NOP register.

- Turn off MultiBurst mode by writing to the MultiBurst Mode Control register.

# 5. HARDWARE PROTECTION

## 5.1 Method of Operation

DiskOnChip G4 enables the user to define two partitions that are protected (in hardware) against any combination of read or write operations. The two protected areas can be configured as read protected or write protected, and are protected by a protection key (i.e. password) defined by the user. Each of the protected areas can be configured separately and can function separately, providing maximum flexibility for the user.

The size and protection attributes (protection key, read, write, changeable, lock) of the protected partition are defined in the media formatting stage (DFORMAT utility or the format function in the TrueFFS SDK).

In order to set or remove read/write protection, the protection key (i.e., password) must be used, as follows:

- Insert the protection key to remove read/write protection.

- Remove the protection key to set read/write protection.

DiskOnChip G4 has an additional hardware safety measure. If the Lock option is enabled (by means of software) and the LOCK# signal is asserted, the protected partition has an additional hardware lock that prevents read/write access to the partition, even with the use of the correct protection key. It is possible to set the Lock protection for one session only; that is, until the next power-up or reset. This Sticky Lock feature can be useful when the boot code in the boot partition must be read/write protected. Upon power-up, the boot code must be unprotected so the CPU can run it directly from DiskOnChip G4. At the end of the boot process, protection can be set until the next power-up or reset.

Setting the Sticky Lock (SLOCK) bit in the Output Control register to 1 has the same effect as asserting the LOCK# signal. Once set, SLOCK can only be cleared by asserting the RSTIN# input. Like the LOCK# input, the assertion of this bit prevents the protection key from disabling the protection for a given partition. For more information, see Section 3.4.5. The target partition does require mounting before calling a hardware protection routine.

The only way to read or write from a protected partition is to insert the key (even DFORMAT cannot remove the protection). This is also true for modifying its attributes (protection key, read, write and lock). Read/write protection is disabled (the key is automatically removed) in each of the following events:

- Power-down

- Change of any protection attribute (not necessarily in the same partition)

- Write operation to the IPL area

- Removal of the protection key.

For further information on hardware protection, please refer to the *TrueFFS Software Development Kit (SDK)* developer guide.

# 6. MODES OF OPERATION

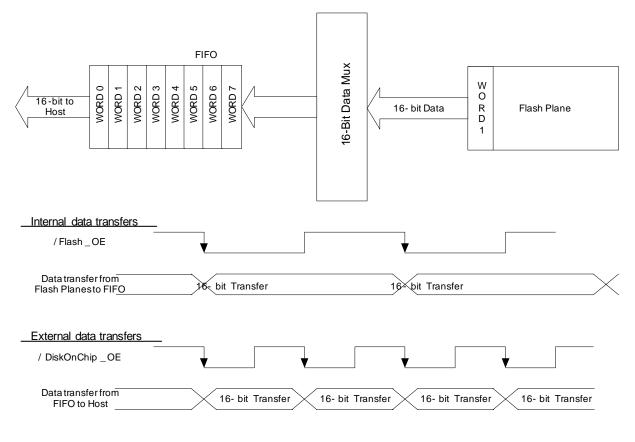

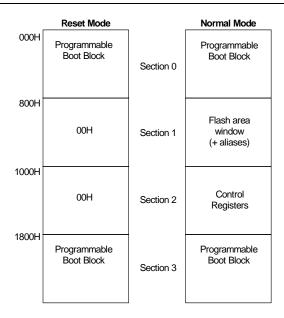

DiskOnChip G4 operates in one of three basic modes:

- Normal mode

- Reset mode

- Deep Power-Down mode

The current mode of the chip can always be determined by reading the DiskOnChip Control register. Mode changes can occur due to any of the following events:

- Assertion of the RSTIN# signal sets the device in Reset mode.

- During host power-up, boot detector circuitry sets the device in Reset mode.

- A valid write sequence to DiskOnChip G4 sets the device in Normal mode. This is done automatically by the TrueFFS driver on power-up (reset sequence end).

- Switching back from Normal mode to Reset mode can be done by a valid write sequence to DiskOnChip G4, or by triggering the boot detector circuitry (via a soft reset).

- Deep Power-Down

- A valid write sequence, initiated by software, sets the device from Normal mode to Deep Power-Down mode. Twelve read cycles from offset 0x1FFF set the device back to Normal mode. Alternately, the device can be set back to Normal mode with an extended access time during a read from the Programmable Boot Block.

- Asserting the RSTIN# signal and holding it in this state puts the device in Deep Power-Down mode. When RSTIN# is released, the device is left in Reset mode.

- Toggling the DPD signal as defined by the DPD Control register.

Figure 9: Operation Modes and Related Events

# 6.1 Normal Mode

This is the mode in which standard operations involving the flash memory are performed. Normal mode is entered when a valid write sequence is sent to the DiskOnChip Control register and Control Confirmation register. A write cycle occurs when both the CE# and WE# inputs are asserted. Similarly, a read cycle occurs when both the CE# and OE# inputs are asserted. Because the flash controller generates its internal clock from these CPU bus signals and some read operations return volatile data, it is essential that the timing requirements specified in Section 10.3 be met. It is also essential that read and write cycles not be interrupted by glitches or ringing on the CE#, WE#, and OE# inputs. All inputs to DiskOnChip G4 are Schmidt Trigger types to improve noise immunity.

# 6.2 Reset Mode

In Reset mode, DiskOnChip G4 ignores all write cycles, except for those to the DiskOnChip Control register and Control Confirmation register. All register read cycles return a value of 00H.

Before attempting to perform any operation, the device is set to Normal mode by TrueFFS software.

## 6.3 Deep Power-Down Mode

While in Deep Power-Down mode, DiskOnChip G4's quiescent power dissipation is reduced by disabling internal high current consumers (e.g. voltage regulators, input buffers, oscillator etc.). The following signals are also disabled in this mode:

- Standard interface: Input buffers A[12:0], WE#, D[15:0] and OE# (when CE# is negated)

- **Multiplexed interface**: Input buffers AD[15:0], AVD#, WE# and OE# (when CE# is negated).

To enter Deep Power-Down mode, a proper sequence must be written to the DiskOnChip G4 Control registers and the CE# input must be negated. All other inputs should be VSS or VCC.

Asserting the RSTIN# signal and holding it in low state puts the device in Deep Power-Down mode. When the RSTIN# signal is released, the device is left in Reset mode.

Toggling the DPD signal, as defined by the DPD Control register, puts the device in Power-Down mode as well.