# 1-Mbit (128K x 8) Static RAM

#### **Features**

- Pin- and function-compatible with CY7C1019B

- · High speed

- $t_{AA} = 10 \text{ ns}$

- · Low active power

- $I_{CC} = 80 \text{ mA} @ 10 \text{ ns}$

- · Low CMOS standby power

- $I_{SB2} = 3 \text{ mA}$

- · 2.0V Data retention

- · Automatic power-down when deselected

- · CMOS for optimum speed/power

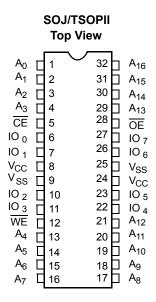

- · Center power/ground pinout

- Easy memory expansion with  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  options

- Functionally equivalent to CY7C1019B

- Available in Pb-free 32-pin 400-Mil wide Molded SOJ and 32-pin TSOP II packages

## Functional Description [1]

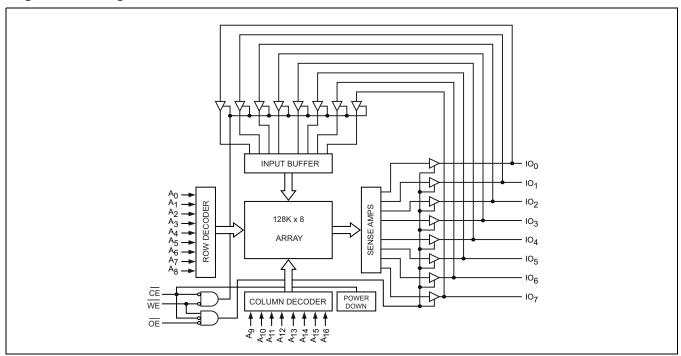

The CY7C1019D is a high-performance CMOS static RAM organized as 131,072 words by 8 bits. Easy memory expansion is provided by an active LOW Chip Enable ( $\overline{\text{CE}}$ ), an active LOW Output Enable ( $\overline{\text{OE}}$ ), and tri-state drivers. This device has an automatic power-down feature that significantly reduces power consumption when deselected. The eight input and output pins ( $\text{IO}_0$  through  $\text{IO}_7$ ) are placed in a high-impedance state when:

- Deselected (CE HIGH)

- Outputs are disabled (OE HIGH)

- When the write operation is active (CE LOW, and WE LOW).

Write to the device by taking Chip Enable ( $\overline{\text{CE}}$ ) and Write Enable ( $\overline{\text{WE}}$ ) inputs LOW. Data on the eight IO pins (IO<sub>0</sub> through IO<sub>7</sub>) is then written into the location specified on the address pins (A<sub>0</sub> through A<sub>16</sub>).

Read from the device by taking Chip Enable  $(\overline{CE})$  and Output Enable  $(\overline{OE})$  LOW while forcing Write Enable  $(\overline{WE})$  HIGH. Under these conditions, the contents of the memory location specified by the address pins appears on the IO pins.

## **Logic Block Diagram**

#### Note

1. For guidelines on SRAM system design, please refer to the 'System Design Guidelines' Cypress application note, available on the internet at www.cypress.com.

Cypress Semiconductor Corporation

Document #: 38-05464 Rev. \*F

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

## **Pin Configuration**

## **Selection Guide**

|                           | –10 (Industrial) | Unit |

|---------------------------|------------------|------|

| Maximum Access Time       | 10               | ns   |

| Maximum Operating Current | 80               | mA   |

| Maximum Standby Current   | 3                | mA   |

## **Maximum Ratings**

Exceeding the maximum ratings may impair the useful life of the device. These user guidelines are not tested. Storage Temperature .......-65°C to +150°C Ambient Temperature with Power Applied ......-55°C to +125°C Supply Voltage on  $V_{CC}$  to Relative GND  $^{[2]}$  ...  $^{-0.5}$ V to +6.0V DC Voltage Applied to Outputs in High-Z State  $^{[2]}$  .....-0.5V to  $V_{CC}$  + 0.5V DC Input Voltage  $^{[2]}$  .....-0.5V to  $V_{CC}$  + 0.5V

| Current into Outputs (LOW)                             | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | > 2001V |

| Latch-up Current>                                      | 200 mA  |

## **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> | Speed |

|------------|------------------------|-----------------|-------|

| Industrial | –40°C to +85°C         | 5V ± 0.5V       | 10 ns |

## Electrical Characteristics (Over the Operating Range)

| Davamatav        | December 1                                     | Took Conditions                                                                                                                                                                                                |                 | –10 (Inc | dustrial)             | Unit |

|------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----------------------|------|

| Parameter        | Description                                    | Test Conditions                                                                                                                                                                                                | rest conditions |          | Max                   | Jill |

| V <sub>OH</sub>  | Output HIGH Voltage                            | I <sub>OH</sub> = -4.0 mA                                                                                                                                                                                      |                 | 2.4      |                       | V    |

| V <sub>OL</sub>  | Output LOW Voltage                             | I <sub>OL</sub> = 8.0 mA                                                                                                                                                                                       |                 |          | 0.4                   | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                             |                                                                                                                                                                                                                |                 | 2.2      | V <sub>CC</sub> + 0.5 | V    |

| V <sub>IL</sub>  | Input LOW Voltage [2]                          |                                                                                                                                                                                                                |                 | -0.5     | 0.8                   | V    |

| I <sub>IX</sub>  | Input Leakage Current                          | $GND \le V_1 \le V_{CC}$                                                                                                                                                                                       |                 | -1       | +1                    | μΑ   |

| I <sub>OZ</sub>  | Output Leakage Current                         | $GND \le V_I \le V_{CC}$ , Output Disabl                                                                                                                                                                       | ed              | -1       | +1                    | μА   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating Supply Current       | V <sub>CC</sub> = Max,                                                                                                                                                                                         | 100 MHz         |          | 80                    | mA   |

|                  |                                                | $I_{OUT} = 0 \text{ mA},$<br>$f = f_{max} = 1/t_{RC}$                                                                                                                                                          | 83 MHz          |          | 72                    | mA   |

|                  |                                                | max No                                                                                                                                                                                                         | 66 MHz          |          | 58                    | mA   |

|                  |                                                |                                                                                                                                                                                                                | 40 MHz          |          | 37                    | mA   |

| I <sub>SB1</sub> | Automatic CE Power-Down<br>Current—TTL Inputs  | $\begin{aligned} &\text{Max V}_{CC}, \ \overline{CE} \geq \text{V}_{IH} \\ &\text{V}_{IN} \geq \text{V}_{IH} \text{ or V}_{IN} \leq \text{V}_{IL}, \ \text{f = f}_{max} \end{aligned}$                         |                 |          | 10                    | mA   |

| I <sub>SB2</sub> | Automatic CE Power-Down<br>Current—CMOS Inputs | $\begin{array}{c} \text{Max V}_{CC}, \ \overline{\text{CE}} \geq \text{V}_{CC} - 0.3\text{V}, \\ \text{V}_{\text{IN}} \geq \text{V}_{CC} - 0.3\text{V}, \text{ or V}_{\text{IN}} \leq 0.3\text{V} \end{array}$ | ', f = 0        |          | 3                     | mA   |

Note

<sup>2.</sup>  $V_{IL}$  (min) = -2.0V and  $V_{IH}$ (max) =  $V_{CC}$  + 1V for pulse durations of less than 5 ns.

## Capacitance [3]

| Parameter        | Description        | Test Conditions                                    | Max | Unit |

|------------------|--------------------|----------------------------------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C$ , $f = 1$ MHz, $V_{CC} = 5.0V$ | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance |                                                    | 8   | pF   |

## Thermal Resistance [3]

| Parameter     | Description                              | Test Conditions                                                         | 400-Mil<br>Wide SOJ | TSOP II | Unit |

|---------------|------------------------------------------|-------------------------------------------------------------------------|---------------------|---------|------|

| $\Theta_{JA}$ | Thermal Resistance (Junction to Ambient) | Still Air, soldered on a 3 × 4.5 inch, four-layer printed circuit board | 56.29               | 62.22   | °C/W |

| $\Theta_{JC}$ | Thermal Resistance (Junction to Case)    |                                                                         | 38.14               | 21.43   | °C/W |

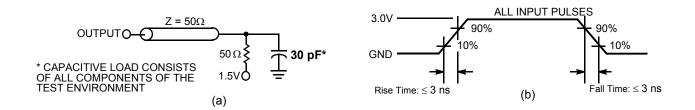

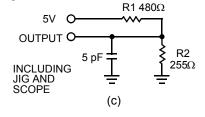

## AC Test Loads and Waveforms [4]

#### **High-Z characteristics:**

#### Notes

- 3. Tested initially and after any design or process changes that may affect these parameters.

- 4. AC characteristics (except High-Z) are tested using the load conditions shown in Figure (a). High-Z characteristics are tested for all speeds using the test load shown in Figure (c).

## Switching Characteristics (Over the Operating Range) [5]

| D                                          | Description.                                  | -10 (Inc | dustrial) | 11 14 |

|--------------------------------------------|-----------------------------------------------|----------|-----------|-------|

| Parameter                                  | Description                                   | Min      | Max       | Unit  |

| Read Cycle                                 |                                               | -        |           | 1     |

| t <sub>power</sub> <sup>[6]</sup>          | V <sub>CC</sub> (typical) to the first access | 100      |           | μS    |

| t <sub>RC</sub>                            | Read Cycle Time                               | 10       |           | ns    |

| t <sub>AA</sub>                            | Address to Data Valid                         |          | 10        | ns    |

| t <sub>OHA</sub>                           | Data Hold from Address Change                 | 3        |           | ns    |

| t <sub>ACE</sub>                           | CE LOW to Data Valid                          |          | 10        | ns    |

| t <sub>DOE</sub>                           | OE LOW to Data Valid                          |          | 5         | ns    |

| t <sub>LZOE</sub>                          | OE LOW to Low Z                               | 0        |           | ns    |

| t <sub>HZOE</sub>                          | OE HIGH to High Z [7, 8]                      |          | 5         | ns    |

| t <sub>LZCE</sub>                          | CE LOW to Low Z [8]                           | 3        |           | ns    |

| t <sub>HZCE</sub> CE HIGH to High Z [7, 8] |                                               |          | 5         | ns    |

| t <sub>PU</sub> <sup>[9]</sup>             | CE LOW to Power-Up                            | 0        |           | ns    |

| t <sub>PD</sub> <sup>[9]</sup>             | CE HIGH to Power-Down                         |          | 10        | ns    |

| Write Cycle [10,                           | 11]                                           | ·        |           |       |

| t <sub>WC</sub>                            | Write Cycle Time                              | 10       |           | ns    |

| t <sub>SCE</sub>                           | CE LOW to Write End                           | 7        |           | ns    |

| t <sub>AW</sub>                            | Address Set-Up to Write End                   | 7        |           | ns    |

| t <sub>HA</sub>                            | Address Hold from Write End                   | 0        |           | ns    |

| t <sub>SA</sub>                            | Address Set-Up to Write Start                 | 0        |           | ns    |

| t <sub>PWE</sub>                           | WE Pulse Width                                | 7        |           | ns    |

| t <sub>SD</sub>                            | Data Set-Up to Write End                      | 6        |           | ns    |

| t <sub>HD</sub>                            | Data Hold from Write End                      | 0        |           | ns    |

| t <sub>LZWE</sub>                          | WE HIGH to Low Z [8]                          | 3        |           | ns    |

| t <sub>HZWE</sub>                          | WE LOW to High Z [7, 8]                       |          | 5         | ns    |

- Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance.

- 6. t<sub>POWER</sub> gives the minimum amount of time that the power supply should be at typical V<sub>CC</sub> values until the first memory access can be performed.

7. t<sub>HZOE</sub>, t<sub>HZCE</sub>, and t<sub>HZWE</sub> are specified with a load capacitance of 5 pF as in (c) of "AC Test Loads and Waveforms [4]" on page 4. Transition is measured when the outputs enter a high impedance state.

- 8. At any given temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ ,  $t_{HZCE}$  is less than  $t_{LZOE}$ , and  $t_{HZWE}$  is less than  $t_{LZWE}$  for any given device.

- 9. This parameter is guaranteed by design and is not tested.

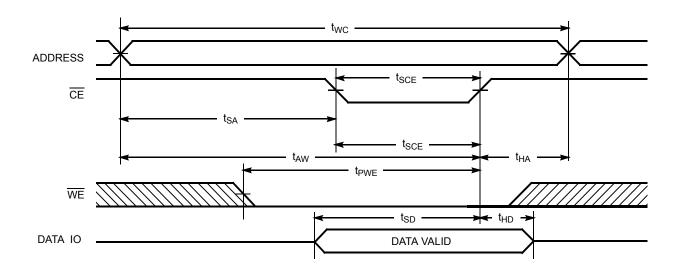

- 10. The internal write time of the memory is defined by the overlap of  $\overline{\text{CE}}$  LOW and  $\overline{\text{WE}}$  LOW.  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  must be LOW to initiate a write, and the transition of any of these signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.

- 11. The minimum write cycle time for Write Cycle no. 3 (WE controlled, OE LOW) is the sum of t<sub>HZWE</sub> and t<sub>SD</sub>.

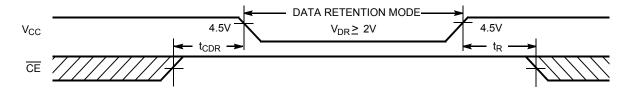

## Data Retention Characteristics (Over the Operating Range)

| Parameter                      | Description                          | Conditions                                                                                                        | Min             | Max | Unit |

|--------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|-----|------|

| $V_{DR}$                       | V <sub>CC</sub> for Data Retention   |                                                                                                                   | 2.0             |     | V    |

| I <sub>CCDR</sub>              | Data Retention Current               | $V_{CC} = V_{DR} = 2.0V, \overline{CE} \ge V_{CC} - 0.3V, \ V_{IN} \ge V_{CC} - 0.3V \text{ or } V_{IN} \le 0.3V$ |                 | 3   | mA   |

| t <sub>CDR</sub> [3]           | Chip Deselect to Data Retention Time |                                                                                                                   | 0               |     | ns   |

| t <sub>R</sub> <sup>[12]</sup> | Operation Recovery Time              |                                                                                                                   | t <sub>RC</sub> |     | ns   |

### **Data Retention Waveform**

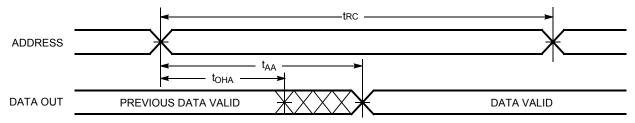

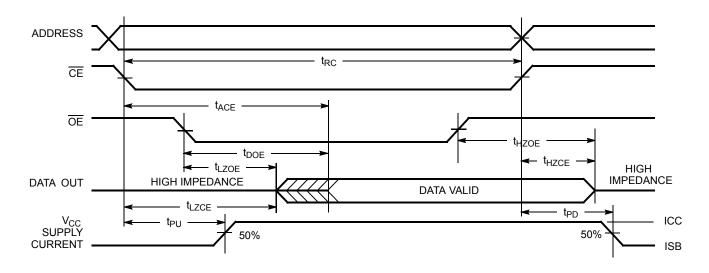

## **Switching Waveforms**

Read Cycle No. 1 (Address Transition Controlled) [13, 14]

Read Cycle No. 2 (OE Controlled) [14, 15]

### Notes

- 12. Full device operation requires linear  $V_{CC}$  ramp from  $V_{DR}$  to  $V_{CC(min)} \ge 50 \ \mu s$  or stable at  $V_{CC(min)} \ge 50 \ \mu s$ .

- 13. Device is continuously selected.  $\overline{OE}$ ,  $\overline{\overline{CE}} = V_{\parallel}$ .

- 14. WE is HIGH for Read cycle.

- 15. Address valid prior to or coincident with  $\overline{\text{CE}}$  transition LOW.

Document #: 38-05464 Rev. \*F

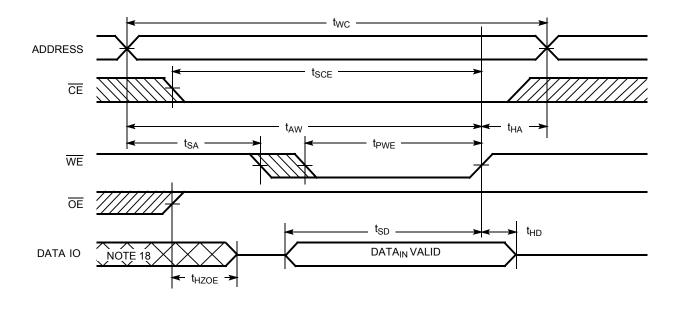

## Switching Waveforms (continued)

Write Cycle No. 1 (CE Controlled) [16, 17]

Write Cycle No. 2 (WE Controlled, OE HIGH During Write) [16, 17]

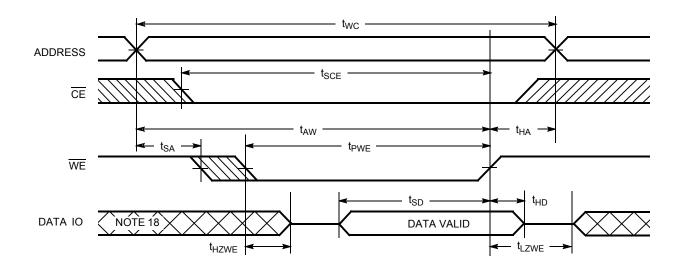

- 16. Data IO is high impedance if  $\overline{OE} = V_{\underline{IH}}$ .

17. If  $\overline{CE}$  goes HIGH simultaneously with  $\overline{WE}$  going HIGH, the output remains in a high-impedance state.

- 18. During this period the IOs are in the output state and input signals should not be applied.

Document #: 38-05464 Rev. \*F

## Switching Waveforms (continued)

Write Cycle No. 3 (WE Controlled, OE LOW) [11, 17]

## **Truth Table**

| CE | OE | WE | IO <sub>0</sub> -IO <sub>7</sub> | Mode                       | Power                      |

|----|----|----|----------------------------------|----------------------------|----------------------------|

| Н  | Х  | Х  | High Z                           | Power-Down                 | Standby (I <sub>SB</sub> ) |

| L  | L  | Н  | Data Out                         | Read                       | Active (I <sub>CC</sub> )  |

| L  | Х  | L  | Data In                          | Write                      | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | High Z                           | Selected, Outputs Disabled | Active (I <sub>CC</sub> )  |

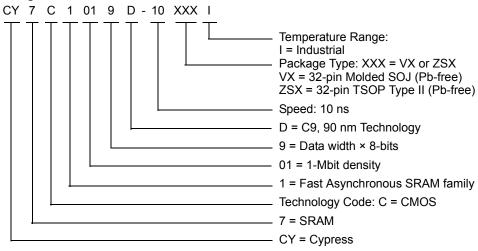

## **Ordering Information**

| Speed (ns) | Ordering Code    | Package<br>Diagram | Package Type                          | Operating<br>Range |

|------------|------------------|--------------------|---------------------------------------|--------------------|

| 10         | CY7C1019D-10VXI  | 51-85033           | 32-pin (400-Mil) Molded SOJ (Pb-free) | Industrial         |

|            | CY7C1019D-10ZSXI | 51-85095           | 32-pin TSOP Type II (Pb-free)         |                    |

## **Ordering Code Definitions**

Please contact your local Cypress sales representative for availability of these parts.

[+] Feedback

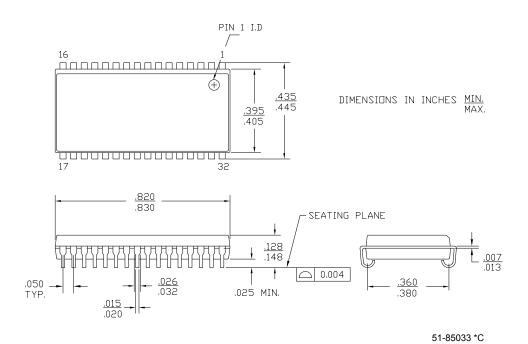

## **Package Diagrams**

Figure 1. 32-pin (400-Mil) Molded SOJ (51-85033)

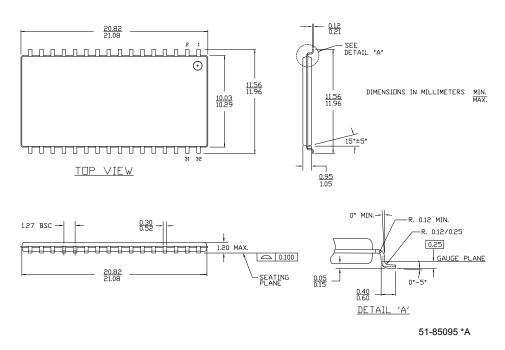

## Package Diagrams (continued)

Figure 2. 32-pin Thin Small Outline Package Type II (51-85095)

All product or company names mentioned in this document may be the trademarks of their respective holders.

[+] Feedback

## **Document History Page**

| REV. | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                            |

|------|---------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 201560  | See ECN    | SWI                | Advance Information data sheet for C9 IPP                                                                                                                                                                                                                                                                                        |

| *A   | 233715  | See ECN    | RKF                | DC parameters are modified as per EROS (Spec # 01-2165) Pb-free offering in the Ordering Information                                                                                                                                                                                                                             |

| *B   | 262950  | See ECN    | RKF                | Added T <sub>power</sub> Spec in Switching Characteristics table Added Data Retention Characteristics table and waveforms Shaded Ordering Information                                                                                                                                                                            |

| *C   | 307598  | See ECN    | RKF                | Reduced Speed bins to -10 and -12 ns                                                                                                                                                                                                                                                                                             |

| *D   | 520647  | See ECN    | VKN                | Converted from Preliminary to Final Removed Commercial Operating range Removed 12 ns speed bin Added I <sub>CC</sub> values for the frequencies 83MHz, 66MHz and 40MHz Updated Thermal Resistance table Updated Ordering Information Table Changed Overshoot spec from V <sub>CC</sub> +2V to V <sub>CC</sub> +1V in footnote #2 |

| *E   | 802877  | See ECN    | VKN                | Changed I $_{\rm CC}$ spec from 60 mA to 80 mA for 100MHz, 55 mA to 72 r for 83MHz, 45 mA to 58 mA for 66MHz, 30 mA to 37 mA for 40MHz                                                                                                                                                                                           |

| *F   | 3110052 | 12/14/2010 | AJU                | Added Ordering Code Definitions. Updated Package Diagrams.                                                                                                                                                                                                                                                                       |

## Sales, Solutions, and Legal Information

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

#### **Products**

Automotive cypress.com/go/automotive Clocks & Buffers cypress.com/go/clocks Interface cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc

Memory cypress.com/go/memory

Optical & Image Sensing cypress.com/go/image

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/USB

Wireless/RF cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5