3.3V CMOS Static RAM 1 Meg (128K x 8-Bit) **Center Power & Ground Pinout**

IDT71V124SA

#### **Features**

- 128K x 8 advanced high-speed CMOS static RAM

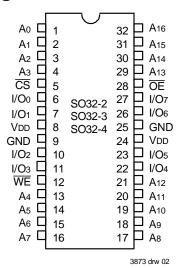

- JEDEC revolutionary pinout (center power/GND) for reduced noise

- Equal access and cycle times

- Commercial: 10/12/15ns

- Industrial: 12/15ns

- One Chip Select plus one Output Enable pin

- Inputs and outputs are LVTTL-compatible

- Single 3.3V supply

- Low power consumption via chip deselect

- Available in a 32-pin 300- and 400-mil Plastic SOJ, and 32-pin Type II TSOP packages.

### **Description**

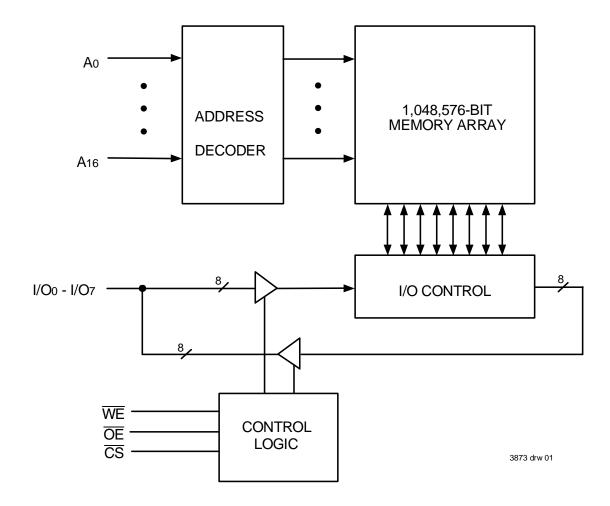

The IDT71V124 is a 1,048,576-bit high-speed static RAM organized as 128K x 8. It is fabricated using IDT's high-performance, high-reliability CMOS technology. This state-of-the-art technology, combined with innovative circuit design techniques, provides a cost-effective solution for highspeed memory needs. The JEDEC center power/GND pinout reduces noise generation and improves system performance.

The IDT71V124 has an output enable pin which operates as fast as 5ns, with address access times as fast as 9ns available. All bidirectional inputs and outputs of the IDT71V124 are LVTTL-compatible and operation is from a single 3.3V supply. Fully static asynchronous circuitry is used; no clocks or refreshes are required for operation.

### **Functional Block Diagram**

### **Pin Configuration**

SOJ and TSOP Top View

### Truth Table<sup>(1)</sup>

| CS | ŌĒ | WE | l/O     | Function             |

|----|----|----|---------|----------------------|

| L  | L  | Н  | DATAout | Read Data            |

| L  | Χ  | L  | DATAIN  | Write Data           |

| L  | Н  | Н  | High-Z  | Output Disabled      |

| Н  | Χ  | Χ  | High-Z  | Deselected – Standby |

NOTE:

1. H = VIH, L = VIL, X = Don't care.

## Capacitance

#### (TA = +25°C, f = 1.0MHz, SOJ package)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | VIN = 3dV  | 6    | pF   |

| Cvo    | I/O Capacitance          | Vout = 3dV | 7    | pF   |

NOTE

1. This parameter is guaranteed by device characterization, but is not production tested.

### Absolute Maximum Ratings(1)

| Symbol    | Rating                              | Value           | Unit |  |

|-----------|-------------------------------------|-----------------|------|--|

| VDD       | Supply Voltage Relative to GND      | -0.5 to +4.6    | ٧    |  |

| Vin, Vout | Terminal Voltage Relative to GND    | -0.5 to VDD+0.5 | V    |  |

| Ta        | Commercial<br>Operating Temperature | -0 to +70       | °C   |  |

| IA        | Industrial<br>Operating Temperature | -40 to +85      | Ç    |  |

| TBIAS     | Temperature Under Bias              | -55 to +125     | °C   |  |

| Tstg      | Storage Temperature                 | -55 to +125     | °C   |  |

| Рт        | Power Dissipation                   | 1.25            | W    |  |

| Іоит      | DC Output Current                   | 50              | mA   |  |

NOTE:

3873 tbl 01

3873 tbl 02

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

# Recommended Operating Temperature and Supply Voltage

| Grade      | Temperature    | GND | VDD       |

|------------|----------------|-----|-----------|

| Commercial | 0°C to +70°C   | 0V  | See Below |

| Industrial | -40°C to +85°C | 0V  | See Below |

3873 bl 02a

# Recommended DC Operating Conditions

| Symbol                         | Parameter          | Min.                | Тур. | Max.                                | Unit |

|--------------------------------|--------------------|---------------------|------|-------------------------------------|------|

| V <sub>DD</sub> <sup>(1)</sup> | Supply Voltage     | 3.15                | 3.3  | 3.6                                 | V    |

| V <sub>DD</sub> <sup>(2)</sup> | Supply Voltage     | 3.0                 | 3.3  | 3.6                                 | V    |

| Vss                            | Ground             | 0                   | 0    | 0                                   | V    |

| VIH                            | Input High Voltage | 2.0                 | _    | V <sub>DD</sub> +0.3 <sup>(3)</sup> | V    |

| VIL                            | Input Low Voltage  | -0.5 <sup>(1)</sup> |      | 0.8                                 | V    |

NOTES:

3873 tbl 04

- 1. For 71V124SA10 only.

- 2. For all speed grades except 71V124SA10.

- 3. VIH (max.) = VDD+2V for pulse width less than 5ns, once per cycle.

- 4.  $V_{IL}$  (min.) = -2V for pulse width less than 5ns, once per cycle.

### **DC Electrical Characteristics**

#### (VDD = Min. to Max., Commercial and Industrial Temperature Ranges)

| Symbol | Parameter              | Test Conditions                                                          | Min. | Max. | Unit |

|--------|------------------------|--------------------------------------------------------------------------|------|------|------|

| ILI    | Input Leakage Current  | VDD = Max., VIN = GND to VDD                                             | -    | 5    | μΑ   |

| ILO    | Output Leakage Current | $V_{DD} = Max.,\overline{CS} = V_{IH}, V_{OUT} = GND \text{ to } V_{DD}$ |      | 5    | μΑ   |

| Vol    | Output Low Voltage     | IOL = 8mA, VDD = Min.                                                    |      | 0.4  | V    |

| Vон    | Output High Voltage    | IOH = -4mA, $VDD = Min$ .                                                | 2.4  |      | V    |

3873 tbl 05

# DC Electrical Characteristics (1,2)

(VDD = Min. to Max., VLC = 0.2V, VHC = VDD - 0.2V)

|        | 71V124SA10 71V124SA12                                                                                                       |            | 71V124SA15 |     |       |     |      |

|--------|-----------------------------------------------------------------------------------------------------------------------------|------------|------------|-----|-------|-----|------|

| Symbol | Parameter                                                                                                                   | Commercial | Com'l      | Ind | Com'l | Ind | Unit |

| lcc    |                                                                                                                             | 145        | 130        | 140 | 100   | 120 | mA   |

| ISB    |                                                                                                                             | 45         | 40         | 40  | 35    | 40  | mA   |

| ISB1   | Full Standby Power Supply Current (static) $\overline{\text{CS}} \geq \text{VHC}$ , Outputs Open, VDD = Max., f = $0^{(3)}$ | 10         | 10         | 10  | 10    | 10  | mA   |

NOTES:

3873 tb1 06

- 1. All values are maximum guaranteed values.

- 2. All inputs switch between 0.2V (Low) and VDD-0.2V (High).

- 3. fmax = 1/trc (all address inputs are cycling at fmax); f = 0 means no address input lines are changing.

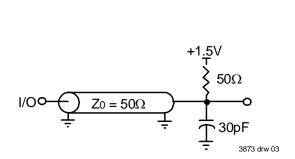

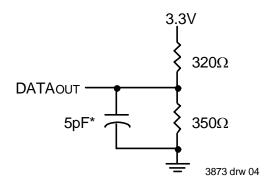

### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V        |

|-------------------------------|--------------------|

| Input Rise/Fall Times         | 3ns                |

| Input Timing Reference Levels | 1.5V               |

| Output Reference Levels       | 1.5V               |

| AC Test Load                  | See Figure 1 and 2 |

3873 tbl 07

Figure 1. AC Test Load

\*Including jig and scope capacitance.

Figure 2. AC Test Load (for tclz, tolz, tchz, tohz, tow, and twhz)

### **AC Electrical Characteristics**

(VDD = Min. to Max., Commercial and Industrial Temperature Ranges)

|                     |                                    | 71V124SA10 |      | 71V12 | 4SA12 | 71V12 | 4SA15 |      |

|---------------------|------------------------------------|------------|------|-------|-------|-------|-------|------|

| Symbol              | Parameter                          | Min.       | Max. | Min.  | Max.  | Min.  | Max.  | Unit |

| READ CYC            | READ CYCLE                         |            |      |       |       |       |       |      |

| trc                 | Read Cycle Time                    | 10         |      | 12    |       | 15    |       | ns   |

| taa                 | Address Access Time                |            | 10   |       | 12    |       | 15    | ns   |

| tacs                | Chip Select Access Time            |            | 10   |       | 12    |       | 15    | ns   |

| tclz <sup>(1)</sup> | Chip Select to Output in Low-Z     | 4          |      | 4     |       | 4     |       | ns   |

| tchz <sup>(1)</sup> | Chip Deselect to Output in High-Z  | 0          | 5    | 0     | 6     | 0     | 7     | ns   |

| toe                 | Output Enable to Output Valid      |            | 5    | _     | 6     |       | 7     | ns   |

| tolz <sup>(1)</sup> | Output Enable to Output in Low-Z   | 0          |      | 0     |       | 0     |       | ns   |

| tohz <sup>(1)</sup> | Output Disable to Output in High-Z | 0          | 5    | 0     | 5     | 0     | 5     | ns   |

| tон                 | Output Hold from Address Change    |            |      | 4     | _     | 4     | _     | ns   |

| WRITE CY            | CLE                                |            |      |       |       |       |       |      |

| twc                 | Write Cycle Time                   | 10         |      | 12    |       | 15    |       | ns   |

| taw                 | Address Valid to End-of-Write      | 7          |      | 8     | _     | 10    | _     | ns   |

| tcw                 | Chip Select to End-of-Write        | 7          |      | 8     |       | 10    | _     | ns   |

| tas                 | Address Set-up Time                | 0          |      | 0     |       | 0     |       | ns   |

| twp                 | Write Pulse Width                  | 7          |      | 8     | _     | 10    | _     | ns   |

| twr                 | Write Recovery Time                | 0          |      | 0     | _     | 0     | _     | ns   |

| tow                 | Data Valid to End-of-Write         | 5          |      | 6     | _     | 7     | _     | ns   |

| tDH                 | Data Hold Time                     |            | _    | 0     | _     | 0     | _     | ns   |

| tow <sup>(2)</sup>  | Output Active from End-of-Write    | 3          | _    | 3     | _     | 3     | _     | ns   |

| twhz <sup>(2)</sup> | Write Enable to Output in High-Z   | 0          | 5    | 0     | 5     | 0     | 5     | ns   |

NOTES:

3873 tbl 08

<sup>1.</sup> This parameter guaranteed with the AC load (Figure 2) by device characterization, but is not production tested.

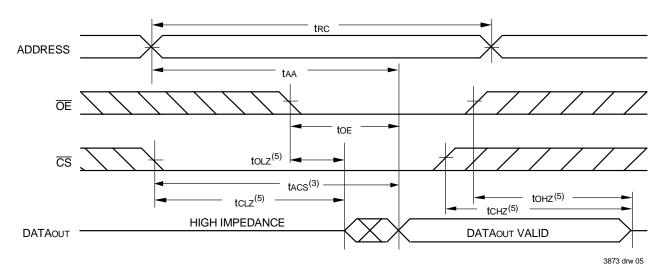

# Timing Waveform of Read Cycle No. 1<sup>(1)</sup>

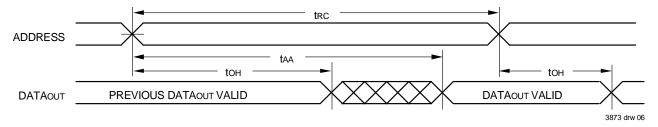

# Timing Waveform of Read Cycle No. 2<sup>(1, 2, 4)</sup>

#### NOTES:

- 1. WE is HIGH for Read Cycle.

- 2. Device is continuously selected,  $\overline{\text{CS}}$  is LOW.

- 3. Address must be valid prior to or coincident with the later of  $\overline{\text{CS}}$  transition LOW; otherwise tax is the limiting parameter.

- 4.  $\overline{\text{OE}}$  is LOW.

- 5. Transition is measured  $\pm 200 mV$  from steady state.

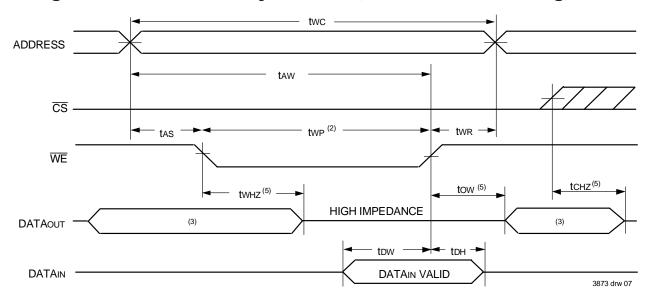

# Timing Waveform of Write Cycle No. 1 (WE Controlled Timing)(1,2,4)

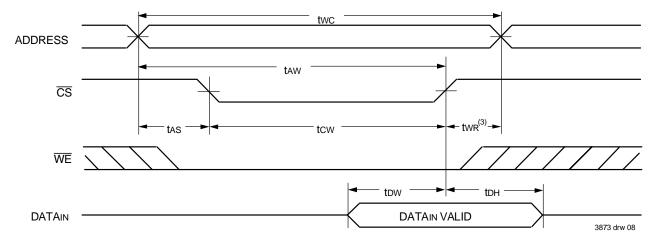

# Timing Waveform of Write Cycle No. 2 (CS Controlled Timing)(1, 4)

#### NOTES:

- 1. A write occurs during the overlap of a LOW  $\overline{\text{CS}}$  and a LOW  $\overline{\text{WE}}$ .

- 2.  $\overline{OE}$  is continuously  $\overline{H}$  GH. During a  $\overline{WE}$  controlled write cycle with  $\overline{OE}$  LOW, twp must be greater than or equal to twHz + tbw to allow the I/O drivers to turn off and data to be placed on the bus for the required tbw. If  $\overline{OE}$  is HIGH during a  $\overline{WE}$  controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp.

- 3. During this period, I/O pins are in the output state, and input signals must not be applied.

- 4. If the CSLOW transition occurs simultaneously with or after the WELOW transition, the outputs remain in a high impedance state. CS must be active during the tcw write period.

- 5. Transition is measured ±200mV from steady state.

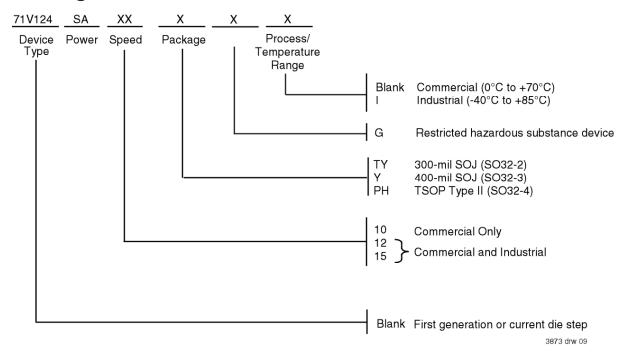

### **Ordering Information**

## **Datasheet Document History**

| 11/22/99 |             | Updated to newformat                                                             |

|----------|-------------|----------------------------------------------------------------------------------|

|          | Pg. 1-4, 7  | Added Industrial Temperature range offerings                                     |

|          | Pg. 2       | Added Recommended Operating Temperature and Supply Voltage table                 |

|          | Pg. 6       | Revised footnotes on Write Cycle No. 1 diagram                                   |

|          | Pg. 8       | Added Datasheet Document History                                                 |

| 08/30/00 | Pg. 3       | Tighten Icc and IsB                                                              |

|          | Pg. 4       | Tighten AC Characteristics to Hz, towand tw Hz                                   |

| 08/22/01 | Pg. 7       | Removed footnote "400-mil SOJ package only offered in 10ns and 12ns speed grade" |

| 11/30/03 | Pg. 1,3,7   | Added Industrial temperature offering 10ns speed grade                           |

| 01/30/04 | Pg. 7       | Added "Restricted hazardous substance device" to ordering information.           |

| 2/14/07  | Pg. 7       | Added H generation die step to data sheet ordering information.                  |

| 10/13/08 | Pg. 7       | Removed "IDT" from the orderable part number                                     |

| 11/15/10 | Pg. 1,3,4,7 | Removed 20ns commercial, 10ns & 20ns industrial and also removed HSA offering.   |

|          |             |                                                                                  |

CORPORATE HEADQUARTERS 6024 Silver Creek Valley Road San Jose, CA 95138

for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775

fax: 408-284-2775 www.idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

for Tech Support: ipchelp@idt.com 800-345-7015