March 1995 Revised March 2001

# GTLP16612 18-Bit TTL/GTLP Universal Bus Transceiver

#### **General Description**

The GTLP16612 is an 18-bit universal bus transceiver which provides TTL to GTLP signal level translation. The device is designed to provide a high speed interface between cards operating at TTL logic levels and a backplane operating at GTLP logic levels. High speed backplane operation is a direct result of GTLP's reduced output swing (<1V), reduced input threshold levels and output edge rate control which minimizes signal settling times. GTLP is a Fairchild Semiconductor derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD8-3.

Fairchild's GTLP has internal edge-rate control and is Process, Voltage, and Temperature (PVT) compensated. Its function is similar to BTL or GTL but with different driver output levels and receiver threshold. GTLP output low voltage is typically less than 0.5V, the output high is 1.5V and the receiver threshold is 1.0V.

#### **Features**

- Bidirectional interface between GTLP and TTL logic levels

- Designed with an edge rate control circuit to reduce output noise on GTLP port

- V<sub>REF</sub> pin provides external supply reference voltage for receiver threshold adjustability

- Special PVT compensation circuitry to provide consistent performance over variations of process, supply voltage and temperature

- TTL compatible Driver and Control inputs

- Designed using Fairchild advanced CMOS technology

- Bushold data inputs on A port to eliminate the need for external pull-up resistors for unused inputs

- Power up/down and power off high impedance for live insertion

- 5V tolerant inputs and outputs on LVTTL port

- Open drain on GTLP to support wired-or connection

- Flow-through pinout optimizes PCB layout

- D-type flip-flop, latch and transparent data paths

- A Port outputs source/sink −32 mA/+32 mA

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

| GTLP16612MEA | MS56A          | 56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300 Wide       |

| GTLP16612MTD | MTD56          | 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code

© 2001 Fairchild Semiconductor Corporation

DS012390

www.fairchildsemi.com

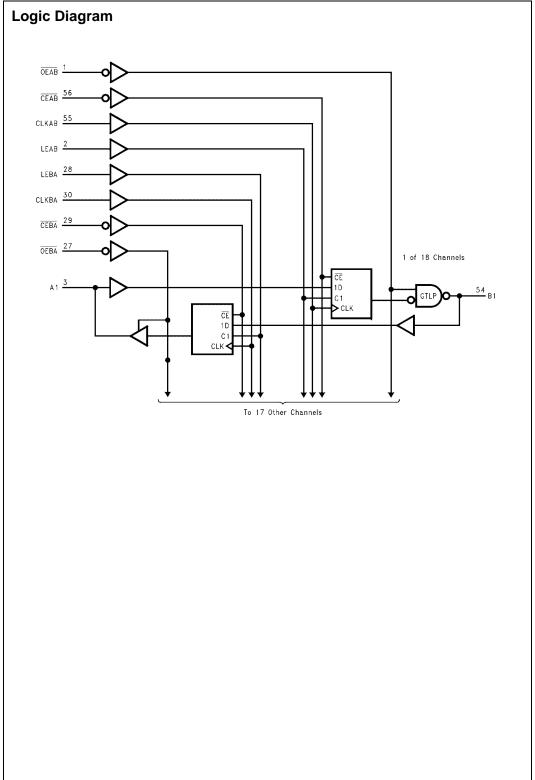

## **Pin Descriptions**

| Pin<br>Names | Description                            |

|--------------|----------------------------------------|

| OEAB         | A-to-B Output Enable (Active LOW)      |

| OEBA         | B-to-A Output Enable (Active LOW)      |

| CEAB         | A-to-B Clock Enable (Active LOW)       |

| CEBA         | B-to-A Clock Enable (Active LOW)       |

| LEAB         | A-to-B Latch Enable (Transparent HIGH) |

| LEBA         | B-to-A Latch Enable (Transparent HIGH) |

| CLKAB        | A-to-B Clock Pulse                     |

| CLKBA        | B-to-A Clock Pulse                     |

| $V_{REF}$    | GTLP Input Reference Voltage           |

| A1-A18       | A-to-B TTL Data Inputs or              |

|              | B-to-A 3-STATE Outputs                 |

| B1-B18       | B-to-A GTLP Data Inputs or             |

|              | A-to-B Open Drain Outputs              |

## **Connection Diagram**

#### **Functional Description**

The GTLP16612 combines a universal transceiver function with a TTL to GTLP translation. The A Port and control pins operate at LVTTL or 5V TTL levels while the B Port operates at GTLP levels. The transceiver logic includes D-type latches and D-type flip-flops to allow data flow in transparent, latched and clock mode.

The functional operation is described in the truth table below.

#### **Truth Table**

(Note 1)

| Inputs |      |      |            |   | Output                  | Mode            |

|--------|------|------|------------|---|-------------------------|-----------------|

| CEAB   | OEAB | LEAB | CLKAB      | Α | В                       |                 |

| Х      | Н    | Х    | Х          | Χ | Z                       | Latched         |

| L      | L    | L    | Н          | Χ | B <sub>0</sub> (Note 2) | storage         |

| L      | L    | L    | L          | Х | B <sub>0</sub> (Note 3) | of A data       |

| Х      | L    | Н    | Х          | Г | L                       | Transparent     |

| Х      | L    | Н    | X          | Н | Н                       |                 |

| L      | L    | L    | 1          | Г | L                       | Clocked storage |

| L      | L    | L    | $\uparrow$ | Н | Н                       | of A data       |

| Н      | L    | L    | Х          | Χ | B <sub>0</sub> (Note 3) | Clock inhibit   |

Note 1: A-to-B data flow is shown. B-to-A data flow is similar but uses  $\overline{\text{OEBA}}$ , LEBA, CLKBA, and  $\overline{\text{CEBA}}$ .

Note 2: Output level before the indicated steady-state input conditions were established, provided that CLKAB was HIGH before LEAB went LOW.

Note 3: Output level before the indicated steady-state input conditions were established.

#### **Absolute Maximum Ratings**(Note 4)

## Recommended Operating Conditions (Note 6)

$\label{eq:supply Voltage VCC} \begin{array}{ll} \text{Supply Voltage (V}_{\text{CC}}, \text{V}_{\text{CCQ}}) & -0.5 \text{V to } +7.0 \text{V} \\ \text{DC Input Voltage (V}_{\text{I}}) & -0.5 \text{V to } +7.0 \text{V} \\ \end{array}$

DC Input Voltage  $(V_1)$  = 0.5 V to +7.

DC Output Voltage  $(V_0)$

Outputs 3-STATE -0.5V to +7.0V Outputs Active (Note 5) -0.5V to  $V_{CC}$  + 0.5V

DC Output Sink Current into

A Port I<sub>OL</sub> 64 mA

DC Output Source Current from

A Port I<sub>OH</sub> –64 mA

DC Output Sink Current

into B Port in the LOW State,  $I_{\rm OL}$  80 mA

DC Input Diode Current (I<sub>IK</sub>)

$V_I < 0V$  -50 mA

DC Output Diode Current ( $I_{OK}$ )

$\label{eq:VO} \begin{array}{ccc} \rm V_O < 0V & -50 \; mA \\ & \rm V_O > V_{CC} & +50 \; mA \\ \\ \rm Storage \; Temperature \; (T_{STG}) & -65^{\circ}C \; to +150^{\circ}C \end{array}$

ESD Performance >2000V

Supply Voltage  $V_{\rm CC}$

$\begin{array}{c} \rm V_{CC} & 3.15V \ to \ 3.45V \\ \rm V_{CCQ} & 4.75V \ to \ 5.25V \\ \rm Bus \ Termination \ Voltage \ (V_{TT}) & 1.35V \ to \ 1.65V \\ \end{array}$

Input Voltage (V<sub>I</sub>)

on A Port and Control Pins 0.0V to 5.5V

HIGH Level Output Current (I<sub>OH</sub>)

A Port –32 mA

LOW Level Output Current (I<sub>OL</sub>)

A Port +32 mA B Port +34 mA

Operating Temperature  $(T_A)$   $-40^{\circ}C$  to  $+85^{\circ}C$ **Note 4:** The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristic tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 5: I<sub>O</sub> Absolute Maximum Rating must be observed.

Note 6: Unused inputs must be held HIGH or LOW.

#### **DC Electrical Characteristics**

Over Recommended Operating Free-Air Temperature Range,  $V_{\mbox{REF}} = 1.0V$  (Unless Otherwise Noted).

|                      | Symbol       | Test Condit                                              | tions                       | Min                   | Typ<br>(Note 7) | Max                   | Units |

|----------------------|--------------|----------------------------------------------------------|-----------------------------|-----------------------|-----------------|-----------------------|-------|

| V <sub>IH</sub>      | B Port       |                                                          |                             | V <sub>REF</sub> +0.1 |                 | V <sub>TT</sub>       | V     |

|                      | Others       | 7                                                        |                             | 2.0                   |                 |                       | V     |

| V <sub>IL</sub>      | B Port       |                                                          |                             | 0.0                   |                 | V <sub>REF</sub> -0.1 | V     |

|                      | Others       | 7                                                        |                             |                       |                 | 0.8                   | 1 '   |

| $V_{REF}$            |              |                                                          |                             |                       | 1.0             |                       | V     |

| V <sub>IK</sub>      |              | V <sub>CC</sub> = 3.15V,                                 | I <sub>I</sub> = -18 mA     |                       |                 | -1.2                  | V     |

|                      |              | $V_{CCQ} = 4.75V$                                        | 11 = -10 111A               |                       |                 | -1.2                  | ľ     |

| V <sub>OH</sub>      | A Port       | V <sub>CC</sub> , V <sub>CCQ</sub> = Min to Max (Note 8) | $I_{OH} = -100 \mu\text{A}$ | V <sub>CC</sub> - 0.2 |                 |                       |       |

|                      |              | V <sub>CC</sub> = 3.15V                                  | I <sub>OH</sub> = -8 mA     | 2.4                   |                 |                       | V     |

|                      |              | $V_{CCQ} = 4.75V$                                        | $I_{OH} = -32 \text{ mA}$   | 2.0                   |                 |                       | Ī     |

| V <sub>OL</sub>      | A Port       | V <sub>CC</sub> , V <sub>CCQ</sub> = Min to Max (Note 8) | $I_{OL} = 100 \mu A$        |                       |                 | 0.2                   |       |

|                      |              | V <sub>CC</sub> = 3.15V                                  | I <sub>OL</sub> = 32 mA     |                       |                 | 0.5                   | V     |

|                      |              | V <sub>CCQ</sub> = 4.75V                                 |                             |                       |                 |                       |       |

|                      | B Port       | V <sub>CC</sub> = 3.15V V <sub>CCQ</sub> = 4.75V         | I <sub>OL</sub> = 34 mA     |                       |                 | 0.65                  | V     |

| l <sub>l</sub>       | Control Pins | V <sub>CC</sub> , V <sub>CCQ</sub> = 0 or Max            | V <sub>I</sub> = 5.5V or 0V |                       |                 | ±10                   | μΑ    |

|                      | A Port       | V <sub>CC</sub> = 3.45V                                  | V <sub>I</sub> = 5.5V       |                       |                 | 20                    |       |

|                      |              | $V_{CCQ} = 5.25V$                                        | $V_I = V_{CC}$              |                       |                 | 1                     | μΑ    |

|                      |              |                                                          | $V_I = 0$                   |                       |                 | -30                   | Ī     |

|                      | B Port       | V <sub>CC</sub> = 3.45V                                  | $V_I = V_{CCQ}$             |                       |                 | 5                     | μА    |

|                      |              | $V_{CCQ} = 5.25V$                                        | $V_I = 0$                   |                       |                 | -5                    | μΑ    |

| I <sub>OFF</sub>     | A Port       | $V_{CC} = V_{CCQ} = 0$                                   | $V_I$ or $V_O = 0$ to 4.5V  |                       |                 | 100                   | μΑ    |

| I <sub>I(hold)</sub> | A Port       | V <sub>CC</sub> = 3.15V,                                 | $V_I = 0.8V$                | 75                    |                 |                       | μА    |

|                      |              | $V_{CCQ} = 4.75V$                                        | $V_1 = 2.0V$                | -20                   |                 |                       | μΑ    |

| I <sub>OZH</sub>     | A Port       | V <sub>CC</sub> = 3.45V,                                 | V <sub>O</sub> = 3.45V      |                       |                 | 1                     | μА    |

|                      | B Port       | V <sub>CCQ</sub> = 5.25V                                 | $V_0 = 1.5V$                |                       |                 | 5                     | μΛ    |

| I <sub>OZL</sub>     | A Port       | V <sub>CC</sub> = 3.45V,                                 | V <sub>O</sub> = 0          |                       |                 | -20                   | μА    |

|                      | B Port       | V <sub>CCQ</sub> = 5.25V                                 | $V_0 = 0.65V$               |                       |                 | -10                   | μΑ    |

## DC Electrical Characteristics (Continued)

|                     | Symbol       | Tes                    | t Conditions         | Min | Typ<br>(Note 7) | Max | Units |

|---------------------|--------------|------------------------|----------------------|-----|-----------------|-----|-------|

| I <sub>CCQ</sub>    | A or B       | $V_{CC} = 3.45V,$      | Outputs HIGH         |     | 30              | 40  |       |

| (V <sub>CCQ</sub> ) | Ports        | $V_{CCQ} = 5.25V$ ,    | Outputs LOW          |     | 30              | 40  | mA    |

|                     |              | $I_O = 0$ ,            |                      |     |                 |     | IIIA  |

|                     |              | $V_I = V_{CCQ}$ or GND | Outputs Disabled     |     | 30              | 40  |       |

| I <sub>CC</sub>     | A or B       | $V_{CC} = 3.45V,$      | Outputs HIGH         |     | 0               | 1   |       |

| (V <sub>CC</sub> )  | Ports        | $V_{CCQ} = 5.25V$ ,    | Outputs LOW          |     | 0               | 1   | mA    |

|                     |              | $I_O = 0$ ,            |                      |     |                 |     | IIIA  |

|                     |              | $V_I = V_{CCQ}$ or GND | Outputs Disabled     |     | 0               | 1   |       |

| $\Delta I_{CC}$     | A Port and   | $V_{CC} = 3.45V,$      | One Input at 2.7V    |     | 0               | 1   |       |

| (Note 9)            | Control Pins | $V_{CCQ} = 5.25V$ ,    |                      |     |                 |     | A     |

|                     |              | A or Control Inputs at |                      |     |                 |     | mA    |

|                     |              | V <sub>CC</sub> or GND |                      |     |                 |     |       |

| C <sub>IN</sub>     | Control Pins |                        | $V_I = V_{CCQ}$ or 0 |     | 8               |     |       |

| C <sub>I/O</sub>    | A Port       |                        | $V_I = V_{CCQ}$ or 0 |     | 9               |     | pF    |

| C <sub>I/O</sub>    | B Port       |                        | $V_I = V_{CCQ}$ or 0 |     | 6               |     |       |

Note 7: All typical values are at  $V_{CC} = 3.3V$ ,  $V_{CCQ} = 5.0V$ , and  $T_A = 25^{\circ}C$ .

## **AC Operating Requirements**

Over recommended ranges of supply voltage and operating free-air temperature,  $V_{REF} = 1.0V$  (unless otherwise noted).

| Symbol           |                         |                            |     | Max | Unit |

|------------------|-------------------------|----------------------------|-----|-----|------|

| f <sub>MAX</sub> | Maximum Clock Frequency |                            | 150 |     | MHz  |

| t <sub>W</sub>   | Pulse Duration          | LEAB or LEBA HIGH          | 3.0 |     |      |

|                  |                         | CLKAB or CLKBA HIGH or LOW | 3.2 |     | ns   |

| t <sub>S</sub>   | Setup Time              | A before CLKAB↑            | 0.5 |     |      |

|                  |                         | B before CLKBA↑            | 3.1 |     |      |

|                  |                         | A before LEAB↓             | 1.3 |     |      |

|                  |                         | B before LEBA↓             | 3.7 |     | ns   |

|                  |                         | CEAB before CLKAB↑         | 0.4 |     |      |

|                  |                         | CEBA before CLKBA↑         | 1.0 |     |      |

| t <sub>H</sub>   | Hold Time               | A after CLKAB↑             | 1.5 |     |      |

|                  |                         | B after CLKBA↑             | 0.0 |     |      |

|                  |                         | A after LEAB↓              | 0.5 |     |      |

|                  |                         | B after LEBA↓              | 0.0 |     | ns   |

|                  |                         | CEAB after CLKAB↑          | 1.5 |     |      |

|                  |                         | CEBA after CLKBA↑          | 1.7 |     |      |

Note 8: For conditions shown as Min or Max, use the appropriate value specified under recommended operating conditions.

$<sup>\</sup>textbf{Note 9:} \ \ \textbf{This is the increase in supply current for each input that is at the specified TTL voltage level rather than V_{CC} \ or \ GND.$

## **AC Electrical Characteristics**

Over recommended range of supply voltage and operating free-air temperature,  $V_{REF} = 1.0V$  (unless otherwise noted).  $C_L = 30$  pF for B Port and  $C_L = 50$  pF for A Port.

| Symbol                              | From                 | То                  | Min | Тур       | Max | Unit |

|-------------------------------------|----------------------|---------------------|-----|-----------|-----|------|

|                                     | (Input)              | (Output)            |     | (Note 10) |     |      |

| PLH                                 | A                    | В                   | 1.0 | 4.3       | 6.5 |      |

| PHL                                 |                      |                     | 1.0 | 5.0       | 8.2 | ns   |

| PLH                                 | LEAB                 | В                   | 1.8 | 4.5       | 6.7 | no   |

| PHL                                 |                      |                     | 1.5 | 5.3       | 8.6 | ns   |

| PLH                                 | CLKAB                | В                   | 1.8 | 4.6       | 6.7 | 20   |

| t <sub>PHL</sub>                    |                      |                     | 1.5 | 5.4       | 8.7 | ns   |

| t <sub>PLH</sub>                    | OEAB                 | В                   | 1.6 | 4.4       | 6.2 |      |

| t <sub>PHL</sub>                    |                      |                     | 1.3 | 6.1       | 9.8 | ns   |

| t <sub>RISE</sub>                   | Transition time, B o | utputs (20% to 80%) |     | 2.6       |     | ns   |

| t <sub>FALL</sub>                   | Transition time, B o | utputs (20% to 80%) |     | 2.6       |     |      |

| t <sub>PLH</sub>                    | В                    | А                   | 2.0 | 5.6       | 8.2 | ns   |

| t <sub>PHL</sub>                    |                      |                     | 1.4 | 5.0       | 7.2 | 115  |

| t <sub>PLH</sub>                    | LEBA                 | А                   | 2.1 | 4.2       | 6.3 | ns   |

| t <sub>PHL</sub>                    |                      |                     | 1.9 | 3.3       | 5.0 | 115  |

| t <sub>PLH</sub>                    | CLKBA                | А                   | 2.3 | 4.4       | 6.8 | ne   |

| PHL                                 |                      |                     | 2.2 | 3.5       | 5.2 | ns   |

| PZH, tPZL                           | OEBA                 | А                   | 1.5 | 5.0       | 6.2 | no   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> |                      |                     | 1.9 | 3.9       | 7.9 | ns   |

Note 10: All typical values are at  $V_{CC} = 3.3 V$ ,  $V_{CCQ} = 5.0 V$ , and  $T_A = 25 ^{\circ} C$ .

## **Test Circuits and Timing Waveforms**

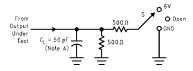

#### **Test Circuit for A Outputs**

C<sub>L</sub> includes probes and jig capacitance.

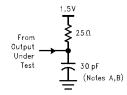

#### **Test Circuit for B Outputs**

${

m C_L}$  includes probes and jig capacitance. For B Port outputs,  ${

m C_L}=30$  pF is used for worst case edge rate.

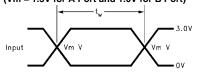

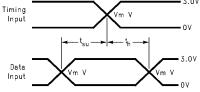

Voltage Waveforms Pulse Duration (Vm = 1.5V for A Port and 1.0V for B Port)

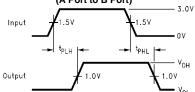

#### Voltage Waveforms Propagation Delay Times (A Port to B Port)

## Voltage Waveforms Setup and Hold Times (Vm = 1.5V for A Port and 1.0V for B Port) 3.0V

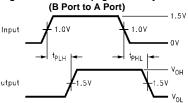

### Voltage Waveforms Propagation Delay Times

All input pulses have the following characteristics: frequency = 10 MHz,  $t_r = t_f = 2$  ns,  $Z_O = 50\Omega$ . The outputs are measured one at a time with one transition per measurement.

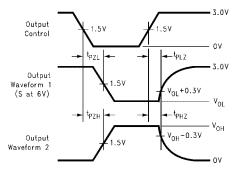

#### Voltage Waveforms Enable and Disable Times (A Port)

Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control. All input pulses have the following characteristics: frequency = 10 MHz,  $t_r = t_f = 2$  ns,  $Z_O = 50\Omega$ . The outputs are measured one at a time with one transition per measurement.

www.fairchildsemi.com

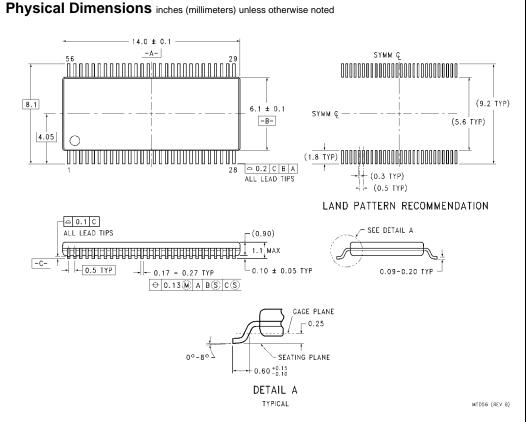

56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide Package Number MTD56

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

www.fairchildsemi.com