May 1988 Revised January 2004

# 74F382 4-Bit Arithmetic Logic Unit

#### **General Description**

The 74F382 performs three arithmetic and three logic operations on two 4-bit words, A and B. Two additional Select input codes force the Function outputs LOW or HIGH. An Overflow output is provided for convenience in twos complement arithmetic. A Carry output is provided for ripple expansion. For high-speed expansion using a Carry Lookahead Generator, refer to the 74F381 data sheet.

#### **Features**

- Performs six arithmetic and logic functions

- Selectable LOW (clear) and HIGH (preset) functions

- LOW input loading minimizes drive requirements

- Carry output for ripple expansion

- Overflow output for twos complement arithmetic

### **Ordering Code:**

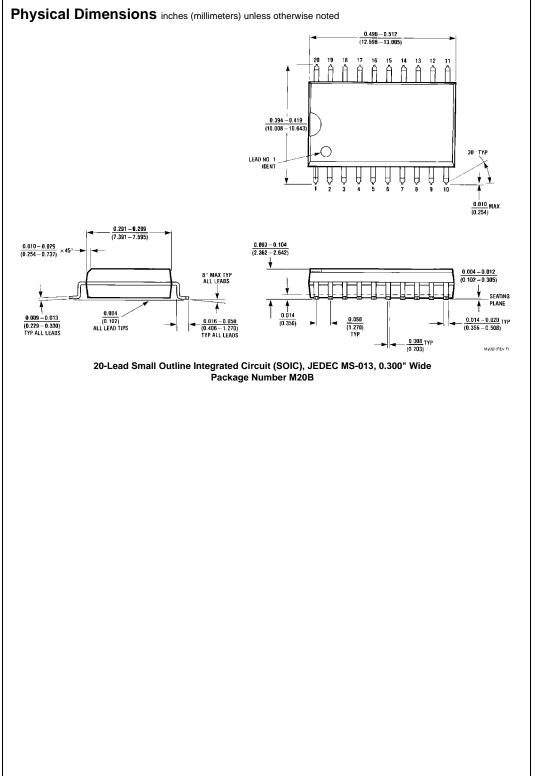

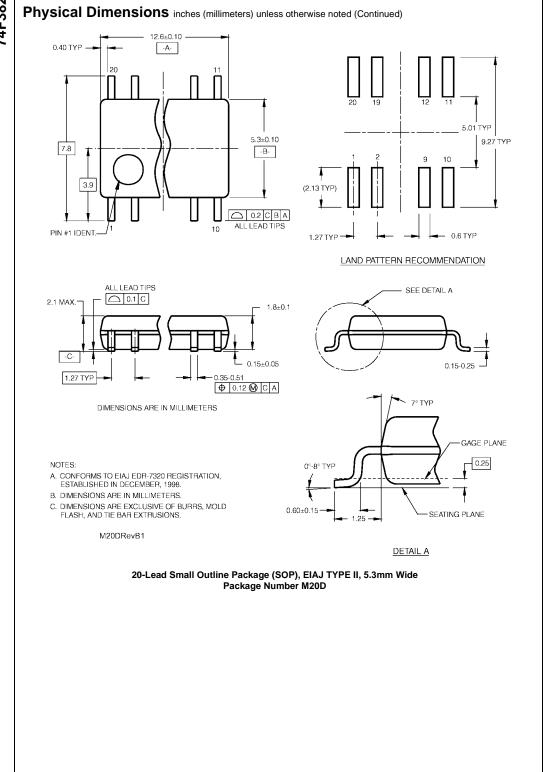

| Order Number | Package Number | Package Description                                                        |

|--------------|----------------|----------------------------------------------------------------------------|

| 74F382SC     | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide |

| 74F382SJ     | M20D           | 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide              |

| 74F382PC     | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide     |

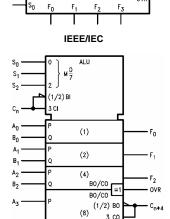

# **Logic Symbols**

#### **Connection Diagram**

© 2004 Fairchild Semiconductor Corporation

DS009529

## **Unit Loading/Fan Out**

| Pin Names                      | Description            | U.L.     | Input I <sub>IH</sub> /I <sub>IL</sub>  |

|--------------------------------|------------------------|----------|-----------------------------------------|

| Fill Names                     | Description            | HIGH/LOW | Output I <sub>OH</sub> /I <sub>OL</sub> |

| A <sub>0</sub> -A <sub>3</sub> | A Operand Inputs       | 1.0/4.0  | 20 μA/–2.4 mA                           |

| B <sub>0</sub> -B <sub>3</sub> | B Operand Inputs       | 1.0/4.0  | 20 μA/–2.4 mA                           |

| S <sub>0</sub> -S <sub>2</sub> | Function Select Inputs | 1.0/1.0  | 20 μA/-0.6 mA                           |

| C <sub>n</sub>                 | Carry Input            | 1.0/5.0  | 20 μA/-3.0 mA                           |

| C <sub>n + 4</sub>             | Carry Output           | 50/33.3  | −1 mA/20 mA                             |

| OVR                            | Overflow Output        | 50/33.3  | −1 mA/20 mA                             |

| F <sub>0</sub> -F <sub>3</sub> | Function Outputs       | 50/33.3  | −1 mA/20 mA                             |

#### **Functional Description**

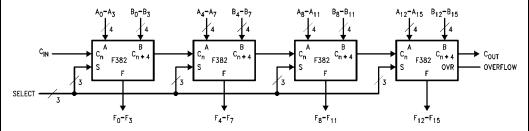

Signals applied to the Select inputs  $S_0 \!\!\!\!- \!\!\! S_2$  determine the mode of operation, as indicated in the Function Select Table. An extensive listing of input and output levels is shown in the Truth Table. The circuit performs the arithmetic functions for either active HIGH or active LOW operands, with output levels in the same convention. In the Subtract operating modes, it is necessary to force a carry (HIGH for active HIGH operands, LOW for active LOW operands) into the  $C_n$  input of the least significant package. Ripple expansion is illustrated in Figure 2. The overflow output OVR is the Exclusive-OR of  $C_{n+3}$  and  $C_{n+4}$ ; a HIGH signal on OVR indicates overflow in twos complement operation. Typical delays for Figure 2 are given in Figure 1.

#### **Function Select Table**

|                | Select         |                | Operation |  |  |  |

|----------------|----------------|----------------|-----------|--|--|--|

| S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> |           |  |  |  |

| L              | L              | L              | Clear     |  |  |  |

| Н              | L              | L              | B Minus A |  |  |  |

| L              | Н              | L              | A Minus B |  |  |  |

| Н              | Н              | L              | A Plus B  |  |  |  |

| L              | L              | Н              | A ⊕ B     |  |  |  |

| Н              | L              | Н              | A + B     |  |  |  |

| L              | Н              | Н              | AB        |  |  |  |

| Н              | Н              | Н              | Preset    |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

| Bath Carrier                                         | Toward  | Output                 |

|------------------------------------------------------|---------|------------------------|

| Path Segment                                         | F       | C <sub>n+4</sub> , OVR |

| A <sub>1</sub> or B <sub>1</sub> to C <sub>n+4</sub> | 6.5 ns  | 6.5 ns                 |

| C <sub>n</sub> to C <sub>n+4</sub>                   | 6.3 ns  | 6.3 ns                 |

| C <sub>n</sub> to C <sub>n+4</sub>                   | 6.3 ns  | 6.3 ns                 |

| C <sub>n</sub> to F                                  | 8.1 ns  | _                      |

| $C_n$ to $C_{n+4}$ , OVR                             | _       | 8.0 ns                 |

| Total Delay                                          | 27.2 ns | 27.1 ns                |

FIGURE 1. 16-Bit Delay Tabulation

FIGURE 2. 16-Bit Ripply Carry ALU Expansion

## **Truth Table**

|           | Inputs         |                |                |                |                |                |                | Outputs        |                |                |     |                    |  |  |  |

|-----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|--------------------|--|--|--|

| Function  | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | C <sub>n</sub> | A <sub>n</sub> | B <sub>n</sub> | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | OVR | C <sub>n + 4</sub> |  |  |  |

| CLEAR     | L              | L              | L              | L              | Χ              | Х              | L              | L              | L              | L              | Н   | Н                  |  |  |  |

|           |                |                |                | Н              | Х              | Χ              | L              | L              | L              | L              | Н   | Η                  |  |  |  |

| B MINUS A | Н              | L              | L              | L              | L              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | L              | Н              | L              | Н              | Н              | Н              | L   | Н                  |  |  |  |

|           |                |                |                | L              | Н              | L              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Н              | L              | L              | L              | L              | L              | L              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | L              | Н              | Н              | Н              | Н              | Н              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | Н              | L              | Н              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | L              | L              | L              | L              | L   | H                  |  |  |  |

| A MINUS B | L              | Н              | L              | L              | L              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | L              | Н              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | L              | L              | Н              | Н              | Н              | L   | Н                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Н              | L              | L              | L              | L              | L              | L              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | L              | Н              | Н              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Н              | Н              | L              | Н              | Н              | Н              | Н              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | L              | L              | L              | L              | L   | Н                  |  |  |  |

| A PLUS B  | Н              | Н              | L              | L              | L              | L              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | L              | L              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | L              | Н              | Н              | Н              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | L              | L              | Н              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Н              | L              | Н              | L              | L              | L              | L              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | Н              | L              | L              | L              | L              | L              | L   | Н                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | Η              | Н              | Н              | Н              | L   | Η                  |  |  |  |

| A ⊕ B     | L              | L              | Н              | Х              | L              | L              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Х              | L              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Х              | Н              | Н              | L              | L              | L              | L              | Н   | Н                  |  |  |  |

|           |                |                |                | Н              | Н              | L              | Н              | Н              | Н              | Н              | Н   | Н                  |  |  |  |

| A + B     | Н              | L              | Н              | Х              | L              | L              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Х              | L              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Х              | Н              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н   | Н                  |  |  |  |

| AB        | L              | Н              | Н              | Х              | L              | L              | L              | L              | L              | L              | Н   | Н                  |  |  |  |

|           |                |                |                | Х              | L              | Н              | L              | L              | L              | L              | L   | L                  |  |  |  |

|           |                |                |                | Х              | Н              | L              | L              | L              | L              | L              | Н   | Н                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н   | Н                  |  |  |  |

| PRESET    | Н              | Н              | Н              | Х              | L              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Х              | L              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Х              | Н              | L              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | L              | Н              | Н              | Н              | Н              | Н              | Н              | L   | L                  |  |  |  |

|           |                |                |                | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н   | Н                  |  |  |  |

### **Absolute Maximum Ratings**(Note 1)

-65°C to +150°C

Storage Temperature Ambient Temperature under Bias -55°C to +125°C

Junction Temperature under Bias -55°C to +150°C V<sub>CC</sub> Pin Potential to Ground Pin -0.5V to +7.0V Input Voltage (Note 2) -0.5V to +7.0V

Input Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

Standard Output -0.5V to  $V_{CC}$

3-STATE Output -0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated I<sub>OL</sub> (mA)

### **Recommended Operating Conditions**

0°C to +70°C Free Air Ambient Temperature Supply Voltage +4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

#### DC Electrical Characteristics over Operating Temperature Range unless otherwise specified

| Symbol           | Parameter                    |                    | Min  | Тур | Max  | Units | v <sub>cc</sub> | Conditions                             |  |

|------------------|------------------------------|--------------------|------|-----|------|-------|-----------------|----------------------------------------|--|

| V <sub>IH</sub>  | Input HIGH Voltage           |                    | 2.0  |     |      | V     |                 | Recognized as a HIGH Signal            |  |

| V <sub>IL</sub>  | Input LOW Voltage            |                    |      |     | 0.8  | V     |                 | Recognized as a LOW Signal             |  |

| V <sub>CD</sub>  | Input Clamp Diode Voltage    |                    |      |     | -1.2 | V     | Min             | $I_{IN} = -18 \text{ mA}$              |  |

| V <sub>OH</sub>  | Output HIGH 10               | 0% V <sub>CC</sub> | 2.5  |     |      | V     | Min             | I <sub>OH</sub> = -1 mA                |  |

|                  | Voltage                      | 5% V <sub>CC</sub> | 2.7  |     |      | •     | IVIIII          | $I_{OH} = -1 \text{ mA}$               |  |

| V <sub>OL</sub>  | Output LOW                   | 00/ \/             |      |     | 0.5  | V     | Min             | I <sub>OI</sub> = 20 mA                |  |

|                  | Voltage                      | 0% V <sub>CC</sub> |      |     | 0.5  | V     | IVIIII          | IOL = 20 IIIA                          |  |

| I <sub>IH</sub>  | Input HIGH                   |                    |      |     | 5.0  | μА    | Max             | V <sub>IN</sub> = 2.7V                 |  |

|                  | Current                      |                    |      |     | 3.0  | μΛ    | IVIAX           | VIN - 2.7 V                            |  |

| I <sub>BVI</sub> | Input HIGH Current           |                    |      |     | 7.0  |       | Max             | V <sub>IN</sub> = 7.0V                 |  |

|                  | Breakdown Test               |                    |      |     | 7.0  | μА    | IVIAX           | VIN - 1.0 V                            |  |

| I <sub>CEX</sub> | Output HIGH                  |                    |      |     | 50   | μА    | Max             | $V_{OUT} = V_{CC}$                     |  |

|                  | Leakage Current              |                    |      |     | 30   | μΛ    | IVIAX           | VOUT - VCC                             |  |

| V <sub>ID</sub>  | Input Leakage                |                    | 4.75 |     |      | V     | 0.0             | $I_{ID} = 1.9  \mu A$                  |  |

|                  | Test                         |                    | 4.73 |     |      | v     | 0.0             | All Other Pins Grounded                |  |

| I <sub>OD</sub>  | Output Leakage               |                    |      |     | 3.75 | μА    | 0.0             | V <sub>IOD</sub> = 150 mV              |  |

|                  | Circuit Current              |                    |      |     | 3.73 | μΛ    | 0.0             | All Other Pins Grounded                |  |

| I <sub>IL</sub>  | Input LOW Current            |                    |      |     | -0.6 |       |                 | $V_{IN} = 0.5V (S_0 - S_2)$            |  |

|                  |                              |                    |      |     | -2.4 | mA    | Max             | $V_{IN} = 0.5V (A_0 - A_3, B_0 - B_3)$ |  |

|                  |                              |                    |      |     | -3.0 |       |                 | $V_{IN} = 0.5V (C_n)$                  |  |

| Ios              | Output Short-Circuit Current |                    | -60  |     | -150 | mA    | Max             | V <sub>OUT</sub> = 0V                  |  |

| I <sub>CC</sub>  | Power Supply Current         |                    |      | 54  | 81   | mA    | Max             |                                        |  |

## **AC Electrical Characteristics**

| Symbol           | Parameter                                              |     | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V<br>$C_L = 50 \text{ pF}$ | ′    | $T_A = 0$ °C to +70°C $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |      | Units |  |

|------------------|--------------------------------------------------------|-----|--------------------------------------------------------------|------|--------------------------------------------------------------|------|-------|--|

|                  |                                                        | Min | Тур                                                          | Max  | Min                                                          | Max  |       |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 3.0 | 8.1                                                          | 12.0 | 3.0                                                          | 13.0 | ns    |  |

| $t_{PHL}$        | C <sub>n</sub> to F <sub>i</sub>                       | 2.5 | 5.7                                                          | 8.0  | 2.5                                                          | 9.0  | 115   |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 4.0 | 10.4                                                         | 15.0 | 3.5                                                          | 17.0 | ns    |  |

| $t_{PHL}$        | Any A or B to Any F                                    | 3.0 | 8.2                                                          | 11.0 | 2.5                                                          | 12.0 | ris   |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 6.5 | 11.0                                                         | 20.5 | 5.5                                                          | 21.5 |       |  |

| t <sub>PHL</sub> | S <sub>i</sub> to F <sub>i</sub>                       | 4.0 | 8.2                                                          | 15.0 | 4.0                                                          | 17.5 | ns    |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 3.5 | 6.0                                                          | 8.5  | 3.5                                                          | 11.0 | ns    |  |

| t <sub>PHL</sub> | A <sub>i</sub> or B <sub>i</sub> to C <sub>n</sub> + 4 | 3.5 | 6.5                                                          | 9.0  | 3.5                                                          | 10.5 | 115   |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 7.0 | 12.5                                                         | 16.5 | 7.0                                                          | 17.5 | ns    |  |

| t <sub>PHL</sub> | S <sub>i</sub> to OVR or C <sub>n+4</sub>              | 5.0 | 9.0                                                          | 12.0 | 5.0                                                          | 14.5 | 115   |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 2.5 | 5.6                                                          | 8.0  | 2.0                                                          | 9.0  |       |  |

| t <sub>PHL</sub> | $C_n$ to $C_{n+4}$                                     | 3.5 | 6.3                                                          | 9.0  | 2.0                                                          | 10.0 | ns    |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 3.5 | 8.0                                                          | 11.0 | 3.5                                                          | 13.0 |       |  |

| t <sub>PHL</sub> | C <sub>n</sub> to OVR                                  | 2.5 | 7.1                                                          | 10.0 | 2.5                                                          | 11.0 | ns    |  |

| t <sub>PLH</sub> | Propagation Delay                                      | 7.0 | 11.5                                                         | 15.5 | 7.0                                                          | 16.5 | ns    |  |

| t <sub>PHL</sub> | A <sub>i</sub> or B <sub>i</sub> to OVR                | 3.0 | 8.0                                                          | 10.5 | 3.0                                                          | 11.5 | 115   |  |

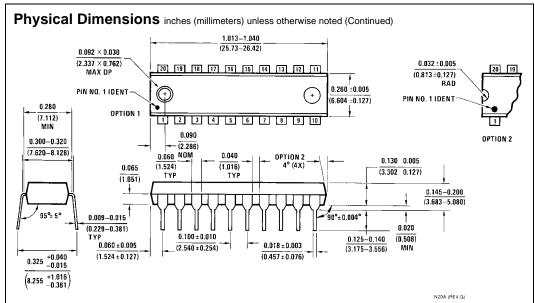

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N20A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

9

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com