# **1W Constant Filterless Class-D Audio Amplifier**

NCP2830 is a cost effective mono audio power amplifier designed for portable communication device applications such as mobile phones. Due to its integrated charge pump structure, this part is capable of delivering 1 W of continuous average power to an 8.0  $\Omega$ Bridge Tied Load no matter the voltage provided by a lithium/Ion battery.

NCP2830 is a preferred solution for long playback audio with minimum space required.

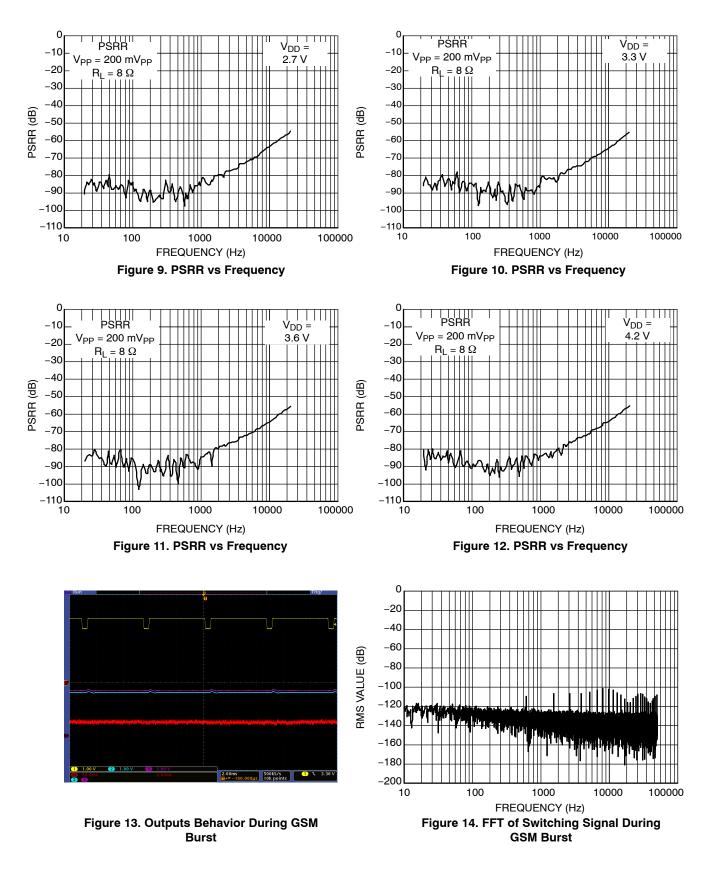

Added to a fast start-up time of 200 µs and a -88dB PSRR, the NCP2830 audio power amplifier is specifically designed to provide high quality and level output power from low supply voltage, requiring very few external components.

# Features

- 1 W to 8  $\Omega$  load for V<sub>DD</sub> from 2.7 V up to 5.5 V

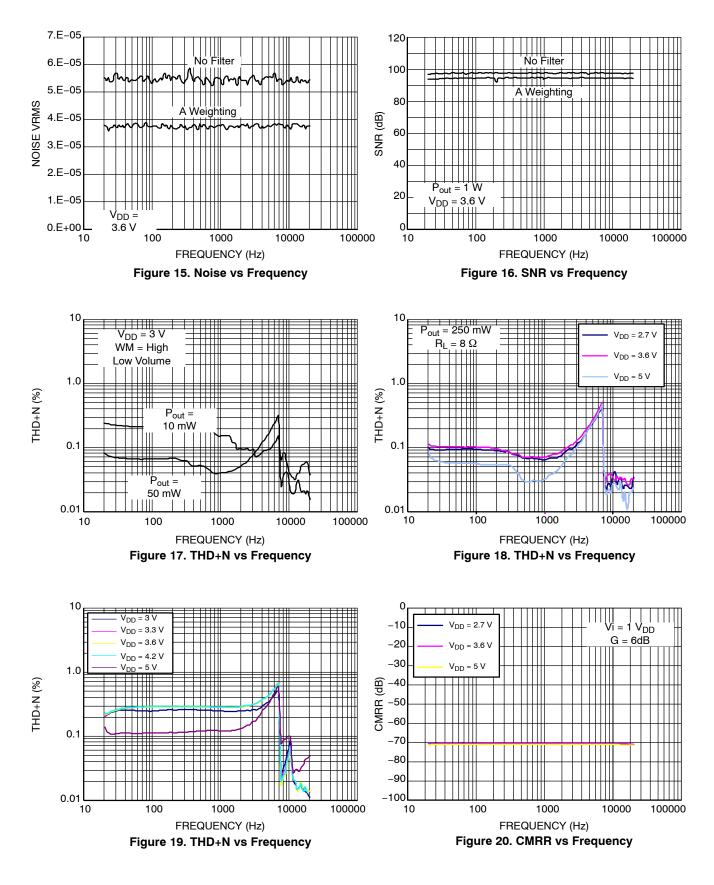

- High quality audio (THD+N = 0.04%)

- Low noise: SNR up to 100 dB

- Very Fast Turn On Time: 200 μs

- Overall system efficiency optimization: up to 89%

- Superior PSRR (-88 dB): Direct Connection to Battery

- Very Low Quiescent Current 7 mA

- Optimized PWM Output Stage: Filterless Capability

- Selectable gain of 2 V/V or 4 V/V

- Fully Differential Capability:

- Thin QFN 3x3 mm, 20 pins

- This Device uses Halogen-Free Molding Compound

- This is a Pb-Free Device

# **Typical Applications**

- Cellular Phones and Digital Cameras

- Personal Digital Assistant and Portable Media Player

- Audio Accessories

- GPS

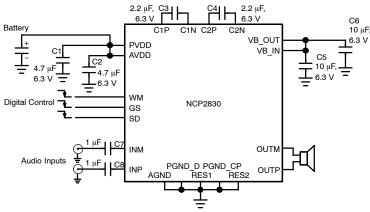

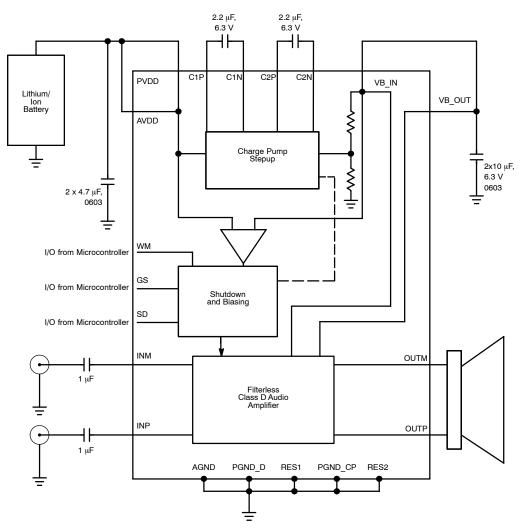

Figure 1. Typical Application Circuit

# **ON Semiconductor®**

http://onsemi.com

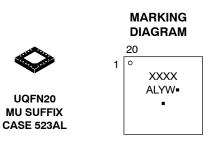

- = Work Week

- = Pb-Free Package

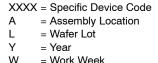

(TOP VIEW) 20-Pin 3 x 3 x 0.50 mm QFN Exposed pad must be soldered to PCB Ground Plane

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 14 of this data sheet.

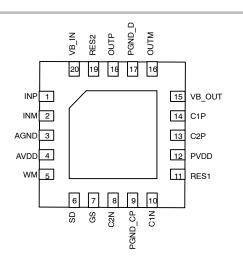

Figure 2. Simplified Block Diagram

# **PIN FUNCTION DESCRIPTION**

| Pin   | Pin Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20    | VB_IN        | I    | This pin must be externally connection in a star configuration with Pin n°15. The C <sub>out</sub> filtering (10 $\mu$ F/6.3 V/0603) capacitor must be connected as close as possible to the connection point.                                                                                                                                                                  |

| 3     | AGND         | Р    | Ground. These pins must be connected separately to the dedicated Ground plane with a minimum of track length. Thus, a star connection is required.                                                                                                                                                                                                                              |

| 9     | PGND_C<br>P  | Р    | Ground. These pins must be connected separately to the dedicated Ground plane with a minimum of track length. Thus, a star connection is required.                                                                                                                                                                                                                              |

| 17    | PGND_D       | Ρ    | Ground. These pins must be connected separately to the dedicated Ground plane with a minimum of track length. Thus, a star connection is required.                                                                                                                                                                                                                              |

| 4, 12 | AVDD<br>PVDD | Р    | These pins are dedicated to the signal connection for the battery input. They must be connected to the power source (ie lithium/lon battery) in a star mode. It must be decoupled by a low ESR ceramic capacitor. (4.7 $\mu$ F/6.3 V/0603). The use of a 4 or more layers board is advised. In that case, a dedicated plane for this battery voltage is mandatory.              |

| 1     | INP          | I    | Positive audio input of the fully differential filterless Class D Audio Amplifier                                                                                                                                                                                                                                                                                               |

| 2     | INM          | I    | Negative audio input of the fully differential filterless Class D Audio Amplifier                                                                                                                                                                                                                                                                                               |

| 16    | OUTM         | 0    | Negative audio output of the fully differential filterless Class D Audio Amplifier                                                                                                                                                                                                                                                                                              |

| 18    | OUTP         | 0    | Positive audio output of the fully differential filterless Class D Audio Amplifier                                                                                                                                                                                                                                                                                              |

| 5     | WM           | I    | Wire Mode pin: When a low level is applied to this pin, the device operates in Normal mode ( $V_B = 5 V$ typ.). In case of a high level, it switches to a Wire Mode ( $V_B = V_{DD}$ )                                                                                                                                                                                          |

| 6     | SD           | I    | Shutdown input. The device enters in shutdown mode when a low level is applied on this pin.                                                                                                                                                                                                                                                                                     |

| 7     | GS           | I    | Gain Select Input. When a low level is applied to this pin, an internal 2 V/V gain is setup. In case of a high level, it switches to an internal 4 V/V gain.                                                                                                                                                                                                                    |

| 8     | C2N          | Р    | One side of the external charge pump capacitor is connected to this pin, associated with C2P. Using a low ESR ceramic capacitor is recommended to optimize charge pump efficiency (2.2 $\mu$ F/6.3 V/0603 recommended).                                                                                                                                                         |

| 10    | C1N          | Р    | One side of the external charge pump capacitor is connected to this pin, associated with C1P. Using a low ESR ceramic capacitor is recommended to optimize charge pump efficiency (2.2µF/6.3V/0603 recommended).                                                                                                                                                                |

| 13    | C2P          | Р    | One side of the external charge pump capacitor is connected to this pin, associated with C2N. Using a low ESR ceramic capacitor is recommended to optimize charge pump efficiency (2.2 $\mu$ F/6.3 V/0603 recommended).                                                                                                                                                         |

| 14    | C1P          | Р    | One side of the external charge pump capacitor is connected to this pin, associated with C1N. Using a low ESR ceramic capacitor is recommended to optimize charge pump efficiency (2.2 $\mu$ F/6.3 V/0603 recommended).                                                                                                                                                         |

| 15    | VB_OUT       | 0    | This pin must be externally connection in a star configuration with Pin n°20. The C <sub>out</sub> filtering (10 $\mu$ F/6.3 V/0603) capacitor must be connected as close as possible to the connection point. This V <sub>B</sub> input is dedicated to supply the internal power stages. Thus, it must be connected to C <sub>out</sub> with the lowest impedance connection. |

| 11    | RES1         | I    | Reserved for production. Must be connected to GND plane in final application                                                                                                                                                                                                                                                                                                    |

| 19    | RES2         | I    | Reserved for production. Must be connected to GND plane in final application                                                                                                                                                                                                                                                                                                    |

# **MAXIMUM RATINGS**

| Rating                                         |                                                           | Symbol          | Value                              | Unit    |

|------------------------------------------------|-----------------------------------------------------------|-----------------|------------------------------------|---------|

| AVDD, PVDD Pins: Power Supply Voltage (Note 2) | )                                                         | V <sub>IN</sub> | – 0.3 to + 7.0                     | V       |

| Digital Input WM; SD; GS Pin:                  | Digital Input WM; SD; GS Pin: Input Voltage Input Current |                 | –0.3 to V <sub>DD</sub> + 0.3<br>1 | V<br>mA |

| Human Body Model (HBM) ESD Rating are (Note 3) | )                                                         | ESD HBM         | 2000                               | V       |

| Machine Model (MM) ESD Rating are (Note 3)     |                                                           | ESD MM          | 200                                | V       |

| Latch up Current Maximum Rating                | I <sub>LU</sub>                                           | (Note 4)        | mA                                 |         |

| QFN 3 x 3 mm Package (Note 7) Thermal Resista  | $R_{	extsf{	heta}JC}$                                     | 29 (Note 7)     | °C/W                               |         |

| Operating Ambient Temperature Range            | T <sub>A</sub>                                            | -40 to +85      | °C                                 |         |

| Operating Junction Temperature Range           | TJ                                                        | -40 to +125     | °C                                 |         |

| Maximum Junction Temperature (Note 6)          | T <sub>JMAX</sub>                                         | +150            | °C                                 |         |

| Storage Temperature Range                      | T <sub>STG</sub>                                          | -65 to +150     | °C                                 |         |

| Moisture Sensitivity (Note 5)                  |                                                           | MSL             | Level 1                            |         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = 25 °C.

According to JEDEC standard JESD22–A108B.

3. This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114 for all pins.

Machine Model (MM) ±200 V per JEDEC standard: JESD22-A115 for all pins.

Latch up Current Maximum Rating:

$\pm$  100 mA for all pins, except digital pins per JEDEC standard: JESD78 class II.

± 10mA for Digital Pins per JEDEC standard: JESD78 class II 5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

6. The thermal shutdown set to 150°C (typical) avoids irreversible damage on the device due to power dissipation.

7. The R<sub>0CA</sub> is dependent of the PCB heat dissipation. The maximum power dissipation (PD) is dependent by the min input voltage, the max output current and external components selected.

$$\mathsf{R}_{\theta \mathsf{CA}} \frac{\mathsf{125} - \mathsf{T}_{\mathsf{A}}}{\mathsf{P}_{\mathsf{D}}} - \mathsf{R}_{\theta \mathsf{JC}}$$

| ELECTRICAL CHARACTERISTICS Min and Max Limits apply for T <sub>A</sub> between -40°C to +85°C and T <sub>J</sub> up to + 125°C for V <sub>IN</sub> |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| between 2.5 V to 5.5 V (Unless otherwise noted). Typical values are referenced to $T_A = + 25^{\circ}C$ and $V_{IN} = 3.6$ V (Note 8)              |  |

| Symbol           | Parameter                       | Conditions                                                             | Min | Тур  | Max | Unit |

|------------------|---------------------------------|------------------------------------------------------------------------|-----|------|-----|------|

| GLOBAL SY        | /STEM                           |                                                                        |     |      |     |      |

| V <sub>DD</sub>  | Operating System Voltage        |                                                                        | 2.7 | -    | 5.5 | V    |

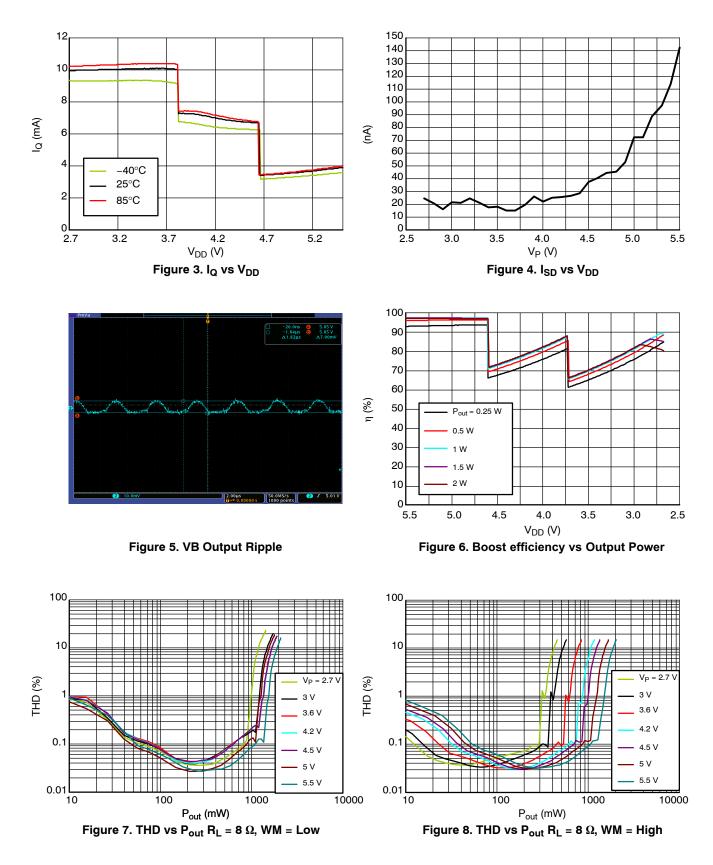

| I <sub>SD</sub>  | Shutdown Current                | $V_{SD}$ = low, $V_{GS}$ = Low, $V_{WM}$ = Low                         | -   | 0.01 | -   | μA   |

| I <sub>SD</sub>  | Shutdown Current                | $V_{SD}$ = low, $V_{GS}$ = Low, $V_{WM}$ = Low, $V_p$ = 5.5 V (Note 9) | -   | -    | 1.5 | μA   |

| l <sub>Q</sub>   | Quiescent Current               | 2X Mode, No load                                                       | -   | 9.5  | 11  | mA   |

| l <sub>Q</sub>   | Quiescent Current               | 1.5X Mode, No load                                                     | -   | 7    | 8   | mA   |

| l <sub>Q</sub>   | Quiescent Current               | Wire Mode, No load                                                     | -   | 3    | 4.5 | mA   |

| R <sub>SD</sub>  | Resistance from SD to GND       |                                                                        | -   | 350  | -   | kΩ   |

| R <sub>WM</sub>  | Resistance from WM to GND       |                                                                        | -   | 350  | -   | kΩ   |

| R <sub>GS</sub>  | Resistance from GS to GND       |                                                                        | -   | 350  | -   | kΩ   |

| V <sub>IH</sub>  | Digital Pins High Voltage       |                                                                        | 1.2 | -    | -   | V    |

| V <sub>IL</sub>  | Digital Pins Low Voltage        |                                                                        | -   | -    | 0.4 | V    |

| BOOST SEC        | CTION                           |                                                                        |     |      |     |      |

| F <sub>SW1</sub> | Charge Pump Switching Frequency |                                                                        | 550 | 650  | 750 | kHz  |

| F <sub>SW1</sub>       | Charge Pump Switching Frequency                     |                                                                                                  | 550  | 650  | 750  | kHz |

|------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|-----|

| V <sub>B</sub>         | Output Regulated Voltage                            | No Load, V <sub>INM</sub> =V <sub>INP</sub> =0, V <sub>WM</sub> = Low, 2X<br>Mode                | 4.75 | 5    | 5.25 | V   |

| V <sub>B</sub>         | Output Regulated Voltage                            | No Load, $V_{INM} = V_{INP} = 0$ , $V_{WM} = Low$ , 1.5X Mode                                    | 4.75 | 5    | 5.25 | V   |

| V <sub>B-Ripple</sub>  | Output Voltage Ripple                               | No Load, V <sub>INM</sub> = V <sub>INP</sub> = 0, V <sub>WM</sub> = Low,<br>2X Mode or 1.5X Mode | -    | 7    | -    | mV  |

| T <sub>Precharge</sub> | Precharge time                                      | $C5 = C6 = 10 \ \mu F$                                                                           | -    | 1.6  | -    | ms  |

| V <sub>TR1</sub>       | Transition Voltage between 2X Mode<br>and 1.5X Mode |                                                                                                  | -    | 3.8  | -    | V   |

| V <sub>TR2</sub>       | Transition Voltage between 2X Mode<br>and Wire Mode |                                                                                                  | -    | 4.65 | -    | V   |

### **CLASS D SECTION**

| F <sub>SW2</sub>   | Class D Switching frequency       |                                                            | 275  | 325  | 375  | kHz               |

|--------------------|-----------------------------------|------------------------------------------------------------|------|------|------|-------------------|

| R <sub>INL</sub>   | Audio Input resistance            | V <sub>GS</sub> = Low (Note 10)                            | -    | 15   | -    | kΩ                |

| R <sub>INH</sub>   | Audio Input resistance            | V <sub>GS</sub> = High (Note 10)                           | -    | 7.5  | -    | kΩ                |

| Z <sub>SD</sub>    | Shutdown impedance                | V <sub>SD</sub> = Low                                      | -    | 20   | -    | kΩ                |

| G <sub>HI</sub>    | Gain High                         | $V_{GS}$ = High, RL = 8 $\Omega$                           | 1.85 | 2    | 2.15 | V/V               |

| G <sub>LO</sub>    | Gain Low                          | $V_{GS}$ = Low, RL = 8 $\Omega$                            | 3.7  | 4    | 4.3  | V/V               |

| V <sub>OS</sub>    | Output Offset Voltage             | $V_{INM} = V_{INP} = 0$                                    | -    | 1    | -    | mV                |

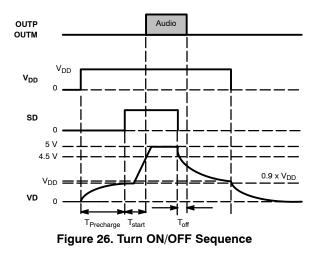

| T <sub>start</sub> | Turn ON time                      | $V_B = V_{DD}, V_{SD} = High$                              | -    | 200  | -    | μs                |

| T <sub>OFF</sub>   | Turn Off time                     |                                                            | -    | 1    | -    | μs                |

| V <sub>N</sub>     | Output Noise Voltage              | No Filter                                                  | -    | 56   | -    | $\mu V_{RMS}$     |

| V <sub>N</sub>     | Output Noise Voltage              | A–Weighting filter                                         | -    | 37   | -    | μV <sub>RMS</sub> |

| THD+N              | Total harmonic distortion + Noise | $P_{out}$ = 0.25 W, f = 1 kHz, R <sub>L</sub> = 8 $\Omega$ | -    | 0.04 | -    | %                 |

| THD+N              | Total harmonic distortion + Noise | $P_{out}$ = 1 W, f = 1 kHz, $R_L$ = 8 $\Omega$             | -    | 0.2  | -    | %                 |

8. Performances guaranteed over the indicated operating temperature range by design and/or characterization, production tested at T<sub>J</sub> = T<sub>A</sub> = 25°C.

9. The maximum value is measured at 85°C

10. Guaranteed by design

| ELECTRICAL CHARACTERISTICS Min and Max Limits apply for T <sub>A</sub> between -40°C to +85°C and T <sub>J</sub> up to + 125°C for V <sub>IN</sub> |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| between 2.5 V to 5.5 V (Unless otherwise noted). Typical values are referenced to $T_A = + 25^{\circ}C$ and $V_{IN} = 3.6$ V (Note 8)              |

| Symbol           | Parameter                    | Conditions                                                                                | Min | Тур        | Max | Unit |

|------------------|------------------------------|-------------------------------------------------------------------------------------------|-----|------------|-----|------|

| CLASS D SI       | CLASS D SECTION              |                                                                                           |     |            |     |      |

| PSRR             | Power Supply Rejection Ratio | $V_{in}$ = AC Grounded, f = 217 Hz, $V_{WM}$ = $V_{GS}$ = Low, $V_{RIPPLE}$ = 200 mV_{PP} | -   | -88        | -   | dB   |

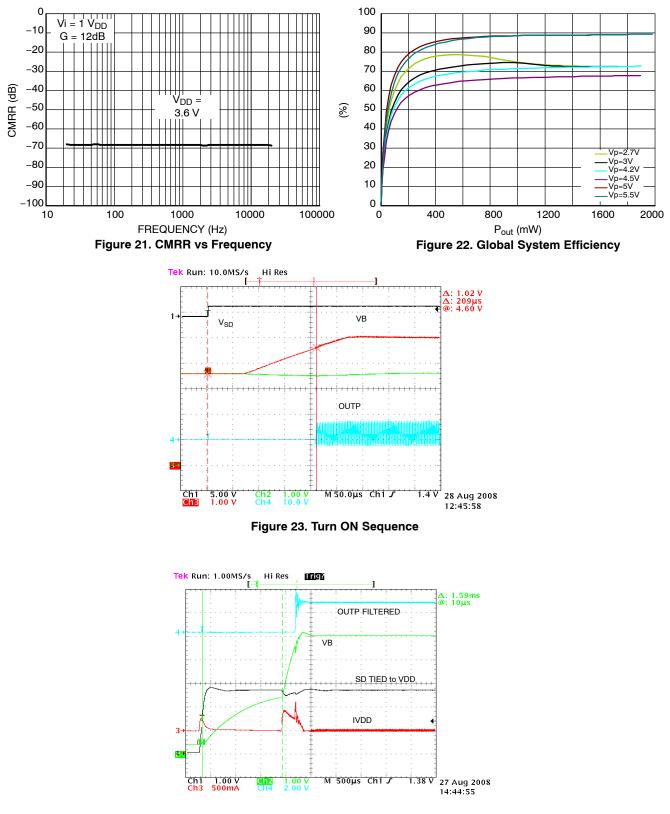

| CMRR             | Common mode rejection ratio  | Vic = 1 V <sub>PP</sub><br>f = 1 kHz<br>V <sub>GS</sub> = Low<br>V <sub>GS</sub> = High   |     | -70<br>-60 |     | dB   |

| η                | Efficiency                   | $R_L = 8 Ω$<br>$V_{DD} = 5 V; P_{out} = 1 W$<br>$V_{DD} = 2.7 V; P_{out} = 0.5 W$         |     | 89<br>80   | -   | %    |

| P <sub>OUT</sub> | Output Power                 | THD+N < 10%, f = 1 kHz, $V_{WM}$ = Low                                                    | 1   | 1.2        | -   | W    |

8. Performances guaranteed over the indicated operating temperature range by design and/or characterization, production tested at T<sub>J</sub> = T<sub>A</sub> = 25°C.

9. The maximum value is measured at 85°C

10. Guaranteed by design

Figure 24. Turn ON Sequence

# **DETAIL OPERATING DESCRIPTION**

Figure 25. Functional Block Diagram

#### **Detailed Descriptions**

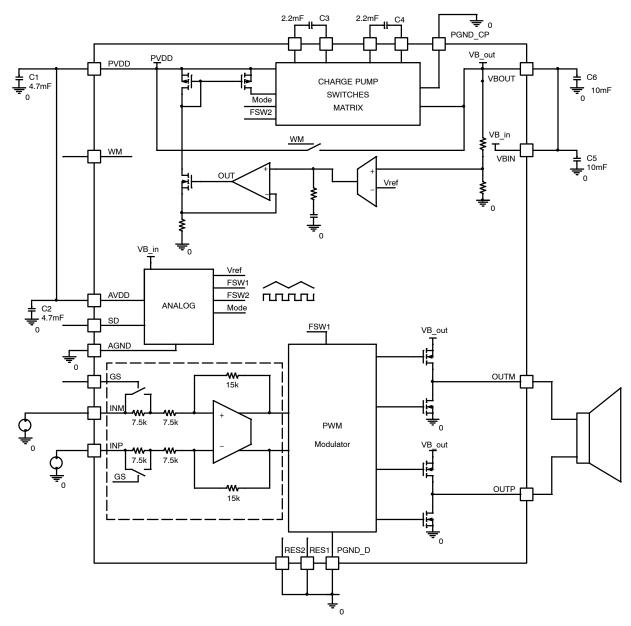

The NCP2830 consists of two parts: a DC–DC converter and a mono class D amplifier. These two parts are strongly matched in order to obtain the best operation of the global system.

#### **DC-DC CONVERTER**

The DC–DC converter is based on a charge pump technique. The switching frequency is synchronized with the class D amplifier ( $F_{SW2} = 2 \times F_{SW1}$ ) in order to avoid mixing frequency. The regulation is based on a voltage regulation. The output voltage is permanently monitored through a resistor ladder and compared to an internal

reference. An error amplifier and a voltage to current conversion allow injecting in the Capacitors C3 and C4 the necessary current to maintain 5 V in output. This linear regulation reduces the output voltage ripple (7 mV typ) and allows a noise free operation.

# Turn ON/OFF sequence

The turn ON and turn OFF sequence has been adapted to an audio applications environment. When the battery voltage is connected to the  $V_{DD}$  pins, the output capacitance is precharged to the  $V_{DD}$  voltage. When VSD is High, the charge pump is activated and the output voltage rises up to 5 V. Internally, the class D amplifier starts to operate when  $V_B$  equals 4.5 V.

When VSD is low, the charge pump is deactivated and the  $V_B$  voltage is maintain to the  $V_{DD}$  value. During this shutdown mode, it is not possible to sink current through the VB pin. Figure 26 depicts the turn ON/OFF sequence.

In order to maximize the global efficiency, the system permanently monitors the battery voltage and changes its operating mode:

- When V<sub>DD</sub> is less than 3.8 V (typ) the system operates in **2X mode.**

- Between 3.8 V and 4.65 V the system operates in 1.5X mode.

- If V<sub>DD</sub> is greater than 4.65 V the system switches automatically to **Wire Mode** operation (V<sub>B</sub> = V<sub>DD</sub>)

#### WM pin

This external pin allows controlling the activation of the boost whatever the battery voltage is. For example, if no power is required, there is no need to boost the supply voltage of the class D amplifier. In that case, disabling the boost by a high logic on WM pin, allows supplying directly the class D by the battery voltage ( $V_B = V_{DD}$ ) and optimizing the efficiency.

### **CLASS D AMPLIFIER**

The NCP2830 is based on a mono class D audio amplifier. This structure is composed by a preamplifier stage, a PWM stage and a H–Bridge stage.

#### Gain selection

The preamplifier stage consists in applying a gain to the input signal selectable by a dedicated digital pin GS.

The gain setting is given by the following truth table:

| GS | Gain Av V/V | Input Impedance k $\Omega$ |

|----|-------------|----------------------------|

| 0  | 2           | 15                         |

| 1  | 4           | 7.5                        |

#### 30 kHz Built-in Low Pass Filter

This filter allows directly connecting a DAC or a CODEC to the NCP2830 input without risk of output noise increase due to a mixing frequency with the DAC/CODEC output frequency. Consequently, the best operation with DACs or CODECs is guarantee without need of additional external components.

### Input Capacitors Cin

Due to its fully differential architecture the NCP2830 does not require input capacitors if the differential source is biased from 0.5 V to  $V_{DD}$  – 0.8 V. However, it is possible to use input capacitors when the differential source is not biased or in single ended configuration. In this case it is necessary to take into account the corner frequency which can influence the low frequency response of the NCP2830. The following equation will help to choose the adequate input capacitors.

$$f_{\rm C} = \frac{1}{2\pi \cdot {\rm Z}_{\rm in} \cdot {\rm C}_{\rm in}} \qquad ({\rm eq.~1})$$

With  $Z_{in}$  the input impedance of the NCP2830.

### **Overcurrent Protection**

This protection allows detecting an over current in the H–Bridge. When the current is higher than 2 A the H–Bridge is put in high impedance. When the short circuit is removed or the current is lower, the NCP2830 go back to normal operation. This protection allows avoiding overcurrent due to a bad assembly (Output shorted together, to  $V_B$  or to ground).

#### **DESIGN PROCEDURE**

#### **Components Selection**

Use very low ESR ceramic capacitors (X5R/X7R) will help to reduce the output resistance of the charge pump and thus improve the system efficiency.

### Input Capacitor (C1 and C2)

NCP2830 is aimed to be connected on the battery line. For such a device, it is mandatory to get as low ripple as possible so as to avoid conducted emission on the battery line. As stated above, the noise generated by turn-on and turn-off transients is optimized by a controlled switching speed.

Placing two 4.7  $\mu$ F/6.3 V (0603 size) input capacitors as close as possible to PDD and AVDD pin will also help to avoid any disturbance for other sensitive parts also connected on the battery line.

# Flying Capacitors (C3 and C4)

As stated above, the value of these capacitors has a direct impact on the load regulation and output resistance of the charge pump. The converter must provide a regulated DC voltage with a sine wave AC current, the frequency of which is twice the audio signal frequency. Selecting a  $2.2 \,\mu$ F/6.3 V (0603 size) will help regarding the load regulation and the device's ability to provide sufficient current drive.

# **Output Capacitors (C5 and C6)**

The value and ESR of this capacitor are directly linked to the ripple of the regulated output voltage. As the charge pump must provide up to 450 mA to the internal audio amplifier, two 10  $\mu$ F/6.3 V capacitors (0603 size) should allow the converter to give its maximum output power capability.

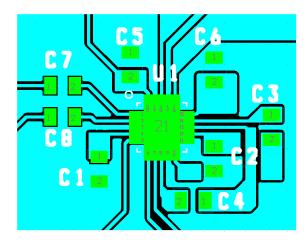

### Layout Recommendations

As all switching devices, special care must be observed in routing power supplies and ground.

$V_{\rm DD}$  pins must be decoupled by C1 and C2 placed as close as possible to the NCP2830 in order to reduce parasitic inductance.

GND pins must be connected to a ground plane. In order to reduce parasitic elements, it is better to connect all the ground pins to the same Ground plane.

Figure 27. Recommended PCB Layout

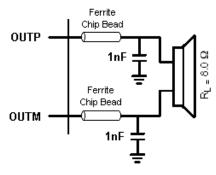

### **Optional Output Filters**

If the traces between the amplifier and the speaker are short, there's no need for an output filter.

In case of applications where short output traces are not possible, it is necessary to protect the application as much as possible from EMI pollution. The use of small 0603 Chip Ferrite beads is a good alternative.

Figure 28. Optional EMI Filter

### **Thermal Considerations**

For thermal dissipation, it is recommended to connect the exposed pad of the NCP2830 to a plan connected to the ground as depicted Figure 27.

# Demo Board Available:

The NCP2830EVB/D evaluation board that configures the device in typical application.

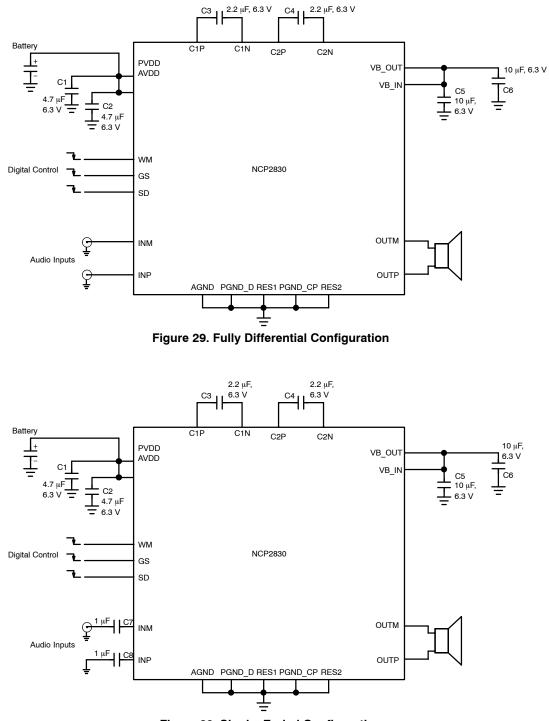

### **TYPICAL APPLICATION**

Figure 30. Single-Ended Configuration

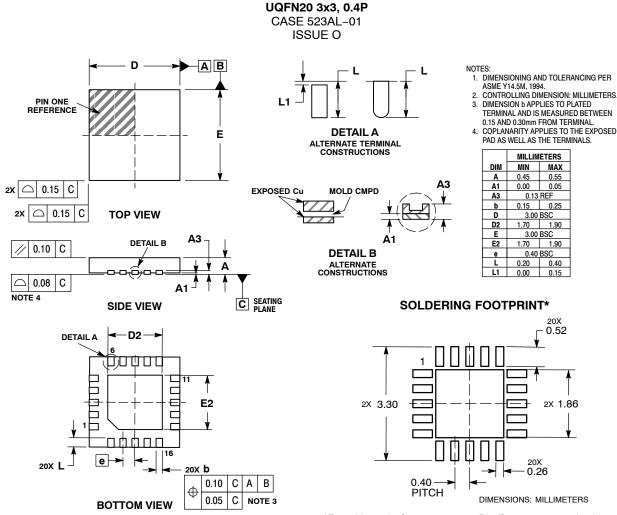

### **ORDERING INFORMATION**

| Device       | Package                    | Shipping <sup>†</sup> |

|--------------|----------------------------|-----------------------|

| NCP2830MUTXG | UQFN20 3x3 mm<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is a Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicatio le copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative