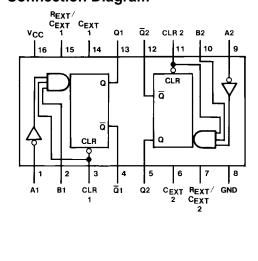

DM74LS123 Dual Retriggerable One-Shot with Clear and Complementary Outputs

# FAIRCHILD

SEMICONDUCTOR

# DM74LS123 Dual Retriggerable One-Shot with Clear and Complementary Outputs

#### **General Description**

The DM74LS123 is a dual retriggerable monostable multivibrator capable of generating output pulses from a few nano-seconds to extremely long duration up to 100% duty cycle. Each device has three inputs permitting the choice of either leading edge or trailing edge triggering. Pin (A) is an active-LOW transition trigger input and pin (B) is an active-HIGH transition trigger input. The clear (CLR) input terminates the output pulse at a predetermined time independent of the timing components. The clear input also serves as a trigger input when it is pulsed with a low level pulse transition ( $\neg$ r). To obtain the best trouble free operation from this device please read the operating rules as well as the Fairchild Semiconductor one-shot application notes carefully and observe recommendations.

#### Features

- DC triggered from active-HIGH transition or active-LOW transition inputs

- Retriggerable to 100% duty cycle

- $\blacksquare$  Compensated for  $V_{CC}$  and temperature variations

- Triggerable from CLEAR input

- DTL, TTL compatible

- Input clamp diodes

## **Ordering Code:**

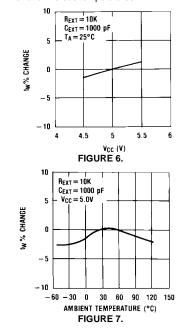

| Order Number           | Package Number            | Package Description                                                         |

|------------------------|---------------------------|-----------------------------------------------------------------------------|

| DM74LS123M             | M16A                      | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

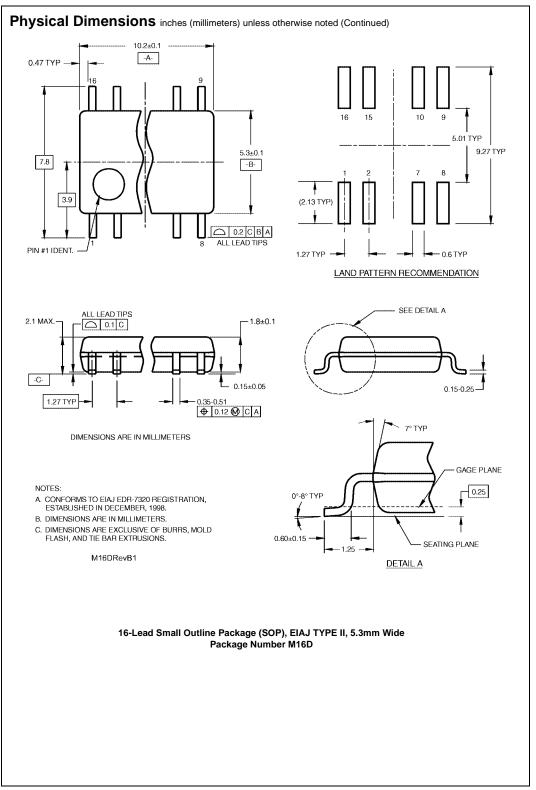

| DM74LS123SJ            | M16D                      | 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

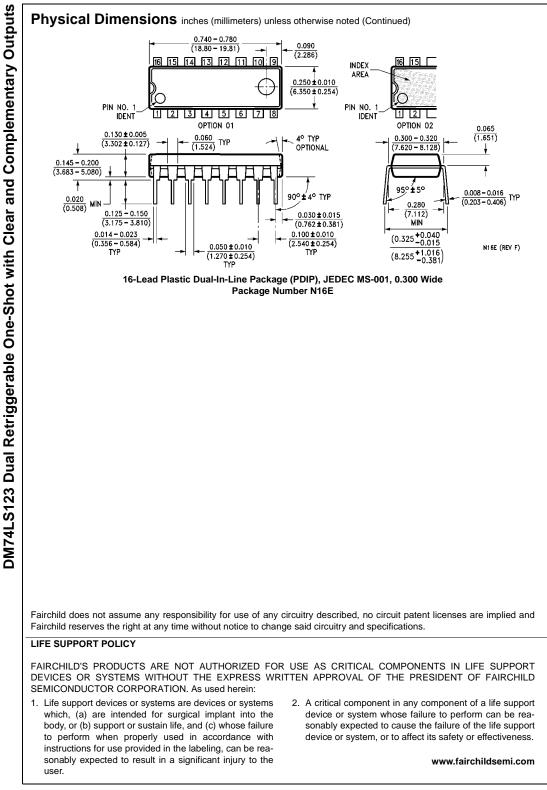

| DM74LS123N             | N16E                      | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

| Devices also available | in Tape and Reel. Specify | by appending the suffix letter "X" to the ordering code.                    |

## Function Table

| Inputs     |              |   | Outputs |     |  |

|------------|--------------|---|---------|-----|--|

| CLEAR      | Α            | В | Q       | Q   |  |

| L          | Х            | Х | L       | Н   |  |

| х          | Н            | Х | L       | н   |  |

| х          | Х            | L | L       | н   |  |

| Н          | L            | ↑ | л       | ъ   |  |

| н          | $\downarrow$ | н | л       | ъ   |  |

| $\uparrow$ | L            | н |         | 7.5 |  |

H = HIGH Logic Leve

- L = LOW Logic Level X = Can Be Either LOW or HIGH

- $\uparrow$  = Positive Going Transition

- $\downarrow$  = Negative Going Transition

- \_\_\_ = A Positive Pulse \_\_ = A Negative Pulse

- L = A Negative Fulse

© 2000 Fairchild Semiconductor Corporation DS006386

#### **Functional Description**

The basic output pulse width is determined by selection of an external resistor ( $R_X$ ) and capacitor ( $C_X$ ). Once triggered, the basic pulse width may be extended by retriggering the gated active-LOW transition or active-HIGH transition inputs or be reduced by use of the active-LOW or

**Operating Rules**

- 1. An external resistor ( $R_X$ ) and an external capacitor ( $C_X$ ) are required for proper operation. The value of  $C_X$  may vary from 0 to any necessary value. For small time constants high-grade mica, glass, polypropylene, polycarbonate, or polystyrene material capacitors may be used. For large time constants use tantalum or special aluminum capacitors. If the timing capacitors have leakages approaching 100 nA or if stray capacitance from either terminal to ground is greater than 50 pF the timing equations may not represent the pulse width the device generates.

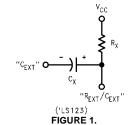

- 2. When an electrolytic capacitor is used for C<sub>X</sub> a switching diode is often required for standard TTL one-shots to prevent high inverse leakage current. This switching diode is not needed for the DM74LS123 one-shot and should not be used. In general the use of the switching diode is not recommended with retriggerable operation. Furthermore, if a polarized timing capacitor is used on the DM74LS123 the negative terminal of the capacitor should be connected to the "C<sub>EXT</sub>" pin of the device (Figure 1).

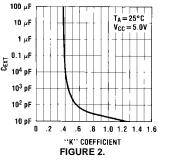

3. For C\_X >> 1000 pF the output pulse width (t\_W) is defined as follows:

$t_W = KR_X \ C_X$  where [R\_X is in kΩ]

- [C<sub>X</sub> is in pF]

- [t<sub>W</sub> is in ns]

- K ≈ 0.37

- The multiplicative factor K is plotted as a function of C<sub>X</sub> below for design considerations:

CLEAR input. Retriggering to 100% duty cycle is possible by application of an input pulse train whose cycle time is shorter than the output cycle time such that a continuous "HIGH" logic state is maintained at the "Q" output.

5. For  $C_X < 1000 \text{ pF}$  see Figure 3 for  $t_W$  vs.  $C_X$  family curves with  $R_X$  as a parameter:

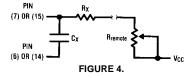

To obtain variable pulse widths by remote trimming, the following circuit is recommended:

- "R<sub>remote</sub>" should be as close to the device pin as possible.

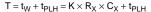

- 7. The retriggerable pulse width is calculated as shown below:

The retriggered pulse width is equal to the pulse width plus a delay time period (Figure 5).

#### **Operating Rules** (Continued)

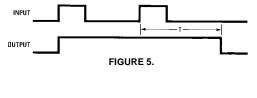

Output pulse width variation versus V<sub>CC</sub> and temperatures: Figure 6 depicts the relationship between pulse width variation versus V<sub>CC</sub>, and Figure 7 depicts pulse width variation versus temperatures.

- 9. Under any operating condition  $C_X$  and  $R_X$  must be kept as close to the one-shot device pins as possible to minimize stray capacitance, to reduce noise pick-up, and to reduce I-R and Ldi/dt voltage developed along their connecting paths. If the lead length from  $C_X$  to pins (6) and (7) or pins (14) and (15) is greater than 3 cm, for example, the output pulse width might be quite different from values predicted from the appropriate equations. A non-inductive and low capacitive path is necessary to ensure complete discharge of  $C_X$  in each cycle of its operation so that the output pulse width will be accurate.

- The C<sub>EXT</sub> pins of this device are internally connected to the internal ground. For optimum system performance they should be hard wired to the system's return ground plane.

- 11. V<sub>CC</sub> and ground wiring should conform to good high-frequency standards and practices so that switching transients on the V<sub>CC</sub> and ground return leads do not cause interaction between one-shots. A 0.01  $\mu$ F to 0.10  $\mu$ F bypass capacitor (disk ceramic or monolithic type) from V<sub>CC</sub> to ground is necessary on each device. Furthermore, the bypass capacitor should be located as close to the V<sub>CC</sub>-pin as space permits.

Note: For further detailed device characteristics and output performance please refer to the Fairchild Semiconductor one-shot application note AN-372. DM74LS123

## Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 7V              |

| Operating Free Air Temperature Range | 0°C to +70°C    |

| Storage Temperature                  | -65°C to +150°C |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol            | Parameter                                                         |           | Min  | Nom            | Max  | Units |

|-------------------|-------------------------------------------------------------------|-----------|------|----------------|------|-------|

| V <sub>CC</sub>   | Supply Voltage                                                    |           | 4.75 | 5              | 5.25 | V     |

| V <sub>IH</sub>   | HIGH Level Input Voltage                                          |           | 2    |                |      | V     |

| V <sub>IL</sub>   | LOW Level Input Voltage                                           |           |      |                | 0.8  | V     |

| I <sub>OH</sub>   | HIGH Level Output Current                                         |           |      |                | -0.4 | mA    |

| I <sub>OL</sub>   | LOW Level Output Current                                          |           |      |                | 8    | mA    |

| t <sub>W</sub>    | Pulse Width A c                                                   | or B HIGH | 40   |                |      |       |

|                   | (Note 2) A c                                                      | or B LOW  | 40   |                |      | ns    |

|                   | Cle                                                               | ear LOW   | 40   |                |      |       |

| R <sub>EXT</sub>  | External Timing Resistor                                          |           | 5    |                | 260  | kΩ    |

| C <sub>EXT</sub>  | External Timing Capacitance                                       |           |      | No Restriction |      | μF    |

| C <sub>WIRE</sub> | Wiring Capacitance at R <sub>EXT</sub> /C <sub>EXT</sub> Terminal |           |      |                | 50   | pF    |

| T <sub>A</sub>    | Free Air Operating Temperature                                    |           | 0    |                | 70   | °C    |

Note 2:  $T_A$  = 25°C and  $V_{CC}$  = 5V.

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol Parameter |                                   | Conditions                                     | Min | Typ<br>(Note 3) | Max  | Units |  |

|------------------|-----------------------------------|------------------------------------------------|-----|-----------------|------|-------|--|

| VI               | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 mA$                   |     |                 | -1.5 | V     |  |

| V <sub>OH</sub>  | HIGH Level                        | $V_{CC} = Min, I_{OH} = Max$                   | 2.7 | 3.4             |      | V     |  |

|                  | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$                   | 2.7 | 0.4             |      | v     |  |

| V <sub>OL</sub>  | LOW Level                         | $V_{CC} = Min, I_{OL} = Max$                   |     | 0.35            | 0.5  |       |  |

|                  | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$                   |     | 0.55            | 0.5  | V     |  |

|                  |                                   | $I_{OL} = 4 \text{ mA}, V_{CC} = Min$          |     | 0.25            | 0.4  |       |  |

| I <sub>I</sub>   | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 7V$                       |     |                 | 0.1  | mA    |  |

| Ι <sub>ΙΗ</sub>  | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.7V$                     |     |                 | 20   | μΑ    |  |

| Ι <sub>ΙL</sub>  | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.4V$                     |     |                 | -0.4 | mA    |  |

| I <sub>OS</sub>  | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 4)                 | -20 |                 | -100 | mA    |  |

| I <sub>CC</sub>  | Supply Current                    | V <sub>CC</sub> = Max (Note 5)(Note 6)(Note 7) |     | 12              | 20   | mA    |  |

Note 3: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 4: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 5: Quiescent I<sub>CC</sub> is measured (after clearing) with 2.4V applied to all clear and A inputs, B inputs grounded, all outputs OPEN,  $C_{EXT} = 0.02 \ \mu$ F, and  $R_{EXT} = 25 \ k\Omega$ .

Note 6: I<sub>CC</sub> is measured in the triggered state with 2.4V applied to all clear and B inputs, A inputs grounded, all outputs OPEN,  $C_{EXT} = 0.02 \ \mu$ F, and  $R_{EXT} = 25 \ k\Omega$ .

Note 7: With all outputs OPEN and 4.5V applied to all data and clear inputs, I<sub>CC</sub> is measured after a momentary ground, then 4.5V is applied to the clock.

## Switching Characteristics

|                      | Parameters                                         | From (Input)<br>To (Output) | $R_L = 2 k\Omega$                                                                                                                                                                                                   |     |                                                                                                                                                                        |     |       |

|----------------------|----------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| Symbol               |                                                    |                             | $\label{eq:CL} \begin{split} \textbf{C}_{\textbf{L}} &= \textbf{15}\textbf{pF} \\ \textbf{C}_{\textbf{EXT}} &= \textbf{0} \ \textbf{pF}, \ \textbf{R}_{\textbf{EXT}} &= \textbf{5} \ \textbf{k} \Omega \end{split}$ |     | $\label{eq:CL} \begin{split} \textbf{C}_{L} = \textbf{15pF} \\ \textbf{C}_{EXT} = \textbf{1000 pF},  \textbf{R}_{EXT} = \textbf{10 k} \boldsymbol{\Omega} \end{split}$ |     | Units |

| Gymbol               |                                                    |                             |                                                                                                                                                                                                                     |     |                                                                                                                                                                        |     |       |

|                      |                                                    |                             | Min                                                                                                                                                                                                                 | Max | Min                                                                                                                                                                    | Max |       |

| t <sub>PLH</sub>     | Propagation Delay Time<br>LOW-to-HIGH Level Output | A to Q                      |                                                                                                                                                                                                                     | 33  |                                                                                                                                                                        |     | ns    |

| t <sub>PLH</sub>     | Propagation Delay Time<br>LOW-to-HIGH Level Output | B to Q                      |                                                                                                                                                                                                                     | 44  |                                                                                                                                                                        |     | ns    |

| t <sub>PHL</sub>     | Propagation Delay Time<br>HIGH-to-LOW Level Output | A to Q                      |                                                                                                                                                                                                                     | 45  |                                                                                                                                                                        |     | ns    |

| t <sub>PHL</sub>     | Propagation Delay Time<br>HIGH-to-LOW Level Output | B to Q                      |                                                                                                                                                                                                                     | 56  |                                                                                                                                                                        |     | ns    |

| t <sub>PLH</sub>     | Propagation Delay Time<br>LOW-to-HIGH Level Output | Clear to $\overline{Q}$     |                                                                                                                                                                                                                     | 45  |                                                                                                                                                                        |     | ns    |

| t <sub>PHL</sub>     | Propagation Delay Time<br>HIGH-to-LOW Level Output | Clear to Q                  |                                                                                                                                                                                                                     | 27  |                                                                                                                                                                        |     | ns    |

| t <sub>WQ(Min)</sub> | Minimum Width of Pulse<br>at Output Q              | A or B to Q                 |                                                                                                                                                                                                                     | 200 |                                                                                                                                                                        |     | ns    |

| t <sub>W(out)</sub>  | Output Pulse Width                                 | A or B to Q                 | 1                                                                                                                                                                                                                   |     | 4                                                                                                                                                                      | 5   | μs    |

# DM74LS123

www.fairchildsemi.com

6

DM74LS123

www.fairchildsemi.com

8