#### Features

- 3.3V operation for low power consumption and easy integration into low-voltage systems

- High-speed, low-power, first-in first-out (FIFO) memories

- 16K × 9 (CY7C4261V)

- 32K × 9 (CY7C4271V)

- 64K × 9 (CY7C4281V)

- 128K × 9 (CY7C4291V)

- 0.35-micron CMOS for optimum speed/power

- High-speed 100-MHz operation (10-ns read/write cycle times)

- Low power

$-I_{CC} = 25 \text{ mA}$

- I<sub>SB</sub> = 4 mA

- Fully asynchronous and simultaneous read and write operation

- Empty, Full, and programmable Almost Empty and Almost Full status flags

- Output Enable (OE) pin

- Independent read and write enable pins

- Supports free-running 50% duty cycle clock inputs

- Width- Expansion capability

- 32-pin PLCC

- Pin-compatible density upgrade to CY7C42X1V family

- Pin-compatible 3.3V solutions for CY7C4261/71/81/91

#### **Functional Description**

The CY7C4261/71/81/91V are high-speed, low-power FIFO memories with clocked read and write interfaces. All are nine bits wide. The CY7C4261/71/81/91V are pin-compatible to the CY7C42x1V Synchronous FIFO family. Programmable features include Almost Full/Almost Empty flags. These FIFOs provide solutions for a wide variety of data buffering needs, including high-speed data acquisition, multiprocessor interfaces, and communications buffering.

These FIFOs have 9-bit input and output ports that are controlled by separate clock and enable signals. The input port is controlled by <u>a free</u>-running clock (WCLK) and two write-enable pins (WEN1, WEN2/LD).

When WEN1 is LOW and WEN2/LD is HIGH, data is written into the FIFO on the rising edge of the WCLK signal. While WEN1 and WEN2/LD are held active, data is continually written into the FIFO on each WCLK cycle. The output port is controlled in a similar manner by <u>a free-running</u> read clock (RCLK) and two read enable pins (REN1, REN2). In <u>addition</u>, the CY7C4261/71/81/91V has an output enable pin (OE). The read (RCLK) and write (WCLK) clocks may be tied together for single-clock operation or the two clocks may be run independently for asynchronous read/write applications. Clock frequencies up to 100 MHz are achievable. Depth expansion is possible using one enable input for system control, while the other enable is controlled by expansion logic to direct the flow of data.

Cypress Semiconductor Corporation Document #: 38-06013 Rev. \*A 3901 North First Street

San Jose, CA 95134 • 408-943-2600 Revised August 25, 2003

# **Selection Guide**

|                               |            | 7C4261/71/81/91V-10 | 7C4261/71/81/91V-15 | 7C4261/71/81/91V-25 | Unit |

|-------------------------------|------------|---------------------|---------------------|---------------------|------|

| Maximum Frequency             |            | 100                 | 66.7                | 40                  | MHz  |

| Maximum Access Time           | ;          | 8                   | 10                  | 15                  | ns   |

| Minimum Cycle Time            |            | 10                  | 15                  | 25                  | ns   |

| Minimum Data or Enable Set-up |            | 3.5                 | 4                   | 6                   | ns   |

| Minimum Data or Enable Hold   |            | 0                   | 0                   | 1                   | ns   |

| Maximum Flag Delay            |            | 8                   | 10                  | 15                  | ns   |

| Active Power Supply           | Commercial | 25                  | 25                  | 25                  | mA   |

| Current (I <sub>CC1</sub> )   | Industrial |                     | 30                  |                     |      |

|                               |            |                     |                     |                     |      |

|         | CY7C4261V   | CY7C4271V   | CY7C4281V   | CY7C4291V   |

|---------|-------------|-------------|-------------|-------------|

| Density | 16K x 9     | 32K x 9     | 64K x 9     | 128K x 9    |

| Package | 32-pin PLCC | 32-pin PLCC | 32-pin PLCC | 32-pin PLCC |

#### **Pin Definitions**

| Signal Name      | Description                  | I/O | Description                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0-8</sub> | Data Inputs                  | Ι   | Data Inputs for 9-bit bus.                                                                                                                                                                                                                                                                                                               |

| Q <sub>0-8</sub> | Data Outputs                 | 0   | Data Outputs for 9-bit bus.                                                                                                                                                                                                                                                                                                              |

| WEN1             | Write Enable 1               | Ι   | The only write enable when device is configured to have programmable flags.<br>Data is written on a LOW-to-HIGH transition of WCLK when WEN1 is asserted and FF is<br>HIGH. If the FIFO is configured to have two write enables, data is written on a LOW-to-HIGH<br>transition of WCLK when WEN1 is LOW and WEN2/LD and FF are HIGH.    |

| WEN2/LD          | Write Enable 2               | Ι   | If HIGH at reset, this pin operates as a second write enable. If LOW at reset, this                                                                                                                                                                                                                                                      |

| Dual Mode Pin    | Load                         |     | pin operates as a control to write or read the programmable flag offsets. WEN1 must be LOW and WEN2 must be HIGH to write data into the FIFO. Data will not be writt <u>en</u> into the FIFO if the FF is LOW. If the FIFO is configured to have programmable flags, WEN2/LD is held LOW to write or read the programmable flag offsets. |

| REN1, REN2       | Read Enable<br>Inputs        | I   | Enables the device for Read operation. Both REN1 and REN2 must be asserted to allow a read operation.                                                                                                                                                                                                                                    |

| WCLK             | Write Clock                  | I   | The rising edge clocks data into the FIFO when WEN1 is LOW and WEN2/LD is HIGH and the FIFO is not Full. When LD is asserted, WCLK writes data into the programmable flag-offset register.                                                                                                                                               |

| RCLK             | Read Clock                   | Ι   | The rising edge clocks data out of the FIFO when REN1 and REN2 are LOW and the FIFO are not Empty. When WEN2/LD is LOW, RCLK reads data out of the programmable flag-offset register.                                                                                                                                                    |

| EF               | Empty Flag                   | 0   | When EF is LOW, the FIFO is empty. EF is synchronized to RCLK.                                                                                                                                                                                                                                                                           |

| FF               | Full Flag                    | 0   | When FF is LOW, the FIFO is full. FF is synchronized to WCLK.                                                                                                                                                                                                                                                                            |

| PAE              | Programmable<br>Almost Empty | 0   | When PAE is LOW, the FIFO is almost empty based on the almost empty offset value programmed into the FIFO. PAE is synchronized to RCLK.                                                                                                                                                                                                  |

| PAF              | Programmable<br>Almost Full  | 0   | When PAF is LOW, the FIFO is almost full based on the almost full offset value programmed into the FIFO. PAF is synchronized to WCLK.                                                                                                                                                                                                    |

| RS               | Reset                        | I   | <b>Resets device to empty condition</b> . A reset is required before an initial read or write operation after power-up.                                                                                                                                                                                                                  |

| OE               | Output Enable                | Ι   | When $\overline{OE}$ is LOW, the FIFO's data outputs drive the bus to which they are connected. If $\overline{OE}$ is HIGH, the FIFO's outputs are in High Z (high-impedance) state.                                                                                                                                                     |

### Functional Description (continued)

The CY7C4261/71/81/91V provides four status pins: Empty, Full, Programmable Almost Empty, and Programmable Almost Full. The Almost Empty/Almost Full flags are programmable to single word granularity. The programmable flags default to Empty +7 and Full -7.

The flags are synchronous, i.e., they change state relative to either the read clock (RCLK) or the write clock (WCLK). When entering or exiting the Empty and Almost Empty states, the flags are updated exclusively by the RCLK. The flags denoting Almost Full, and Full states are updated exclusively by WCLK. The synchronous flag architecture guarantees that the flags maintain their status for at least one cycle

All configurations are fabricated using an advanced 0.35m CMOS technology. Input ESD protection is greater than 2001V, and latch-up is prevented by the use of guard rings.

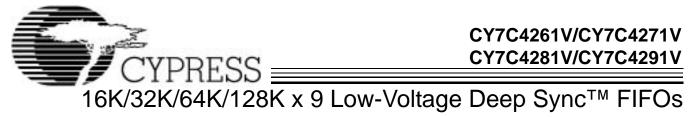

#### Architecture

The CY7C4261/71/81/91V consists of an array of 16K, 32K, 64K, or 128K words of nine bits each (implemented by a dual-port array of SRAM cells), <u>a read pointer</u>, <u>a write pointer</u>, <u>control signals (RCLK, WCLK, REN1, REN2, WEN1, WEN2, RS)</u>, and flags (EF, PAE, PAF, FF).

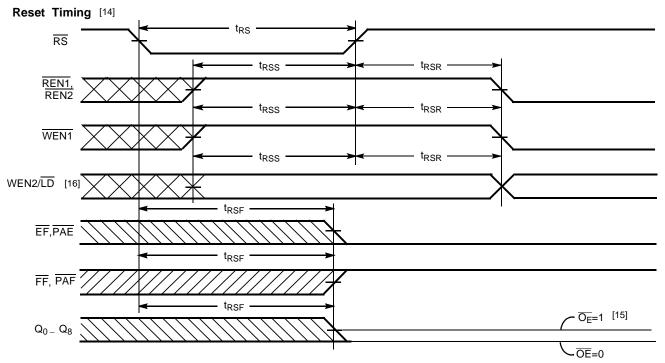

#### **Resetting the FIFO**

Upon power-up, the FIFO must be reset with a Reset ( $\overline{RS}$ ) cycle. This causes the FIFO to enter the Empty condition signified by  $\overline{EF}$  being LOW. All data outputs ( $Q_{0-8}$ ) go LOW t<sub>RSF</sub> after the rising edge of  $\overline{RS}$ . In order for the FIFO to reset to its default state, the user must not read or write while  $\overline{RS}$  is LOW. All flags are guaranteed to be valid t<sub>RSF</sub> after  $\overline{RS}$  is taken LOW.

### **FIFO Operation**

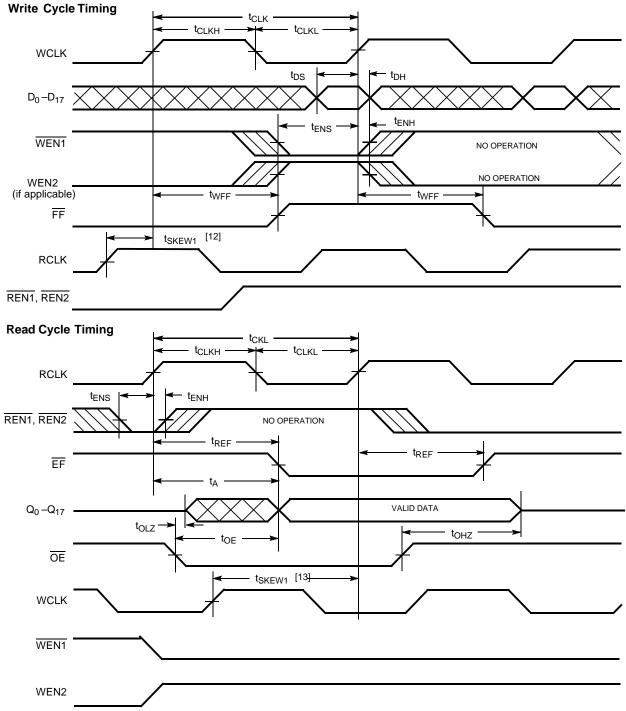

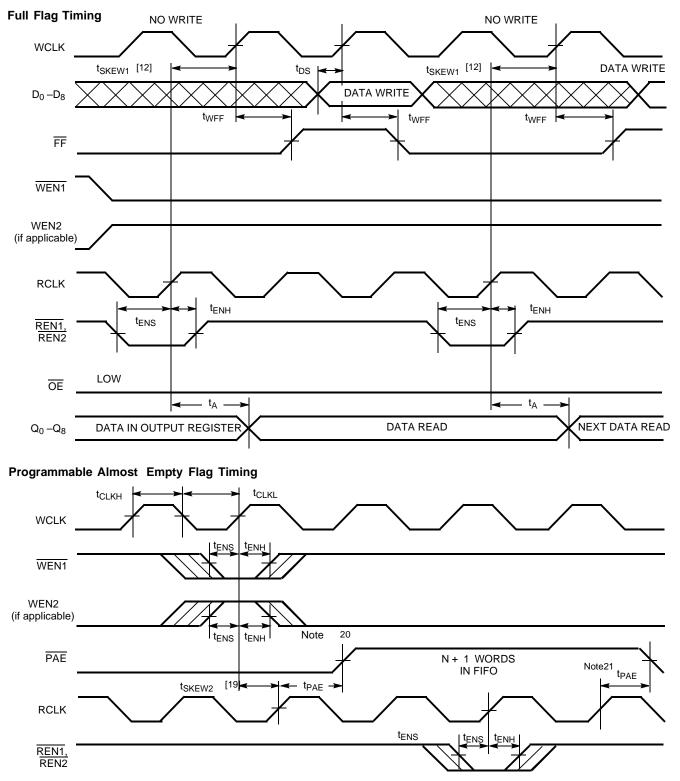

When the WEN1 signal is active LOW, WEN2 is active HIGH, and FF is active HIGH, data present on the  $D_{0-8}$  pins is written into the FIFO on <u>each</u> rising edge of the WCLK signal. Similarly, when the REN1 and REN2 signals are active LOW and EF is active HIGH, data in the FIFO memory will be presented on the  $Q_{0-8}$  outputs. New data will be presented on each rising edge of RCLK while REN1 and REN2 are active. REN1 and REN2 must set up t<sub>ENS</sub> before RCLK for it to be a valid read function. WEN1 and WEN2 must occur t<sub>ENS</sub> before WCLK for it to be a valid write function.

An output enable  $\overline{(OE)}$  pin is provided to three-state the  $Q_{0-8}$  outputs when  $\overline{OE}$  is asserted. When  $\overline{OE}$  is enabled (LOW),

data in the output register will be available to the  $Q_{0-8}$  outputs after  $t_{OE}$ . If devices are cascaded, the  $\overline{OE}$  function will only output data on the FIFO that is read enabled.

The FIFO contains overflow circuitry to disallow additional writes when the FIFO is full, and underflow circuitry to disallow additional reads when the FIFO is empty. An empty FIFO maintains the data of the last valid read on its  $Q_{0-8}$  outputs even after additional reads occur.

Write Enable 1 (WEN1). If the FIFO is configured for programmable flags, Write Enable 1 (WEN1) is the only write <u>enable</u> control pin. In this configuration, when Write Enable 1 (WEN1) is LOW, data can be loaded into the input register and RAM array on the LOW-to-HIGH transition of every write clock (WCLK). Data is stored is the RAM array sequentially and independently of any on-going read operation.

Write Enable 2/Load (WEN2/LD). This is a dual-purpose pin. The FIFO is configured at Reset to have programmable flags or to have two write enables, which allows for depth expansion. If Write Enable 2/Load (WEN2/LD) is set active HIGH at Reset (RS = LOW), this pin operates as a second write enable pin.

If the FIF<u>O is configured to have two write enables, when Write</u> Enable (WEN1) is LOW and Write Enable 2/Load (WEN2/LD) is HIGH, data can be loaded into the input register and RAM array on the LOW-to-HIGH transition of every write clock (WCLK). Data is stored in the RAM array sequentially and independently of any on-going read operation.

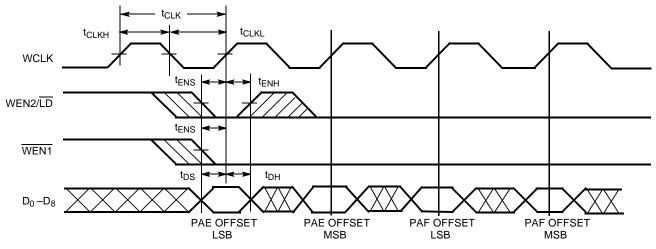

#### Programming

When WEN2/LD is held LOW during Reset, this pin is the load (LD) enable for flag offset programming. In this configuration, WEN2/LD can be used to access the four 9-bit offset registers contained in the CY7C4261/71/81/91V for writing or reading data to these registers.

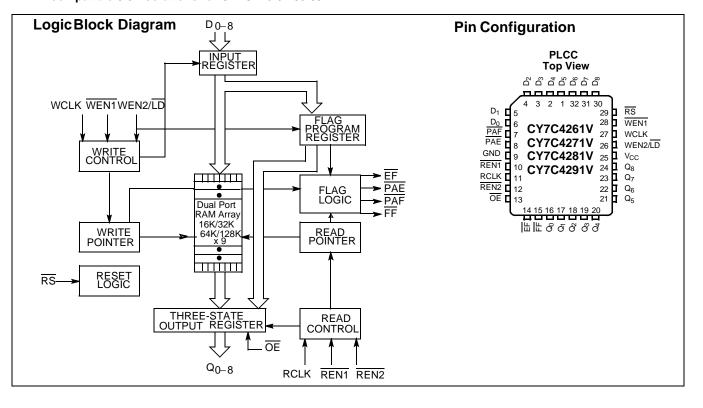

When the device is configured for programmable flags and both WEN2/LD and WEN1 are LOW, the first LOW-to-HIGH transition of WCLK writes data from the data inputs to the empty offset least significant bit (LSB) register. The second, third, and fourth LOW-to-HIGH transitions of WCLK store data in the empty offset most significant bit (MSB) register, full offset LSB register, and full offset MSB register, respectively, when WEN2/LD and WEN1 are LOW. The fifth LOW-to-HIGH transition of WCLK while WEN2/LD and WEN1 are LOW writes data to the empty LSB register again. *Figure 1* shows the registers sizes and default values for the various device types.

Figure 1. Offset Register Location and Default Values

It is not necessary to write to all the offset registers at one time. A subset of <u>th</u>e offset registers can be written; then by bringing the WEN2/LD input HIGH, the FIFO is returned to normal read and write operation. The next time WEN2/LD is brought LOW, a write operation stores data in the next offset register in sequence.

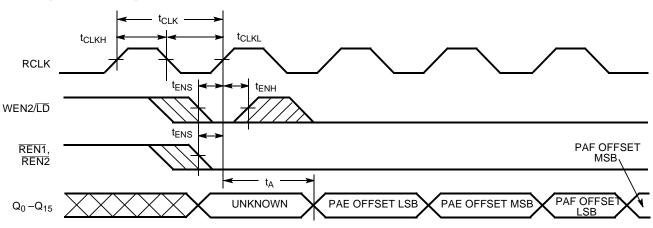

The contents of the offset registers can be read to the data outputs when WEN2/LD is LOW and both REN1 and REN2 are LOW. LOW-to-HIGH transitions of RCLK read register contents to the data outputs. Writes and reads should not be performed simultaneously on the offset registers.

#### Programmable Flag (PAE, PAF) Operation

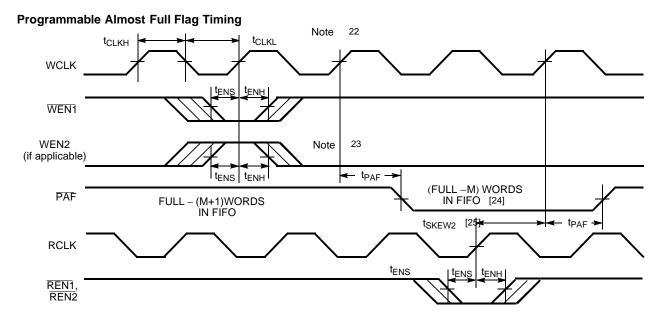

Whether the flag offset registers are programmed as described in *Table 1* or the default values are used, the programmable almost-empty flag (PAE) and programmable almost-full flag (PAF) states are determined by their corresponding offset registers and the difference between the read and write pointers.

| Table 1. Writing the Offset Registers <sup>1</sup> | Table 1. | Vriting the Offset Registe | ers <sup>[1]</sup> |

|----------------------------------------------------|----------|----------------------------|--------------------|

|----------------------------------------------------|----------|----------------------------|--------------------|

| LD | WEN | WCLK | Selection                                                                          |

|----|-----|------|------------------------------------------------------------------------------------|

| 0  | 0   |      | Empty Offset (LSB)<br>Empty Offset (MSB)<br>Full Offset (LSB)<br>Full Offset (MSB) |

| 0  | 1   |      | No Operation                                                                       |

| 1  | 0   |      | Write Into FIFO                                                                    |

| 1  | 1   |      | No Operation                                                                       |

The number formed by the empty offset least significant bit register and empty offset most significant bit register is referred to as *n* and determines the operation of PAE. PAF is synchronized to the LOW-to-HIGH transition of RCLK by one flip-flop and is LOW when the FIFO contains n or fewer unread words. PAE is set HIGH by the LOW-to-HIGH transition of RCLK when the FIFO contains (n+1) or greater unread words.

The number formed by the full offset least significant bit register and full offset most significant bit register is referred to as *m* and determines the operation of PAF. PAE is synchronized to the LOW-to-HIGH transition of WCLK by one flip-flop and is set LOW when the number of unread words in the FIFO is greater than or equal to CY7C4261V (16k – m), CY7C4271V (32k – m), CY7C4281V (64k - m) and CY7C4291V (128k – m). PAF is set HIGH by the LOW-to-HIGH transition of WCLK when the number of available memory locations is greater than m.

#### Note:

1. The same selection sequence applies to reading from the registers. REN1 and REN2 are enabled and a read is performed on the LOW-to-HIGH transition of RCLK.

#### Table 2. Status Flags

|                                     | Number of Words in FIFO             |                                     |                                          |    |     |     |    |

|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------------------|----|-----|-----|----|

| CY7C4261V                           | CY7C4271V                           | V CY7C4281V CY7C4291V               |                                          | FF | PAF | PAE | EF |

| 0                                   | 0                                   | 0                                   | 0                                        | Н  | Н   | L   | L  |

| 1 to n <sup>[2]</sup>                    | Н  | Н   | L   | Н  |

| (n+1) to (1638 – (m+1))             | (n+1) to (32768 – (m+1))            | (n+1) to (65536 – (m+1))            | (n+1) to (131072–<br>(m+1))              | Н  | Н   | Н   | Н  |

| (16384 – m) <sup>[3]</sup> to 16383 | (32768 – m) <sup>[3]</sup> to 32767 | (65536 – m) <sup>[3]</sup> to 65535 | (131072 – m) <sup>[3]</sup> to<br>131071 | Н  | L   | Н   | Н  |

| 16384                               | 32768                               | 65536                               | 131072                                   | L  | L   | Н   | Н  |

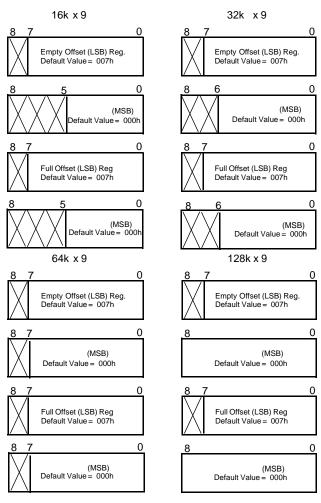

#### Width-Expansion Configuration

Word width may be increased simply by connecting the corresponding input controls signals of multiple devices. A composite flag should be created for each of the end-point status flags (EF and FF). The partial status flags (PAE and PAF) can be detected from any one device. Figure 2 demonstrates a 18-bit word width by using two CY7C42x1Vs. Any word width can be attained by adding additional CY7C42x1Vs.

When the CY7C42x1V is in a Width-Expansion Configuration, the Read Enable (REN2) control input can be grounded (see Figure 2). In this configuration, the Write Enable 2/Load (WEN2/LD) pin is set to LOW at Reset so that the pin operates as a control to load and read the programmable flag offsets.

#### Flag Operation

The CY7C4261/71/81/91V devices provide five flag pins to indicate the condition of the FIFO contents. Empty, Full, PAE, and PAF are synchronous.

#### Full Flag

The Full Flag (FF) will go LOW when the device is full. Write operations are inhibited whenever FF is LOW regardless of the state of WEN1 and WEN2/LD. FF is synchronized to WCLK, i.e., it is exclusively updated by each rising edge of WCLK.

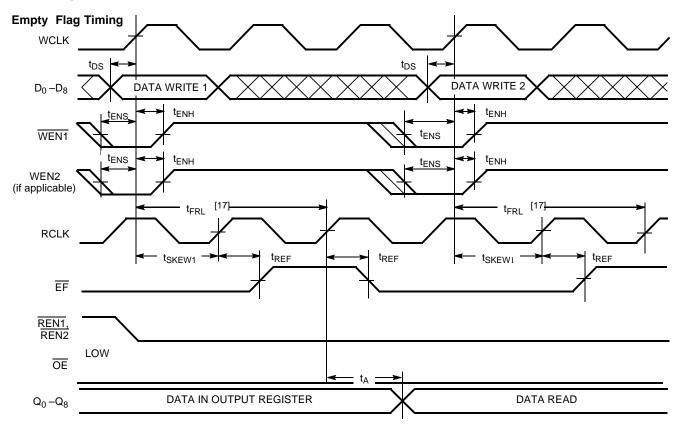

#### **Empty Flag**

The Empty Flag ( $\overline{EF}$ ) will go LOW when the device is empty. Read operations are inhibited whenever EF is LOW, regardless of the state of REN1 and REN2. EF is synchronized to RCLK, i.e., it is exclusively updated by each rising edge of RCLK.

Figure 2. Block Diagram of 16k/32k/64k/128k x 9 Low-Voltage Deep Sync FIFO Memory Used in a Width-Expansion Configuration

- n = Empty Offset (n = 7 default value). m = Full Offset (m = 7 default value).

# CY7C4261V/CY7C4271V CY7C4281V/CY7C4291V

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                                        |  |

|--------------------------------------------------------------------------|--|

| Ambient Temperature with<br>Power Applied55°C to +125°C                  |  |

| Supply Voltage to Ground Potential –0.5V to +3.6V                        |  |

| DC Voltage Applied to Outputs in High-Z State0.5V to $\rm V_{CC}$ + 0.5V |  |

| DC Input Voltage                                           | . –0.5V to V <sub>CC</sub> + 0.5V |

|------------------------------------------------------------|-----------------------------------|

| Output Current into Outputs (LOW)                          | 20 mA                             |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | > 2001V                           |

| Latch-up Current                                           | > 200 mA                          |

# **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub> <sup>[4]</sup> |

|------------|---------------------|--------------------------------|

| Commercial | 0°C to +70°C        | 3.3V ±300 mV                   |

| Industrial | –40°C to +85°C      | 3.3V ±300 mV                   |

### Electrical Characteristics Over the Operating Range

|                                      |                               |                                                                |              |      | '1/81/91V-<br>0 |      | ′1/81/91V-<br>5 |      | /1/81/91V-<br>25 |      |

|--------------------------------------|-------------------------------|----------------------------------------------------------------|--------------|------|-----------------|------|-----------------|------|------------------|------|

| Parameter                            | Description                   | Test Conditio                                                  | ns           | Min. | Max.            | Min. | Max.            | Min. | Max.             | Unit |

| V <sub>OH</sub>                      | Output HIGH<br>Voltage        | $V_{CC} = Min., I_{OH} = -1$<br>$V_{CC} = 3.0V, I_{OH} = -2$   |              | 2.4  |                 | 2.4  |                 | 2.4  |                  | V    |

| V <sub>OL</sub>                      | Output LOW<br>Voltage         | $V_{CC} = Min., I_{OL} = 4.0$<br>$V_{CC} = 3.0V, I_{OL} = 8.0$ | 0 mA<br>0 mA |      | .04             |      | 0.4             |      | 0.4              | V    |

| V <sub>IH</sub>                      | Input HIGH<br>Voltage         |                                                                |              | 2.0  | V <sub>CC</sub> | 2.0  | V <sub>CC</sub> | 2.0  | V <sub>CC</sub>  | V    |

| V <sub>IL</sub>                      | Input LOW<br>Voltage          |                                                                |              | -0.5 | 0.8             | -0.5 | 0.8             | -0.5 | 0.8              | V    |

| I <sub>IX</sub>                      | Input Leakage<br>Current      | V <sub>CC</sub> = Max.                                         |              | -10  | +10             | -10  | +10             | -10  | +10              | μA   |

| I <sub>OZL</sub><br>I <sub>OZH</sub> | Output OFF,<br>High Z Current | $\overline{OE} \ge V_{IH},$<br>$V_{SS} < V_O < V_{CC}$         |              | -10  | +10             | -10  | +10             | -10  | +10              | μA   |

| I <sub>CC1</sub> <sup>[5]</sup>      | Active Power                  | C                                                              | om'l         |      | 25              |      | 25              |      | 25               | mA   |

|                                      | Supply Current                | In                                                             | nd           |      |                 |      | 30              |      |                  | mA   |

| I <sub>SB</sub> <sup>[6]</sup>       | Average                       |                                                                | om'l         |      | 4               |      | 4               |      | 4                | mA   |

|                                      | Standby Current               | In                                                             | nd           |      |                 |      | 4               |      |                  | mA   |

## Capacitance<sup>[7]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 5    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 3.3V$                         | 7    | pF   |

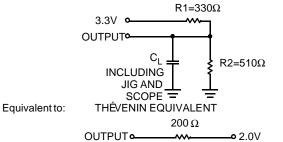

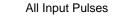

## AC Test Loads and Waveforms (-15 and -25)<sup>[8, 9]</sup>

Notes:

4.  $V_{CC}$  Range for commercial -10 ns is 3.3V ±150mV.

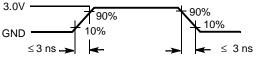

Input signals switch from 0V to 3V with a rise/fall time of less than 3 ns, clocks and clock enables switch at maximum frequency of 20 MHz, while data inputs switch at 10 MHz. Outputs are unloaded.) All inputs =  $V_{CC} - 0.2V$ , except WCLK and RCLK (which are at frequency = 0 MHz). All outputs are unloaded. Tested initially and after any design or process changes that may affect these parameters.  $C_L = 30 \text{ pF}$  for all AC parameters except for t<sub>OHZ</sub>. 5.

6.

7.

8.

9.  $C_L = 5 \text{ pF}$  for  $t_{OHZ}$ .

# AC Test Loads and Waveforms (continued) (-10)

#### Switching Characteristics Over the Operating Range

|                    |                                                                                               |      | 71/81/91V-<br>I0 | 7C4261/71/81/91V-<br>15 |      | 7C4261/71/81/91V-<br>25 |      |      |  |

|--------------------|-----------------------------------------------------------------------------------------------|------|------------------|-------------------------|------|-------------------------|------|------|--|

| Parameter          | Description                                                                                   | Min. | Max.             | Min.                    | Max. | Min.                    | Max. | Unit |  |

| t <sub>S</sub>     | Clock Cycle Frequency                                                                         |      | 100              |                         | 66.7 |                         | 40   | MHz  |  |

| t <sub>A</sub>     | Data Access Time                                                                              | 2    | 8                | 2                       | 10   | 2                       | 15   | ns   |  |

| t <sub>CLK</sub>   | Clock Cycle Time                                                                              | 10   |                  | 15                      |      | 25                      |      | ns   |  |

| t <sub>CLKH</sub>  | Clock HIGH Time                                                                               | 4.5  |                  | 6                       |      | 10                      |      | ns   |  |

| t <sub>CLKL</sub>  | Clock LOW Time                                                                                | 4.5  |                  | 6                       |      | 10                      |      | ns   |  |

| t <sub>DS</sub>    | Data Set-up Time                                                                              | 3.5  |                  | 4                       |      | 6                       |      | ns   |  |

| t <sub>DH</sub>    | Data Hold Time                                                                                | 0    |                  | 0                       |      | 1                       |      | ns   |  |

| t <sub>ENS</sub>   | Enable Set-up Time                                                                            | 3.5  |                  | 4                       |      | 6                       |      | ns   |  |

| t <sub>ENH</sub>   | Enable Hold Time                                                                              | 0    |                  | 0                       |      | 1                       |      | ns   |  |

| t <sub>RS</sub>    | Reset Pulse Width <sup>[10]</sup>                                                             | 10   |                  | 15                      |      | 25                      |      | ns   |  |

| t <sub>RSS</sub>   | Reset Set-up Time                                                                             | 8    |                  | 10                      |      | 15                      |      | ns   |  |

| t <sub>RSR</sub>   | Reset Recovery Time                                                                           | 8    |                  | 10                      |      | 15                      |      | ns   |  |

| t <sub>RSF</sub>   | Reset to Flag and Output Time                                                                 |      | 10               |                         | 15   |                         | 25   | ns   |  |

| t <sub>OLZ</sub>   | Output Enable to Output in Low Z <sup>[11]</sup>                                              | 0    |                  | 0                       |      | 0                       |      | ns   |  |

| t <sub>OE</sub>    | Output Enable to Output Valid                                                                 | 3    | 7                | 3                       | 10   | 3                       | 12   | ns   |  |

| t <sub>OHZ</sub>   | Output Enable to Output in High Z <sup>[11]</sup>                                             | 3    | 7                | 3                       | 8    | 3                       | 12   | ns   |  |

| t <sub>WFF</sub>   | Write Clock to Full Flag                                                                      |      | 8                |                         | 10   |                         | 15   | ns   |  |

| t <sub>REF</sub>   | Read Clock to Empty Flag                                                                      |      | 8                |                         | 10   |                         | 15   | ns   |  |

| t <sub>PAF</sub>   | Clock to Programmable Almost-Full Flag                                                        |      | 8                |                         | 10   |                         | 15   | ns   |  |

| t <sub>PAE</sub>   | Clock to Programmable Almost-Full Flag                                                        |      | 8                |                         | 10   |                         | 15   | ns   |  |

| t <sub>SKEW1</sub> | Skew Time between Read Clock and Write Clock for Empty Flag and Full Flag                     | 5    |                  | 6                       |      | 10                      |      | ns   |  |

| t <sub>SKEW2</sub> | Skew Time between Read Clock and Write<br>Clock for Almost-Empty Flag and<br>Almost-Full Flag | 10   |                  | 15                      |      | 18                      |      | ns   |  |

Notes:

Pulse widths less than minimum values are not allowed.

Values guaranteed by design, not currently tested.

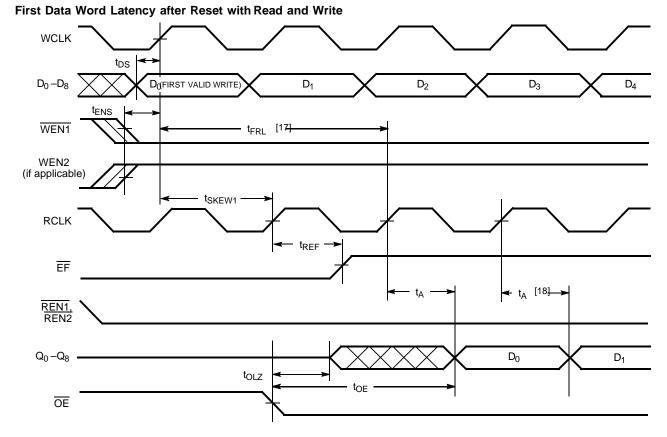

### **Switching Waveforms**

- 12. t<sub>SKEW1</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW1</sub>, then FF may not change state until the next WCLK rising edge.

- 13. t<sub>SKEW1</sub> is the minimum time between a rising WCLK edge and a rising <u>RCLK</u> edge to guarantee that EF will go HIGH during the current clock cycle. It the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>SKEW2</sub>, then EF may not change state until the next RCLK rising edge.

- The clocks (RCLK, WCLK) can be free-<u>running during reset</u>.

After reset, the <u>outputs will be LOW if OE = 0</u> and three-state if OE=1.

Holding WEN2/LD HIGH during reset will make the pin act as a second enable pin. Holding WEN2/LD LOW during reset will make the pin act as a load enable for the programmable flag offset registers.

- When t<sub>SKEW1</sub> ≥ minimum specification, t<sub>FRL</sub> (maximum) = t<sub>CLK</sub> + t<sub>SKEW2</sub>. When t<sub>SKEW1</sub> < minimum specification, t<sub>FRL</sub> (maximum) = either 2\*t<sub>CLK</sub> + t<sub>SKEW1</sub> or t<sub>CLK</sub> + t<sub>SKEW1</sub>. The Latency Timing applies only at the Empty Boundary (EF = LOW).

The first word is available the cycle after EF goes HIGH, always.

- t<sub>SKEW2</sub> is the minimum time between a rising WCLK and a rising RCLK edge for PAE to change state during that clock cycle. If the time between the edge of WCLK and the rising RCLK is less than t<sub>SKEW2</sub>, then PAE may not change state until the next RCLK. 19.

- 20. PAE offset = n. 21. If a read is performed on this rising edge of the read clock, there will be Empty + (n-1) words in the FIFO when PAE goes LOW.

#### Write Programmable Registers

- If a write is performed on this rising edge of the write clock, there will be Full (m-1) words of the FIFO when  $\overline{PAF}$  goes LOW. PAF offset = m. 22

- 23.

- TAF UITSET = IT. 16K m words for CY7C4261V, 32K m words for CY7C4271V, 64K m words for CY7C4281V, and 128K m words for CY4291V. t<sub>SKEW2</sub> is the minimum time between a rising RCLK edge and a rising WCLK edge for PAF to change during that clock cycle. If the time between the rising edge of RCLK and the rising edge of WCLK is less than t<sub>SKEW2</sub>, then PAF may not change state until the next WCLK. 24. 25.

#### **Read Programmable Registers**

# **Ordering Information**

#### 16Kx9 Low-voltage Deep Sync FIFO

| Speed<br>(ns) | Ordering Code     | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|-------------------|-----------------|-------------------------------------|--------------------|

| 10            | CY7C4261V-10JC    | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

| 15            | CY7C4261V-15JC    | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C4261V-15JI    | J65             | 32-Lead Plastic Leaded Chip Carrier | Industrial         |

| 25            | 25 CY7C4261V-25JC |                 | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

# 32Kx9 Low-voltage Deep Sync FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|----------------|-----------------|-------------------------------------|--------------------|

| 10            | CY7C4271V-10JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

| 15            | CY7C4271V-15JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C4271V-15JI | J65             | 32-Lead Plastic Leaded Chip Carrier | Industrial         |

| 25            | CY7C4271V-25JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

#### 64kx9 Low-voltage Deep Sync FIFO

| Speed<br>(ns) | Ordering Code  | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|----------------|-----------------|-------------------------------------|--------------------|

| 10            | CY7C4281V-10JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

| 15            | CY7C4281V-15JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7C4281V-15JI | J65             | 32-Lead Plastic Leaded Chip Carrier | Industrial         |

| 25            | CY7C4281V-25JC | J65             | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

#### 128kx9 Low-voltage Deep Sync FIFO

| Speed<br>(ns)                                             | Ordering Code  | Package<br>Name                     | Package Type                        | Operating<br>Range |

|-----------------------------------------------------------|----------------|-------------------------------------|-------------------------------------|--------------------|

| 10                                                        | CY7C4291V-10JC | J65                                 | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

| 15                                                        | CY7C4291V-15JC | J65                                 | 32-Lead Plastic Leaded Chip Carrier | Commercial         |

|                                                           | CY7C4291V-15JI | J65                                 | 32-Lead Plastic Leaded Chip Carrier | Industrial         |

| 25 CY7C4291V-25JC J65 32-Lead Plastic Leaded Chip Carrier |                | 32-Lead Plastic Leaded Chip Carrier | Commercial                          |                    |

Document #: 38-06013 Rev. \*A

# CY7C4261V/CY7C4271V CY7C4281V/CY7C4291V

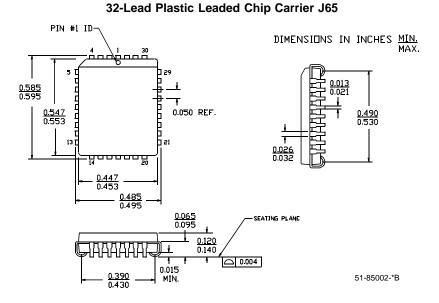

# Package Diagram

Deep Sync is a trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

Document #: 38-06013 Rev. \*A

Page 15 of 16

© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges. Downloaded from Elcodis.com electronic components distributor

# **Document History Page**

| Document Title: CY7C4261V/CY7C4271V/CY7C4281V/CY7C4291V 16K/32K/64K/128K/X9 Low-Voltage Deep Sync FIFO Document Number: 38-06013 |         |            |                    |                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                                                             | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                  |

| **                                                                                                                               | 106474  | 09/15/01   | SZV                | Changed Spec number from 38-00656 to 38-06013                                                                                                                                                          |

| *A                                                                                                                               | 127858  | 09/04/03   | FSG                | $\begin{array}{l} Changed: t_{SKEW2} \mbox{ to } t_{SKEW1} \mbox{ in Switching Waveforms "Empty Flag Timing" diagram} \\ Fixed \mbox{ flag timing diagram in Switching Waveforms section} \end{array}$ |