August 1986 Revised March 2000

# DM74LS85 4-Bit Magnitude Comparator

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

These 4-bit magnitude comparators perform comparison of straight binary or BCD codes. Three fully-decoded decisions about two, 4-bit words (A, B) are made and are externally available at three outputs. These devices are fully expandable to any number of bits without external gates. Words of greater length may be compared by connecting comparators in cascade. The A > B, A < B, and A = B outputs of a stage handling less-significant bits are connected to the corresponding inputs of the next stage handling more-significant bits. The stage handling the least-significant bits must have a high-level voltage applied to the A = B input. The cascading path is implemented with only a two-gate-level delay to reduce overall comparison times for long words.

#### Features

- Typical power dissipation 52 mW

- Typical delay (4-bit words) 24 ns

## **Ordering Code:**

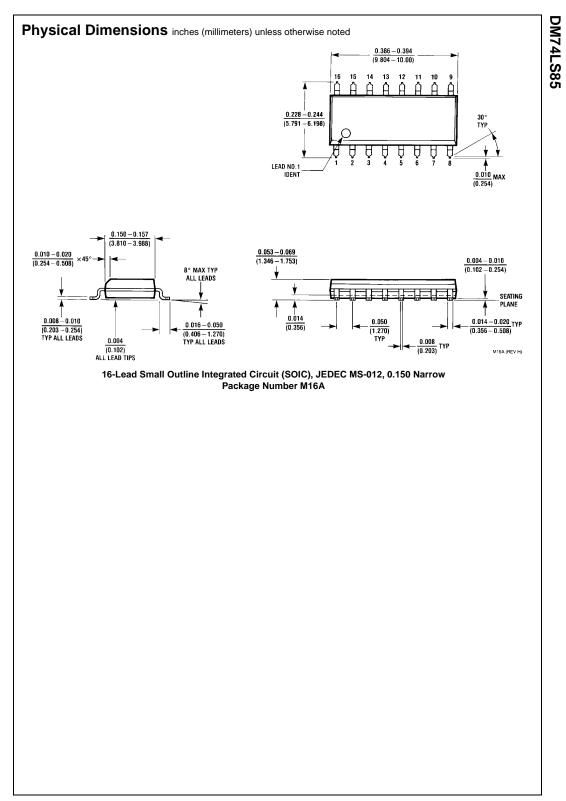

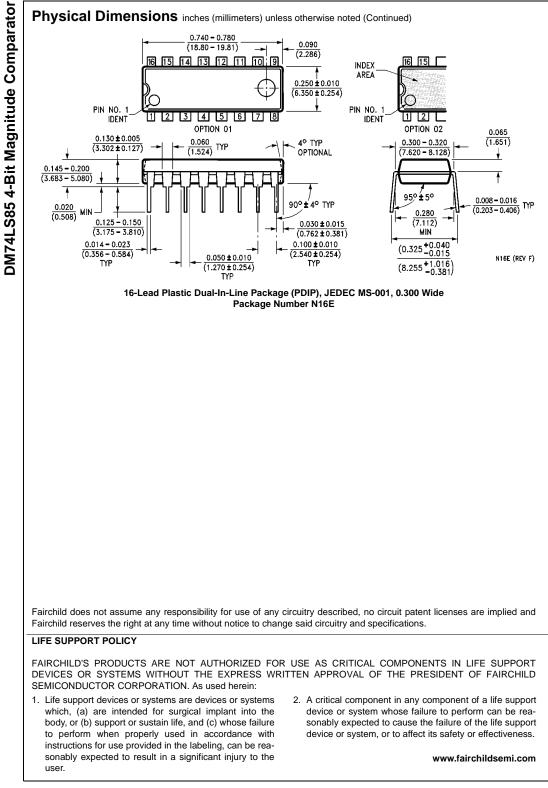

| Order Number           | Package Number           | Package Description                                                         |

|------------------------|--------------------------|-----------------------------------------------------------------------------|

| DM74LS85M              | M16A                     | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow |

| DM74LS85N              | N16E                     | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

| Devices also available | in Tane and Reel Specify | by appending the suffix letter "X" to the ordering code                     |

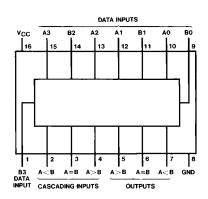

## **Connection Diagram**

© 2000 Fairchild Semiconductor Corporation DS006379

www.fairchildsemi.com

# Function Table

**DM74LS85**

|         | Comp    | baring  |         | 0     | Cascading | 9                         |       | Outputs |                           |

|---------|---------|---------|---------|-------|-----------|---------------------------|-------|---------|---------------------------|

| Inputs  |         |         | Inputs  |       |           |                           |       |         |                           |

| A3, B3  | A2, B2  | A1, B1  | A0, B0  | A > B | A < B     | $\mathbf{A} = \mathbf{B}$ | A > B | A < B   | $\mathbf{A} = \mathbf{B}$ |

| A3 > B3 | Х       | Х       | Х       | Х     | Х         | Х                         | Н     | L       | L                         |

| A3 < B3 | Х       | Х       | Х       | Х     | Х         | Х                         | L     | н       | L                         |

| A3 = B3 | A2 > B2 | Х       | Х       | Х     | Х         | Х                         | Н     | L       | L                         |

| A3 = B3 | A2 < B2 | Х       | Х       | Х     | Х         | Х                         | L     | н       | L                         |

| A3 = B3 | A2 = B2 | A1 > B1 | Х       | Х     | Х         | Х                         | Н     | L       | L                         |

| A3 = B3 | A2 = B2 | A1 < B1 | Х       | Х     | Х         | Х                         | L     | н       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 > B0 | Х     | Х         | Х                         | Н     | L       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 < B0 | Х     | Х         | Х                         | L     | Н       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | н     | L         | L                         | Н     | L       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | L     | Н         | L                         | L     | н       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | L     | L         | Н                         | L     | L       | Н                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | Х     | Х         | н                         | L     | L       | Н                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | н     | н         | L                         | L     | L       | L                         |

| A3 = B3 | A2 = B2 | A1 = B1 | A0 = B0 | L     | L         | L                         | н     | н       | L                         |

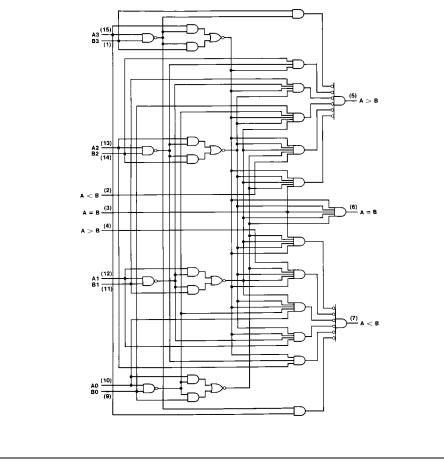

# Logic Diagram

www.fairchildsemi.com

2

### Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# DM74LS85

# **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| / <sub>cc</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| / <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| / <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| ОН              | HIGH Level Output Current      |      |     | -0.4 | mA    |

| OL              | LOW Level Output Current       |      |     | 8    | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                    | Conditions                                   | Min    | Typ<br>(Note 2) | Max  | Units |    |  |

|-----------------|------------------------------|----------------------------------------------|--------|-----------------|------|-------|----|--|

| VI              | Input Clamp Voltage          | $V_{CC} = Min, I_I = -18 mA$                 |        |                 | -1.5 | V     |    |  |

| V <sub>OH</sub> | HIGH Level                   | $V_{CC} = Min, I_{OH} = Max$                 | 2.7    | 3.4             |      | V     |    |  |

|                 | Output Voltage               | $V_{IL} = Max, V_{IH} = Min$                 | 2.7    | 3.4             |      | v     |    |  |

| V <sub>OL</sub> | LOW Level                    | $V_{CC} = Min, I_{OL} = Max$                 |        | 0.35            | 0.5  |       |    |  |

|                 | Output Voltage               | $V_{IL} = Max, V_{IH} = Min$                 |        | 0.55            | 0.5  | V     |    |  |

|                 |                              | $I_{OL} = 4 \text{ mA}, V_{CC} = \text{Min}$ |        | 0.25            | 0.4  |       |    |  |

| I <sub>I</sub>  | Input Current @ Max          | V <sub>CC</sub> = Max                        | A < B  |                 |      | 0.1   |    |  |

|                 | Input Voltage                | $V_1 = 7V$                                   | A > B  |                 |      | 0.1   | mA |  |

|                 |                              |                                              | Others |                 |      | 0.3   |    |  |

| Ι <sub>Η</sub>  | HIGH Level                   | V <sub>CC</sub> = Max                        | A < B  |                 |      | 20    |    |  |

|                 | Input Current                | $V_I = 2.7V$                                 | A > B  |                 |      | 20    | μΑ |  |

|                 |                              |                                              | Others |                 |      | 60    |    |  |

| IIL             | LOW Level                    | V <sub>CC</sub> = Max                        | A < B  |                 |      | -0.4  |    |  |

|                 | Input Current                | $V_I = 0.4V$                                 | A > B  |                 |      | -0.4  | mA |  |

|                 |                              |                                              | Others |                 |      | -1.2  |    |  |

| I <sub>OS</sub> | Short Circuit Output Current | V <sub>CC</sub> = Max (Note 3)               |        | -20             |      | -100  | mA |  |

| I <sub>CC</sub> | Supply Current               | V <sub>CC</sub> = Max (Note 4)               |        |                 | 10   | 20    | mA |  |

Note 2: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 4: I<sub>CC</sub> is measured with all outputs OPEN, A = B grounded and all other inputs at 4.5V.

| 35 |  |

|----|--|

| õ  |  |

| 4  |  |

| 2  |  |

| N  |  |

| С  |  |

# Switching Characteristics

|                                         |                          | From<br>Input    | To<br>Output | Number of<br>Gate Levels | $R_L = 2 k\Omega$      |     |                        |     |       |

|-----------------------------------------|--------------------------|------------------|--------------|--------------------------|------------------------|-----|------------------------|-----|-------|

| Symbol                                  | Parameter                |                  |              |                          | C <sub>L</sub> = 15 pF |     | C <sub>L</sub> = 50 pF |     | Units |

|                                         |                          |                  |              |                          | Min                    | Max | Min                    | Max |       |

| t <sub>PLH</sub>                        | Propagation Delay Time   | Any A or B       | A < B,       | 3                        |                        | 36  |                        | 42  |       |

|                                         | LOW-to-HIGH Level Output | Data Input       | A > B        | 3                        |                        | 30  |                        | 42  | ns    |

|                                         |                          |                  | A = B        | 4                        |                        | 40  |                        | 40  |       |

| t <sub>PHL</sub>                        | Propagation Delay Time   | Any A or B       | A < B,       | 3                        |                        | 30  |                        | 40  | ns    |

|                                         | HIGH-to-LOW Level Output | Data Input       | A > B        | 5                        |                        | 30  |                        | 40  |       |

|                                         |                          |                  | A = B        | 4                        |                        | 30  |                        | 40  |       |

|                                         | Propagation Delay Time   | A < B  or  A = B | A > B        | 1                        |                        | 22  |                        | 26  | ns    |

|                                         | LOW-to-HIGH Level Output |                  |              |                          |                        | 22  |                        |     |       |

| t <sub>PHL</sub> Propagation Delay Time | Propagation Delay Time   | A < B  or  A = B | A > B        | 1                        |                        | 17  |                        | 26  | ns    |

|                                         | HIGH-to-LOW Level Output |                  | A20          |                          |                        | 17  |                        | 20  | 115   |

| t <sub>PLH</sub>                        | Propagation Delay Time   | A = B            | A = B        | 2                        | 20                     | 20  |                        | 25  | ns    |

|                                         | LOW-to-HIGH Level Output |                  |              |                          |                        |     | 20                     | 115 |       |

| t <sub>PHL</sub>                        | Propagation Delay Time   | A = B            | A = B        | 2                        |                        | 17  |                        | 26  | ns    |

| н                                       | HIGH-to-LOW Level Output | A - D            |              |                          |                        |     |                        |     |       |

| t <sub>PLH</sub>                        | Propagation Delay Time   | A > B  or  A = B | A < B        | 1                        |                        | 22  |                        | 26  | ns    |

|                                         | LOW-to-HIGH Level Output | AZBOIA-D         |              |                          |                        | ~~~ |                        | 20  | 115   |

| t <sub>PHL</sub>                        | Propagation Delay Time   | A > B  or  A = B | A < B        | 1                        |                        | 17  |                        | 26  | ns    |

|                                         | HIGH-to-LOW Level Output |                  |              |                          |                        | .,  |                        | 20  | 115   |

www.fairchildsemi.com

www.fairchildsemi.com

6